# **Backlight Driver with I/O Expander**

# ADP5520

## **FEATURES**

- Efficient asynchronous boost converter for driving up to 6 white LEDs

- 2.7 V to 5.5 V input voltage range

- 128 programmable backlight LED current levels (30 mA maximum)

- Ambient light sensing with autonomous backlight adjustment

- Programmable backlight fade-in/fade-out times

- Programmable backlight dim and off times

- 8 configurable GPIO pins (input, output, up to 4 × 4 keypad)

- Up to 3 auxiliary LED current sinks (1 dedicated, 2 configurable)

- 64 programmable auxiliary LED current levels (14 mA maximum)

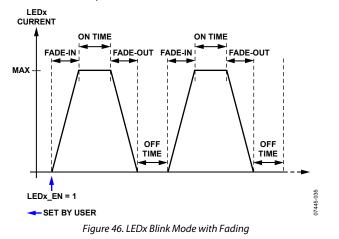

- Programmable auxiliary LED fade-in/fade-out times Programmable auxiliary LED on and off times (allows blinking)

- I<sup>2</sup>C-compatible serial interface

- Interrupt line for signaling an external processor (INT)

- Hard reset (RST)

- **Current limit protection**

- Thermal overload protection Available in small 4.0 mm  $\times$  4.0 mm, 24-lead LFCSP package

#### **APPLICATIONS**

## Display backlight driver for phones that require slider or flip keypad functions with single or multiple LED indicators

#### **GENERAL DESCRIPTION**

The ADP5520 is a versatile single-chip, white LED backlight driver with a user configurable I/O expander. This device fits handset applications where the flip or slider section of the phone requires backlighting, I/O signaling and detecting, auxiliary LED lighting, and keypad functions. By incorporating an I<sup>2</sup>Ccompatible serial interface and a single line interrupt, the ADP5520 significantly reduces the total number of lines required to interface with the baseband processor across the hinge flex.

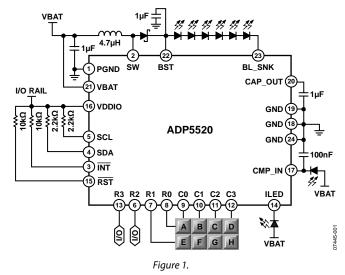

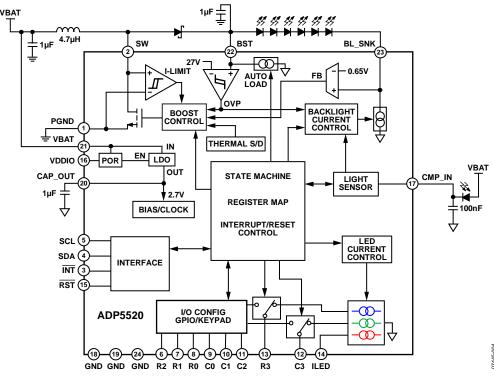

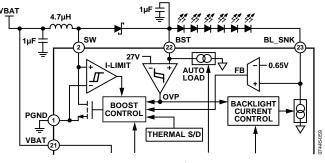

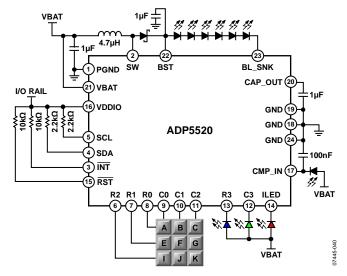

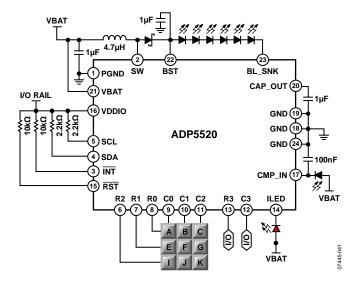

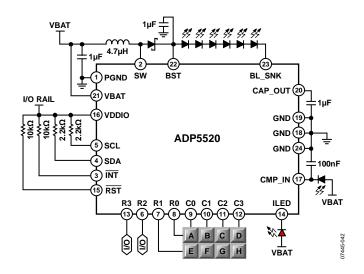

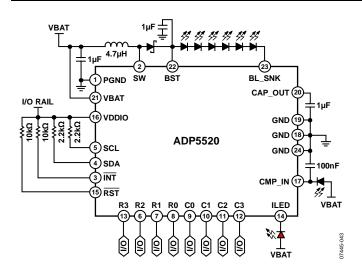

## **TYPICAL OPERATING CIRCUIT**

The ADP5520 can detect ambient light levels and adjust the backlight brightness accordingly, resulting in extended battery operation.

Once configured, the ADP5520 is capable of controlling the flip/slider backlight intensity, on/off timing, dimming, and fading without the intervention of the main processor, which results in valuable battery power saving.

#### Rev. B

#### **Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2008-2017 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# TABLE OF CONTENTS

| Features 1                                  |

|---------------------------------------------|

| Applications1                               |

| Typical Operating Circuit1                  |

| General Description1                        |

| Revision History                            |

| Specifications                              |

| I <sup>2</sup> C Timing Specifications      |

| Absolute Maximum Ratings5                   |

| Thermal Resistance                          |

| ESD Caution                                 |

| Pin Configuration and Function Descriptions |

| Typical Performance Characteristics         |

| Theory of Operation                         |

| Backlight Drive and Control9                |

| Backlight Operating Levels10                |

| Backlight Maximum and Dim Settings10        |

| Backlight Turn On/Off/Dim11                 |

| Automatic Dim and Turn Off Timers11         |

| Linear Backlight Fade In and Fade Out12     |

| Fade Override                               |

## **REVISION HISTORY**

#### 10/2017—Rev. A to Rev. B

| Changed nINT, nRST, and nSTNBY to INT, RST, and |           |

|-------------------------------------------------|-----------|

| STNBY                                           | hroughout |

| Change to Package Type Column, Table 4          | 5         |

| Changes to Figure 3 and Table 5                 | 6         |

| Updated Outline Dimensions                      |           |

| Changes to Ordering Guide                       |           |

\_ \_

| Advanced Fading (Square)13                                       |

|------------------------------------------------------------------|

| Advanced Fading (Cubic 1 and Cubic 2)14                          |

| Ambient Light Sensing14                                          |

| Automatic Backlight Adjustment15                                 |

| I/O Expansion Pins (GPIOs)15                                     |

| I/O Expansion Pins (Keypad Matrix)15                             |

| I/O Expansion Pins and ILED Pin (Auxiliary LED Current<br>Sinks) |

| Interrupt Output (INT)19                                         |

| Reset Input (RST)                                                |

| Communication Interface                                          |

| Register Map                                                     |

| Detailed Register Descriptions                                   |

| Applications Information                                         |

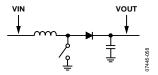

| Converter Topology                                               |

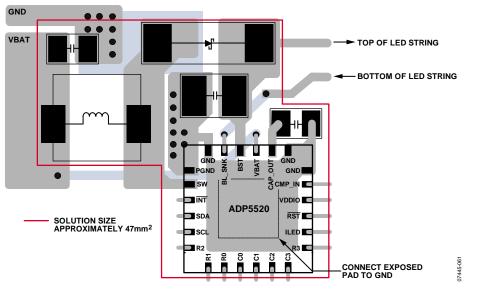

| PCB Layout                                                       |

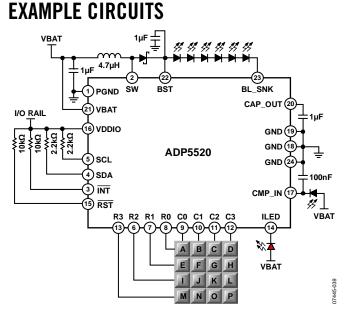

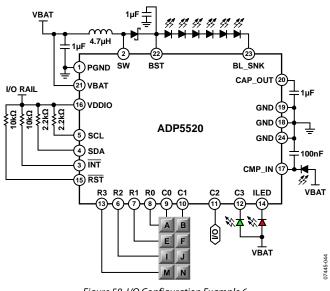

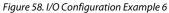

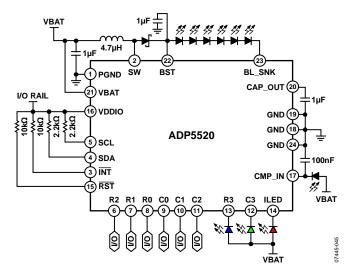

| Example Circuits                                                 |

| Outline Dimensions                                               |

| Ordering Guide                                                   |

#### 1/2010-Rev. 0 to Rev. A

| Changes to Table 1         | 3 |

|----------------------------|---|

| Changes to Table 5         |   |

| Changes to Figure 32       |   |

| Updated Outline Dimensions |   |

| Changes to Ordering Guide  |   |

| 0 0                        |   |

7/2008—Revision 0: Initial Version

# **SPECIFICATIONS**

VBAT = 2.7 V to 4.8 V,  $T_J = -40^{\circ}$ C to +125°C, unless otherwise noted.<sup>1</sup>

#### Table 1.

| Parameter                                                                       | Symbol                  | Conditions                                             | Min                | Тур | Max              | Unit  |

|---------------------------------------------------------------------------------|-------------------------|--------------------------------------------------------|--------------------|-----|------------------|-------|

| SUPPLY VOLTAGE                                                                  |                         |                                                        |                    |     |                  |       |

| VBAT Input Voltage Range                                                        | VBAT                    |                                                        | 2.7                |     | 5.5              | V     |

| VDDIO Input Voltage Range                                                       | V <sub>VDDIO</sub>      |                                                        | 1.7                |     | 3.3 <sup>2</sup> | V     |

| Undervoltage Lockout Threshold                                                  | UVLOVBAT                | VBAT falling                                           | 1.7                | 2.1 |                  | V     |

|                                                                                 | UVLO <sub>VBAT</sub>    | VBAT rising                                            |                    | 2.4 | 2.7              | V     |

|                                                                                 | UVLO <sub>VDDIO</sub>   | VDDIO falling                                          | 1.1                | 1.3 |                  | V     |

|                                                                                 | UVLO <sub>VDDIO</sub>   | VDDIO rising                                           |                    | 1.4 | 1.62             | V     |

| SW leakage                                                                      | SWLEAKAGE               |                                                        |                    | 0.1 | 1                | μΑ    |

| SUPPLY CURRENT                                                                  |                         |                                                        |                    |     |                  |       |

| Shutdown Current <sup>3</sup>                                                   | I <sub>SD</sub>         | VDDIO = 0 V                                            |                    | 0.1 | 1                | μΑ    |

| Standby Current <sup>4</sup>                                                    | Istnby                  | $\frac{1.7 \text{ V} \leq}{\text{STNBY}} = 0$          |                    | 25  | 45               | μΑ    |

| BACKLIGHT LED DRIVER (SW, BST)                                                  |                         |                                                        |                    |     |                  |       |

| Current Limit (Peak Inductor Current)                                           |                         |                                                        | 450                | 600 | 750              | mA    |

| Switch On Resistance                                                            |                         |                                                        | 100                | 200 | 400              | mΩ    |

| Overvoltage Limit                                                               |                         |                                                        | 24.5               | 27  | 29.5             | V     |

| Boost Startup Time                                                              |                         |                                                        |                    | 1   |                  | ms    |

| BACKLIGHT LED CURRENT SINK (BL_SNK)                                             |                         |                                                        |                    |     |                  |       |

| Full-Scale Backlight Current                                                    |                         |                                                        | 26                 | 30  | 32               | mA    |

| Backlight Current Ramp Rate                                                     |                         | Fade timers disabled                                   |                    | 0.3 |                  | mA/ms |

| AMBIENT LIGHT SENSOR (CMP_IN)                                                   |                         |                                                        |                    |     |                  |       |

| Full-Scale Current                                                              | BLFULLSCALE             |                                                        | 0.7                | 1   | 1.2              | mA    |

| INPUT LOGIC LEVELS (SCL, SDA, RST, C0, C1, C2, C3, R0, R1, R2, R3) <sup>5</sup> |                         |                                                        |                    |     |                  |       |

| Logic Low Input Voltage                                                         | VIL                     | $1.7 \text{ V} \leq \text{VDDIO} \leq 3.3 \text{ V}^2$ |                    |     | 0.3 × VDDIO      | v     |

| Logic High Input Voltage                                                        | VIH                     | $1.7 \text{ V} \leq \text{VDDIO} \leq 3.3 \text{ V}^2$ | $0.7 \times VDDIO$ |     |                  | V     |

| Input Leakage Current                                                           | VI-LEAKAGE              | $1.7 \text{ V} \leq \text{VDDIO} \leq 3.3 \text{ V}^2$ |                    | 0.1 | 1                | μA    |

| INPUT LOGIC DEBOUNCE (RST, C0, C1, C2, C3, R0, R1, R2, R3) <sup>6</sup>         | V <sub>IL-DBNC</sub>    |                                                        | 50                 | 75  | 100              | μs    |

| PUSH-PULL OUTPUT LOGIC LEVELS (C0, C1, C2, C3, R0, R1, R2, R3) <sup>7</sup>     |                         |                                                        |                    |     |                  |       |

| Logic Low Output Voltage                                                        | Vol                     | $I_{SINK} = 1 \text{ mA}$                              |                    |     | 0.4              | v     |

| Logic High Output Voltage                                                       | Vон                     | $I_{SOURCE} = 1 \text{ mA}$                            | VDDIO - 0.2        |     |                  | v     |

| OPEN-DRAIN OUTPUT LOGIC LEVELS (INT), SDA)                                      |                         |                                                        |                    |     |                  |       |

| Logic Low Output Voltage                                                        | Vol                     | $I_{SINK} = 1 \text{ mA}$                              |                    |     | 0.4              | v     |

| Logic Light Leakage Current                                                     | V <sub>OH-LEAKAGE</sub> | $1.7 \text{ V} \leq \text{VDDIO} \leq 3.3 \text{ V}^2$ |                    | 0.1 | 1                | μA    |

| AUX LED CURRENT SINK (ILED, C3, R3) <sup>8</sup>                                | OT LEARAGE              |                                                        |                    |     |                  |       |

| Leakage                                                                         | LEDLEAKAGE              | Sink disabled                                          |                    | 0.1 | 1                | μA    |

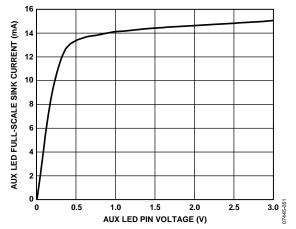

| Full-scale Current Sink                                                         |                         | Applied pin voltage = $1 V$                            | 10.5               | 14  | 16.5             | mA    |

| GPIO PULL-UP RESISTANCE (C0, C1, C2, C3, R0, R1, R2, R3) <sup>9</sup>           |                         | The purchase of                                        | 50                 | 65  | 80               | kΩ    |

| THERMAL SHUTDOWN                                                                | +                       |                                                        |                    |     |                  | +     |

| Thermal Shutdown Threshold                                                      | TS                      | TJ rising                                              |                    | 150 |                  | °C    |

| Thermal Shutdown Hysteresis                                                     | TS                      | T <sub>J</sub> falling                                 |                    | 10  |                  | °C    |

<sup>1</sup> All limits at temperature extremes are guaranteed via correlation using standard statistical quality control (SQC). Typical values are at T<sub>A</sub> = 25<sup>o</sup>C, VBAT = 3.6 V.

$^{\rm 2}$  3.3 V or VBAT, whichever is smaller.

<sup>3</sup> Internal LDO powered down, digital blocks inactive, I<sup>2</sup>C inactive, boost inactive.

<sup>4</sup> Internal LDO powered up, digital blocks active, <sup>1</sup>C active, boost inactive.

<sup>5</sup> C0, C1, C2, C3, R0, R1, R2, and R3 are configured as digital inputs.

<sup>6</sup> C0, C1, C2, C3, R0, R1, R2, and R3 are configured as digital inputs.

<sup>6</sup> C0, C1, C2, C3, R0, R1, R2, and R3 are configured as digital outputs.

<sup>8</sup> C3 and R3 are configured as digital inputs with pull-up.

<sup>9</sup> C0, C1, C2, C3, R0, R1, R2, and R3 are configured as digital inputs with pull-up.

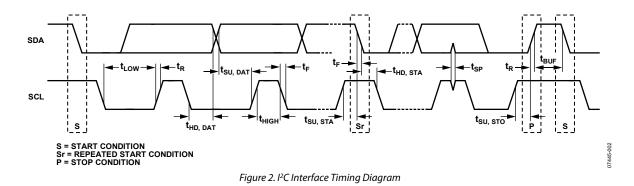

## I<sup>2</sup>C TIMING SPECIFICATIONS

#### Table 2.

| Parameter                                               | Description                                | Min                     | Max | Unit |

|---------------------------------------------------------|--------------------------------------------|-------------------------|-----|------|

| Delay from Reset Deassertion to I <sup>2</sup> C Access |                                            | 60                      |     | μs   |

| f <sub>SCL</sub>                                        | SCL clock frequency                        |                         | 400 | kHz  |

| tнigh                                                   | SCL high time                              | 0.6                     |     | μs   |

| t <sub>LOW</sub>                                        | SCL low time                               | 1.3                     |     | μs   |

| tsu, dat                                                | Data setup time                            | 100                     |     | ns   |

| t <sub>HD, DAT</sub>                                    | Data hold time                             | 0                       | 0.9 | μs   |

| tsu, sta                                                | Setup time for repeated start              | 0.6                     |     | μs   |

| t <sub>hd, sta</sub>                                    | Hold time for start/repeated start         | 0.6                     |     | μs   |

| t <sub>BUF</sub>                                        | Bus free time for stop and start condition | 1.3                     |     | μs   |

| tsu, sto                                                | Setup time for stop condition              | 0.6                     |     | μs   |

| t <sub>R</sub>                                          | Rise time for SCL and SDA                  | 20 + 0.1 C <sub>B</sub> | 300 | ns   |

| tF                                                      | Fall time for SCL and SDA                  | 20 + 0.1 C <sub>B</sub> | 300 | ns   |

| tsp                                                     | Pulse width of suppressed spike            | 0                       | 50  | μs   |

| C <sub>B</sub> <sup>1</sup>                             | Capacitive load for each bus line          |                         | 400 | pF   |

$^1\,C_B$  is the total capacitance of one bus line in picofarads.

# **ABSOLUTE MAXIMUM RATINGS**

#### Table 3.

| Parameter                                                                                              | Rating           |

|--------------------------------------------------------------------------------------------------------|------------------|

| VBAT to GND                                                                                            | -0.3 V to +6 V   |

| VDDIO to GND                                                                                           | –0.3 V to VBAT   |

| SW, BST to GND                                                                                         | –0.3 V to +30 V  |

| ILED, R0, R1 <u>, R2, R3,</u> C0, C1, C2, C3, CMP_IN,<br>SCL, SDA, INT, RST, CAP_OUT, BL_SNK<br>to GND | –0.3 V to +6 V   |

| PGND to GND                                                                                            | –0.3 V to +0.3 V |

| Operating Ambient Temperature Range                                                                    | -40°C to +85°C1  |

| Operating Junction Temperature Range                                                                   | -40°C to +125°C  |

| Storage Temperature Range                                                                              | –65°C to +150°C  |

| Soldering Conditions                                                                                   | JEDEC J-STD-020  |

<sup>1</sup> In applications where high power dissipation and poor thermal resistance are present, the maximum ambient temperature may have to be derated. Maximum ambient temperature ( $T_{A(MAX)}$ ) is dependent on the maximum operating junction temperature ( $T_{J(MAXOP)} = 125^{\circ}$ C), the maximum power dissipation of the device ( $PD_{(MAX)}$ ), and the junction-to-ambient thermal resistance of the part/package in the application ( $\theta_{JA}$ ), using the following equation:  $T_{A(MAX)} = T_{J(MAXOP)} - (\theta_{JA} \times P_{D(MAX)})$ .

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

Absolute maximum ratings apply individually only, not in combination. Unless otherwise specified, all other voltages are referenced to GND.

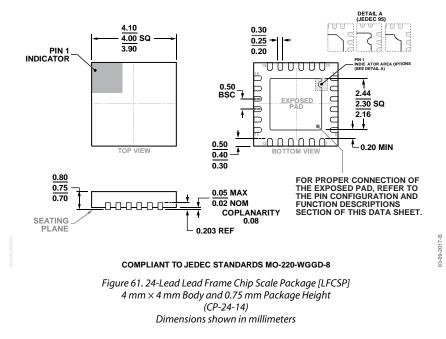

## THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

### Table 4. Thermal Resistance

| Package Type             | θ」Α | Unit |

|--------------------------|-----|------|

| 24-Lead LFCSP (CP-24-14) | 50  | °C/W |

## **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

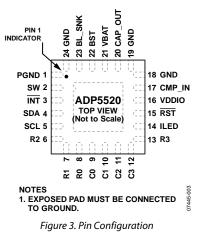

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

#### **Table 5. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                          |

|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | PGND     | Power Switch Output to Ground.                                                                                                                       |

| 2       | SW       | Power Switch Input.                                                                                                                                  |

| 3       | INT      | Processor Interrupt. This pin is active low, and open drain, Pull up to VDDIO.                                                                       |

| 4       | SDA      | I <sup>2</sup> C-Compatible Serial Data Line. Open drain requires external pull-up to VDDIO.                                                         |

| 5       | SCL      | I <sup>2</sup> C-Compatible Serial Clock Line. Open drain requires external pull-up to VDDIO.                                                        |

| 6       | R2       | Row 2 when configured in a keypad matrix, D2 when configured as an I/O.                                                                              |

| 7       | R1       | Row 1 when configured in a keypad matrix, D1 when configured as an I/O.                                                                              |

| 8       | RO       | Row 0 when configured in a keypad matrix, D0 when configured as an I/O.                                                                              |

| 9       | C0       | Column 0 when configured in a keypad matrix, D4 when configured as an I/O.                                                                           |

| 10      | C1       | Column 1 when configured in a keypad matrix, D5 when configured as an I/O.                                                                           |

| 11      | C2       | Column 2 when configured in a keypad matrix, D6 when configured as an I/O.                                                                           |

| 12      | C3       | Column 3 when configured in a keypad matrix, D7 when configured as an I/O, LED 2 when configured as a current sink.                                  |

| 13      | R3       | Row 3 when configured in a keypad matrix, D3 when configured as an I/O, LED 3 when configured as a current sink.                                     |

| 14      | ILED     | LED 1 Current Sink.                                                                                                                                  |

| 15      | RST      | Reset Input, Active Low. This input signal resets the device to the power-up default conditions. Must be driven low for 75 μs (typical) to be valid. |

| 16      | VDDIO    | Supply Voltage for the I/O Pins. Voltage is 1.7 V to 3.3 V (or VBAT, whichever is smaller). If VDDIO = 0, the device goes into full shutdown mode.   |

| 17      | CMP_IN   | Input for Ambient Light Sensing.                                                                                                                     |

| 18      | GND      | Ground.                                                                                                                                              |

| 19      | GND      | Ground.                                                                                                                                              |

| 20      | CAP_OUT  | Capacitor for Internal 2.7 V LDO. A 1 $\mu$ F capacitor must be connected between this pin and GND. Do not use this pin to supply external loads.    |

| 21      | VBAT     | Main Supply Voltage for the IC (2.7 V to 5.5 V).                                                                                                     |

| 22      | BST      | Overvoltage Monitor Input for the Boost Converter.                                                                                                   |

| 23      | BL_SNK   | Backlight Current Sink.                                                                                                                              |

| 24      | GND      | Ground.                                                                                                                                              |

|         | EPAD     | Exposed Pad. Exposed pad must be connected to ground.                                                                                                |

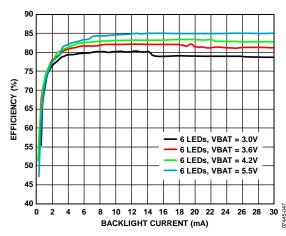

# **TYPICAL PERFORMANCE CHARACTERISTICS**

VBAT = 3.6 V, T<sub>A</sub> = 25°C, unless otherwise noted. Inductor = LPS4012-472MLB. Schottky rectifier = MBR140SFT1G.

Figure 4. Efficiency vs. Backlight Current (6 LEDS)

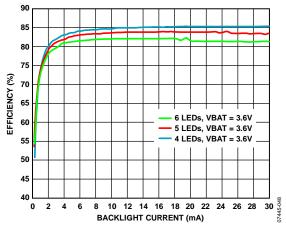

Figure 5. Efficiency vs. Backlight Current (4, 5, and 6 LEDS)

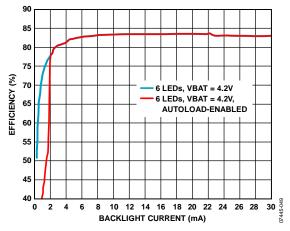

Figure 6. Efficiency vs. Backlight Current (Autoload On/Off)

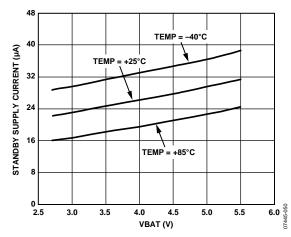

Figure 7. Standby Supply Current vs. VBAT

Figure 8. Typical Auxiliary LED Pin (R3, C3, or ILED), Full-Scale Sink Current vs. Applied Pin Voltage

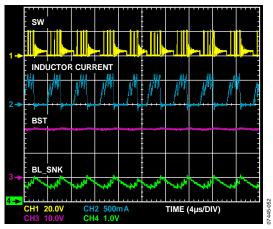

Figure 9. Boost Operation (Backlight = 30 mA)

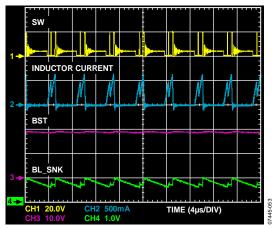

Figure 10. Boost Operation (Backlight = 15 mA)

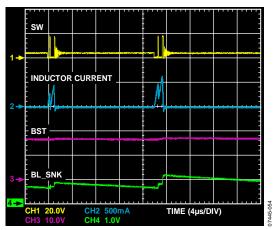

Figure 11. Boost Operation (Backlight = 2 mA)

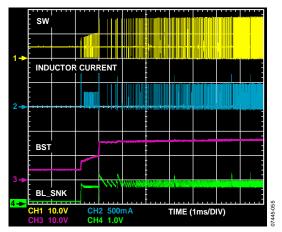

Figure 12. Boost Startup

# THEORY OF OPERATION

Figure 13. Internal Block Diagram

The ADP5520 is a backlight white LED driver with an I/O port expander. It is ideal for cell phone designs and other portable devices, where keypad and/or extended I/O functionality is needed. Programmable fade-in, fade-out, dim, and off timers provide the backlight with flexible control features. Using an external photodiode, the ADP5520 can perform ambient light sensing, and adjust the backlight brightness according to varying lighting conditions.

The I/O port expander has eight configurable GPIO pins. The I/Os can be configured as a keypad matrix, digital inputs, or digital outputs. Additionally, two of the I/Os (R3 and C3) can be configured as current sink lines and, paired with a dedicated sink line (ILED), can be used to drive up to three auxiliary LEDs. Programmable fading is also available for auxiliary LEDs.

Once programmed through its I<sup>2</sup>C-compatible interface, the ADP5520 can run autonomously. An interrupt line ( $\overline{INT}$ ) is available to alert an external microprocessor of the status of its I/Os, keypad presses and releases, ambient light sensor comparator states, and overvoltage conditions.

## **BACKLIGHT DRIVE AND CONTROL**

White LEDs are common in backlighting the displays of modern portable devices such as cell phones. White LEDs require a high forward voltage,  $V_F$ , before they conduct current and emit light. Display panels, depending on their size, can be backlit with single or multiple white LEDs. In panels that require multiple LEDs, the LEDs are commonly connected in a series string to achieve uniform brightness in each LED by passing a common current through all of them. The LED string needs to be biased with a voltage greater than the sum of the  $V_F$  of each LED before it conducts.

The ADP5520 is an asynchronous boost converter capable of driving an LED string with 24.5 V (minimum). For detailed information about the boost device, see the Applications Information section. With sufficient forward voltage created, the ADP5520 controls the current (and thus the brightness) of the LED string via an adjustable internal current sink. An internal state machine, in conjunction with programmable timers, dynamically adjusts the current sink between 0 mA and 30 mA to achieve impressive backlight control features.

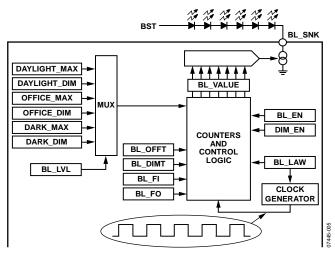

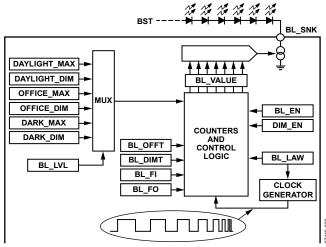

Figure 14. Backlight Brightness Control

### **BACKLIGHT OPERATING LEVELS**

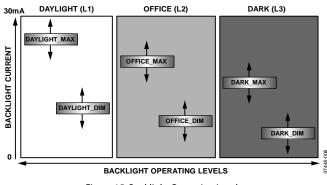

Backlight brightness control can operate in three distinct levels: daylight (L1), office (L2), and dark (L3). The BL\_LVL bits in Register 0x02 control the level in which the backlight operates. The BL\_LVL bits can be changed manually, or if in automatic mode, by the ambient light sensor (see the Ambient Light Sensing section). By default, the backlight operates at daylight level (BL\_LVL = 00), where the maximum brightness is set using Register 0x05 (DAYLIGHT\_MAX). A daylight dim setting can also be set using Register 0x06 (DAYLIGHT\_DIM). When operating at office level (BL\_LVL = 01), the backlight maximum and dim brightness settings are set by Register 0x07 (OFFICE\_MAX) and Register 0x08 (OFFICE\_DIM). When operating at dark level (BL\_LVL = 10), the backlight maximum and dim brightness settings are set by Register 0x09 (DARK\_MAX) and Register 0x0A (DARK\_DIM).

Figure 15. Backlight Operating Levels

### **BACKLIGHT MAXIMUM AND DIM SETTINGS**

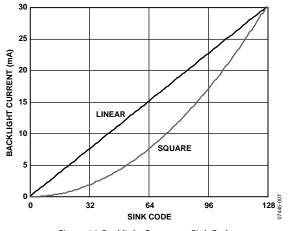

The backlight maximum and dim current settings are determined by a 7-bit code programmed by the user into the registers listed in the Backlight Operating Levels section. This 7-bit resolution allows the user to set the backlight to 1 of 128 different levels between 0 mA and 30 mA. The ADP5520 can implement two distinct algorithms to achieve a linear and a nonlinear relationship between input code and backlight current. The BL\_LAW bits in Register 0x02 are used to swap between algorithms.

By default, the ADP5520 uses a linear algorithm (BL\_LAW = 00), where backlight current increases linearly for a corresponding increase of input code. Backlight current (in mA) is determined by the following equation:

$$Backlight Current = Code \times (Fullscale\_Current/127)$$

(1)

where:

*Code* is the input code programmed by the user. *Fullscale\_Current* is the maximum sink current allowed (typically 30 mA).

The ADP5520 can also implement a nonlinear (square approximation) relationship between input code and backlight current level. In this case (BL\_LAW = 01), the backlight current (in mA) is determined by the following equation:

$$Backlight Current = \left(Code \times \frac{\sqrt{Fullscale \_Current}}{127}\right)^2 \qquad (2)$$

Figure 16 shows the backlight current level vs. input code for both the linear and square law algorithms.

Figure 16. Backlight Current vs. Sink Code

## **BACKLIGHT TURN ON/OFF/DIM**

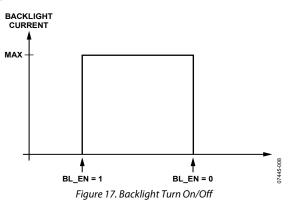

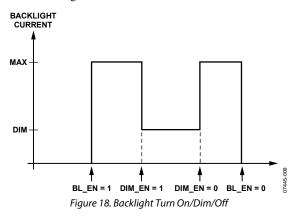

With the device in operating mode  $(\overline{\text{STNBY}} = 1)$ , the backlight can be turned on using the BL\_EN bit in Register 0x00. Before turning on the backlight, choose which level (daylight (L1), office (L2), or dark (L3)) to operate in, and ensure that maximum and dim settings are programmed for that level. The backlight turns on when BL\_EN = 1. The backlight turns off when BL\_EN = 0.

While the backlight is on  $(BL\_EN = 1)$ , the user can make it change to a dim setting by programming DIM\_EN = 1 in Register 0x00. If DIM\_EN = 0, the backlight reverts to its maximum setting.

The maximum and dim settings can be set between 0 mA and 30 mA; therefore, it is possible to program a dim setting that is greater than a maximum setting. For normal expected operation, ensure that the dim setting is programmed to be less than the maximum setting.

It is also possible to activate the backlight automatically when a key press is detected. With the row and column pins configured as a keypad matrix, and the KP\_BL\_EN bit asserted in Register 0x02, the internal state machine asserts BL\_EN and turns on the backlight if a key is pressed. See the I/O Expansion Pins (Keypad Matrix) section for more information on using keypad functionality.

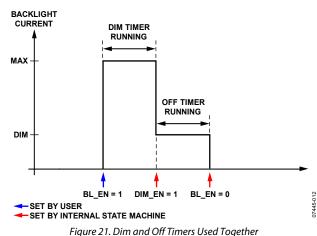

## AUTOMATIC DIM AND TURN OFF TIMERS

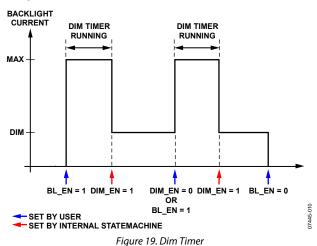

The user can program the backlight to dim automatically by using the BL\_DIMT timer in Register 0x03. The dim timer has 15 settings ranging from 10 sec to 2 min. Program the dim timer before turning on the backlight. If BL\_EN = 1, the backlight turns on to its maximum setting, and the dim timer starts counting. When the dim timer expires, the internal state machine sets DIM\_EN = 1, and the backlight goes to its dim setting.

If the user clears the DIM\_EN bit (or reasserts the BL\_EN bit), the backlight reverts to its maximum setting and the dim timer begins counting again. When the dim timer expires, the internal state machine again sets DIM\_EN = 1, and the backlight goes to its dim setting. Reasserting BL\_EN at any point during the dim timer countdown causes the timer to reset and begin counting again. The backlight can be turned off at any point during the dim timer countdown by clearing BL\_EN.

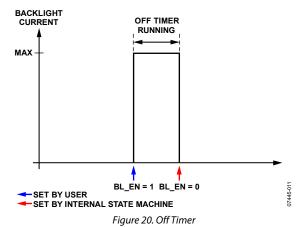

The user can also program the backlight to turn off automatically by using the BL\_OFFT timer in Register 0x03. The off timer has 15 settings ranging from 10 sec to 2 min. Program the off timer before turning on the backlight. If  $BL_EN = 1$ , the backlight turns on to its maximum setting, and the off timer starts counting. When the off timer expires, the internal state machine clears the BL\_EN bit, and the backlight turns off.

Reasserting BL\_EN at any point during the off timer countdown causes the timer to reset and begin counting again. The backlight can be turned off at any point during the off timer countdown by clearing BL\_EN.

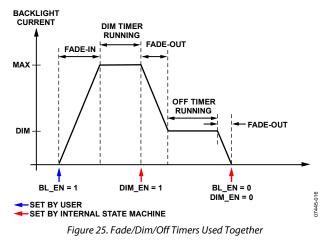

The dim timer and off timer can be used together for sequential maximum-to-dim-to-off functionality. With both the dim and off timers programmed, if BL\_EN is asserted, the backlight turns on to its maximum setting. When the dim timer expires, the backlight changes to its dim setting. When the off timer expires, the backlight turns off.

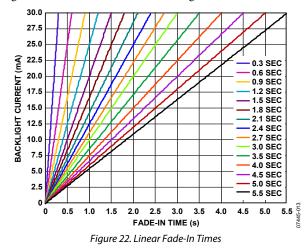

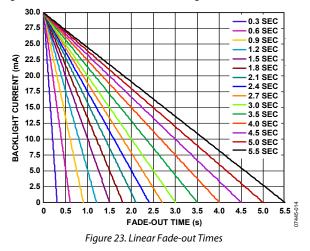

### LINEAR BACKLIGHT FADE IN AND FADE OUT

To counteract the abrupt visual effect of near instant turn-on and turn-off of the backlight, the ADP5520 contains timers to facilitate the smooth fading between off, on, and dim states. By default (BL\_LAW = 00), the ADP5520 implements a fading scheme using the linear backlight code algorithm (see Equation 1).

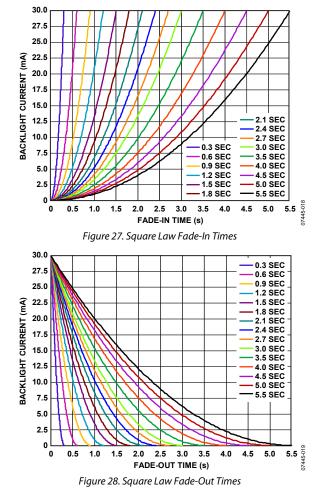

The BL\_FI timer in Register 0x04 can be used for smooth fade-in transitions from low to high backlight settings, such as off-to-dim, off-to-maximum, and dim-to-maximum. The BL\_FI timer can be programmed to one of 15 settings ranging from 0.3 sec to 5.5 sec. Program the BL\_FI timer before asserting BL\_EN.

The time programmed in BL\_FI represents the time it takes the backlight current to go from 0 mA to 30 mA. Fading between intermediate settings is shorter.

The BL\_FO timer in Register 0x04 can be used for smooth fadeout transitions from high to low backlight settings such as maximum-to-dim and dim-to-off. The BL\_FO timer can be programmed to one of 15 settings ranging from 0.3 sec to 5.5 sec. Program the BL\_FO timer before asserting BL\_EN.

The time programmed in BL\_FO represents the time it takes the backlight current to go from 30 mA to 0 mA. Fading between intermediate settings is shorter.

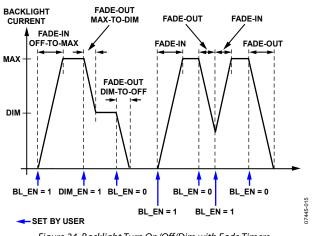

Figure 24 shows the fade timers in use. With BL\_FI and BL\_FO programmed, if BL\_EN is asserted, then the backlight fades in to its maximum setting. If DIM\_EN is asserted, then the backlight fades out to its dim setting. If BL\_EN is cleared, the backlight fades out to off.

Figure 24. Backlight Turn On/Off/Dim with Fade Timers

During any point in a fade-out, if BL\_EN is asserted, then the backlight stops at its current fade-out position and begins fading in.

The fade-in and fade-out timers can be used independently of each other, that is, fade-in can be enabled while fade-out is disabled. The fade timers can also be used with the off and dim timers. Figure 25 shows the fade timers used with the dim and off timers.

## FADE OVERRIDE

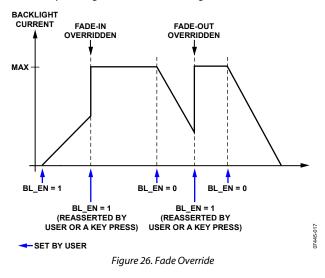

A fade override feature allows the BL\_FI and BL\_FO timers to be overridden if the BL\_EN bit is reasserted (either by the user or due to a key press) during a fade-in or fade-out period, and sets the backlight to its maximum setting. Fade override can be activated by setting the FOVR bit in Register 0x02.

## **ADVANCED FADING (SQUARE)**

Although the default linear fade algorithm gives a smooth increase and decrease in backlight current, the resulting increase and decrease in brightness still appears visually abrupt. For example, for a given fade-in time, the eye can notice an initial increase in brightness as backlight current is increased, but cannot perceive much more of an increase in brightness as backlight current is increased to maximum.

The reason for this is that the eye, like all human senses, perceives changes in light when the brightness of the light source is changed logarithmically (Weber-Fechner law). To achieve a more natural fading experience to the user, the fade timers can be used in conjunction with the square law approximation backlight codes (see Equation 2) by setting BL\_LAW = 01.

## **ADVANCED FADING (CUBIC 1 AND CUBIC 2)**

Two additional advanced techniques are available for fading the backlight brightness levels, Cubic 1 (BL\_LAW = 10) and Cubic 2 (BL\_LAW = 11). Referring to the backlight brightness control block diagram shown in Figure 14, linear and square fading is implemented by ramping the 128 linear/square algorithm codes at a fixed frequency over the duration of a given fade-in/fade-out time.

Cubic fading is implemented by reusing the square algorithm codes, but by ramping them with a clock source whose frequency output increases as the sink current code increases (see Figure 29). Cubic 1 and Cubic 2 differ by having separate frequency vs. code characteristics.

Figure 29. Backlight Brightness Control (Cubic)

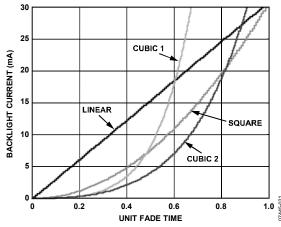

Figure 30 shows a comparison of fade law techniques. Cubic fades complete faster than linear or square fades for a given fade time setting. Cubic 1 completes approximately 30% faster, and Cubic 2 completes approximately 10% faster than an equivalent linear or square fade time.

With four fade laws and 15 fade time settings, users have tremendous flexibility to find the right fade experience for their application.

Figure 30. Fade Law Comparison Over a Unit Fade Time

## AMBIENT LIGHT SENSING

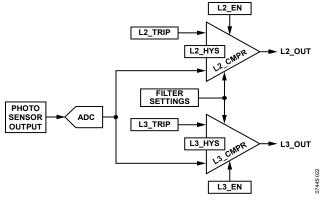

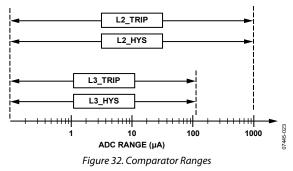

The ADP5520 can be used in conjunction with an external photosensor to detect when ambient light conditions have dropped below programmable set points. An ADC samples the output of the external photosensor. The ADC result is fed into two programmable trip comparators. The ADC has an input range of 0  $\mu$ A to 1000  $\mu$ A (typical).

Figure 31. Ambient Light Sensing and Trip Comparators

The Level 2 (office) light sensor comparator, L2\_CMPR, is used to detect when the photosensor output has dropped below the programmable L2\_TRIP point. If this event occurs, the L2\_OUT status signal is set. L2\_CMPR contains programmable hysteresis, meaning that the photosensor output must rise above L2\_TRIP + L2\_HYS before L2\_OUT is cleared. L2\_CMPR is enabled in Register 0x0C via the L2\_EN bit. The L2\_TRIP and L2\_HYS values of L2\_CMPR can be set between 0  $\mu$ A and 1000  $\mu$ A (typical) in steps of 4  $\mu$ A (typical).

L3\_CMPR is used to detect when the photosensor output has dropped below the programmable L3\_TRIP point. If this event occurs, the L3\_OUT status signal is set. L3\_CMPR contains programmable hysteresis, meaning that the photosensor output must rise above L3\_TRIP + L3\_HYS before L3\_OUT is cleared. L3\_CMPR is enabled in Register 0x0C via the L3\_EN bit. The L3\_TRIP and L3\_HYS values of L3\_CMPR can be set between 0  $\mu$ A and 127  $\mu$ A (typical) in steps of 0.5  $\mu$ A (typical).

The L2\_CMPR and L3\_CMPR comparators can be enabled independently of each other. The ADC and comparators run continuously when L2\_EN and/or L3\_EN are set, during automatic backlight adjustment mode. A single conversion

# Data Sheet

takes 80 ms (typical). Filter times of between 80 ms and 10 sec can be programmed for the comparators before they change state.

It is also possible to use the light sensor comparators in a single shot mode. After the single shot measurement is completed, the internal state machine clears the FORCE\_RD bit.

The interrupt flag, CMPR\_INT, is set in Register 0x00 if either of the L2\_OUT or L3\_OUT status bits change state, meaning interrupts can be generated if ambient light conditions transition between any of the programmed trip points. CMPR\_INT can cause the INT pin to be asserted if the CMPR\_IEN bit is set in Register 0x00. The CMPR\_INT flag can be cleared only by writing a 1 to it.

## AUTOMATIC BACKLIGHT ADJUSTMENT

The ambient light sensor comparators can be used to automatically transition the backlight between one of its three operating levels. To enable this mode, the BL\_AUTO\_ADJ bit is set in Register 0x02.

Once enabled, the internal state machine takes control of the BL\_LVL bits and changes them based on the L2\_OUT and L3\_OUT status bits. The L2\_OUT status bit indicates that ambient light conditions have dropped below the L2\_TRIP point and the backlight must be moved to its office (L2) level. The L3\_OUT status bit indicates that ambient light conditions have dropped below the L3\_TRIP point and the backlight must be moved to its dark (L3) level. Table 6 shows the relationship between backlight operation and the ambient light sensor comparator outputs.

The L3\_OUT status bit has greater priority, so the backlight operates at L3 (dark) even if L2\_OUT is set.

| BL_AUTO_ADJ | L3_OUT | L2_OUT | <b>Backlight Operation</b>                          |

|-------------|--------|--------|-----------------------------------------------------|

| 0           | Х      | Х      | BL_LVL can be manually<br>set by the user           |

| 1           | 0      | 0      | BL_LVL = 00, backlight<br>operates at L1 (daylight) |

| 1           | 0      | 1      | BL_LVL = 01, backlight<br>operates at L2 (office)   |

| 1           | 1      | 0      | BL_LVL = 10, backlight<br>operates at L3 (dark)     |

| 1           | 1      | 1      | BL_LVL = 10, backlight<br>operates at L3 (dark)     |

Table 6. Comparator Output Truth Table (X = Don't Care)

## I/O EXPANSION PINS (GPIOs)

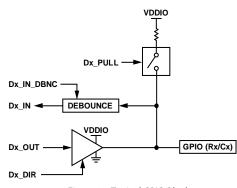

The eight I/O expansion pins (R0, R1, R2, R3, C0, C1, C2, and C3) can be configured as general-purpose digital inputs, digital inputs with pull-up, or digital outputs. Two of the I/O pins (R3 and C3) are LED current sinks by default. To use them as GPIOs, set Bit 4 and Bit 5 in Register 0x11. Register 0x17 to Register 0x1F are used to configure the I/O pins in GPIO mode. Figure 33 shows the typical makeup of a GPIO block, where Rx/Cx represents any one of the eight I/O lines.

Figure 33. Typical GPIO Block

When configured as an output, a digital buffer drives the GPIO Rx and Cx pins to 0 V for a Logic 0 and to the VDDIO rail for a Logic 1. Output data for each I/O is set using Register 0x1A.

Each I/O has a pull-up resistor that can be enabled when used as an input. This can be useful for interfacing to an external signal that has only pull-down capabilities. Pull-ups can be enabled and disabled using Register 0x1F.

Each I/O has a debounce circuit that effectively filters out glitches and pulses less than 75  $\mu$ s (typical) to prevent false triggering when configured as an input. By default, debounce is enabled but can be disabled using Register 0x1E.

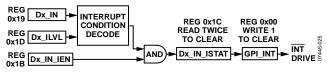

I/Os configured as inputs store the digital state sensed at each pin in Register 0x19. Interrupts can be generated by digital inputs if enabled in Register 0x1B. The input interrupt level can be selected using Register 0x1D. Interrupts generated are stored in Register 0x1C. The master GPI\_INT bit is set if any interrupt bits are set in Register 0x1C, and the INT pin is asserted.

To deassert the  $\overline{INT}$  pin and clear the GPI\_INT bit, the 0x1C register must be cleared by reading it twice (assuming the interrupt condition has gone away), and then a 1 must be written to the GPI\_INT bit in Register 0x00. Figure 34 shows the interrupt generation scheme, where Dx represents any one of the eight digital input lines.

Figure 34. GPIO Interrupt generation

## I/O EXPANSION PINS (KEYPAD MATRIX)

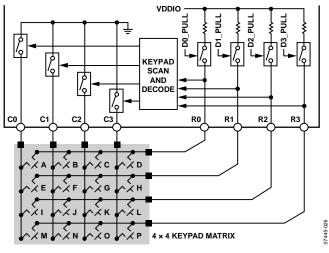

The eight I/O expansion pins (R0, R1, R2, R3, C0, C1, C2, and C3) can be configured to decode a keypad matrix, consisting of up to 16 switches ( $4 \times 4$  matrix). See the Example Circuits section for other possible matrix configurations.

Two of the I/O pins (R3 and C3) are LED current sinks by default. To use them as keypad decoders, set Bit 4 and Bit 5 in Register 0x11. The R0, R1, R2, and R3 I/O pins make up the rows of the keypad matrix. The C0, C1, C2, and C3 I/O pins make up the columns of the keypad matrix.

To configure the device for key scanning and decoding, the R0, R1, R2, and R3 pull-ups must be enabled in Register 0x1F. Key scanning and decoding is then enabled by programming the row and column bits in Register 0x17. The row pull-ups must be enabled before enabling key scanning.

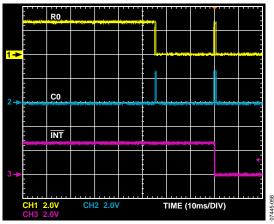

Figure 35 shows the row and column pins connected to a typical  $4 \times 4$ , 16-switch keypad matrix. When key scanning is idle, the row pins are pulled high and the column pins are pulled low. The key scanner operates by checking if the row pins are low. If the A button in the matrix is pressed, the switch connects R0 to C0. The key scan circuit senses that the R0 pin has been pulled low and begins a key scan cycle. To prevent glitches or narrow press times registering as valid key presses, the key scanner requires the key to be pressed for two scan cycles. The key scanner has a sampling period of 25 ms, so the key must be pressed and held for at least 25 ms to register as being pressed. If the key is continuously pressed, the key scanner continues to sample every 25 ms.

Figure 35. Keypad Decode Configuration

Figure 36. Key Press(R0,C0)

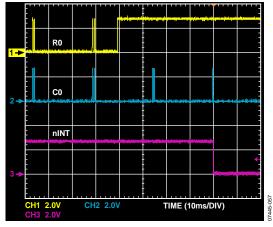

If the A button is released, the switch opens the connection between R0 and C0, and R0 is pulled up high. The key scanner requires that the key be released for two scan cycles. Because the release of a key is not necessarily in sync with the key scanning sampling period, it may take between 25 ms and 50 ms for a key to register as being released. Once the key is registered as being released, the key scanner returns to idle mode.

Figure 37. Key Press (R0, C0)

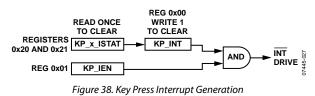

Key press/release status and interrupt information is recorded in Register 0x20 through Register 0x25. When a key is pressed, an interrupt is generated and stored. Key press interrupts for A through H are stored in Register 0x20, and key press interrupts for I through P are stored in Register 0x21. The master KP\_INT flag is set if any interrupt bits are set in Register 0x20 or Register 0x21. The INT pin is asserted if KP\_INT is set and if KP\_IEN is enabled in Register 0x01.

To deassert the  $\overline{INT}$  pin and clear the KP\_INT flag, Register 0x20 and Register 0x21 must be cleared by reading them once, and then a 1 must be written to the KP\_INT bit in Register 0x00. Figure 38 shows the interrupt generation scheme, where KP\_x\_ISTAT represents any one of the 16 key press interrupt status bits.

It is possible to clear key press interrupts (KP\_INT = 1) and deassert  $\overline{INT}$  while a key is still pressed.

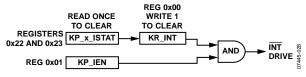

When a key is released, an interrupt is also generated and stored. Key release interrupts for A through H are stored in Register 0x22, and key release interrupts for I through P are stored in Register 0x23. The master KR\_INT flag is set if any interrupt bits are set in Register 0x22 or Register 0x23. The INT pin is asserted if KR\_INT is set and if KR\_IEN is enabled in Register 0x01.

To deassert the  $\overline{\rm INT}$  pin and clear the KR\_INT flag, Register 0x22 and Register 0x23 must be cleared by reading them once, and then a 1 must be written to the KR\_INT bit in Register 0x00. Figure 39 shows the interrupt generation scheme, where KR\_x\_ISTAT represents any one of the 16-key release interrupt status bits.

Figure 39. Key Release Interrupt Generation

The backlight can be programmed to turn on as a consequence of a key press, using the KP\_BL\_EN bit in Register 0x02. To enable this feature, observe the following sequence:

- 1. Enable the row pull-ups using Register 0x1F.

- 2. Enable key scanning on rows and columns using Register 0x17.

- 3. Enable backlight turn-on due to key press by setting KP\_BL\_EN in Register 0x02.

- 4. Set device to operating mode  $(\overline{\text{STNBY}} = 1)$  in Register 0x00.

When a key is pressed, the backlight turns on. If the off timer is programmed, the backlight turns off, or the user can turn off the backlight by clearing BL\_EN.

If the user wants the backlight to turn on again with a subsequent key press, the KP\_INT and KR\_INT bits in Register 0x00 must be cleared.

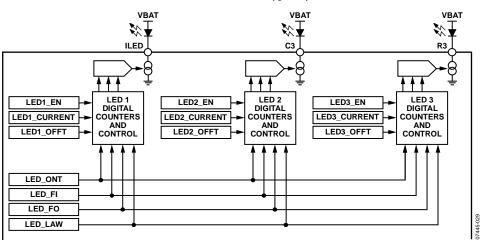

# I/O EXPANSION PINS AND ILED PIN (AUXILIARY LED CURRENT SINKS)

The ILED pin and two of the I/O expansion pins (R3 and C3) can be used as auxiliary LED current sinks. Each LED current sink is programmable up to 14 mA (typical) and can be independently turned on and off.

The ILED pin is the current sink for LED 1. Its sink current can be set using LED1\_CURRENT in Register 0x14. The LED 1 sink can be enabled with LED1\_EN in Register 0x11.

The C3 pin is the current sink for LED 2. Its sink current can be set using LED2\_CURRENT in Register 0x15. The LED 2 sink can be enabled with LED2\_EN in Register 0x11.

The R3 pin is the current sink for LED 3. Its sink current can be set using LED3\_CURRENT in Register 0x16. The LED 3 sink can be enabled with LED3\_EN in Register 0x11.

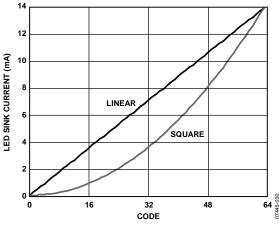

The LEDx\_CURRENT registers are six bits wide, allowing the user to set the LED sink current to one of 64 different levels between 0 mA and 14 mA. The ADP5520 can implement two distinct algorithms, to achieve a linear and a nonlinear relationship between input code and sink current.

By default, the ADP5520 uses a linear algorithm (LED\_LAW = 0), where the LED sink current increases linearly for a corresponding increase of input code. LED sink current (in milliamps) is determined by the following equation:

$LED Sink Current = Code \times (Fullscale_Current/63)$ (3)

where:

*Code* is the input code programmed by the user. *Fullscale\_Current* is the maximum sink current allowed (typically 14 mA).

Figure 40. LED Current Sinks

# ADP5520

The ADP5520 can also implement a nonlinear (square approximation) relationship between input code and LED sink current level. In this case (LED\_LAW = 1), the LED sink current (in milliamps) is determined by the following equation:

$$LED Sink Current = \left(Code \times \frac{\sqrt{Fullscale \_Current}}{63}\right)^2 \qquad (4)$$

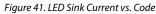

Figure 41 shows the auxiliary LED sink current levels vs. input code for both the linear and square law algorithms.

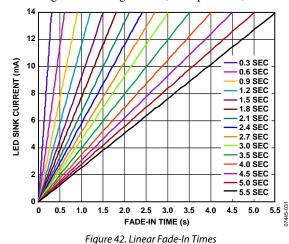

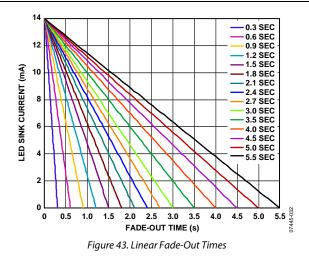

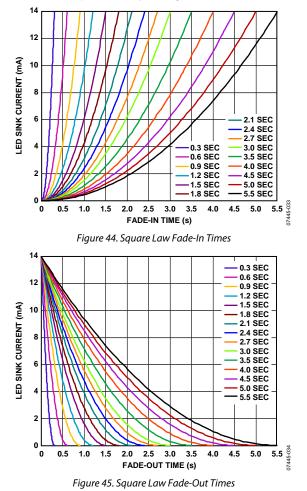

Similar to the backlight current sink, the ADP5520 contains timers to facilitate the smooth fading between off and on states of the LED current sinks. All three LED sinks share a common fade-in (LED\_FI) timer as well as a common fade-out (LED\_FO) timer. The fade-in and fade-out timers are located in Register 0x13, and can be programmed to one of 15 settings ranging from 0.3 sec to 5.5 sec. Fade-in times represent the time it takes to fade from 0 mA to 14 mA. Fade-out times represent the time it takes to fade from 14 mA to 0 mA. Fading between intermediate settings is shorter. Program the fade timers before asserting LEDx\_EN.

By default (LED\_LAW = 0), the ADP5520 implements a fading scheme using the linear algorithm (see Equation 3).

To achieve a more natural fading experience to the eye, the fade timers can be used in conjunction with the square law approximation codes (see Equation 4) by setting  $LED_LAW = 1$ .

The LED current sinks have additional timers to facilitate blinking functions. A shared on timer (LED\_ONT) used in conjunction with three off timers (LED1\_OFFT, LED2\_OFFT, and LED3\_OFFT) allow the LED current sinks to be configured in various blinking modes. The on timer can be set to four different settings: 0.2 sec, 0.6 sec, 0.8 sec, and 1.2 sec. The off timers have four different settings: disabled, 0.6 sec, 0.8 sec, and 1.2 sec. Blink mode is activated by setting the off timers to any setting other than disabled.

Program all fade, on, and off timers before enabling any of the LED current sinks. If LEDx is on during a blink cycle and LEDx\_EN is cleared, it turns off (or fades to off if fade-out is enabled). If LEDx is off during a blink cycle and LEDx\_EN is cleared, then it stays off.

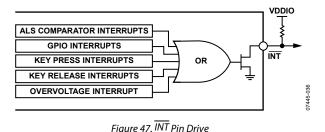

## INTERRUPT OUTPUT (INT)

The ADP5520 can generate interrupts to an external processor via its interrupt output,  $\overline{\text{INT}}$ .  $\overline{\text{INT}}$  is an active low open-drain pin that must be pulled up to VDDIO.  $\overline{\text{INT}}$  can be asserted by one of several internal blocks, as shown in Figure 47.

## RESET INPUT (RST)

The ADP5520 can be restored to a power-on reset state if the  $\overline{\text{RST}}$  pin is held low.  $\overline{\text{RST}}$  contains a debounce circuit, so the pin must be held low for greater than 75 µs (typical) before a reset occurs.

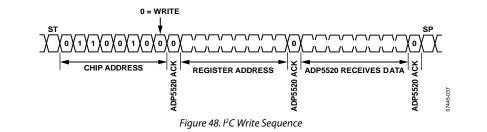

# **COMMUNICATION INTERFACE**

Communication to the ADP5520 is done via its I<sup>2</sup>C-compatible serial interface. Figure 48 shows a typical write sequence for programming an internal register.

- 1. The cycle begins with a start condition, followed by the chip write address (0x64).

- 2. The ADP5520 acknowledges the chip write address byte by pulling the data line low.

- 3. The address of the register to which data is to be written is sent next.

- 4. The ADP5520 acknowledges the register address byte by pulling the data line low.

- 5. The data byte to be written is sent next.

- 6. The ADP5520 acknowledges the data byte by pulling the data line low.

- 7. A stop condition completes the sequence.

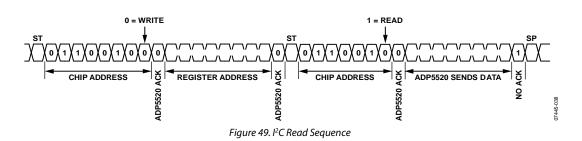

Figure 49 shows a typical read sequence for reading back an internal register.

- 1. The cycle begins with a start condition, followed by the chip write address (0x64).

- 2. The ADP5520 acknowledges the chip write address byte by pulling the data line low.

- 3. The address of the register from which data is to be read is sent next.

- 4. The ADP5520 acknowledges the register address byte by pulling the data line low.

- 5. The cycle continues with a repeat start, followed by the chip read address (0x65).

- 6. The ADP5520 acknowledges the chip read address byte by pulling the data line low.

- 7. The ADP5520 places the contents of the previously addressed register on the bus for readback.

- 8. There is a no acknowledge following the readback data byte, and the cycle is completed with a stop condition.

# **REGISTER MAP**

All registers are 0 on reset. Unused bits are read as 0.

## Table 7.

| Register<br>Address | Register Name    | Register Description                                                                                         |

|---------------------|------------------|--------------------------------------------------------------------------------------------------------------|

| 0x00                | MODE_STATUS      | Sets device operating mode. Contains enables for backlight on/dim. Contains top-level interrupt status bits. |

| 0x01                | INTERRUPT_ENABLE | Contains enables for allowing interrupts to assert INT.                                                      |

| 0x02                | BL_CONTROL       | Sets parameters relating to backlight control.                                                               |

| 0x03                | BL_TIME          | Contains backlight off and dim timers.                                                                       |

| 0x04                | BL_FADE          | Contains backlight fade-in and fade-out timers.                                                              |

| 0x05                | DAYLIGHT_MAX     | Sets daylight (L1) maximum current.                                                                          |

| 0x06                | DAYLIGHT_DIM     | Sets daylight (L1) dim current.                                                                              |

| 0x07                | OFFICE_MAX       | Sets office (L2) maximum current.                                                                            |

| 0x08                | OFFICE_DIM       | Sets office (L2) dim current.                                                                                |

| 0x09                | DARK_MAX         | Sets dark (L3) maximum current.                                                                              |

| 0x0A                | DARK_DIM         | Sets dark (L3) dim current.                                                                                  |

| 0x0B                | BL_VALUE         | Read-only register of what the backlight is presently set to.                                                |

| 0x0C                | ALS_CMPR_CFG     | Sets enables and filters for ambient light sensor comparators. Contains comparator output status bits.       |

| 0x0D                | L2_TRIP          | Sets the light sensor comparator (L2_CMPR) threshold point.                                                  |

| 0x0E                | L2_HYS           | Sets the light sensor comparator (L2_CMPR hysteresis.                                                        |

| 0x0F                | L3_TRIP          | Sets the light sensor comparator (L3_CMPR) threshold point.                                                  |

| 0x10                | L3_HYS           | Sets the light sensor comparator (L3_CMPR) hysteresis.                                                       |

| 0x11                | LED_CONTROL      | Contains enables and configuration for the three auxiliary LED current sinks.                                |

| 0x12                | LED_TIME         | Contains the on and off timers for the three auxiliary LED current sinks.                                    |

| 0x13                | LED_FADE         | Contains the fade-in and fade-out timers for the three auxiliary LED current sinks.                          |

| 0x14                | LED1_CURRENT     | Sets the LED 1 (ILED) sink current.                                                                          |

| 0x15                | LED2_CURRENT     | Sets the LED 2 (C3) sink current.                                                                            |

| 0x16                | LED3_CURRENT     | Sets the LED 3 (R3) sink current.                                                                            |

| 0x17                | GPIO_CFG_1       | Configuration for I/O pins. (GPIOs or keypad matrix)                                                         |

| 0x18                | GPIO_CFG_2       | Configuration for I/O pins. (GPIO direction, input or output)                                                |

| 0x19                | GPIO_IN          | Read-only register. Reflects the logic state of GPIO inputs.                                                 |

| 0x1A                | GPIO_OUT         | Sets GPIO output logic drive level.                                                                          |

| 0x1B                | GPIO_INT_EN      | GPIO input interrupt enable.                                                                                 |

| 0x1C                | GPIO_INT_STAT    | GPIO input interrupt status.                                                                                 |

| 0x1D                | GPIO_INT_LVL     | Configures the GPIO input interrupt level that causes an interrupt (active high or low).                     |

| 0x1E                | GPIO_DEBOUNCE    | GPIO input debounce enable/disable.                                                                          |

| 0x1F                | GPIO_PULLUP      | GPIO pull-up enable/disable.                                                                                 |

| 0x20                | KP_INT_STAT_1    | Read only register. Contains interrupt status information for key presses on Key A through Key H.            |

| 0x21                | KP_INT_STAT_2    | Read-only register. Contains interrupt status information for key presses on Key I through Key P.            |

| 0x22                | KR_INT_STAT_1    | Read-only register. Contains interrupt status information for key releases on Key A through Key H.           |

| 0x23                | KR_INT_STAT_2    | Read-only register. Contains interrupt status information for key releases on Key I through Key P.           |

| 0x24                | KEY_STAT_1       | Read-only register. Reflects the present state of Key A through Key H.                                       |

| 0x25                | KEY_STAT_2       | Read-only register. Reflects the present state of Key I through Key P.                                       |

# **DETAILED REGISTER DESCRIPTIONS**

If one of the interrupt bits in Table 8 is cleared and there is a pending interrupt,  $\overline{INT}$  deasserts for 50 µs and reasserts, but the status of the pending interrupt stays set.

| Bit | Mnemonic | R/W | Description                                                                                                                                                                                                                                                                                                              |

|-----|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | STNBY    | R/W | $0 =$ device is in standby mode. If $1.8 V \le VDDIO \le 3.3 V$ , then $I^2C$ , GPIO, and key scanning functions are available.                                                                                                                                                                                          |

|     |          |     | 1 = device is in operating mode. Additional functions, such as backlight driver, auxiliary LED sinks, and ambient light sensor functions, can be enabled.                                                                                                                                                                |

| 6   | BL_EN    | R/W | 0 = backlight driver is disabled.                                                                                                                                                                                                                                                                                        |

|     |          |     | 1 = backlight driver is enabled.                                                                                                                                                                                                                                                                                         |

| 5   | DIM_EN   |     | 0 = dim mode is disabled.                                                                                                                                                                                                                                                                                                |

|     |          |     | 1 = dim mode is enabled. Dim mode can be enabled in two ways. One is by manually setting this bit, in which case the backlight stays at a dim level until this bit is manually cleared. The second method is by setting the BL_DIMT timer, in which case an internal state machine sets this bit when the timer expires. |

| 4   | OVP_INT  | R/W | 0 = no overvoltage protection (OVP) condition.                                                                                                                                                                                                                                                                           |

|     |          |     | 1 = OVP condition detected. Once set, this bit can be cleared by writing a 1 to it.                                                                                                                                                                                                                                      |

| 3   | CMPR_INT |     | 0 = no ambient light sensor comparators have triggered.                                                                                                                                                                                                                                                                  |

|     |          |     | 1 = One of the ambient light sensor comparators has triggered. Once set, this bit can be cleared by writing a 1 to it.                                                                                                                                                                                                   |

| 2   | GPI_INT  |     | 0 = no GPIO input interrupt detected.                                                                                                                                                                                                                                                                                    |

|     |          |     | 1 = GPIO input interrupt condition has occurred. To clear this interrupt bit, the GPIO interrupt status (Register 0x1C) must be cleared first. Then this bit can be cleared by writing a 1 to it.                                                                                                                        |

| 1   | KR_INT   |     | 0 = no key release interrupt present.                                                                                                                                                                                                                                                                                    |

|     |          |     | 1 = key release detected. To clear this interrupt bit, Key Release Interrupt Status 1<br>(Register 0x22) and Key Release Interrupt Status 2 (Register 0x23) must be cleared first.<br>Then this bit can be cleared by writing a 1 to it.                                                                                 |

| 0   | KP_INT   |     | 0 = no key press interrupt present.                                                                                                                                                                                                                                                                                      |

|     |          |     | 1 = key press detected. To clear this interrupt bit, Key Press Interrupt Status 1 (Register 0x20) and Key Press Interrupt Status 2 (Register 0x21) must be cleared first. Then this bit can be cleared by writing a 1 to it.                                                                                             |

Table 8. Register 0x00, Device Mode and Status (MODE\_STATUS)

## Table 9. Register 0x01, Interrupt Enable (INTERRUPT\_ENABLE)

| Bit   | Mnemonic   | R/W | Description                                                                                                                             |

|-------|------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------|

| [7:5] |            |     | Unused.                                                                                                                                 |

| 4     | AUTO_LD_EN | R/W | 0 = autoload disabled.                                                                                                                  |

|       |            |     | 1 = autoload enabled. A 1 mA dummy load turns on when the backlight code is less than 8 (linear law) or less than Code 32 (square law). |

| 3     | CMPR_IEN   | R/W | 0 = ambient light sensor comparators interrupt disabled.                                                                                |

|       |            |     | 1 = ambient light sensor comparators interrupt enabled.                                                                                 |

| 2     | OVP_IEN    | R/W | 0 = OVP interrupt disabled.                                                                                                             |

|       |            |     | 1 = OVP interrupt enabled.                                                                                                              |

| 1     | KR_IEN     | R/W | 0 = key release interrupt disabled.                                                                                                     |

|       |            |     | 1 = key release interrupt enabled.                                                                                                      |

| 0     | KP_IEN     | R/W | 0 = key press interrupt disabled.                                                                                                       |

|       |            |     | 1 = key press interrupt enabled.                                                                                                        |

| Bit   | Mnemonic    | R/W | Description                                                                                                                                                                       |

|-------|-------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6] | BL_LVL      | R/W | Brightness level control for the backlight.                                                                                                                                       |

|       |             |     | 00 = daylight (L1).                                                                                                                                                               |

|       |             |     | 01 = office (L2).                                                                                                                                                                 |

|       |             |     | 10 = dark (L3).                                                                                                                                                                   |

|       |             |     | See the description for the BL_AUTO_ADJ bit.                                                                                                                                      |

| [5:4] | BL_LAW      | R/W | Backlight fade-on/fade-off transfer characteristic.                                                                                                                               |

|       |             |     | 00 = linear.                                                                                                                                                                      |

|       |             |     | 01 = square.                                                                                                                                                                      |

|       |             |     | 10 = Cubic 1.                                                                                                                                                                     |

|       |             |     | 11 = Cubic 2.                                                                                                                                                                     |

| 3     | BL_AUTO_ADJ | R/W | 0 = ambient light sensor comparators have no effect on the backlight operating level. The user can manually adjust backlight operating level using the BL_LVL bits.               |

|       |             |     | 1 = ambient light sensor comparators automatically adjust the backlight operating level. The internal state machine takes control of the BL_LVL bits.                             |

| 2     | OVP_EN      | R/W | 0 = backlight ramp-down during OVP disabled.                                                                                                                                      |

|       |             |     | 1 = backlight ramp-down during OVP enabled.                                                                                                                                       |

| 1     | FOVR        | R/W | 0 = backlight fade override disabled.                                                                                                                                             |

|       |             |     | 1 = backlight fade override enabled.                                                                                                                                              |

| 0     | KP_BL_EN    | R/W | 0 = key press has no effect on the backlight.                                                                                                                                     |

|       |             |     | 1 = key press causes internal state machine to assert BL_EN and turn on the backlight. If this function is used, assert this bit before asserting $\overline{\text{STNBY}} = 1$ . |

## Table 10. Register 0x02, Backlight Control (BL\_CONTROL)

## Table 11. Register 0x03, Backlight Off and Dim Timers (BL\_TIME)

| Bit   | Mnemonic | R/W | Description                                               |

|-------|----------|-----|-----------------------------------------------------------|

| [7:4] | BL_OFFT  | R/W | Backlight off timer (set this timer before BL_EN is set). |

|       |          |     | 0000 = timer disabled.                                    |

|       |          |     | 0001 = 10 sec.                                            |

|       |          |     | 0010 = 15 sec.                                            |

|       |          |     | 0011 = 20 sec.                                            |

|       |          |     | 0100 = 25 sec.                                            |

|       |          |     | 0101 = 30 sec.                                            |

|       |          |     | 0110 = 35 sec.                                            |

|       |          |     | 0111 = 40 sec.                                            |

|       |          |     | 1000 = 50 sec.                                            |

|       |          |     | 1001 = 60 sec.                                            |

|       |          |     | 1010 = 70 sec.                                            |

|       |          |     | 1011 = 80 sec.                                            |

|       |          |     | 1100 = 90 sec.                                            |

|       |          |     | 1101 = 100 sec.                                           |

|       |          |     | 1110 = 110 sec.                                           |

|       |          |     | 1111 = 120 sec.                                           |

| [3:0] | BL_DIMT  | R/W | Backlight dim timer (set this timer before BL_EN is set). |

|       |          |     | 0000 = timer disabled.                                    |

|       |          |     | 0001 = 10 sec.                                            |

|       |          |     | 0010 = 15 sec.                                            |

|       |          |     | 0011 = 20 sec.                                            |