# Low-Power, High-Performance Audio DAC with Class H Headphone Drivers

### **System Features**

- Stereo headphone (HP) output with 114-dB dynamic range

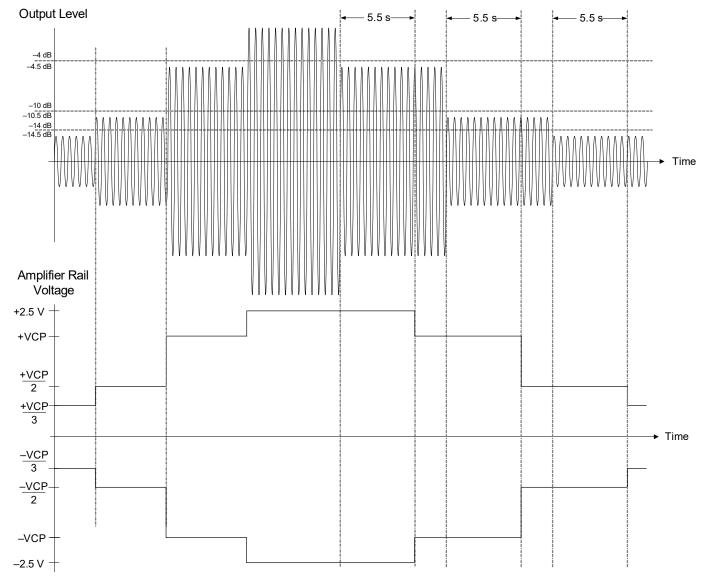

- Class H HP amplifier with four-level automatic or manual supply adjust

- -98-dB THD+N into 30  $\Omega$  with 10-mW output power

- 2 x 35 mW output power into 30  $\Omega$  with 0.018% THD+N

- Load detection

- Headphone load detection of 15 or 30  $\Omega$

- Line-level load (3 kΩ) with capacitance detection

- · Headphone insertion/removal detection with WAKE

- Audio serial port (ASP)

- I<sup>2</sup>S (two channels) or TDM (up to four channels)

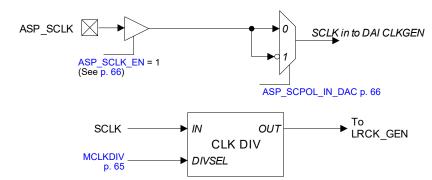

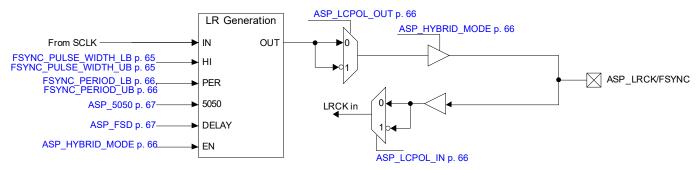

- Slave or Hybrid-Master Mode (bit-clock slave and LRCK/FSYNC derived from bit clock)

- Supports up to 32-bit audio

- Sample rate support for 8 to 192 kHz

- I<sup>2</sup>C control with interrupt output

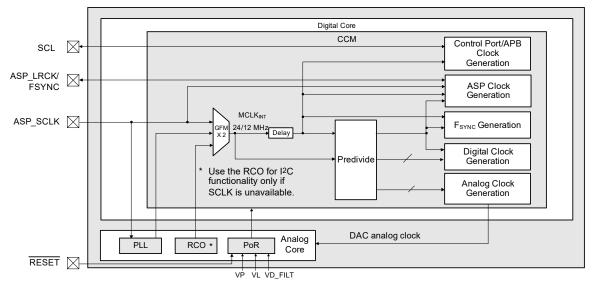

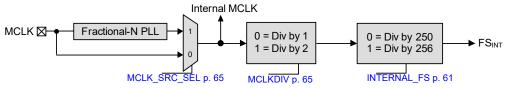

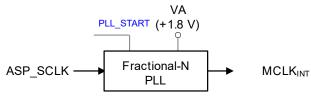

- · Integrated fractional-N PLL

- Increases system-clock flexibility for audio processing

- Reference clock sourced from I<sup>2</sup>S/TDM bit clock

- Bypassable SRCs for maximum flexibility

- · Attenuation, mute, and volume controls for each output

- · Integrated power management

- Digital core operates from either an external 1.2-V supply or LDO from a 1.8-V supply.

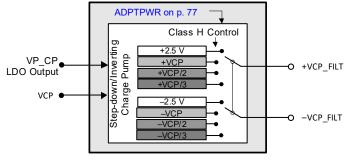

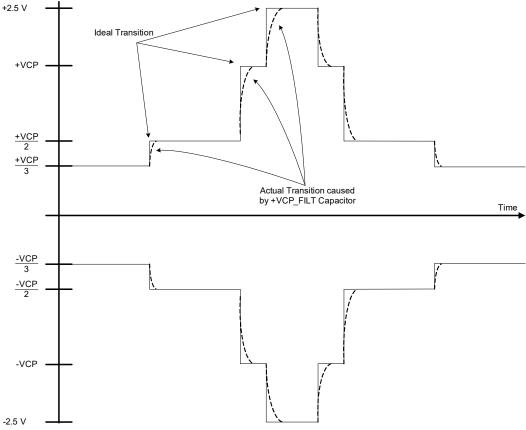

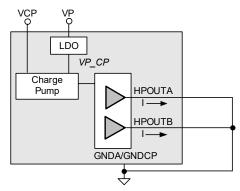

- Step-down charge pump improves HP efficiency

- Independent peripheral power-down controls

- Standby operation from VP with all other supplies powered off

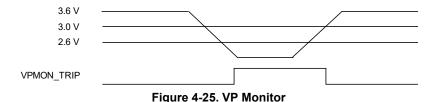

- VP monitor to detect and report brownout conditions

- Low-impedance switching suppresses ground-noise

### **Applications**

- · Ultrabooks, tablets, and smartphones

- · Digital headsets

### **General Description**

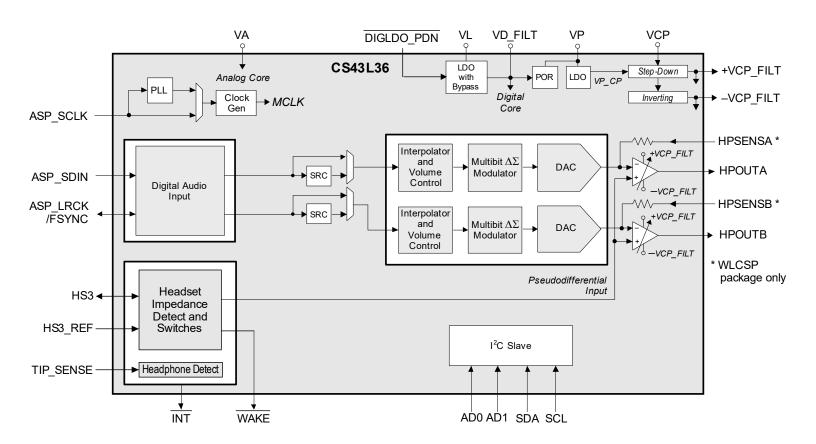

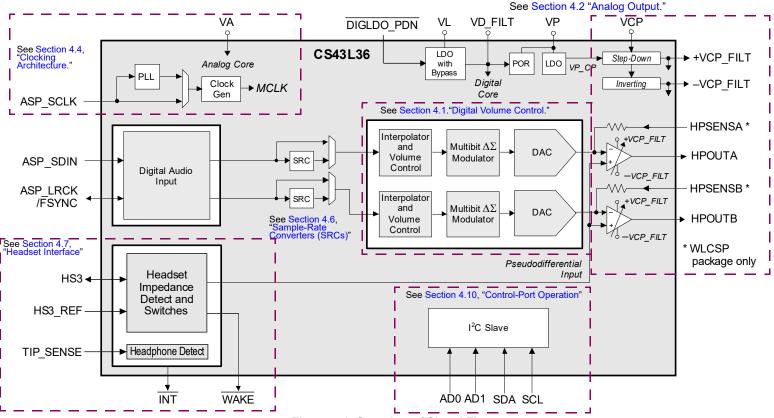

The CS43L36 is a low-power, high dynamic-range, stereo audio DAC with integrated I<sup>2</sup>S/I<sup>2</sup>C/TDM interfaces designed for portable applications. The CS43L36 features support for up to 32-bit audio inputs and includes bypassable SRCs.

The bypassable fractional-N PLL sourced from the ASP SCLK allows for maximum flexibility in any system.

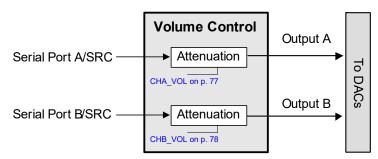

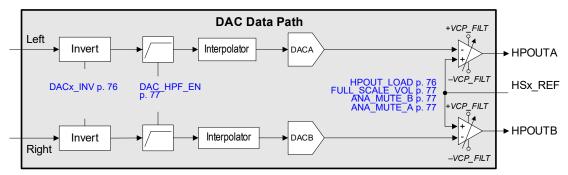

There is independent attenuation on each input along with volume adjustment and mute control.

The CS43L36 is available in 49-ball WLCSP package and a 40-pin QFN package, both supporting an extended commercial operational temperature range of –40°C to +85°C.

## **Table of Contents**

| 1 | Pin Assignments and Descriptions                                                                                                 | 4    |

|---|----------------------------------------------------------------------------------------------------------------------------------|------|

|   | 1.1 WLCSP Pin Out (Through-Package View)                                                                                         | 4    |

|   | 1.2 QFN Pin Out (Through-Package View)                                                                                           | 5    |

|   | 1.3 Pin Descriptions                                                                                                             | 5    |

| _ | 1.3 Pin Descriptions                                                                                                             | [    |

| 2 | Typical Connections                                                                                                              | . 10 |

|   | Typical Connections                                                                                                              | . 11 |

| 3 | Characteristics and Specifications Table 3-1. Parameter Definitions                                                              | . 12 |

|   | Table 3-1. Parameter Definitions                                                                                                 | 12   |

|   | Table 3-2. Recommended Operating Conditions                                                                                      | 12   |

|   | Table 3-3. Absolute Maximum Ratings                                                                                              | 12   |

|   | Table 3-4. Combined DAC Digital, On-Chip Analog, and HPOUTx                                                                      |      |

|   | Filter Characteristics Table 3-5. DAC High-Pass Filter (HPF) Characteristics Table 3-6. SDIN to HPOUTx with SRC-Enabled Datapath | 13   |

|   | Table 3-5. DAC High-Pass Filter (HPF) Characteristics                                                                            | 13   |

|   | Table 3-6. SDIN to HPOUTx with SRC-Enabled Datapath                                                                              |      |

|   | Characteristics                                                                                                                  | 13   |

|   | Table 3-7. Serial Data In-to-HPOUTx Characteristics                                                                              | 14   |

|   | Table 3-8. DC Characteristics                                                                                                    | 15   |

|   | Table 3-9. Power-Supply Rejection Ratio (PSRR) Characteristics                                                                   | 15   |

|   | Table 3-10. Power Consumption                                                                                                    | 16   |

|   | Table 3-11. Register Field Settings                                                                                              | 16   |

|   | Table 3-12. Digital Audio Interface Timing Characteristics                                                                       | 17   |

|   | Table 3-13. I <sup>2</sup> C Slave Port Characteristics                                                                          | 17   |

|   | Table 3-14 Digital Interface Specifications and Characteristics                                                                  | 19   |

| 4 | Functional Description                                                                                                           | . 20 |

|   | Functional Description                                                                                                           | . 21 |

|   | 4.2 Analog Output                                                                                                                | . 22 |

|   | 4.2 Analog Output                                                                                                                | . 23 |

|   | 4.4 Clocking Architecture 4.5 Audio Serial Port (ASP) 4.6 Sample-Rate Converters (SRCs)                                          | . 28 |

|   | 4.5 Audio Serial Port (ASP)                                                                                                      | . 34 |

|   | 4.6 Sample-Rate Converters (SRCs)                                                                                                | . 40 |

|   | 4./ Headset Interface                                                                                                            | . 41 |

|   | 4.8 Plug Presence Detect                                                                                                         | . 41 |

|   | 4.9 Power-Supply Considerations                                                                                                  | . 43 |

|   | 4.10 Control-Port Operation                                                                                                      | . 45 |

|   | 4.11 Reset                                                                                                                       | . 47 |

|   | 4.12 Interrupts                                                                                                                  | . 47 |

|   | 4.13 FILT+ Operation                                                                                                             | . 48 |

| 5 | 4.13 FILT+ Operation System Applications                                                                                         | . 49 |

|   | 5.1 Power-Up Sequence                                                                                                            | . 49 |

|   | 5.2 Power-Down Sequence                                                                                                          | . 51 |

|   | 5.3 Page 0x30 Read Sequence                                                                                                      | . 52 |

|   | 5.4 PLL Clocking                                                                                                                 | . 52 |

|   | 5.4 PLĽ Clocking                                                                                                                 | . 52 |

| 6 | Register Quick Reference                                                                                                         | . 53 |

|   | 6.1 Global Registers                                                                                                             | . 53 |

|   | 6.2 Power-Down and Headset-Detect Registers                                                                                      | . 54 |

|   | 6.3 Clocking Registers                                                                                                           | . 55 |

|   | 6.4 Interrupt Registers                                                                                                          | . 55 |

|   | 6.5 Fractional-N PLL Registers                                                                                                   | 56   |

|   | 6.6 HP Load Detect Registers 6.7 Headset Interface Registers                                                                     | . 57 |

|   | 6.7 Headset Interface Registers                                                                                                  | . 57 |

|   | 6.8 DAC Registers                                                                                                                | . 58 |

|   | 6.8 DAC Registers                                                                                                                | . 58 |

|   | 6.10 Class H Registers                                                                                                           | . 58 |

|   | 6.11 Mixer Volume Registers                                                                                                      | . 58 |

|   | 6.12 AudioPort Interface Registers                                                                                               | . 59 |

|   | 6.13 SRC Registers                                                                                                               | . 59 |

|   | 6.14 Serial Port Receive Registers                                                                                               | 59   |

|   | 6.15 ID Registers                                                                                                                | . 60 |

| 7 | Register Descriptions                                                                                                            | . 60 |

| - | 7.1 Global Registers                                                                                                             |      |

|   | 7.2 Power Down and Headset Detects                                                                                               | . 63 |

|   | 7.3 Clocking Registers                                                                                                           |      |

|   | 7.4 Interrupt Registers                                                                                                          |      |

|   | 7.5 Fractional-N PLL Registers                                                                                                   | . 72 |

|   | 7.6 HP Load-Detect Registers                                                                                                     | . 74 |

|   | 7.7 Headset Interface Registers                                                                                                  | . 74 |

|   | 7.8 DAC Control Registers                                                                                                        | . 76 |

|   | 7.9 HP Control Register                                                                                                          | . 77 |

|   | 7.10 Class H Register                                                                                                            | . 77 |

|   | 7.11 Volume Control                                                                                                              |      |

|   | 7.12 AudioPort Interface Registers                                                                                               | . 78 |

|   | 7.13 SRC Registers                                                                                                               |      |

|   | - 3                                                                                                                              |      |

| 7.14 Serial Port Receive Registers | / |

|------------------------------------|---|

| 7.15 ID Registers                  | 8 |

| PCB Layout Considerations          | 8 |

| 8.1 Power Supply                   | 8 |

| 8.2 Grounding                      |   |

| 8.3 QFN Thermal Pad                |   |

| Plots                              |   |

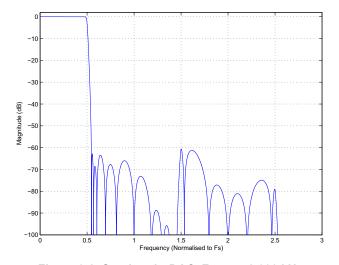

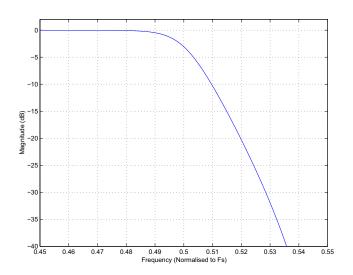

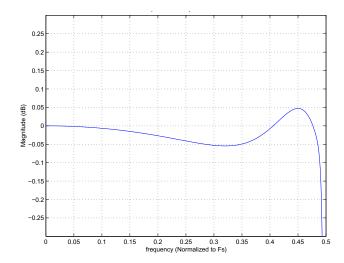

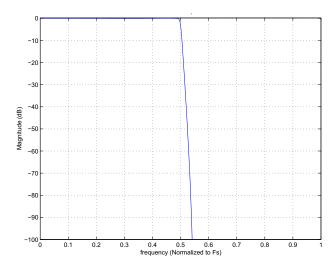

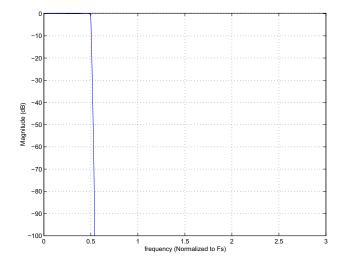

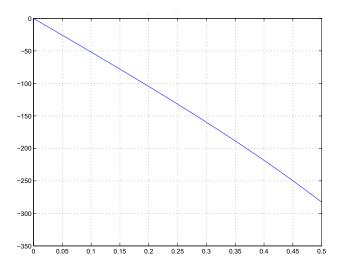

| 9.1 Digital Filter Response        | 8 |

| 0 Package Dimensions               |   |

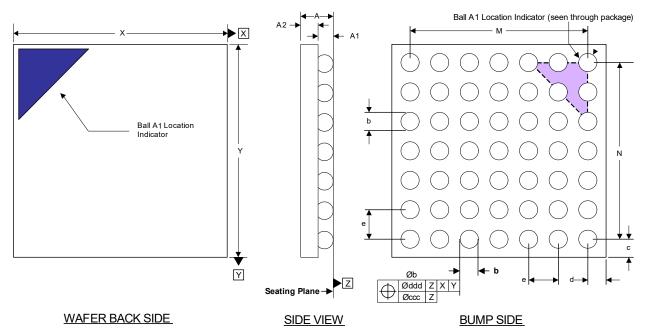

| 10.1 WLCSP Package Dimensions      |   |

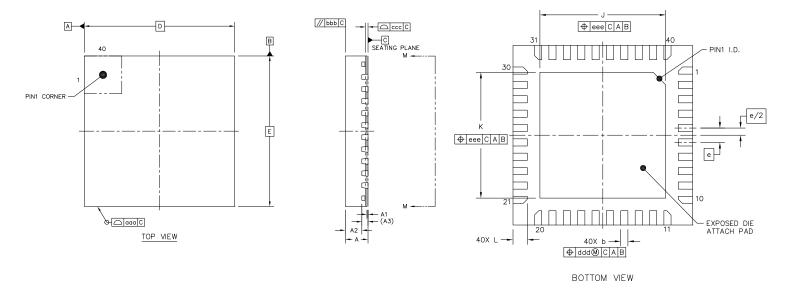

| 10.2 QFN Package Dimensions        |   |

| 1 Thermal Characteristics          |   |

| 2 Ordering Information             |   |

| 3 References                       |   |

| 4 Revision History                 |   |

|                                    |   |

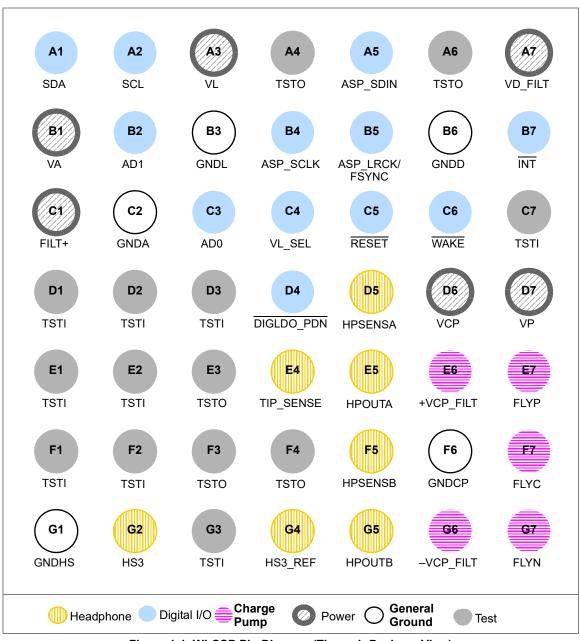

## 1 Pin Assignments and Descriptions

This section shows pin assignments and describes pin functions.

## 1.1 WLCSP Pin Out (Through-Package View)

Figure 1-1. WLCSP Pin Diagram (Through-Package View)

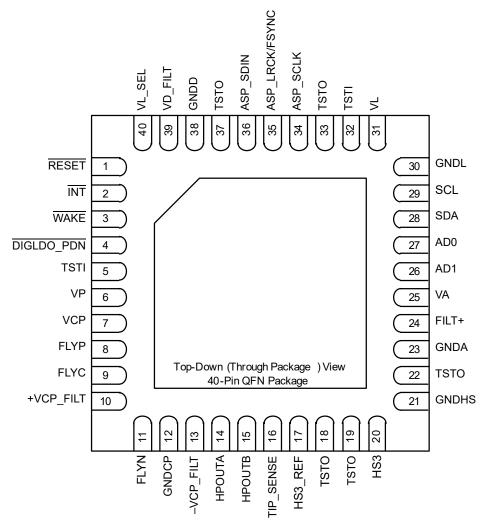

## 1.2 QFN Pin Out (Through-Package View)

Figure 1-2. QFN Pin Diagram

# 1.3 Pin Descriptions

Table 1-1. Pin Descriptions

| Pin Name           | CSP<br>Pin # | QFN<br>Pin # | Power<br>Supply | I/O | Pin Description                                                                                                               | Internal<br>Connection <sup>1</sup> | Driver | Receiver    | State at<br>Reset |

|--------------------|--------------|--------------|-----------------|-----|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------|-------------|-------------------|

|                    |              |              |                 |     | Headphone 베                                                                                                                   |                                     |        |             |                   |

| HS3_REF            | G4           | 17           | VP              | I   | Headset Connection Reference. Input to pseudodifferential HP output reference                                                 | _                                   | _      | _           | Input             |

| HS3                | G2           | 20           | VP              | I   | Headset Connections. Input to headset and mic-button detection functions                                                      | _                                   | _      | <del></del> | Input             |

| HPOUTA<br>HPOUTB   | E5<br>G5     | 14<br>15     | ±VCP_<br>FILT   | 0   | <b>Headphone Audio Output.</b> Ground-centered audio output.                                                                  | _                                   | _      | <del></del> | _                 |

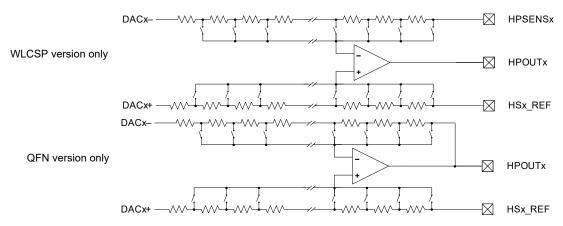

| HPSENSA<br>HPSENSB | D5<br>F5     | _            | ±VCP_<br>FILT   | I   | <b>Headphone Audio Sense Input.</b> Audio sense input. WLCSP package only                                                     | _                                   | _      | <del></del> | Input             |

| TIP_SENSE          | E4           | 16           | VP              | I   | <b>Tip Sense.</b> Output can be set to wake the system. Independently configurable to be debounced on plug and unplug events. | _                                   | Hi-Z   | _           | _                 |

Table 1-1. Pin Descriptions (Cont.)

| Pin Name           | CSP<br>Pin # | QFN<br>Pin # | Power<br>Supply         | I/O | Pin Description                                                                                                                                                    | Internal<br>Connection <sup>1</sup> | Driver                                | Receiver                       | State at<br>Reset |

|--------------------|--------------|--------------|-------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------------------|--------------------------------|-------------------|

|                    |              |              |                         |     | Digital I/O                                                                                                                                                        |                                     |                                       |                                |                   |

| AD0<br>AD1         | C3<br>B2     | 27<br>26     | VL                      | ı   | I <sup>2</sup> C Address Input. Address pins for I <sup>2</sup> C Instance ID [1:0] input.                                                                         | _                                   | _                                     | Hysteresis<br>on CMOS<br>input | Input             |

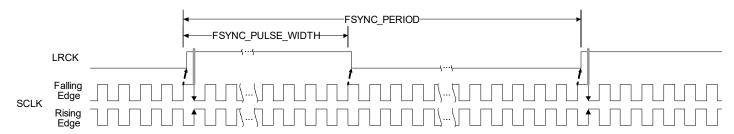

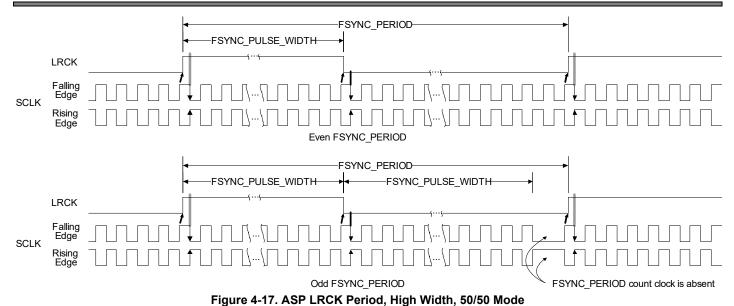

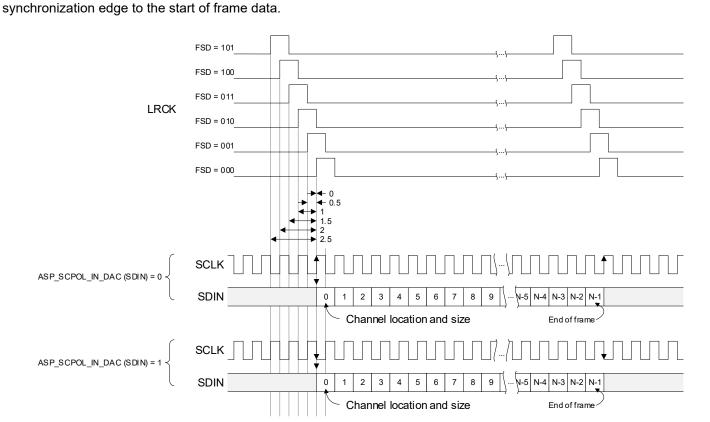

| ASP_LRCK/<br>FSYNC | B5           | 35           | VL                      | I/O | ASP Left/Right Clock or Frame Sync. Left or right word select, or frame start sync for the ASP interface.                                                          | _                                   | CMOS<br>output                        | Hysteresis<br>on CMOS<br>input | Input             |

| ASP_SCLK           | В4           | 34           | VL                      | I   | <b>ASP/ Serial Data Clock.</b> Serial data-shift clock for the ASP interface in I <sup>2</sup> S/TDM Mode. Source clock used for internal master clock generation. | _                                   | _                                     | Hysteresis<br>on CMOS<br>input | Input             |

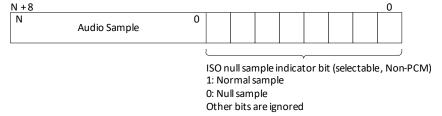

| ASP_SDIN           | A5           | 36           | VL                      | I/O | <b>ASP Serial Data Input.</b> Serial data input and output in serial data input for the ASP interface in I <sup>2</sup> S/TDM mode.                                | _                                   | CMOS<br>output                        | Hysteresis<br>on CMOS<br>input | Input             |

| DIGLDO_PDN         | D4           | 4            | VP                      | I   | <b>Digital LDO Power Down.</b> Digital core logic LDO power down.                                                                                                  | _                                   | _                                     | Hysteresis<br>on CMOS<br>input | Input             |

| ĪNT                | В7           | 2            | VP                      | 0   | Interrupt output. Programmable, open-drain, active-low programmable interrupt output.                                                                              | _                                   | CMOS<br>open-drain<br>output          | <u> </u>                       | Output            |

| RESET              | C5           | 1            | VP                      | I   | Reset. Hardware reset.                                                                                                                                             | _                                   | _                                     | Hysteresis<br>on CMOS<br>input | Input             |

| SCL                | A2           | 29           | VL                      | I   | I <sup>2</sup> C Clock. Clock input for the I <sup>2</sup> C interface.                                                                                            | _                                   | _                                     | Hysteresis<br>on CMOS<br>input | Input             |

| SDA                | A1           | 28           | VL                      | I/O | I2C Input/Output. I2C input and output.                                                                                                                            | _                                   | CMOS<br>open-drain<br>output          | Hysteresis<br>on CMOS<br>input | Input             |

| VL_SEL             | C4           | 40           | VP                      | I   | VL Supply Voltage Select. Select for VL power supply voltage level. Connect to VP for 1.8-V VL supply, connect to GNDD for 1.2-V VL supply                         | _                                   | _                                     | Hysteresis<br>on CMOS<br>input | Input             |

| WAKE               | C6           | 3            | VP                      | 0   | Wake up. Programmable, open-drain, active-low output. This outputs the state of the Mic S0 or HP wake detect.                                                      | _                                   | Hi-Z,<br>CMOS<br>open-drain<br>output | <u>-</u>                       | Output            |

|                    |              |              |                         |     | Charge Pump 🛑                                                                                                                                                      |                                     |                                       |                                |                   |

| -VCP_FILT          | G6           | 13           | VCP/<br>VP <sup>2</sup> | 0   | <b>Inverting Charge Pump Filter Connection.</b> Power supply for the inverting charge pump that provides the negative rail for the HP amplifier.                   | _                                   | _                                     | _                              | _                 |

| +VCP_FILT          | E6           | 10           | VCP/<br>VP <sup>2</sup> | 0   | Step Down Charge Pump Filter Connection.  Power supply for the step down charge pump that provides the positive rail for the HP amplifier.                         | _                                   | _                                     |                                | _                 |

| FLYC               | F7           | 9            | VCP/<br>VP <sup>2</sup> | 0   | Charge Pump Cap Common Node. Common positive node for the HP amplifiers' step-down and inverting charge pumps' flying capacitors.                                  | _                                   | _                                     |                                | _                 |

| FLYN               | G7           | 11           | VCP/<br>VP <sup>2</sup> | 0   | <b>Charge Pump Cap Negative Node.</b> Negative node for the inverting charge pump's flying capacitor.                                                              | _                                   | _                                     |                                |                   |

| FLYP               | E7           | 8            | VCP/<br>VP <sup>2</sup> | 0   | Charge Pump Cap Positive Node. Positive node for HP amps' step-down charge pump's flying capacitor.                                                                |                                     | _                                     | _                              | _                 |

|                    |              |              |                         |     | Power                                                                                                                                                              |                                     |                                       |                                |                   |

| FILT+              | C1           | 24           | VA                      | I   | Positive Voltage Reference. Positive reference voltage for internal sampling circuits.                                                                             | _                                   | _                                     | _                              | _                 |

| VA                 | B1           | 25           | N/A                     | I   | <b>Analog Power Supply.</b> Power supply for the internal analog section.                                                                                          | _                                   |                                       | _                              |                   |

| VCP                | D6           | 7            | N/A                     | I   | <b>Charge Pump Power.</b> Power supply for the internal HP amplifiers charge pump.                                                                                 | _                                   | _                                     | _                              | _                 |

| VD_FILT            | A7           | 39           | N/A                     | Ι   | <b>1.2-V Digital Core Power Supply.</b> Power supply for internal digital logic.                                                                                   | _                                   | _                                     | _                              | _                 |

| VL                 | A3           | 31           | N/A                     | Ī   | I/O Power Supply. Power supply for external interface and internal digital logic.                                                                                  | _                                   | _                                     | _                              | _                 |

| Table 1-1. | Pin | <b>Descriptions</b> | (Cont.) |

|------------|-----|---------------------|---------|

|------------|-----|---------------------|---------|

| Pin Name | CSP<br>Pin #                 | QFN<br>Pin # | Power<br>Supply | I/O | Pin Description                                                                         | Internal<br>Connection <sup>1</sup> | Driver | Receiver | State at Reset |

|----------|------------------------------|--------------|-----------------|-----|-----------------------------------------------------------------------------------------|-------------------------------------|--------|----------|----------------|

| VP       | D7                           | 6            | N/A             | I   | <b>High Voltage Interface Supply.</b> Power supply for high voltage interface.          | _                                   | _      | _        | _              |

|          |                              |              |                 |     | Ground 🔘                                                                                |                                     |        |          |                |

| GNDA     | C2                           | 23           | N/A             | I   | <b>Analog Ground.</b> Ground reference for the internal analog section.                 | _                                   | _      | _        | _              |

| GNDL     | В3                           | 30           | N/A             | I   | <b>Digital Ground.</b> Ground reference for interface section.                          | _                                   | _      | _        | _              |

| GNDHS    | G1                           | 21           | N/A             | I   | <b>Headset Ground.</b> Ground reference for the internal analog section.                | _                                   | _      | _        | _              |

| GNDCP    | F6                           | 12           | N/A             | I   | <b>Charge Pump Ground.</b> Ground reference for the internal HP amplifiers charge pump. | _                                   | _      | _        | _              |

| GNDD     | В6                           | 38           | N/A             | I   | <b>Digital Ground.</b> Ground reference for the internal digital circuits.              | _                                   | _      | _        | _              |

|          |                              |              |                 |     | Test                                                                                    |                                     |        |          |                |

| TSTI     | C7                           | 5            | N/A             | ı   | Test input. Connect to GNDD                                                             | _                                   | _      | _        | _              |

| TSTI     | D3                           | 32           | VL              | ı   | Test input. Connect to GNDD.                                                            | _                                   | _      |          | _              |

| TSTI     | D1, E1,<br>E2, F1,<br>F2, G3 | _            | VP              | I   | Test input. Connect to GNDA.                                                            | _                                   | _      | _        | _              |

| TSTI     | D2                           | _            | VA              | I   | Test input. Connect to GNDA.                                                            | _                                   | _      | _        | _              |

| TSTO     | A4, A6                       | 33,37        | VL              | 0   | Test output. No connection                                                              |                                     | _      | _        | _              |

| TSTO     | E3, F3,<br>F4                | 18,19,<br>22 | VP              | 0   | Test output. No connection                                                              | _                                   | _      | _        | _              |

<sup>1.</sup> There are no internal connections for the CS43L36.

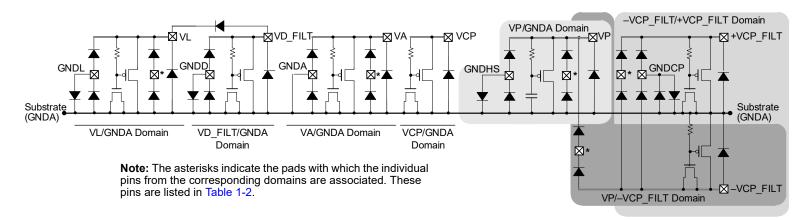

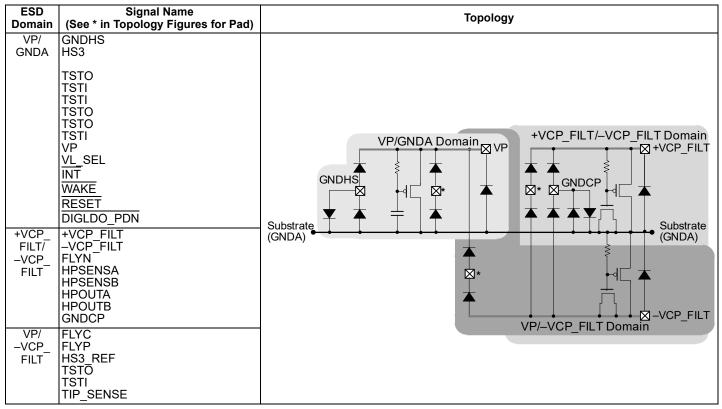

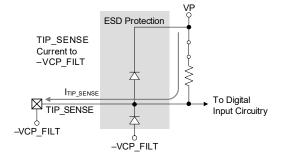

## 1.4 Electrostatic Discharge (ESD) Protection Circuitry

ESD-sensitive device. The CS43L36 is manufactured on a CMOS process. Therefore, it is generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken while handling and storing this device. This device is qualified to current JEDEC ESD standards.

Fig. 1-3 provides a composite view of the ESD domains showing the ESD protection paths between each pad and the substrate (GNDA) and the interrelations between some domains. Note that this figure represents the structure for the internal protection devices and that additional protections can be implemented as part of the integration into the board.

Figure 1-3. Composite ESD Topology

<sup>2.</sup> The power supply is determined by ADPTPWR setting (see Section 7.10.1). VP is used if ADPTPWR = 001 (VP\_CP Mode) or when necessary for ADPTPWR = 111 (Adapt-to-Signal Mode).

Table 1-2 shows the individual ESD domains and lists the pins associated with each domain.

Table 1-2. ESD Domains

| ESD          | Signal Name                                                                              | Topology              |

|--------------|------------------------------------------------------------------------------------------|-----------------------|

| Domain       | (See * in Topology Figures for Pad)                                                      |                       |

|              | AD0 AD1 ASP_LRCK/FSYNC GNDL SCL SDA TSTO TSTO TSTI ASP_SCLK ASP_SCLK ASP_SDIN VD_FILT VL | Substrate (GNDA)      |

| GNDA         | VD_FILT<br>GNDD<br>TSTI                                                                  | Substrate (GNDA)      |

| VA/<br>GNDA  | FILT+<br>GNDA<br>TSTI<br>VA                                                              | GNDA Substrate (GNDA) |

| VCP/<br>GNDA | VCP                                                                                      | Substrate (GNDA)      |

#### Table 1-2. ESD Domains (Cont.)

<sup>1.</sup> See Section 5.5 for additional information regarding VD\_FILT and VL.

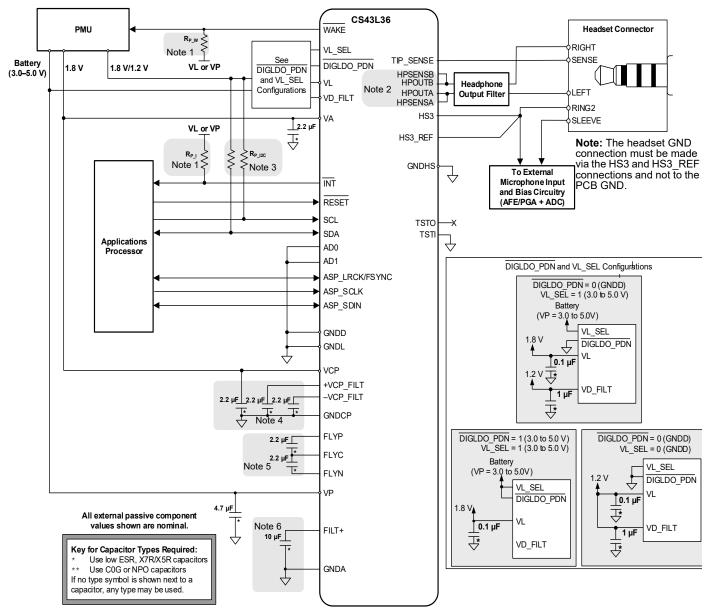

## 2 Typical Connections

Figure 2-1. Typical Connection Diagram

#### Notes:

- 1. R<sub>P I</sub> and R<sub>P W</sub> values can be determined by the  $\overline{\text{INT}}$  and  $\overline{\text{WAKE}}$  pin specifications in Table 3-14.

- 2. HPSENSA and HPSENSB are supported only on the WLCSP package.

- 3. RP I2C values can be determined by the I2C pull-up resistance specification in Table 3-13.

- 4. The headphone amplifier's output power and distortion ratings use the nominal capacitances shown. Larger capacitance reduces ripple on the internal amplifiers' supplies and, in turn, reduces distortion at high-output power levels. Smaller capacitance may not reduce ripple enough to achieve output power and distortion ratings. Because actual values of typical X7R/X5R ceramic capacitors deviate from nominal values by a percentage specified in the manufacturer's data sheet, capacitors must be selected for minimum output power and maximum distortion required. Higher value capacitors than those shown may be used, however lower value capacitors must not (values can vary from the nominal by ±20%). See Section 2.1.2 for additional details.

- 5. Series resistance in the path of the power supplies must be avoided. Any voltage drop on VCP directly affects the negative charge-pump supply (–VCP\_FILT) and clips the audio output.

- 6. Lowering capacitance below the value shown affects PSRR, THD+N performance, and interchannel isolation and intermodulation.

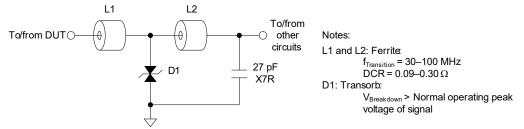

## 2.1 Electromagnetic Compatibility (EMC) Circuitry

The circuit in Fig. 2-2 may be applied to signals not local to the CS43L36 (i.e., that traverse significant distances) for EMC.

Figure 2-2. Optional EMC Circuit

### 2.1.1 Low-Profile Charge-Pump Capacitors

In the typical connection for analog mics (Fig. 2-1), the recommended capacitor values for the charge-pump circuitry are 2.2 µF, rated as X7R/X5R or better. The following low-profile versions of these capacitors are suitable for the application:

- Description: 2.2 µF ±20%, 6.3 V, X5R, 0201

- Manufacturer, Part Number: Murata, GRM033R60J225ME47, nominal height = 0.3 mm

- Manufacturer, Part Number: AVX, 02016D225MAT2A, nominal height = 0.33 mm

**Note:** Although the 0201 capacitors described are suitable, larger capacitors such as 0402 or larger may provide acceptable performance.

### 2.1.2 Ceramic Capacitor Derating

Note 4 in Fig. 2-1 highlights that ceramic capacitor derating factors can significantly affect in-circuit capacitance values and, in turn, CS43L36 performance. Under typical conditions, numerous types and brands of large-value ceramic capacitors in small packages exhibit effective capacitances well below their ±20% tolerance, with some being derated by as much as –50%. These same capacitors, when tested by a multimeter, read much closer to their rated value. A similar derating effect has not been observed with tantalum capacitors.

The derating observed varied with manufacturer and physical size: Larger capacitors performed better, as did ones from Kemet Electronics Corp. and TDK Corp. of any size. This derating effect is described in data sheets and in applications notes from capacitor manufacturers. For instance, as DC and AC voltages are varied from the standard test points (applied DC and AC voltages for standard test points versus PSRR test are 0 and 1 V<sub>RMS</sub> @ 1 kHz versus 0.9 V and ~1 mV<sub>RMS</sub> @ 20 Hz–20 kHz), it is documented that the capacitances vary significantly.

## 3 Characteristics and Specifications

Table 3-1 defines parameters as they are characterized in this section.

#### **Table 3-1. Parameter Definitions**

| Parameter                       | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 | The ratio of the rms value of the signal to the rms sum of all other spectral components over the specified bandwidth. A signal-to-noise ratio measurement over the specified bandwidth made with a –60 dB signal; 60 dB is added to resulting measurement to refer the measurement to full scale. This technique ensures that distortion components are below the noise level and do not affect the measurement. This measurement technique has been accepted by the Audio Engineering Society, AES17–1991, and the Electronic Industries Association of Japan, EIAJ CP–307. Dynamic range is expressed in decibel units. |

| Idle channel noise              | The rms value of the signal with no input applied (properly back-terminated analog input, digital zero, or zero modulation input). Measured over the specified bandwidth.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Interchannel isolation          | A measure of cross talk between the left and right channel pairs. Interchannel isolation is measured for each channel at the converter's output with no signal to the input under test and a full-scale signal applied to the other channel. Interchannel isolation is expressed in decibel units.                                                                                                                                                                                                                                                                                                                         |

| Load resistance and capacitance | The recommended minimum resistance and maximum capacitance required for the internal op-amp's stability and signal integrity. The load capacitance effectively moves the band-limiting pole of the amp in the output stage. Increasing load capacitance beyond the recommended value can cause the internal op-amp to become unstable.                                                                                                                                                                                                                                                                                     |

| Offset error                    | The deviation of the midscale transition (111111 to 000000) from the ideal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Output offset voltage           | The DC offset voltage present at the amplifier's output when its input signal is in a mute state. The offset exists due to CMOS process limitations and is proportional to analog volume settings. When measuring the offset out the headphone amplifier, the headphone amplifier is ON.                                                                                                                                                                                                                                                                                                                                   |

|                                 | The ratio of the rms sum of distortion and noise spectral components across the specified bandwidth (typically 20 Hz–20 kHz) relative to the rms value of the signal. THD+N is measured at –1 and –20 dBFS for the analog input and at 0 and –20 dB for the analog output, as suggested in AES17–1991 Annex A. THD+N is expressed in decibel units.                                                                                                                                                                                                                                                                        |

#### **Table 3-2. Recommended Operating Conditions**

Test conditions: GNDA = GNDL = GNDCP = 0 V; voltages are with respect to ground.

|                                                | Parameters                                                             | Symbol                                          | Minimum                               | Maximum                           | Unit             |

|------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------|---------------------------------------|-----------------------------------|------------------|

| DC power supply                                | Charge pump                                                            | VCP                                             | 1.66                                  | 1.94                              | V                |

|                                                | LDO regulator for digital <sup>1</sup> DIGLDO_PDN = 0 and VL_SEL = 0   | VD_FILT                                         | 1.10                                  | 1.30                              | V                |

|                                                | Serial interface control port DIGLDO_PDN = 0 and VL_SEL = 0 VL_SEL = 1 | VL<br>VL                                        | 1.10<br>1.66                          | 1.30<br>1.94                      | V                |

|                                                | Analog                                                                 | VA                                              | 1.66                                  | 1.94                              | V                |

|                                                | Battery supply                                                         | VP                                              | 2.50 <sup>2</sup>                     | 5.25                              | V                |

| External voltag<br>applied to pin <sup>3</sup> |                                                                        | V <sub>INHI</sub><br>Vvcpf<br>Vvl<br>Vva<br>Vvp | -VCP_FILT<br>-VCP_FILT<br>0<br>0<br>0 | VP<br>+VCP_FILT<br>VL<br>VA<br>VP | V<br>V<br>V<br>V |

| Ambient tempe                                  | erature                                                                | T <sub>A</sub>                                  | -40                                   | +85                               | °C               |

**Note:** The device is fully functional and meets all parametric specifications in this section if operated within the specified conditions. Functionality and parametric performance is not guaranteed or implied outside of these limits. Operation outside of these limits may adversely affect device reliability.

- 1.If DIGLDO PDN is deasserted, no external voltage must be applied to VD FILT.

- 2.Although device operation is guaranteed down to 2.5 V, device performance is guaranteed only down to 3.0 V. The following are affected when VP < 3.0 V: charge pump LDO, TIP\_SENSE threshold.

- 3. The maximum over/undervoltage is limited by the input current.

- 4. Table 1-1 lists the power supply domain in which each CS43L36 pin resides.

- 5.±VCP\_FILT is specified in Table 3-8.

#### Table 3-3. Absolute Maximum Ratings

Test conditions: GNDA = GNDL = GNDCP = 0 V; voltages are with respect to ground.

| Parameters                                                 | Symbol                                                                                            | Minimum                                                                                               | Maximum                                                                                                                  | Unit                                                                                                                                                    |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Charge pump, LDO, serial/control, analog (see Section 4.9) | VL, VA, VCP                                                                                       | -0.3                                                                                                  | 2.33                                                                                                                     | V                                                                                                                                                       |

| Digital core                                               | VD_FILT                                                                                           | -0.3                                                                                                  | 1.55                                                                                                                     | V                                                                                                                                                       |

| Battery                                                    | VP                                                                                                | -0.3                                                                                                  | 6.3                                                                                                                      | V                                                                                                                                                       |

|                                                            | I <sub>in</sub>                                                                                   | _                                                                                                     | ±10                                                                                                                      | mA                                                                                                                                                      |

| Ambient operating temperature (power applied)              |                                                                                                   |                                                                                                       |                                                                                                                          | °C                                                                                                                                                      |

|                                                            | T <sub>stg</sub>                                                                                  | -65                                                                                                   | +150                                                                                                                     | °C                                                                                                                                                      |

|                                                            | Charge pump, LDO, serial/control, analog (see Section 4.9) Digital core Battery e (power applied) | Charge pump, LDO, serial/control, analog (see Section 4.9) Digital core Battery  In  In  In  Ta  Tstg | Charge pump, LDO, serial/control, analog (see Section 4.9) VL, VA, VCP UD-FILT VP US | Charge pump, LDO, serial/control, analog (see Section 4.9)  Digital core Battery  VD_FILT  -0.3  1.55  -0.3  1in  ±10  e (power applied)  TA  -50  +115 |

**Caution:** Stresses beyond "Absolute Maximum Ratings" levels may cause permanent damage to the device. These levels are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Table 3-2, "Recommended Operating Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

1. Any pin except supply pins. Transient currents of up to ±100 mA on analog input pins do not cause SCR latch-up.

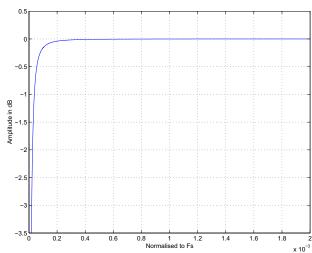

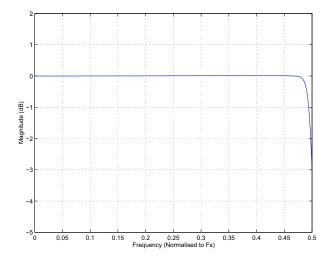

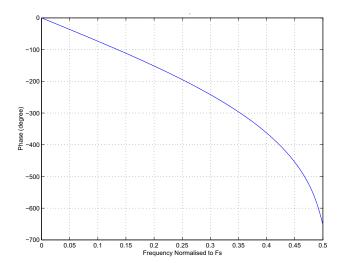

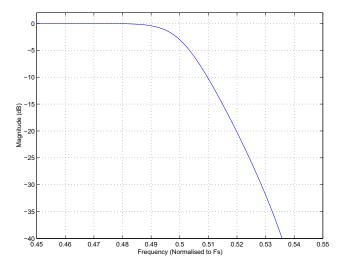

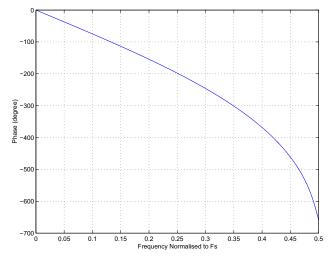

#### Table 3-4. Combined DAC Digital, On-Chip Analog, and HPOUTx Filter Characteristics

Test conditions (unless specified otherwise): T<sub>A</sub> = +25°C; MCLK = 12 MHz, MCLK\_SRC\_SEL = 0, Fs<sub>INT</sub> = 48 kHz; path is internal routing engine to HPOUTx, analog and digital gains are all set to 0 dB; HPF disabled.

| Parameter <sup>1</sup>                                                                                                                          | Minimum | Typical                | Maximum | Unit              |

|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------|---------|-------------------|

| Passband –0.05-dB corner                                                                                                                        | _       | 0.48                   | _       | Fs <sub>INT</sub> |

| -3.0-dB corner                                                                                                                                  | _       | 0.50                   | _       | Fs <sub>INT</sub> |

| Passband ripple (0.417x10 <sup>-3</sup> Fs <sub>INT</sub> to 0.417 Fs <sub>INT</sub> ; normalized to 0.417x10 <sup>-3</sup> Fs <sub>INT</sub> ) | -0.04   | _                      | 0.063   | dB                |

| Stopband attenuation (0.545 Fs <sub>INT</sub> to Fs <sub>INT</sub> )                                                                            | 60      | _                      | _       | dB                |

| Total group delay <sup>2</sup>                                                                                                                  |         | 5.35/Fs <sub>INT</sub> | _       | s                 |

<sup>1.</sup> Response scales with Fs<sub>INT</sub> (based on internal MCLK). Specifications are normalized to Fs<sub>INT</sub> and denormalized by multiplying by Fs<sub>INT</sub>.

#### Table 3-5. DAC High-Pass Filter (HPF) Characteristics

Test conditions (unless specified otherwise) Analog and digital gains are all set to 0 dB; TA = +25°C.

| Parameter <sup>1</sup>                                                                                                         | Minimum | Typical                                 | Maximum | Unit              |

|--------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------------|---------|-------------------|

| Passband –0.05-dB corner                                                                                                       | _       | 0.180x10 <sup>-3</sup>                  | _       | Fs <sub>INT</sub> |

| -3.0-dB corner                                                                                                                 | _       | 19.5x10 <sup>-6</sup>                   | _       | Fs <sub>INT</sub> |

| Passband ripple (0.417x10 <sup>-3</sup> Fs <sub>INT</sub> to 0.417 Fs <sub>INT</sub> ; normalized to 0.417 Fs <sub>INT</sub> ) | _       | _                                       | 0.01    | dB                |

| Phase deviation @ 0.453x10 <sup>-3</sup> Fs <sub>INT</sub>                                                                     | _       | 2.45                                    | _       | 0                 |

| Filter settling time <sup>2</sup>                                                                                              | _       | 24.5x10 <sup>3</sup> /Fs <sub>INT</sub> | 1       | S                 |

<sup>1.</sup> Response scales with Fs<sub>INT</sub> (internal sample rate, based on MCLK). Specifications are normalized to Fs<sub>INT</sub> and are denormalized by multiplying by Fs<sub>INT</sub>.

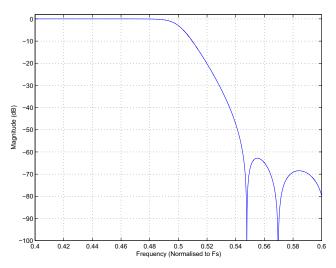

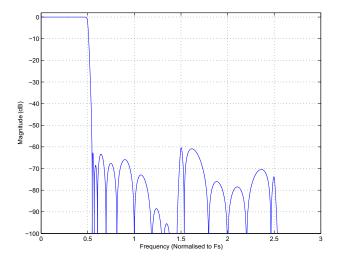

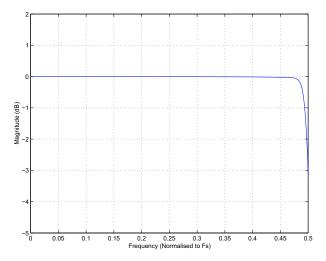

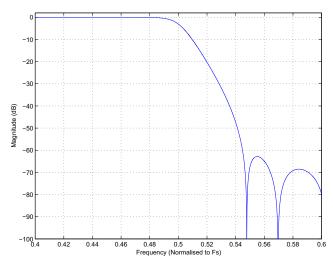

#### Table 3-6. SDIN to HPOUTx with SRC-Enabled Datapath Characteristics

Test conditions (unless specified otherwise): LRCK =  $Fs_{INT}$  =  $Fs_{EXT}$  = 48 kHz; MCLK = 12 MHz; HPF disabled; passband/stopband levels normalized to 0.417x10<sup>-3</sup>  $Fs_{EXT}$ ; entire path characteristics including serial port + SRC + DAC + HPOUT.

| Parameters <sup>1</sup>                                                                                                                         | Minimum | Typical                                                 | Maximum              | Unit              |

|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------|----------------------|-------------------|

| Passband –0.2-dB corner                                                                                                                         | _       | 0.463                                                   | _                    | Fs <sub>EXT</sub> |

| -3.0-dB corner                                                                                                                                  |         | 0.466                                                   | _                    | Fs <sub>EXT</sub> |

| Passband ripple (0.417x10 <sup>-3</sup> Fs <sub>EXT</sub> to 0.417 Fs <sub>EXT</sub> ; normalized to 0.417x10 <sup>-3</sup> Fs <sub>EXT</sub> ) | -0.16   | _                                                       | 0.02                 | dB                |

| Response at 0.5 Fs <sub>EXT</sub>                                                                                                               | _       | _                                                       | -54.9                | dB                |

| Stopband rejection from 0.480 Fs <sub>EXT</sub> to 0.524 Fs <sub>EXT</sub>                                                                      | 55      | _                                                       | _                    | dB                |

| Stopband rejection from 0.524 Fs <sub>EXT</sub> to 0.545 Fs <sub>EXT</sub>                                                                      | 39      | _                                                       | _                    | dB                |

| Stopband rejection from 0.545 Fs <sub>EXT</sub> to 3 Fs <sub>EXT</sub>                                                                          | 60      | _                                                       | _                    | dB                |

| Square wave overshoot                                                                                                                           | _       | _                                                       | 3.1                  | dB                |

| Group delay, bark-weighted average                                                                                                              | _       | _                                                       | 34/Fs <sub>EXT</sub> | S                 |

| Group delay $Fs_{EXT} \le 48 \text{ kHz}$                                                                                                       | _       | (15.8 ± 1.5)/Fs <sub>EXT</sub> + 10.3/Fs <sub>INT</sub> | _                    | S                 |

| $Fs_{EXT} \ge 88.2 \text{ kHz}$                                                                                                                 | _       | $(20.1 \pm 1)/Fs_{EXT} + (11.6 \pm 0.5)/Fs_{INT}$       | _                    | s                 |

| SRC disabled group delay <sup>2</sup>                                                                                                           | _       | (15±1)/Fs                                               | _                    | S                 |

<sup>1.</sup>Fs<sub>EXT</sub> is the external sample rate (LRCK/FSYNC frequency). Response scales with Fs<sub>EXT</sub>.

<sup>2.</sup>Informational only; group delay cannot be measured for this block by itself. An additional 5.5/Fs<sub>int</sub> group delay may be present through the serial ports and internal audio bus.

<sup>2.</sup> Required time for the magnitude of the DC component present at the output of the HPF to reach 5% of the applied DC signal.

<sup>2.</sup> This value varies by up to 1 Fs. If SRC is disabled, Fs =  $Fs_{OUT}$  =  $Fs_{IN}$ .

#### Table 3-7. Serial Data In-to-HPOUTx Characteristics

Test conditions (unless specified otherwise): Fig. 2-1 shows CS43L36 connections; input test signal is a 24-bit full-scale 997-Hz sine wave with 1 LSB of triangular PDF dither applied; GNDA = GNDL = GNDCP = 0 V; voltages are with respect to ground; parameters can vary with VA; typical performance data taken with VL = VA = 1.8 V, VP = 3.6 V; min/max performance data taken with VA = 1.66–1.94 V; VL = 1.8 V, VP = 3.6 V; VCP Mode;  $T_A = +25^{\circ}C$ ; measurement bandwidth is 20 Hz–20 kHz; ASP\_LRCK =  $F_{SINT} = 48$ -kHz mode; MCLK = 12 MHz, MCLK\_SRC\_SEL = 0; volume = 0 dB; FULL\_SCALE\_VOL = 0 (0dB); HP load:  $R_L = 30 \Omega$ ,  $R_L = 10 \Omega$ ,  $R_L = 10$

|                         | Parameter <sup>1</sup>                              |                          |                                                | Minimum | Typical    | Maximum | Unit            |

|-------------------------|-----------------------------------------------------|--------------------------|------------------------------------------------|---------|------------|---------|-----------------|

| $R_L = 3 k\Omega$       | Dynamic range                                       | 18-24 bit                | A-weighted                                     |         | 114        | _       | dB              |

| VP_CP Mode              | (defined in Table 3-1)                              |                          | unweighted                                     | 105     | 111        | _       | dB              |

|                         | THD+N <sup>2</sup> (defined in Table 3-1)           | 18–24 bit                | 0 dB                                           |         | -90        | -84     | dB              |

|                         |                                                     |                          | –20 dB                                         |         | -83        | _       | dB              |

|                         |                                                     | 40.1.9                   | −60 dB                                         |         | -51        | -48     | dB              |

|                         |                                                     | 16 bit                   | 0 dB<br>–20 dB                                 |         | -88<br>-73 | -82     | dB              |

|                         |                                                     |                          | -20 dB<br>-60 dB                               |         | -73<br>-33 | <br>_27 | dB<br>dB        |

|                         | Idle channel noise (A-weighted)                     |                          | _00 db                                         |         | 2.0        | -21     | μV              |

|                         | Full-scale output voltage <sup>3</sup>              |                          |                                                | 1.50•VA | 1.58•VA    | 1.66•VA | V <sub>PP</sub> |

| R <sub>I</sub> = 30 Ω   | Dynamic range (defined in Table 3-1)                | 18–24 bit                | A-weighted                                     | 1.50°VA | 114        | 1.00*VA | dB              |

| VP CP Mode              | Dynamic range (defined in Table 5-1)                | 10-24 DIL                | unweighted                                     | 105     | 114        | _       | dВ              |

|                         | THD+N <sup>2</sup> (defined in Table 3-1)           |                          | Pout = 10 mW                                   | _       | -98        | _       | dB              |

|                         | (4564 142 6 .)                                      |                          | Pout = 35 mW                                   |         | <b>-75</b> | -69     | dB              |

|                         | Full-scale output voltage <sup>3</sup>              |                          |                                                | 1.50•VA | 1.58•VA    | 1.66•VA | $V_{PP}$        |

|                         | Output power <sup>2</sup>                           |                          |                                                |         | 35.0       | _       | mW              |

| $R_L = 15 \Omega$       | Dynamic range (defined in Table 3-1)                | 18-24 bit                | A-weighted                                     | 102     | 108        | _       | dB              |

| VCP Mode                |                                                     |                          | unweighted                                     | 99      | 105        | _       | dB              |

| (FULL_SCALE_            | THD+N <sup>2</sup> (defined in Table 3-1)           |                          | Pout = 17.3 mW                                 |         | -75        | -69     | dB              |

| VOL = 1 [-6 dB])        | Full-scale output voltage <sup>3</sup>              |                          |                                                | 0.71•VA | 0.79•VA    | 0.86•VA | $V_{PP}$        |

|                         | Output power <sup>2</sup>                           |                          |                                                |         | 17.3       | _       | mW              |

| $R_L = 15 \Omega$       | Dynamic range                                       | 18–24 bit                | A-weighted                                     | 102     | 108        | _       | dB              |

| VP_CP Mode              |                                                     |                          | unweighted                                     | 99      | 105        | —       | dB              |

| Other characteristics   | Interchannel isolation $^3$ (3 k $\Omega$ )         |                          | 217 Hz                                         | _       | 90         | _       | dB              |

| (Table 3-1 gives        |                                                     |                          | 1 kHz                                          |         | 90         | _       | dB              |

| parameter definitions.) |                                                     |                          | 20 kHz                                         |         | 80         | _       | dB              |

|                         | Interchannel isolation $^3$ (30 $\Omega$ )          |                          | 217 Hz                                         | _       | 90         | _       | dB              |

|                         |                                                     |                          | 1 kHz                                          | _       | 90         | _       | dB              |

|                         | Output offset voltage: mute <sup>3,4</sup> (ANA MUT | T v = 1 222 2 77         | 20 kHz<br>') HPOUTx                            |         | 70<br>±0.5 | ±1.0    | dB<br>mV        |

|                         |                                                     | <u>_x = 1, see p. 77</u> | <u>,                                      </u> |         |            | _       |                 |

|                         | Output offset voltage 3,4                           |                          | HPOUTx                                         | —<br>45 | ±0.5       | ±2.5    | mV              |

|                         | Load resistance (R <sub>L</sub> )                   |                          | Normal operation <sup>3</sup>                  | 15      | _          | _       | Ω               |

|                         | Load capacitance (C <sub>L</sub> ) <sup>3,5</sup>   |                          | HPOUT_LOAD = 0<br>HPOUT_LOAD = 1               | _<br>_  |            | 1<br>10 | nF<br>nF        |

|                         | Turn-on time <sup>6</sup>                           | CI OV                    | V START EN = 000                               |         |            | 25      |                 |

|                         | rum-on ume ·                                        | SLUV                     | V_31AK1_EN = 000                               | _       | _          | 25      | ms              |

<sup>1.</sup> One LSB of triangular PDF dither is added to data.

<sup>3.</sup>HP output test configuration. Symbolized component values are specified in the test conditions above.

<sup>4.</sup>Assumes no external impedance on HSx/HSx\_REF. External impedance on HSx/HSx\_REF affects the offset and step deviation. See Section 4.2.1. 5.Amplifier is guaranteed to be stable with either headphone load setting.

<sup>2.</sup>Because VCP settings lower than VA reduce the HP amplifier headroom, the specified THD+N performance at full-scale output voltage and power may not be achieved.

<sup>6.</sup> Turn-on time is measured from when the HP\_PDN = 0 ACK signal is received to when the signal appears on the HP output. In most cases, enabling the SRC increases the turn-on time and may exceed the maximum specified value.

#### Table 3-8. DC Characteristics

Test conditions (unless specified otherwise): Fig. 2-1 shows CS43L36 connections; GNDA = GNDL = GNDCP = 0 V; voltages are with respect to ground; VL = VCP = VA = 1.8 V, VP = 3.6 V; T<sub>A</sub> = +25°C.

|                           | Parameters                                                   |               | Minimum | Typical | Maximum | Unit |

|---------------------------|--------------------------------------------------------------|---------------|---------|---------|---------|------|

| VCP_FILT (No load         | VP_CP Mode (ADPTPWR = 001)                                   | +VCP_FILT     |         | 2.6     | _       | V    |

| connected to HPOUTx.)     |                                                              | -VCP_FILT     | _       | -2.6    | _       | V    |

|                           | VCP Mode (ADPTPWR = 010)                                     | +VCP_FILT     | _       | VCP     | _       | V    |

|                           |                                                              | -VCP_FILT     | _       | -VCP    | _       | V    |

|                           | VCP/2 Mode (ADPTPWR = 011)                                   | +VCP_FILT     |         | VCP/2   | _       | V    |

|                           |                                                              | -VCP_FILT     | _       | -VCP/2  | _       | V    |

|                           | VCP/3 Mode (ADPTPWR = 100)                                   | +VCP_FILT     | _       | VCP/3   | _       | V    |

|                           |                                                              | -VCP_FILT     | _       | -VCP/3  | _       | V    |

| HS3 ground switch resista | ance (Typical values have ±25% tolerance.)                   |               | _       | 0.5     | _       | Ω    |

| Other DC filter           | FILT+ voltage                                                |               | _       | VA      | _       | V    |

|                           | HP output current limiter on threshold. See Section 4.3.4. 1 |               | 80      | 115     | 160     | mΑ   |

|                           | VD_FILT and VL power-on reset threshold (V <sub>POR</sub> )  | Up            | _       | 0.777   | _       | V    |

|                           |                                                              | Down          | _       | 0.628   | _       | V    |

| HPOUT pull-down           | HPOUT_PULLDOWN = 000                                         | 00–0111, 1100 | _       | 0.9     | _       | kΩ   |

| resistance 2,3            | HPOUT_PULLI                                                  |               |         | 9.3     | _       | kΩ   |

|                           | HPOUT_PULLI                                                  | DOWN = 1010   | _       | 5.8     | _       | kΩ   |

<sup>1.</sup> The HP output current limiter threshold spec is valid only while the Class H rails are in VCP Mode.

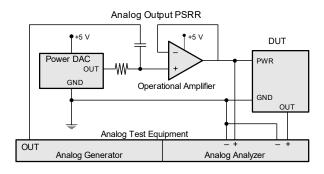

### Table 3-9. Power-Supply Rejection Ratio (PSRR) Characteristics

Test conditions (unless specified otherwise): Fig. 2-1 shows CS43L36 connections; input test signal held low (all zero data); GNDA = GNDL = GNDCP = 0 V; voltages are with respect to ground; VL = VA = 1.8 V, VP = 3.6 V; T<sub>A</sub> = +25°C.

| Parameters 1                                                    |        | Minimum | Typical | Maximum | Unit |

|-----------------------------------------------------------------|--------|---------|---------|---------|------|

| HPOUTx (-6-dB analog gain)                                      | 217 Hz | _       | 75      | _       | dB   |

| PSRR with 100-mVpp signal AC coupled to VA supply <sup>2</sup>  | 1 kHz  | _       | 75      | _       | dB   |

|                                                                 | 20 kHz | —       | 70      | _       | dB   |

| HPOUTx (-6-dB analog gain)                                      | 217 Hz | _       | 85      | _       | dB   |

| PSRR with 100-mVpp signal AC-coupled to VCP supply <sup>2</sup> | 1 kHz  | _       | 85      | _       | dB   |

|                                                                 | 20 kHz | —       | 65      | _       | dB   |

| HPOUTx (0-dB analog gain)                                       | 217 Hz | _       | 80      | _       | dB   |

| PSRR with 100-mVpp signal AC coupled to VP supply               | 1 kHz  | _       | 80      | _       | dB   |

|                                                                 | 20 kHz | _       | 60      | _       | dB   |

<sup>1.</sup>PSRR test configuration: Typical PSRR can vary by approximately 6 dB below the indicated values.

2. No load connected to any analog outputs.

<sup>2.</sup> Typical values have ±20% tolerance.

<sup>3.</sup> Clamp is disabled (HPOUT CLAMP = 1) and channel is powered down (HPOUT PDN = 1).

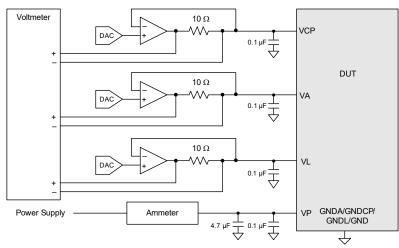

#### Table 3-10. Power Consumption

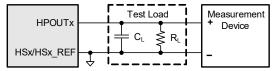

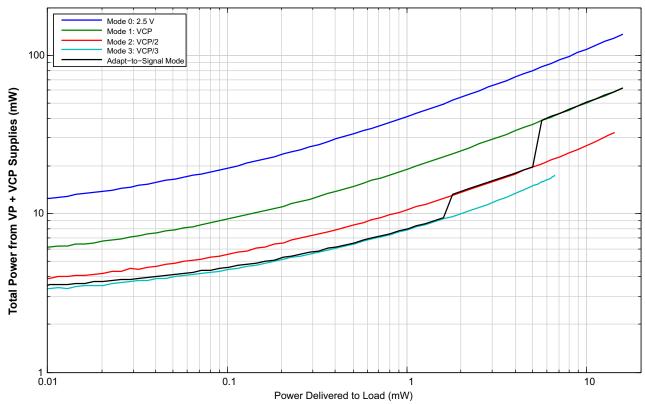

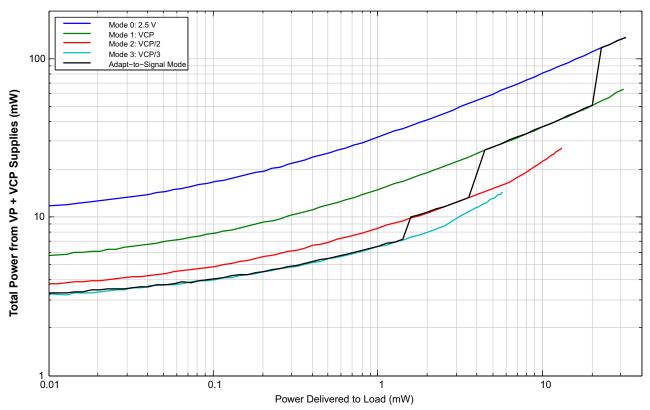

Test conditions (unless specified otherwise): Fig. 2-1 shows CS43L36 connections; GNDA = GNDL = GNDCP = 0 V; voltages are with respect to ground; performance data taken with VA = VCP = VL = 1.8 V;  $\overline{DIGLDO\_PDN}$  is deasserted; VP = 3.6 V;  $T_A$  = +25°C; ASP\_LRCK = 48-kHz Mode;  $F_{SINT}$  = 48 kHz; SCLK = 12 MHz, MCLK\_SRC\_SEL = 0; volume= 0 dB;  $F_{SINT}$  = 40 kHz; or independent of the fields are set to defaults; no signal on any input; control port inactive; input clock/data are held low when not required; test load is  $R_L$  = 30  $\Omega$  and  $R_L$  = 1 nF for HPOUTx; measured values include currents consumed by the DAC and do not include current delivered to external loads unless specified otherwise (e.g., HPOUTx); see Fig. 3-1.

|   | 1190 (1290) |                        | ClassH                                   | Typical Current (μA) |                  |                 |                 | Total Power |       |

|---|-------------|------------------------|------------------------------------------|----------------------|------------------|-----------------|-----------------|-------------|-------|

|   |             |                        | Mode                                     | i <sub>VA</sub>      | i <sub>VCP</sub> | i <sub>VL</sub> | i <sub>VP</sub> | (μW)        |       |

| 1 | Α           | Off <sup>1</sup>       |                                          | _                    | 0                | 0               | 0               | 3.1         | 11.16 |

| 2 | Α           | Standby <sup>2,3</sup> |                                          | _                    | 0                | 0               | 0               | 20          | 72.0  |

| 3 | Α           | Standby (RCO Mode) 4,5 |                                          |                      | 0                | 0               | 343             | 31          | 729   |

| 4 | Α           | Playback               | Stereo HPOUT (no signal, HPOUT_LOAD = 0) | VCP/3                | 1413             | 1204            | 858             | 58          | 6464  |

|   | В           |                        | Stereo HPOUT (0.1 mW, HPOUT_LOAD = 0)    | VCP/3                | 1441             | 2336            | 965             | 58          | 8744  |

- 1. Off configuration: Clock/data lines held low; RESET = LOW; VA = VL = VCP = 0 V; VP = 3.6 V.

- 2.Standby configuration: Clock/data lines held low; VA = VL = VCP = 0 V; VP = 3.6 V; M HP WAKE = 0 (unmasked).

- 3.SCLK PRESENT = 1.

- 4.SCLK PRESENT = 0 (RCO clocking).

- 5. Standby configuration (RCO clocking): Clock/data lines held low; VA = 0 V; VL = 1.8 V, VCP = 0 V, VP = 3.6 V; M\_HP\_WAKE = 0 (unmasked).

**Note:** The current draw on the VA, VCP, and VL power supply pins is derived from the measured voltage drop across a 10- $\Omega$  series resistor between the associated supply source and each voltage supply pin. Given the larger currents that are possible on the VP supply, an ammeter is used for the measurement.

Figure 3-1. Power Consumption Test Configuration

Table 3-11. Register Field Settings

|   |             |         |             | Register Fields and S | ettings               |

|---|-------------|---------|-------------|-----------------------|-----------------------|

|   | lse<br>ises | PDN_ALL | ASP_DAI_PDN | HP_PDN                | Class H Mode<br>p. 23 |

| 1 | Α           |         | _           | _                     | _                     |

| 2 | Α           | 1       | _           | _                     | _                     |

| 3 | Α           | 1       | _           | _                     | _                     |

| 4 | Α           | 0       | 0           | 0                     | VCP/3                 |

|   | В           | 0       | 0           | 0                     | VCP/3                 |

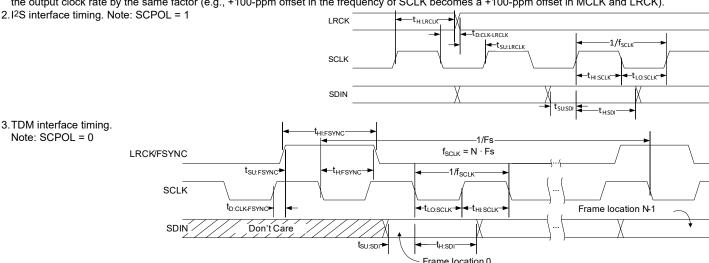

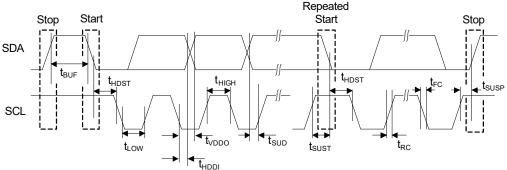

#### Table 3-12. Digital Audio Interface Timing Characteristics

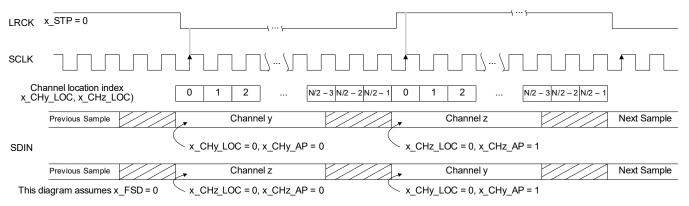

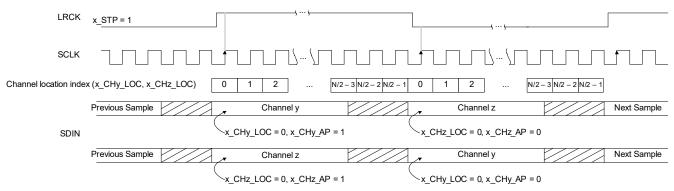

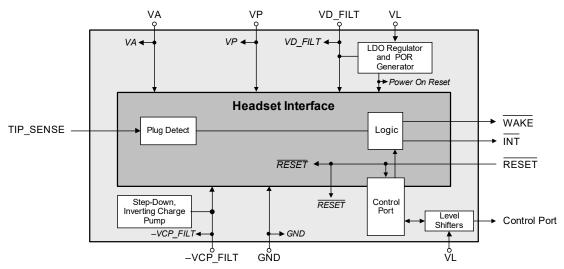

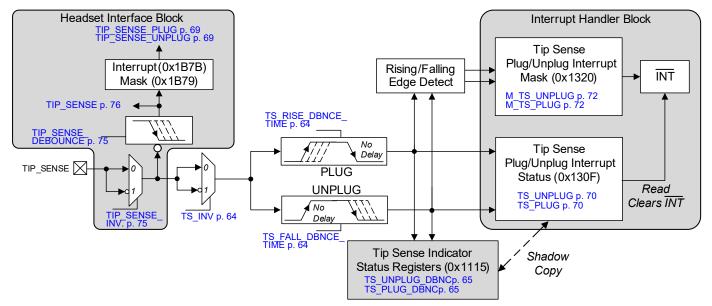

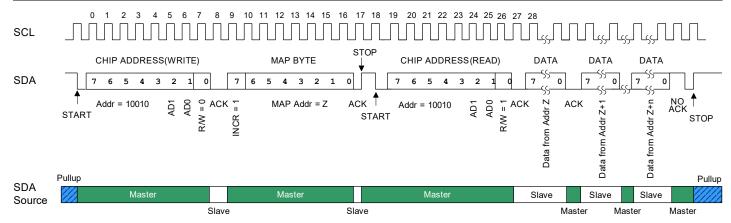

Test conditions (unless specified otherwise): GNDA = GNDL = GNDCP = 0 V; all voltages with respect to ground; values are for both VL = 1.2 and 1.8 V; inputs: Logic 0 = GNDL = 0 V, Logic 1 = VL;  $T_A$  = +25°C;  $C_{LOAD}$  = 30 pF (for VL = 1.2 V) and 60 pF (for VL = 1.8 V); input timings are measured at  $V_{IL}$  and  $V_{IH}$  thresholds; output timings are measured at  $V_{OL}$  and  $V_{OH}$  thresholds (see Table 3-14); ASP\_TX\_HIZ\_DLY = 00.