# Integrated, Precision Battery **Sensor for Automotive**

**ADuC7033**

#### **FEATURES**

**High precision ADCs**

Dual channel, simultaneous sampling, 16-bit, Σ-Δ ADCs Programmable ADC throughput from 1 Hz to 8 kHz

On-chip 5 ppm/°C voltage reference

**Current channel**

Fully differential, buffered input Programmable gain from 1 to 512 ADC input range: -200 mV to +300 mV

Digital comparators, with current accumulator feature

Voltage channel

Buffered, on-chip attenuator for 12 V battery inputs

**Temperature channel**

External and on-chip temperature sensor options

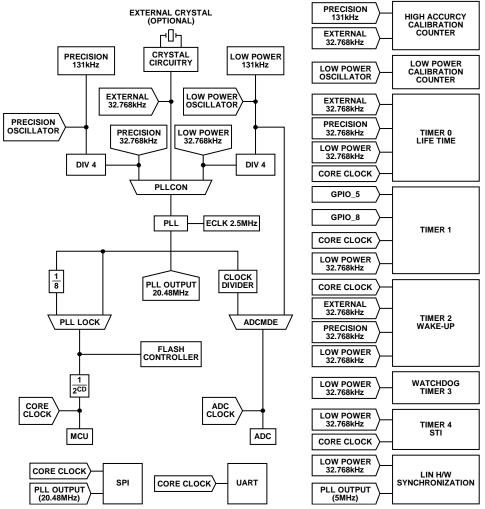

Microcontroller

ARM7TDMI core, 16-/32-bit RISC architecture 20.48 MHz PLL with programmable divider

PLL input source

On-chip precision oscillator

On-chip low power oscillator

External (32.768 kHz) watch crystal

JTAG port supports code download and debug

#### Memory

96 kB Flash/EE memory, 6 kB SRAM

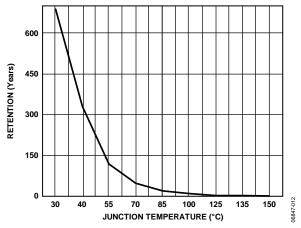

10,000-cycle Flash/EE endurance, 20-year Flash/EE

In-circuit download via JTAG and LIN

On-chip peripherals

LIN 2.0-compatible (slave) support via UART with

hardware synchronization

Flexible wake-up I/O pin, master/slave SPI serial I/O

9-pin GPIO port, 3× general-purpose timers

Wake-up and watchdog timers

Power supply monitor and on-chip power-on reset

**Power**

Operates directly from 12 V battery supply

**Current consumption**

Normal mode: 10 mA at 10 MHz

Low power monitor mode

Package and temperature range

48-lead, 7 mm × 7 mm LQFP

Fully specified for -40°C to +115°C operation

#### **APPLICATIONS**

Battery sensing/management for automotive systems

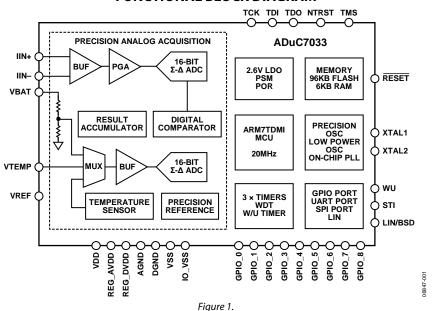

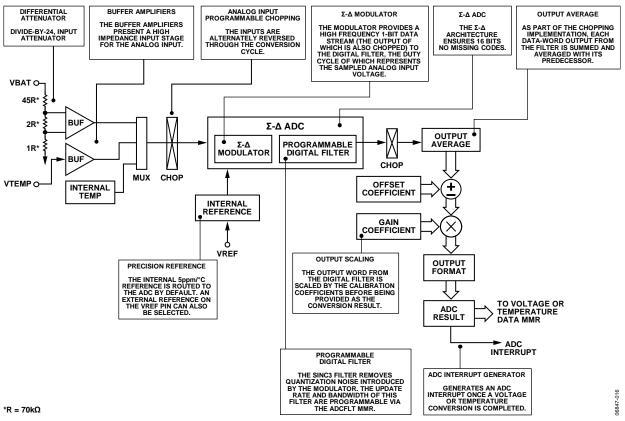

### **FUNCTIONAL BLOCK DIAGRAM**

## **TABLE OF CONTENTS**

| Features                                                    |

|-------------------------------------------------------------|

| Applications1                                               |

| Functional Block Diagram1                                   |

| Revision History                                            |

| Specifications                                              |

| Electrical Specifications                                   |

| Timing Specifications                                       |

| Absolute Maximum Ratings                                    |

| ESD Caution                                                 |

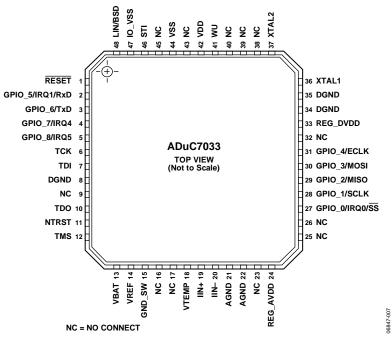

| Pin Configuration and Function Descriptions16               |

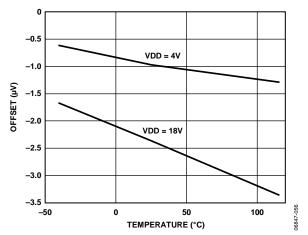

| Typical Performance Characteristics                         |

| Terminology                                                 |

| Theory of Operation                                         |

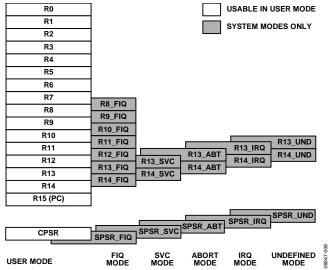

| Overview of the ARM7TDMI Core21                             |

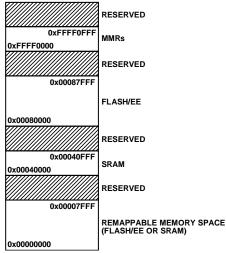

| Memory Organization                                         |

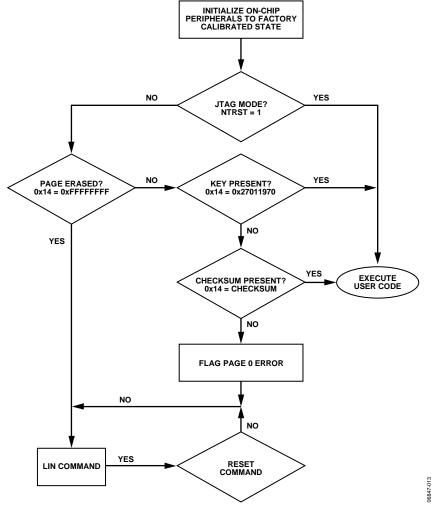

| Reset                                                       |

| Flash/EE Memory                                             |

| Programming Flash/EE Memory In-Circuit                      |

| Flash/EE Memory Control Interface                           |

| Flash/EE Memory Security                                    |

| Flash/EE Memory Reliability                                 |

| CODE Execution Time from SRAM and Flash/EE33                |

| ADuC7033 Kernel                                             |

| Memory Mapped Registers                                     |

| Complete MMR Listing                                        |

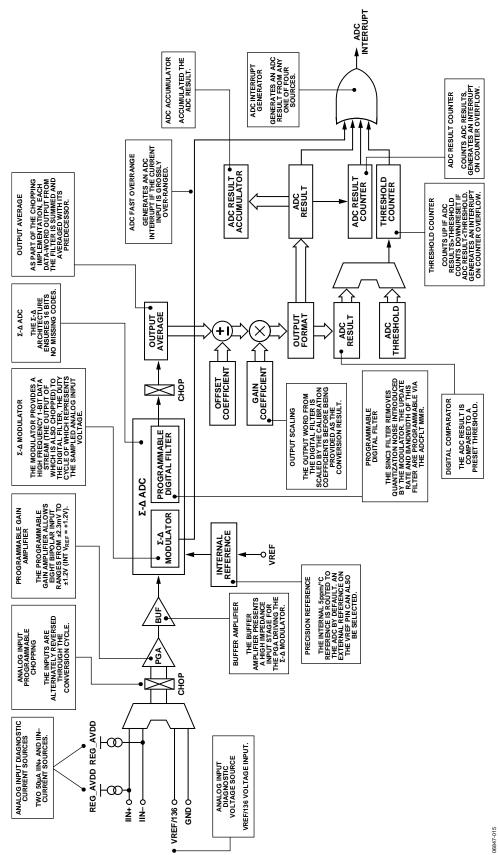

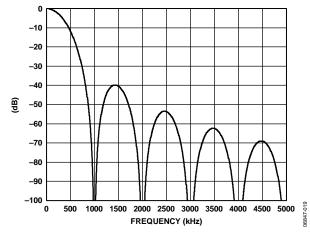

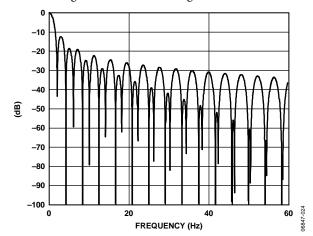

| 16-Bit, $\Sigma\text{-}\Delta$ Analog-to-Digital Converters |

| Current Channel ADC (I-ADC)43                               |

| Voltage/Temperature Channel ADC (V/T-ADC)45                 |

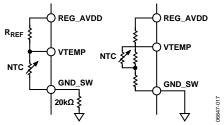

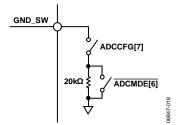

| ADC Ground Switch46                                         |

| ADC Noise Performance Tables47                              |

| ADC MMR Interface                                           |

| ADC Power Modes of Operation59                              |

| ADC Diagnostics                                             |

| Power Supply Support Circuits                               |

| System Clocks                                               |

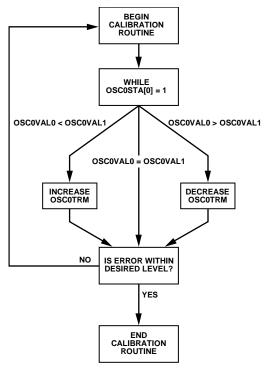

| Low Power Clock Calibration69                               |

|                                                             |

| Processor Reference Peripherals                             |

| Processor Reference Peripherals                             |

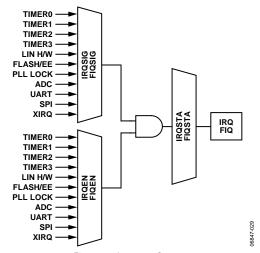

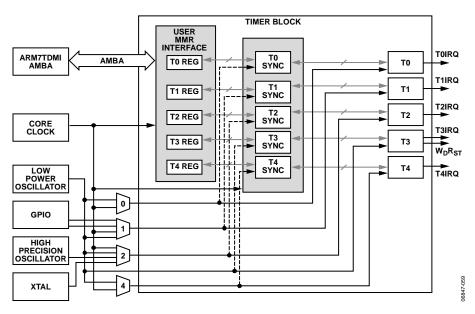

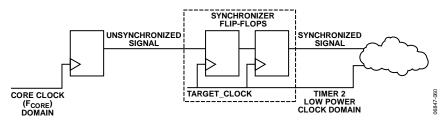

| Synchronization of Timers Across Asynchronous Clock  Domains           | 74 |

|------------------------------------------------------------------------|----|

| Programming the Timers                                                 |    |

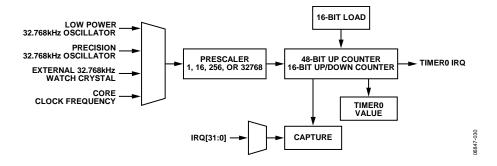

| Timer0—Lifetime Timer                                                  |    |

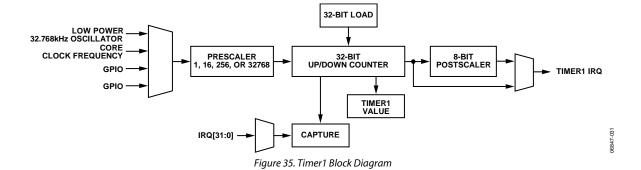

| Timer1                                                                 |    |

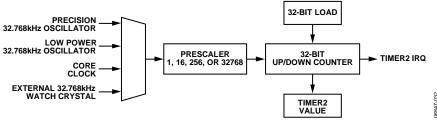

| Timer2 or Wake-Up Timer                                                |    |

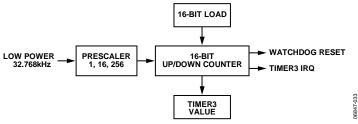

| Timer3 or Watchdog Timer                                               |    |

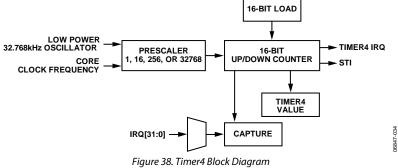

| Timer4 or STI Timer                                                    |    |

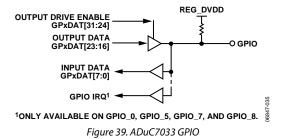

| General-Purpose Input/Output                                           |    |

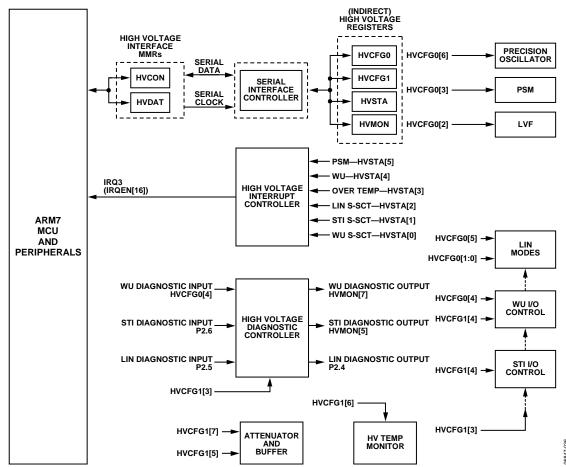

| High Voltage Peripheral Control Interface                              |    |

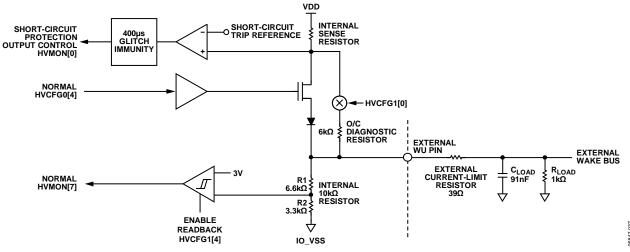

| Wake-Up (WU) Pin                                                       |    |

| <u>.</u>                                                               | Л. |

| Handling Interrupts from the High Voltage Peripheral Control Interface | )7 |

| Low Voltage Flag (LVF)10                                               |    |

| High Voltage Diagnostics10                                             |    |

| UART Serial Interface                                                  |    |

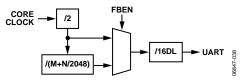

| Baud Rate Generation                                                   | 36 |

| UART Register Definition10                                             | 36 |

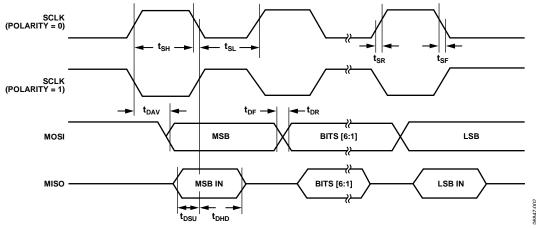

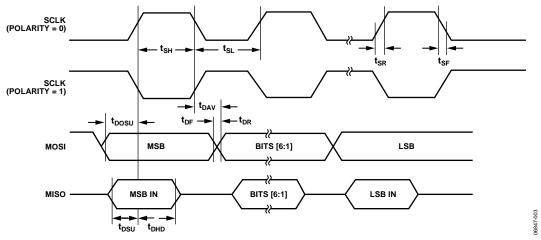

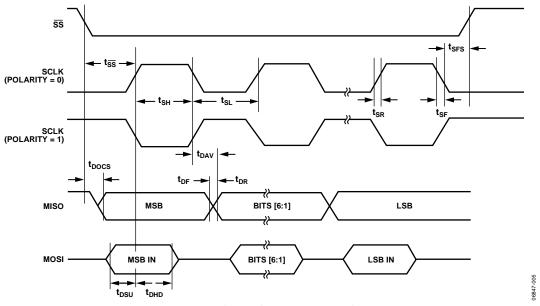

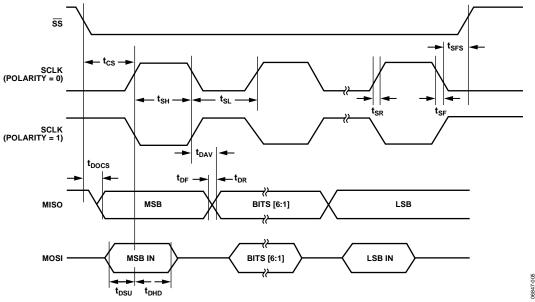

| Serial Peripheral Interface11                                          |    |

| MISO (Master In, Slave Out Data I/O Pin)                               |    |

| MOSI (Master Out, Slave In Pin)1                                       |    |

| SCLK (Serial Clock I/O Pin)11                                          |    |

| Chip Select $(\overline{SS})$ Input Pin                                |    |

| SPI Register Definitions                                               |    |

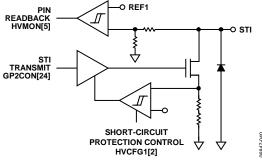

| Serial Test Interface                                                  |    |

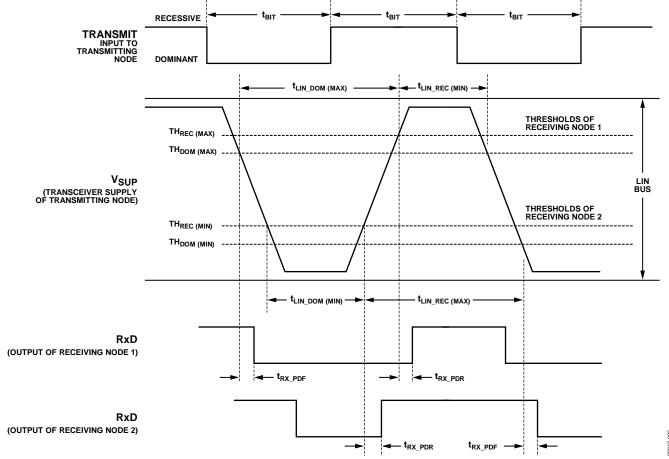

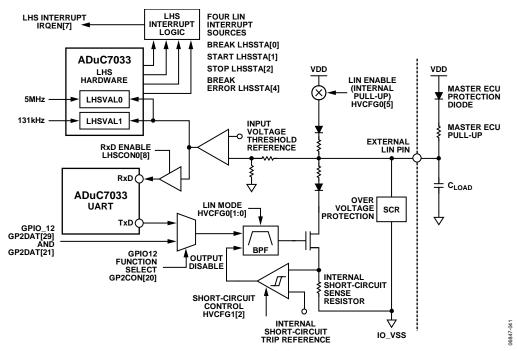

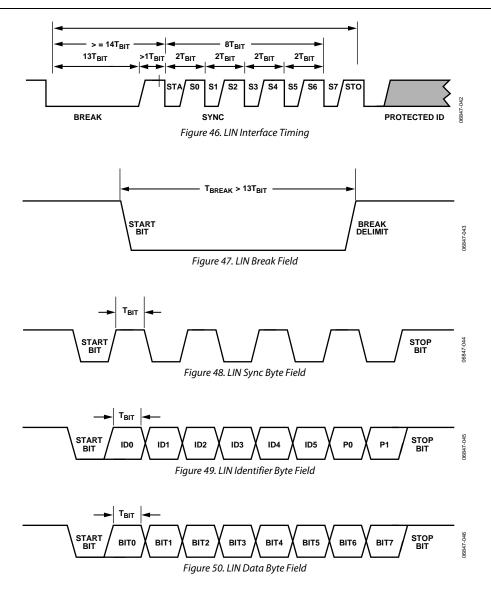

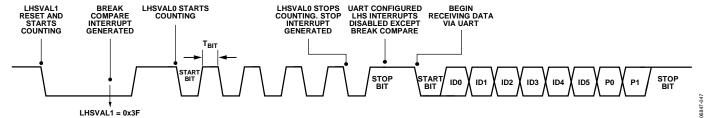

| LIN (Local Interconnect Network) Interface                             |    |

| LIN MMR Description                                                    |    |

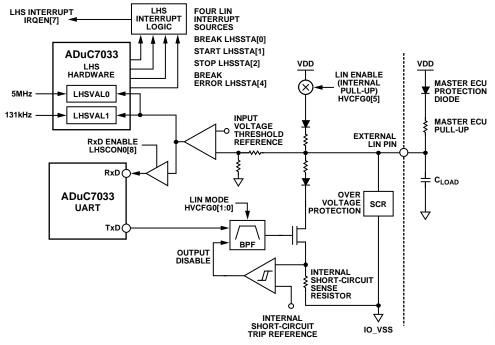

| LIN Hardware Interface 12                                              |    |

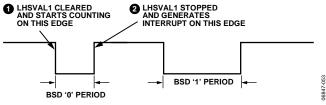

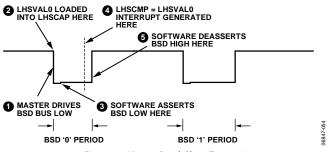

| Bit Serial Device (BSD) Interface                                      |    |

| BSD Communication Hardware Interface                                   |    |

| BSD Related MMRs13                                                     |    |

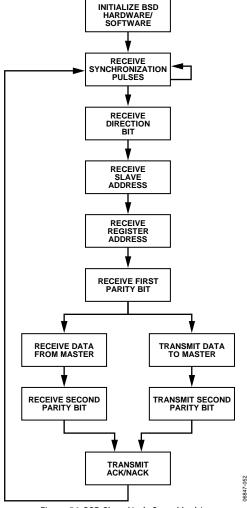

| BSD Communications Frame                                               |    |

| BSD Data Reception13                                                   |    |

| BSD Data Transmission                                                  |    |

| Wake-Up from BSD Interface13                                           |    |

| Part Identification                                                    |    |

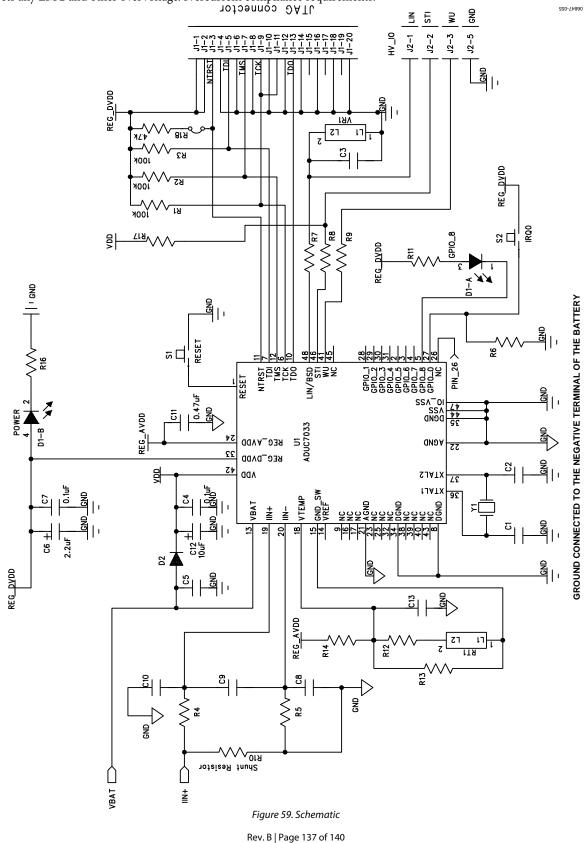

| Schematic                                                              |    |

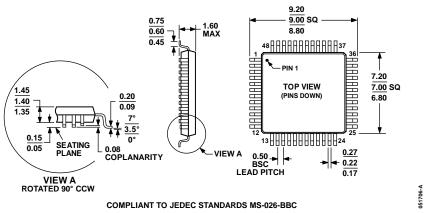

| Outline Dimensions                                                     |    |

| Ordering Guide                                                         |    |

### **REVISION HISTORY**

| 10/10— | Rev. | A to | Rev. | В |

|--------|------|------|------|---|

|--------|------|------|------|---|

11/07—Revision 0: Initial Version

| Changes to Table 32                             | 47          |

|-------------------------------------------------|-------------|

| Changes to Timers Section                       | 74          |

| Added Synchronization of Timers across Asynchro | onous Clock |

| Domains Section, Figure 32, and Figure 33       | 74          |

| Added Programming the Timers Section            | 75          |

| 11/09—Rev. 0 to Rev. A                          |             |

| Removed LFCSP                                   | Throughout  |

| Updated Outline Dimensions                      | 136         |

| Changes to Ordering Guide                       |             |

|                                                 |             |

## **SPECIFICATIONS**

### **ELECTRICAL SPECIFICATIONS**

VDD = 3.5 V to 18 V, VREF = 1.2 V internal reference,  $f_{CORE} = 10.24 \text{ MHz}$  driven from external 32.768 kHz watch crystal or on-chip precision oscillator, all specifications  $T_A = -40^{\circ}\text{C}$  to  $+115^{\circ}\text{C}$ , unless otherwise noted.

**Table 1. ADuC7033 Electrical Specifications**

| Parameter                                 | Test Conditions/Comments                                    | Min  | Тур   | Max  | Unit       |

|-------------------------------------------|-------------------------------------------------------------|------|-------|------|------------|

| ADC SPECIFICATIONS                        |                                                             |      |       |      |            |

| Conversion Rate <sup>1</sup>              | Chop off, ADC normal operating mode                         | 4    |       | 8000 | Hz         |

|                                           | Chop on, ADC normal operating mode                          | 4    |       | 2600 | Hz         |

|                                           | Chop on, ADC low power mode                                 | 1    |       | 650  | Hz         |

| Current Channel                           |                                                             |      |       |      |            |

| No Missing Codes <sup>1</sup>             | Valid for all ADC update rates and ADC modes                | 16   |       |      | Bits       |

| Integral Nonlinearity <sup>1, 2</sup>     |                                                             |      | ±10   | ±60  | ppm of FSR |

| Offset Error <sup>2, 3, 4, 5</sup>        | Chop off, 1 LSB = (36.6/gain) $\mu$ V                       | -10  | ±3    | +10  | LSB        |

| Offset Error <sup>1, 3, 6</sup>           | Chop on                                                     | -2   | ±0.5  | +2   | μV         |

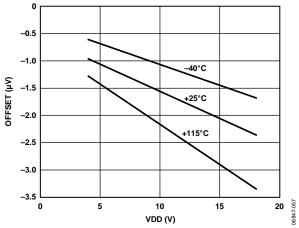

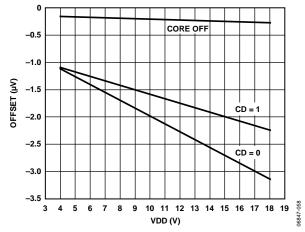

| Offset Error <sup>1, 3</sup>              | Chop on, low power or low power plus mode, MCU powered down | 0    | -200  | -650 | nV         |

| Offset Error <sup>1, 3</sup>              | Chop on, normal mode, CD = 1                                | 0    | -1.5  | -5   | μV         |

| Offset Error Drift <sup>6</sup>           | Chop off, valid for ADC gains of 4 to 64, normal mode       |      | ±0.03 |      | LSB/°C     |

|                                           | Chop off, valid for ADC gains of 128 to 512, normal mode    |      | ±30   |      | nV/°C      |

|                                           | Chop on                                                     |      | ±10   |      | nV/°C      |

| Total Gain Error <sup>1, 3, 7, 8, 9</sup> | Normal mode                                                 | -0.5 | ±0.1  | +0.5 | %          |

| Total Gain Error <sup>1, 3, 7, 9</sup>    | Low power mode, using ADCREF MMR                            | -4   | ±0.2  | +4   | %          |

| Total Gain Error <sup>1, 3, 7, 9</sup>    | Low power plus mode, using precision V <sub>REF</sub>       | -1   | ±0.2  | +1   | %          |

| Gain Drift                                |                                                             |      | ±3    |      | ppm/°C     |

| PGA Gain Mismatch Error                   |                                                             |      | ±0.1  |      | %          |

| Output Noise <sup>1, 10, 11</sup>         | 4 Hz update rate, gain = 512, chop enabled                  |      | 60    | 90   | nV rms     |

|                                           | 4 Hz update rate, gain = 512, chop disabled                 |      | 75    | 115  | nV rms     |

|                                           | 10 Hz update rate, gain = 512, chop enabled                 |      | 100   | 150  | nV rms     |

|                                           | 10 Hz update rate, gain = 512, chop disabled                |      | 120   | 180  | nV rms     |

|                                           | 1 kHz update rate, gain ≥ 64, chop enabled                  |      | 8.0   | 1.2  | μV rms     |

|                                           | 1 kHz update rate, gain ≥ 64, chop disabled                 |      | 1     | 1.5  | μV rms     |

|                                           | 1 kHz update rate, gain = 512                               |      | 0.6   | 0.9  | μV rms     |

|                                           | 1 kHz update rate, gain = 32                                |      | 8.0   | 1.2  | μV rms     |

|                                           | 1 kHz update rate, gain = 8, chop enabled                   |      | 2.1   | 4.1  | μV rms     |

|                                           | 1 kHz update rate, gain = 8, chop disabled                  |      | 1.6   | 2.4  | μV rms     |

|                                           | 1 kHz update rate, gain = 8 (ADCFLT = 0x0101)               |      | 2.6   | 3.9  | μV rms     |

|                                           | 1 kHz update rate, gain = 4                                 |      | 2.0   | 2.8  | μV rms     |

|                                           | 8 kHz update rate, gain = 32                                |      | 2.5   | 3.5  | μV rms     |

|                                           | 8 kHz update rate, gain = 4                                 |      | 14    | 21   | μV rms     |

|                                           | ADC low power mode, $f_{ADC} = 10 \text{ Hz}$ , gain = 128  |      | 1.25  | 1.9  | μV rms     |

|                                           | ADC low power mode, $f_{ADC} = 1$ Hz, gain = 128            |      | 0.35  | 0.5  | μV rms     |

|                                           | ADC low power plus mode, $f_{ADC} = 1$ Hz, gain = 512       |      | 0.1   | 0.15 | μV rms     |

| Voltage Channel <sup>12</sup>             |                                                             |      |       |      |            |

| No Missing Codes <sup>1</sup>             | Valid at all ADC update rates                               | 16   |       |      | Bits       |

| Integral Nonlinearity <sup>1</sup>        |                                                             |      | ±10   | ±60  | ppm of FSR |

| Offset Error <sup>3, 5</sup>              | Chop off, 1 LSB = 439.5 $\mu$ V                             | -10  | ±1    | +10  | LSB        |

| Offset Error <sup>1, 3</sup>              | Chop on                                                     | -1   | ±0.3  | +1   | LSB        |

| Offset Error Drift                        | Chop off                                                    |      | ±0.03 |      | LSB/°C     |

| Parameter                                               | Test Conditions/Comments                               | Min   | Тур                     | Max   | Unit        |

|---------------------------------------------------------|--------------------------------------------------------|-------|-------------------------|-------|-------------|

| Total Gain Error <sup>1, 3, 7, 13, 14</sup>             | Includes resistor mismatch                             | -0.25 | ±0.06                   | +0.25 | %           |

|                                                         | Temperature range = $-25^{\circ}$ C to $+65^{\circ}$ C | -0.15 | ±0.03                   | +0.15 | %           |

| Gain Drift                                              | Includes resistor mismatch drift                       |       | ±3                      |       | ppm/°C      |

| Output Noise <sup>1, 10, 15</sup>                       | 4 Hz update rate, chop enabled                         |       | 60                      | 90    | μV rms      |

|                                                         | 10 Hz update rate, chop enabled                        |       | 60                      | 90    | μV rms      |

|                                                         | 1 kHz update rate, chop disabled                       |       | 180                     | 270   | μV rms      |

|                                                         | 1 kHz update rate, chop enabled                        |       | 240                     | 307   | μV rms      |

|                                                         | 1 kHz update rate (ADCFLT = 0x0101)                    |       | 270                     | 405   | μV rms      |

|                                                         | 8 kHz update rate                                      |       | 1600                    | 2400  | μV rms      |

| Temperature Channel                                     |                                                        |       |                         |       |             |

| No Missing Codes <sup>1</sup>                           | Valid at all ADC update rates                          | 16    |                         |       | Bits        |

| Integral Nonlinearity <sup>1</sup>                      |                                                        |       | ±10                     | ±60   | ppm of FSR  |

| Offset Error <sup>3, 5, 16, 17</sup>                    | Chop off, 1 LSB = 19.84 $\mu$ V (in unipolar mode)     | -10   | ±3                      | +10   | LSB         |

| Offset Error <sup>1, 3</sup>                            | Chop on                                                | -5    | ±1                      | +5    | LSB         |

| Offset Error Drift                                      | Chop off                                               |       | ±0.03                   |       | LSB/°C      |

| Total Gain Error <sup>1, 3, 13</sup>                    | Using AVDD/2 for reference                             | -0.2  | ±0.06                   | +0.2  | %           |

| Gain Drift                                              |                                                        |       | ±3                      |       | ppm/°C      |

| Output Noise <sup>1</sup>                               | 1 kHz update rate                                      |       | 7.5                     | 11.25 | μV rms      |

| ADC SPECIFICATIONS ANALOG                               | Internal V <sub>REF</sub> = 1.2 V                      |       |                         |       |             |

| INPUT                                                   |                                                        |       |                         |       |             |

| Current Channel                                         |                                                        |       |                         |       |             |

| Absolute Input Voltage Range                            | Applies to both IIN+ and IIN-                          | -200  |                         | +300  | mV          |

| Input Voltage Range <sup>18, 19</sup>                   | Gain = $1^{20}$                                        |       | ±1.2                    |       | V           |

|                                                         | Gain = $2^{20}$                                        |       | ±600                    |       | mV          |

|                                                         | Gain = $4^{20}$                                        |       | ±300                    |       | mV          |

|                                                         | Gain = 8                                               |       | ±150                    |       | mV          |

|                                                         | Gain = 16                                              |       | ±75                     |       | mV          |

|                                                         | Gain = 32                                              |       | ±37.5                   |       | mV          |

|                                                         | Gain = 64                                              |       | ±18.75                  |       | mV          |

|                                                         | Gain = 128                                             |       | ±9.375                  |       | mV          |

|                                                         | Gain = 256                                             |       | ±4.68                   |       | mV          |

|                                                         | Gain = 512                                             |       | ±2.3                    |       | mV          |

| Input Leakage Current <sup>1</sup>                      |                                                        | -3    |                         | +3    | nA          |

| Input Offset Current <sup>1,21</sup>                    |                                                        |       | 0.5                     | 1.5   | nA          |

| Voltage Channel                                         |                                                        |       |                         |       |             |

| Absolute Input Voltage Range                            |                                                        | 4     |                         | 18    | V           |

| Input Voltage Range                                     |                                                        |       | 0 to 28.8               |       | V           |

| VBAT Input Current                                      | VBAT = 18 V                                            | 3     | 5.5                     | 8     | μΑ          |

| Temperature Channel                                     | $V_{REF} = (REG\_AVDD, GND\_SW)/2$                     |       |                         |       |             |

| Absolute Input Voltage Range                            |                                                        | 100   |                         | 1300  | mV          |

| Input Voltage Range                                     |                                                        |       | $0$ to $V_{\text{REF}}$ |       | V           |

| VTEMP Input Current <sup>1</sup>                        |                                                        |       | 2.5                     | 100   | nA          |

| VOLTAGE REFERENCE                                       |                                                        |       |                         |       |             |

| ADC Precision Reference                                 |                                                        |       |                         |       |             |

| Internal V <sub>REF</sub>                               |                                                        |       | 1.2                     |       | V           |

| Power-Up Time <sup>1</sup>                              |                                                        |       | 0.5                     |       | Ms          |

| Initial Accuracy <sup>1</sup>                           | Measured at $T_A = 25^{\circ}C$                        | -0.15 |                         | +0.15 | %           |

| Temperature Coefficient <sup>1, 22</sup>                |                                                        | -20   | ±5                      | +20   | ppm/°C      |

| Reference Long-Term Stability <sup>23</sup>             |                                                        |       | 100                     |       | ppm/1000 hr |

| External Reference Input Range <sup>24</sup>            |                                                        | 0.1   |                         | 1.3   | V           |

| V <sub>REF</sub> Divide-by-2 Initial Error <sup>1</sup> |                                                        |       | 0.1                     | 0.3   | %           |

| Parameter                             | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Min      | Тур     | Max             | Unit   |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|-----------------|--------|

| ADC Low Power Reference               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |         |                 |        |

| Internal V <sub>REF</sub>             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | 1.2     |                 | V      |

| Initial Accuracy                      | Measured at $T_A = 25^{\circ}C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -5       |         | +5              | %      |

| Initial Accuracy <sup>1</sup>         | Using ADCREF, measured at T <sub>A</sub> = 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | 0.1     |                 | %      |

| Temperature Coefficient1,22           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -300     | ±150    | +300            | ppm/°C |

| RESISTIVE ATTENUATOR                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |         |                 |        |

| Divider Ratio                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | 24      |                 |        |

| Resistor Mismatch Drift               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | 3       |                 | ppm/°C |

| ADC GROUND SWITCH                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |         |                 |        |

| Resistance                            | Direct path to ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | 10      |                 | Ω      |

|                                       | 20 kΩ resistor selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10       | 20      | 30              | kΩ     |

| Input Current                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |         | 6               | mA     |

| TEMPERATURE SENSOR <sup>25</sup>      | After user calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |         |                 |        |

| Accuracy                              | MCU in power-down or standby mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | ±3      |                 | °C     |

|                                       | MCU in power-down or standby mode,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | ±2      |                 | °C     |

|                                       | temperature range = $-25^{\circ}$ C to $+65^{\circ}$ C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | <b></b> |                 |        |

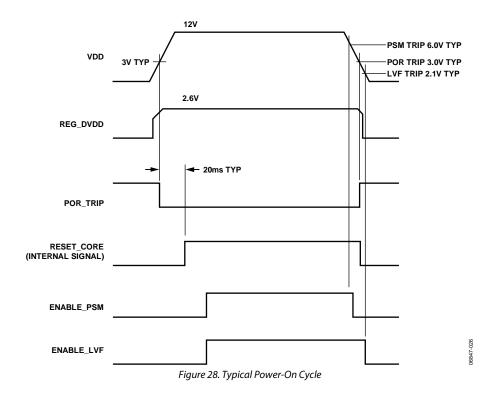

| POWER-ON RESET (POR)                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1        |         |                 |        |

| POR Trip Level                        | Refers to voltage at VDD pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.85     | 3.0     | 3.15            | V      |

| POR Hysteresis                        | , and the second |          | 300     |                 | mV     |

| RESET Timeout from POR                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | 20      |                 | ms     |

| LOW VOLTAGE FLAG (LVF)                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |         |                 | 5      |

| LVF Level                             | Refers to voltage at VDD pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1.9      | 2.1     | 2.3             | V      |

| POWER SUPPLY MONITOR (PSM)            | neiers to voltage at VBB pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12       |         |                 | 1      |

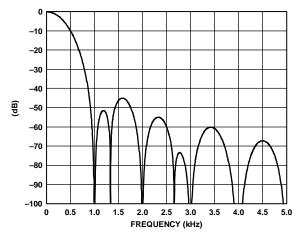

| PSM Trip Level                        | Refers to voltage at VDD pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          | 6.0     |                 | V      |