# RENESAS

#### EL5202, EL5203 400MHz Slew Enhanced VFAs

# DATASHEET

FN7331 Rev 9.00 January 17, 2014

The EL5202 and EL5203 are dual, high-speed VFAs based on a CFA architecture. This gives the typical high slew rate benefits of a CFA family along with the stability and ease of use associated with the VFA type architecture. With slew rates of  $3500V/\mu s$ , these devices enable the use of voltage feedback amplifiers in a space where the only alternative has been current feedback amplifiers. This family also includes single, dual, and triple versions with 750MHz bandwidths; please see the EL5104 through EL5304 data sheet for details.

Both devices operate on single 5V or  $\pm$ 5V supplies from minimum supply current. The EL5202 also features an output enable function, which can be used to put the output in to a high-impedance mode. This allows the outputs of multiple amplifiers to be tied together for use in multiplexing applications.

Typical applications for these families include cable driving, filtering, A/D and D/A buffering, multiplexing and summing within video, communications, and instrumentation designs.

#### **Features**

- Operates off 3V, 5V, or ±5V supplies

- Power-down to 13µA (EL5202)

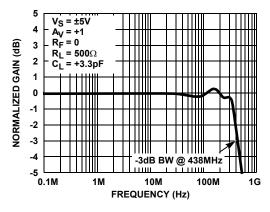

- -3dB bandwidth = 400MHz

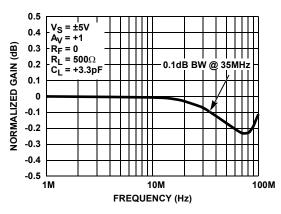

- ±0.1dB bandwidth = 35MHz

- Low supply current = 5mA per amplifier

- Slew rate = 3500V/µs

- Low offset voltage = 5mV max

- Output current = 150mA

- A<sub>VOL</sub> = 2000

- Differential gain/phase = 0.01%/0.01°

- Pb-free (RoHS compliant)

## **Applications**

- Video amplifiers

- PCMCIA applications

- A/D drivers

- Line drivers

- · Portable computers

- High speed communications

- RGB applications

- Broadcast equipment

- · Active filtering

# **Ordering Information**

| PART NUMBER<br>(Note 3)    | PART MARKING | TEMP RANGE<br>(°C) | PACKAGE<br>(Pb-free) | PKG<br>DWG. # |

|----------------------------|--------------|--------------------|----------------------|---------------|

| EL5202IYZ (Note 2)         | BAAAD        | -40 to +85         | 10 Ld MSOP (3.0mm)   | M10.118A      |

| EL5202IYZ-T7 (Notes 1, 2)  | BAAAD        | -40 to +85         | 10 Ld MSOP (3.0mm)   | M10.118A      |

| EL5202IYZ-T13 (Notes 1, 2) | BAAAD        | -40 to +85         | 10 Ld MSOP (3.0mm)   | M10.118A      |

| EL5203ISZ (Note 2)         | 5203ISZ      | -40 to +85         | 8 Ld SOIC (150 mil)  | M8.15E        |

| EL5203ISZ-T7 (Notes 1, 2)  | 5203ISZ      | -40 to +85         | 8 Ld SOIC (150 mil)  | M8.15E        |

| EL5203ISZ-T13 (Notes 1, 2) | 5203ISZ      | -40 to +85         | 8 Ld SOIC (150 mil)  | M8.15E        |

| EL5203IYZ (Note 2)         | BAAAE        | -40 to +85         | 8 Ld MSOP (3.0mm)    | M8.118A       |

| EL5203IYZ-T7 (Notes 1, 2)  | BAAAE        | -40 to +85         | 8 Ld MSOP (3.0mm)    | M8.118A       |

| EL5203IYZ-T13 (Notes 1, 2) | BAAAE        | -40 to +85         | 8 Ld MSOP (3.0mm)    | M8.118A       |

NOTES:

1. Please refer to TB347 for details on reel specifications.

2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), please see product information page for <u>EL5202</u>, <u>EL5203</u>. For more information on MSL, please see tech brief <u>TB363</u>.

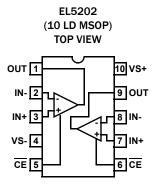

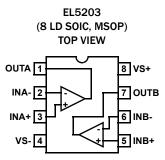

## **Pin Configurations**

#### Absolute Maximum Ratings (T<sub>A</sub> = +25°C)

| Supply Voltage between V <sub>S</sub> + and V <sub>S</sub>                       | 13.2V           |

|----------------------------------------------------------------------------------|-----------------|

| Maximum Supply Slew Rate between V <sub>S</sub> + and V <sub>S<sup>-</sup></sub> | 1V/µs           |

| Input Voltage                                                                    | ±V <sub>S</sub> |

| Differential Input Voltage                                                       | ±4V             |

| Maximum Continuous Output Current                                                | 80mA            |

| Maximum Current into I <sub>N</sub> +, I <sub>N</sub> -, CE                      | ±5mA            |

#### **Thermal Information**

| Thermal Resistance (Typical)             | $\theta_{JA}$ (°C/W) | θ <sub>JC</sub> (°C/W) |

|------------------------------------------|----------------------|------------------------|

| 10 Ld MSOP Package (Notes 4, 5)          | 160                  | 75                     |

| 8 Ld SOIC Package (Notes 4, 5)           | 125                  | 75                     |

| 8 Ld MSOP Package (Notes 4, 5)           | 170                  | 80                     |

| Storage Temperature Range                | 6                    | 5°C to +150°C          |

| Ambient Operating Temperature Range      |                      | 40°C to +85°C          |

| Operating Junction Temperature           |                      | +150°C                 |

| Pb-Free Reflow Profile                   |                      | . see link below       |

| http://www.intersil.com/pbfree/Pb-FreeRe | eflow.asp            |                        |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

4.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

5. For  $\theta_{\text{JC}},$  the "case temp" location is taken at the package top center.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

| PARAMETER            | DESCRIPTION                                  | CONDITIONS                                              | MIN<br>(Note 9)       | ТҮР  | MAX<br>(Note 9)       | UNIT   |

|----------------------|----------------------------------------------|---------------------------------------------------------|-----------------------|------|-----------------------|--------|

| V <sub>OS</sub>      | Offset Voltage                               |                                                         |                       | 1    | 5                     | mV     |

| TCV <sub>OS</sub>    | Offset Voltage Temperature Coefficient       | Measured from T <sub>MIN</sub> to T <sub>MAX</sub>      |                       | 10   |                       | μV∕°C  |

| IB                   | Input Bias Current                           | V <sub>IN</sub> = OV                                    | -12                   | 2    | 12                    | μΑ     |

| I <sub>OS</sub>      | Input Offset Current                         | V <sub>IN</sub> = OV                                    | -8                    | 1    | 8                     | μΑ     |

| TCI <sub>OS</sub>    | Input Bias Current Temperature Coefficient   | Measured from T <sub>MIN</sub> to T <sub>MAX</sub>      |                       | 50   |                       | nA∕ °C |

| PSRR                 | Power Supply Rejection Ratio                 | $V_{S} = \pm 4.75V$ to $\pm 5.25V$                      | -70                   | -80  |                       | dB     |

| CMRR                 | Common Mode Rejection Ratio                  | V <sub>CM</sub> = -3V to 3.0V                           | -60                   | -80  |                       | dB     |

| CMIR                 | Common Mode Input Range                      | Guaranteed by CMRR test                                 | -3                    | ±3.3 | 3                     | v      |

| R <sub>IN</sub>      | Input Resistance                             | Common mode                                             | 200                   | 400  |                       | kΩ     |

| C <sub>IN</sub>      | Input Capacitance                            | SO package                                              |                       | 1    |                       | pF     |

| I <sub>S,ON</sub>    | Supply Current - Enabled, Per Amplifier      |                                                         | 4.6                   | 5.2  | 5.8                   | mA     |

| I <sub>S,OFF</sub>   | Supply Current - Shut-down,<br>Per Amplifier | V <sub>S</sub> +                                        | +1                    | +9   | +25                   | μA     |

|                      |                                              | V <sub>S</sub> -                                        | -25                   | -13  | -1                    | μA     |

| AVOL                 | Open Loop Gain                               | $V_{OUT}$ = ±2.5V, R <sub>L</sub> = 1k $\Omega$ to GND  | 58                    | 66   |                       | dB     |

|                      |                                              | $V_{OUT}$ = ±2.5V, R <sub>L</sub> = 150 $\Omega$ to GND |                       | 60   |                       | dB     |

| V <sub>OUT</sub>     | Output Voltage Swing                         | $R_L = 1 k\Omega$ to GND                                | ±3.5                  | ±3.9 |                       | v      |

|                      |                                              | $R_L = 150\Omega$ to GND                                | ±3.4                  | ±3.7 |                       | v      |

| IOUT                 | Output Current                               | $A_V = 1, R_L = 10\Omega$ to 0V                         | ±80                   | ±150 |                       | mA     |

| V <sub>CE</sub> -ON  | CE Pin Voltage for Power-up                  |                                                         | (V <sub>S</sub> +) -5 |      | (V <sub>S</sub> +) -3 | v      |

| V <sub>CE</sub> -OFF | CE Pin Voltage for Shut-down                 |                                                         | (V <sub>S</sub> +) -1 |      | V <sub>S</sub> +      | v      |

| ICE-ON               | CE Pin Current - Enabled                     | CE = OV                                                 | -1                    | 0    | +1                    | μA     |

| ICE-OFF              | CE Pin Current - Disabled                    | <u>CE</u> = +5V                                         | 1                     | 14   | 25                    | μA     |

#### **DC Electrical Specifications** MV<sub>S</sub>+ = +5V, V<sub>S</sub>- = -5V, T<sub>A</sub> = +25°C, R<sub>L</sub> = 500 $\Omega$ , V<sub>CE</sub> = 0V, Unless Otherwise Specified.

**Closed Loop AC Electrical Specifications**  $V_S$ + = +5V,  $V_{S^-}$  = -5V,  $T_A$  = +25°C,  $V_{\overline{CE}}$  = 0V,  $A_V$  = +1,  $R_F$  = 0 $\Omega$ ,  $R_L$  = 150 $\Omega$  to GND, Unless Otherwise Specified. (Note 6)

| PARAMETER                      | DESCRIPTION                                               | CONDITIONS                                                       | MIN<br>(Note 9) | TYP  | MAX<br>(Note 9) | UNIT   |

|--------------------------------|-----------------------------------------------------------|------------------------------------------------------------------|-----------------|------|-----------------|--------|

| BW                             | -3dB Bandwidth (V <sub>OUT</sub> = 400mV <sub>P-P</sub> ) | $A_V = 1$ , $R_F = 0\Omega$                                      |                 | 400  |                 | MHz    |

| SR                             | Slew Rate                                                 | $A_V = +2$ , $R_L = 100\Omega$ , $V_{OUT} = -3V$ to $+3V$        | 1100            | 2200 | 5000            | V/µs   |

|                                |                                                           | $R_{L} = 500\Omega, V_{OUT} = -3V \text{ to } +3V$               |                 | 4000 |                 | V/µs   |

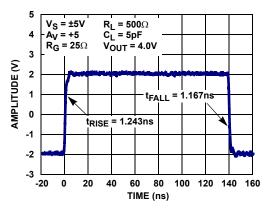

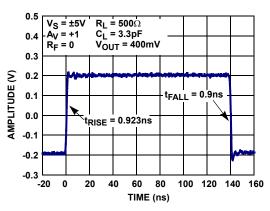

| t <sub>R</sub> ,t <sub>F</sub> | Rise Time, Fall Time                                      | ±0.1V step                                                       |                 | 2.8  |                 | ns     |

| OS                             | Overshoot                                                 | ±0.1V step                                                       |                 | 10   |                 | %      |

| t <sub>S</sub>                 | 0.1% Settling Time                                        | $V_{S} = \pm 5V, R_{L} = 500\Omega, A_{V} = 1, V_{OUT} = \pm 3V$ |                 | 20   |                 | ns     |

| dG                             | Differential Gain (Note 7)                                | $A_V = 2$ , $R_F = 1$ k $\Omega$                                 |                 | 0.01 |                 | %      |

| dP                             | Differential Phase (Note 7)                               | $A_V = 2$ , $R_F = 1$ k $\Omega$                                 |                 | 0.01 |                 | 0      |

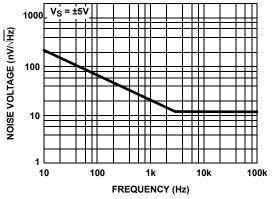

| e <sub>N</sub>                 | Input Noise Voltage                                       | f = 10kHz                                                        |                 | 12   |                 | nV/√Hz |

| i <sub>N</sub>                 | Input Noise Current                                       | f = 10kHz                                                        |                 | 11   |                 | pA∕√Hz |

| t <sub>DIS</sub>               | Disable Time (Note 8)                                     |                                                                  |                 | 50   |                 | ns     |

| t <sub>EN</sub>                | Enable Time (Note 8)                                      |                                                                  |                 | 25   |                 | ns     |

NOTES:

6. All AC tests are performed on a "warmed up" part, except slew rate, which is pulse tested.

7. Standard NTSC signal =  $286mV_{P,P}$ , f = 3.58MHz, as  $V_{IN}$  is swept from 0.6V to  $1.314V.R_L$  is DC coupled.

8. Disable/Enable time is defined as the time from when the logic signal is applied to the  $\overline{CE}$  pin to when the supply current has reached half its final value.

9. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

### **Typical Performance Curves**

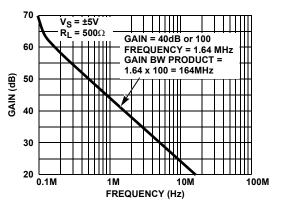

FIGURE 1. GAIN vs FREQUENCY (-3dB BANDWIDTH)

FIGURE 3. 0.1dB BANDWIDTH

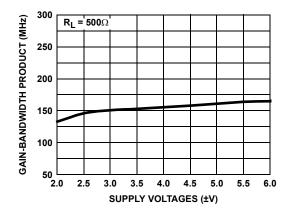

FIGURE 5. GAIN BANDWIDTH PRODUCT vs SUPPLY VOLTAGES

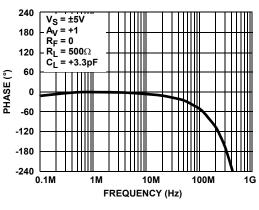

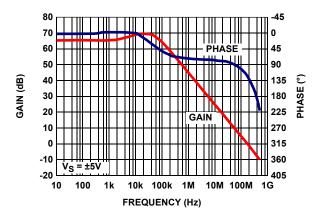

FIGURE 2. PHASE vs FREQUENCY

FIGURE 4. GAIN BANDWIDTH PRODUCT

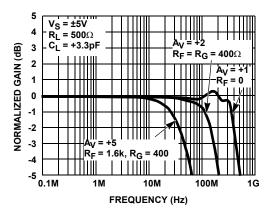

FIGURE 6. GAIN vs FREQUENCY FOR VARIOUS +A $_{\rm V}$

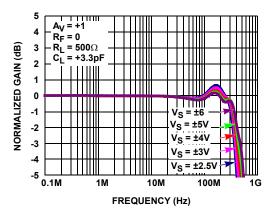

FIGURE 7. GAIN vs FREQUENCY FOR VARIOUS ±VS

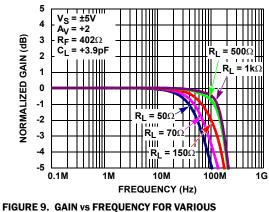

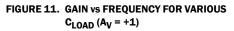

FIGURE 8. GAIN vs FREQUENCY FOR VARIOUS  $R_{LOAD} \, (A_V = +1)$

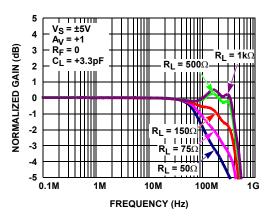

FIGURE 10. GAIN vs FREQUENCY FOR VARIOUS  $R_{LOAD} (A_V = +5)$

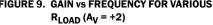

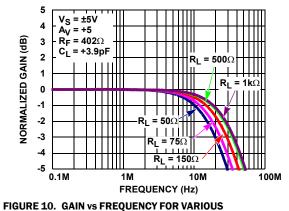

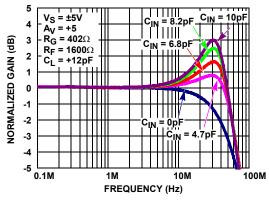

FIGURE 12. GAIN vs FREQUENCY FOR VARIOUS  $\label{eq:cload} C_{LOAD} \, (A_V = +2)$

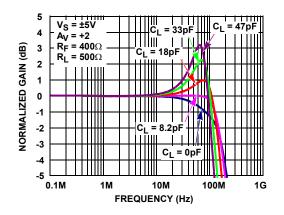

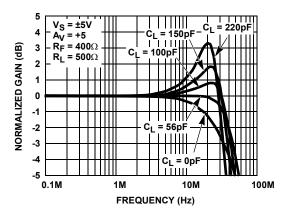

FIGURE 13. GAIN vs FREQUENCY FOR VARIOUS  $C_{LOAD}$  (A<sub>V</sub> = +5)

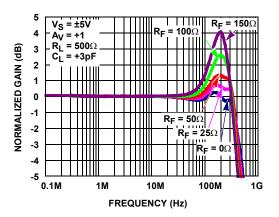

FIGURE 15. GAIN vs FREQUENCY FOR VARIOUS  $R_F (A_V = +2)$

FIGURE 14. GAIN vs FREQUENCY FOR VARIOUS R<sub>F</sub> (A<sub>V</sub> = +1)

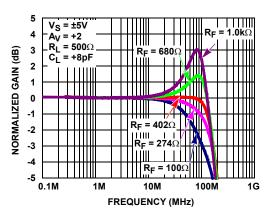

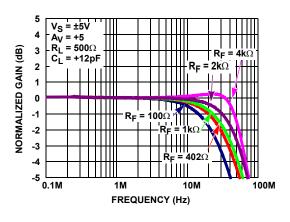

FIGURE 16. GAIN vs FREQUENCY FOR VARIOUS  $R_F (A_V = +5)$

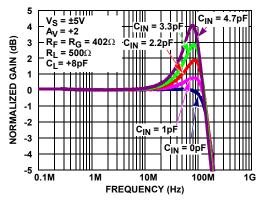

FIGURE 19. OPEN LOOP GAIN AND PHASE vs FREQUENCY

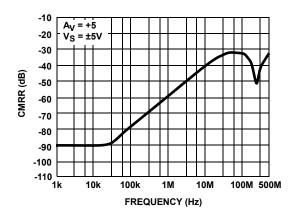

FIGURE 21. CMRR vs FREQUENCY

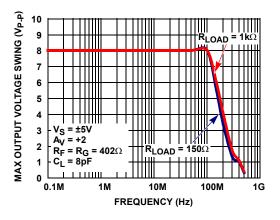

FIGURE 23. MAX OUTPUT VOLTAGE SWING vs FREQUENCY

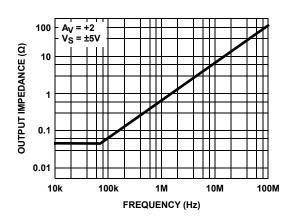

FIGURE 20. OUTPUT IMPEDANCE vs FREQUENCY

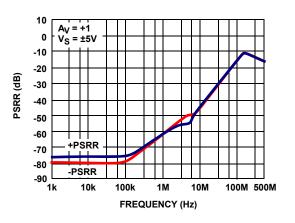

FIGURE 22. PSRR vs FREQUENCY

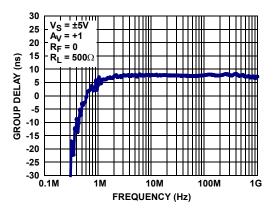

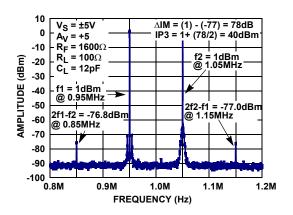

FIGURE 24. GROUP DELAY vs FREQUENCY

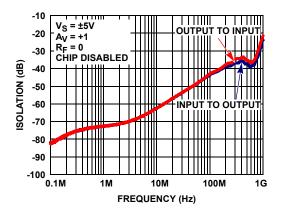

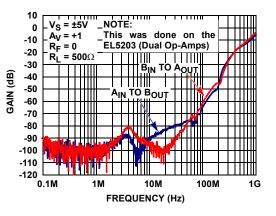

FIGURE 25. INPUT AND OUTPUT ISOLATION

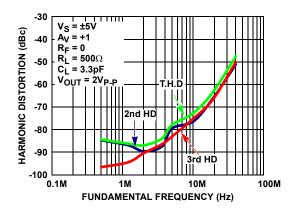

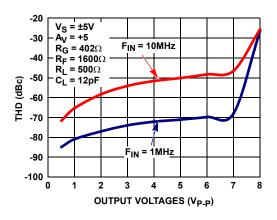

FIGURE 27. HARMONIC DISTORTION vs FREQUENCY

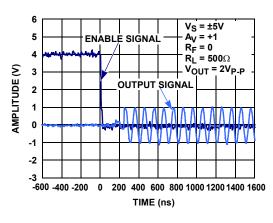

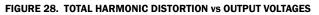

FIGURE 29. TURN-ON TIME

FIGURE 26. CHANNEL-TO-CHANNEL ISOLATION

FIGURE 30. TURN-OFF TIME

FIGURE 31. EQUIVALENT NOISE VOLTAGE vs FREQUENCY

FIGURE 33. LARGE SIGNAL STEP RESPONSE RISE AND FALL TIME

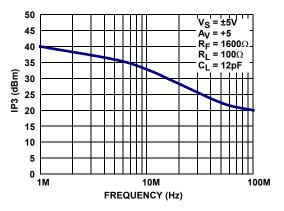

FIGURE 35. THIRD ORDER IMD INTERCEPT (IP3)

FIGURE 32. SMALL SIGNAL STEP RESPONSE RISE AND FALL TIME

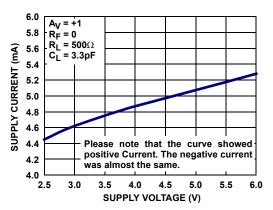

FIGURE 34. SUPPLY CURRENT vs SUPPLY VOLTAGE

FIGURE 36. THIRD ORDER IMD INTERCEPT vs FREQUENCY

© Copyright Intersil Americas LLC 2002-2014. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="http://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN7331 Rev 9.00 January 17, 2014

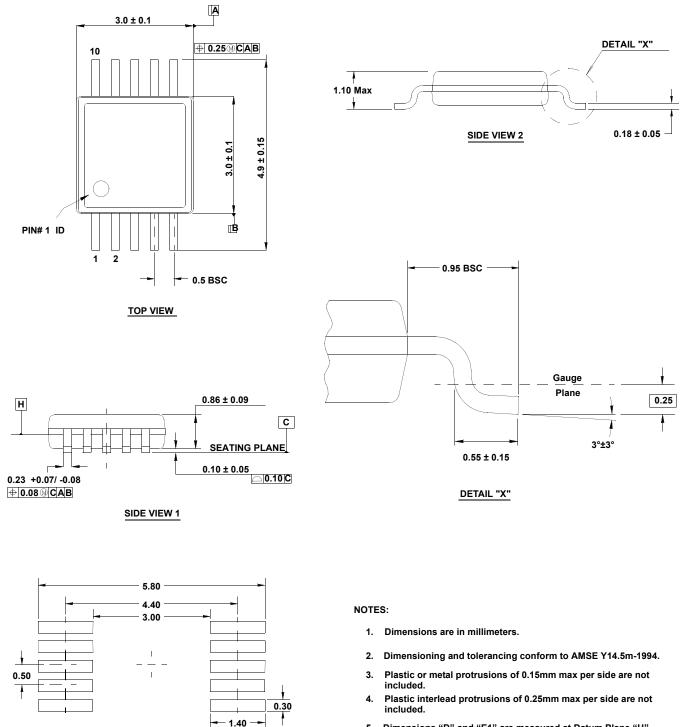

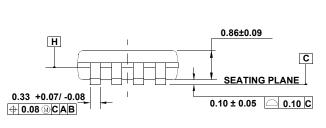

### Package Outline Drawing

M10.118A (JEDEC MO-187-BA)

10 LEAD MINI SMALL OUTLINE PLASTIC PACKAGE (MSOP) Rev 0, 9/09

- 5. Dimensions "D" and "E1" are measured at Datum Plane "H".

- 6. This replaces existing drawing # MDP0043 MSOP10L.

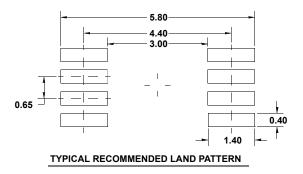

TYPICAL RECOMMENDED LAND PATTERN

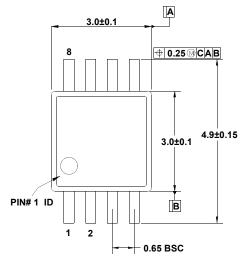

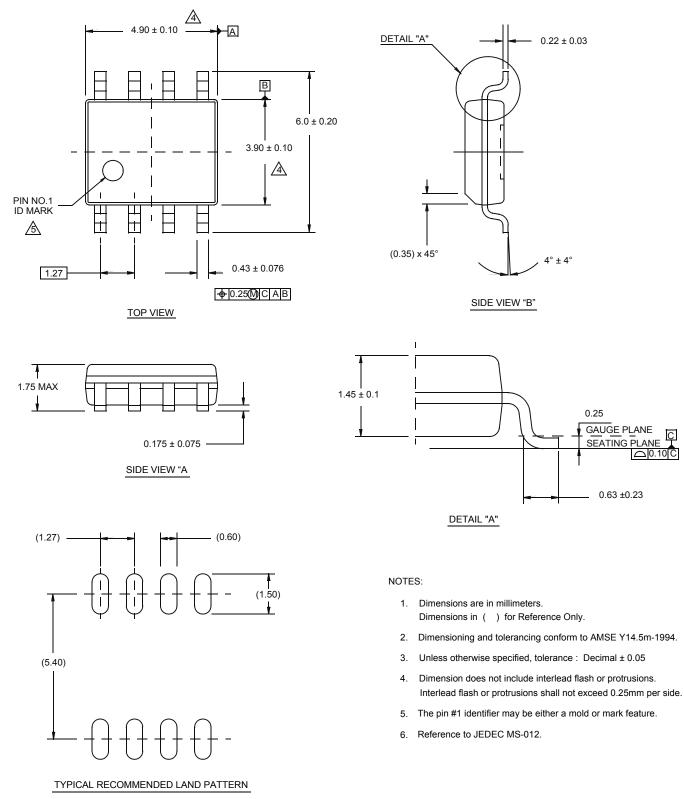

### Package Outline Drawing

#### M8.118A

8 LEAD MINI SMALL OUTLINE PLASTIC PACKAGE (MSOP) Rev 0, 9/09

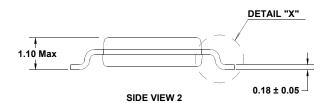

SIDE VIEW 1

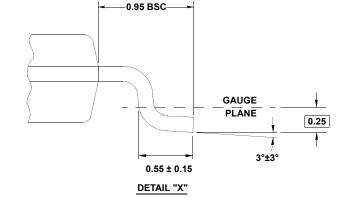

#### NOTES:

- 1. Dimensions are in millimeters.

- 2. Dimensioning and tolerancing conform to JEDEC MO-187-AA and AMSE Y14.5m-1994.

- 3. Plastic or metal protrusions of 0.15mm max per side are not included.

- 4. Plastic interlead protrusions of 0.25mm max per side are not included.

- 5. Dimensions "D" and "E1" are measured at Datum Plane "H".

- 6. This replaces existing drawing # MDP0043 MSOP 8L.

# Package Outline Drawing

#### M8.15E

8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE Rev 0, 08/09

0.10C