# FlexRay® Bus Driver

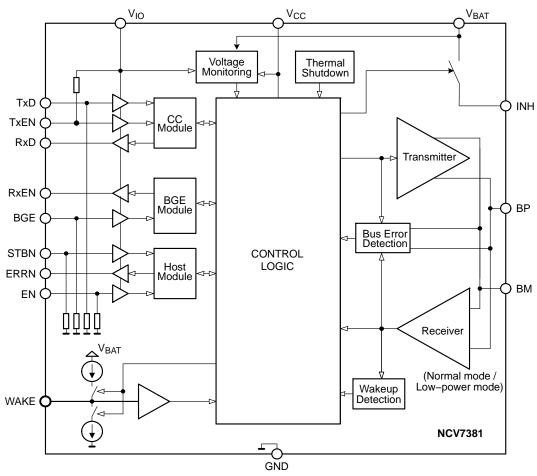

NCV7381 is a single-channel FlexRay bus driver compliant with the FlexRay Electrical Physical Layer Specification Rev. 3.0.1, capable of communicating at speeds of up to 10 Mbit/s. It provides differential transmit and receive capability between a wired FlexRay communication medium on one side and a protocol controller and a host on the other side.

NCV7381 mode control functionality is optimized for nodes permanently connected to car battery.

It offers excellent EMC and ESD performance.

# KEY FEATURES General

- Compliant with FlexRay Electrical Physical Layer Specification Rev 3 0 1

- FlexRay Transmitter and Receiver in Normal–power Modes for Communication up to 10 Mbit/s

- Support of 60 ns Bit Time

- FlexRay Low-power Mode Receiver for Remote Wakeup Detection

- Excellent Electromagnetic Susceptibility (EMS) Level over Full Frequency Range. Very Low Electromagnetic Emissions (EME)

- Bus Pins Protected against >10 kV System ESD Pulses

- Safe Behavior under Missing Supply or No Supply Conditions

- Interface Pins for a Protocol Controller and a Host (TxD, RxD, TxEN, RxEN, STBN, BGE, EN, ERRN)

- INH Output for Control of External Regulators

- Local Wakeup Pin WAKE

- TxEN Time-out

- BGE Feedback

- Supply Pins V<sub>BAT</sub>, V<sub>CC</sub>, V<sub>IO</sub> with Independent Voltage Ramp Up:

- ◆ V<sub>BAT</sub> Supply Parametrical Range from 5.5 V to 50 V

- V<sub>CC</sub> Supply Parametrical Range from 4.75 V to 5.25 V

- V<sub>IO</sub> Supply Parametrical Range from 2.3 V to 5.25 V

- Compatible with 14 V and 28 V Systems

- Operating Ambient Temperature –40°C to +125°C (T<sub>AMB\_Class1</sub>)

- Junction Temperature Monitoring with Two Levels

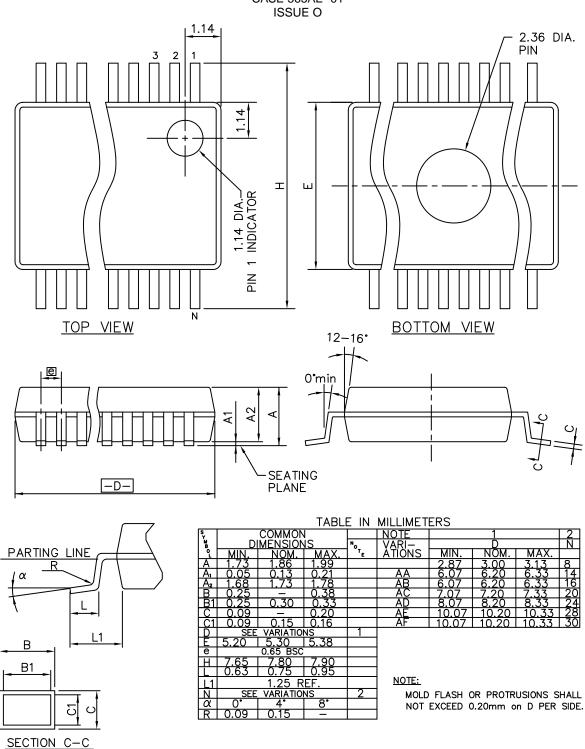

- SSOP-16 Package

#### FlexRay Functional Classes

- Bus Driver Voltage Regulator Control

- Bus Driver Bus Guardian Interface

- Bus Driver Logic Level Adaptation

- Bus Driver Remote Wakeup

#### Quality

NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

#### ON Semiconductor®

http://onsemi.com

SSOP-16 DP SUFFIX CASE 565AE

#### **MARKING DIAGRAM**

A = Assembly Location WL = Wafer Lot

YYWW = Year / Work Week ■ = Pb-Free Package

PIN CONNECTIONS

# INH VCC BP VIO BP STBN VAKE ERRN RXEN

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 23 of this data sheet.

Figure 1. Block Diagram

**Table 1. PIN DESCRIPTION**

| Pin<br>Number | Pin<br>Name     | Pin Type                         | Pin Function                                                                          |

|---------------|-----------------|----------------------------------|---------------------------------------------------------------------------------------|

| 1             | INH             | high-voltage analog output       | External regulator control output                                                     |

| 2             | EN              | digital input                    | Mode control input; internal pull-down resistor                                       |

| 3             | V <sub>IO</sub> | supply                           | Supply voltage for digital pins level adaptation                                      |

| 4             | TxD             | digital input                    | Data to be transmitted; internal pull-down resistor                                   |

| 5             | TxEN            | digital input                    | Transmitter enable input; when High transmitter disabled; internal pull-up resistor   |

| 6             | RxD             | digital output                   | Receive data output                                                                   |

| 7             | BGE             | digital input                    | Bus guardian enable input; when Low transmitter disabled; internal pull-down resistor |

| 8             | STBN            | digital input                    | Mode control input; internal pull-down resistor                                       |

| 9             | RxEN            | digital output                   | Bus activity detection output; when Low bus activity detected                         |

| 10            | ERRN            | digital output                   | Error diagnosis and status output                                                     |

| 11            | $V_{BAT}$       | supply                           | Battery supply voltage                                                                |

| 12            | WAKE            | high-voltage analog input        | Local wake up input; internal pull up or pull down (depends on voltage at pin WAKE)   |

| 13            | GND             | ground                           | Ground connection                                                                     |

| 14            | BM              | high-voltage analog input/output | Bus line minus                                                                        |

| 15            | BP              | high-voltage analog input/output | Bus line plus                                                                         |

| 16            | V <sub>CC</sub> | supply                           | Bus driver core supply voltage; 5 V nominal                                           |

#### **APPLICATION INFORMATION**

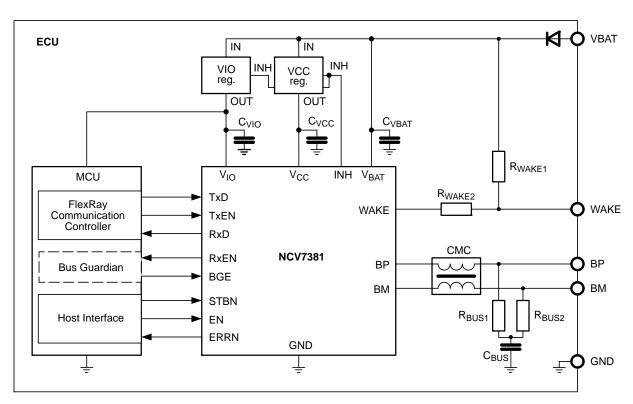

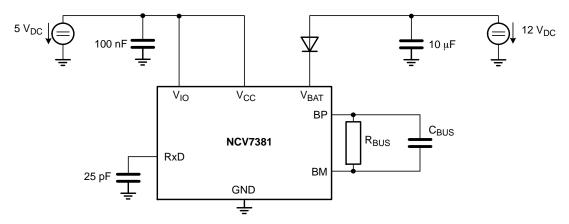

Figure 2. Application Diagram

Table 2. RECOMMENDED EXTERNAL COMPONENTS FOR THE APPLICATION DIAGRAM

| Component          | Function                                                     | Min | Тур  | Max | Unit |

|--------------------|--------------------------------------------------------------|-----|------|-----|------|

| C <sub>VBAT</sub>  | Decoupling capacitor on battery line, ceramic                |     | 100  |     | nF   |

| C <sub>VCC</sub>   | Decoupling capacitor on V <sub>CC</sub> supply line, ceramic |     | 100  |     | nF   |

| C <sub>VIO</sub>   | Decoupling capacitor on V <sub>IO</sub> supply line, ceramic |     | 100  |     | nF   |

| R <sub>WAKE1</sub> | Pull-up resistor on WAKE pin                                 |     | 33   |     | kΩ   |

| R <sub>WAKE2</sub> | Serial protection resistor on WAKE pin                       |     | 3.3  |     | kΩ   |

| R <sub>BUS1</sub>  | Bus termination resistor (Note 1)                            |     | 47.5 |     | Ω    |

| R <sub>BUS2</sub>  | Bus termination resistor (Note 1)                            |     | 47.5 |     | Ω    |

| C <sub>BUS</sub>   | Common–mode stabilizing capacitor, ceramic (Note 2)          |     | 4.7  |     | nF   |

| CMC                | Common-mode choke                                            |     | 100  |     | μН   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

- 1. Tolerance ±1%, type 0805

- 2. Tolerance ±20%, type 0805

#### **FUNCTIONAL DESCRIPTION**

#### **Operating Modes**

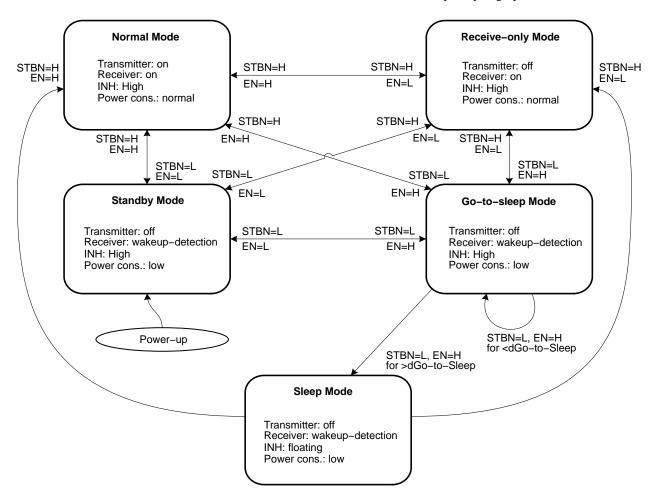

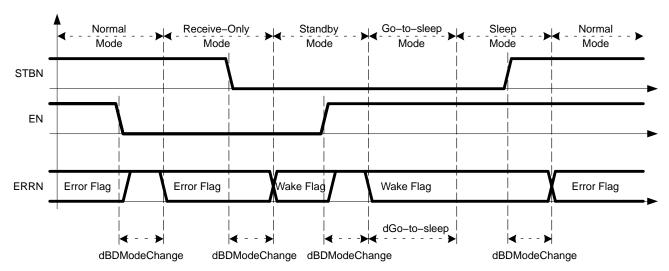

NCV7381 can switch between several operating modes depicted in Figure 3. In Normal and Receive—only modes, the chip interconnects a FlexRay communication controller with the bus medium for full—speed communication. These two modes are also referred to as normal—power modes.

In Standby and Sleep modes, the communication is suspended and the power consumption is substantially reduced. A wakeup on the bus or through a locally monitored signal on pin WAKE can be detected and signaled to the host. Go-to-sleep mode is a temporary mode ensuring

correct transition between any mode and the Sleep mode. All three modes – Standby, Sleep and Go–to–sleep – are referred to as low–power modes.

The operating mode selected is a function of the host signals STBN and EN, the state of the supply voltages and the wakeup detection. As long as all three supplies ( $V_{BAT}$ ,  $V_{CC}$ ,  $V_{IO}$ ) remain above their respective under–voltage detection levels, the logical control by EN and STBN pins shown in Figure 3 applies. Influence of the power–supplies and of the wakeup detection on the operating modes is described in subsequent paragraphs.

Figure 3. Operating Modes and their Control by the STBN and EN Pins

Figure 4. Timing Diagram of Operating Modes Control by the STBN and EN Pins

### **Power Supplies and Power Supply Monitoring**

NCV7381 is supplied by three pins.  $V_{BAT}$  is the main supply both for NCV7381 and the full electronic module.  $V_{BAT}$  will be typically connected to the automobile battery through a reverse–polarity protection.  $V_{CC}$  is a 5 V low–voltage supply primarily powering the FlexRay bus driver core in a normal–power mode.  $V_{IO}$  supply serves to adapt the logical levels of NCV7381 to the host and/or the FlexRay communication controller digital signal levels. All supplies should be properly decoupled by filtering capacitors – see Figure 2 and Table 2.

All three supplies are monitored by under-voltage detectors with individual thresholds and filtering times both for under-voltage detection and recovery – see Table 18.

#### **Logic Level Adaptation**

Level shift input  $V_{IO}$  is used to apply a reference voltage  $uV_{DIG} = uV_{IO}$  to all digital inputs and outputs in order to adapt the logical levels of NCV7381 to the host and/or the FlexRay communication controller digital signal levels

# **Internal Flags**

The NCV7381 control logic uses a number of internal flags (i.e. one–bit memories) reflecting important conditions or events. Table 3 summarizes the individual flags and the conditions that lead to a set or reset of the flags.

#### **Table 3. INTERNAL FLAGS**

| Flag                               | Set Condition                                                                                                                                                                                               | Reset Condition                                                                                                                                                                                                     | Comment                                                                   |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Local<br>Wakeup                    | Low level detected on WAKE pin in a low-<br>power mode                                                                                                                                                      | Low–power mode is entered                                                                                                                                                                                           |                                                                           |

| Remote<br>Wakeup                   | Remote wakeup detected on the bus in a low–power mode                                                                                                                                                       | Low–power mode is entered                                                                                                                                                                                           |                                                                           |

| Wakeup                             | Local Wakeup flag changes to set or Remote Wakeup flag changes to set                                                                                                                                       | Normal mode is entered or Low–power mode is entered or Any under–voltage flag becomes set                                                                                                                           |                                                                           |

| Power-on                           | Internal power supply of the chip becomes sufficient for the operation of the control logic                                                                                                                 | Normal mode is entered                                                                                                                                                                                              |                                                                           |

| Thermal<br>Warning                 | Junction temperature is higher than <i>Tjw</i> (typ. 140°C) in a normal–power mode and V <sub>BAT</sub> is not in under–voltage                                                                             | (Junction temperature is below <i>Tjw</i> in a normal–power mode or the status register is read in a low–power mode) and V <sub>BAT</sub> is not in under–voltage                                                   | The thermal warning flag has no influence on the bus driver function      |

| Thermal<br>Shutdown                | Junction temperature is higher than <i>Tjsd</i> (typ. 165°C) in a normal–power mode and V <sub>BAT</sub> is not in under–voltage                                                                            | Junction temperature is below <i>Tjsd</i> in a normal–power mode and falling edge on TxEN and V <sub>BAT</sub> is not in under–voltage                                                                              | The transmitter is disabled as long as the thermal shutdown flag is set   |

| TxEN<br>Timeout                    | TxEN is Low for longer than dBDTxActiveMax (typ. 1.5 ms) and bus driver is in Normal mode                                                                                                                   | TxEN is High or Normal mode is left                                                                                                                                                                                 | The transmitter is disabled as long as the timeout flag is set            |

| Bus Error                          | Transmitter is enabled and Data on bus are different from TxD signal (sampled after each TXD edge)                                                                                                          | (Transmitter is enabled and Data on bus are identical to TxD signal) or Transmitter is disabled                                                                                                                     | The bus error flag<br>has no influence on<br>the bus driver func-<br>tion |

| V <sub>BAT</sub> Under–<br>voltage | $\rm V_{BAT}$ is below the under–voltage threshold for longer than dBDUVV_{BAT}                                                                                                                             | V <sub>BAT</sub> is above the under–voltage threshold<br>for longer than dBDRV <sub>BAT</sub><br>or<br>Wake flag becomes set                                                                                        |                                                                           |

| V <sub>CC</sub> Under-<br>voltage  | $\ensuremath{\text{V}_{\text{CC}}}$ is below the under–voltage threshold for longer than dBDUVV $_{\text{CC}}$                                                                                              | V <sub>CC</sub> is above the under–voltage threshold for longer than dBDRV <sub>CC</sub> or Wake flag becomes set                                                                                                   |                                                                           |

| V <sub>IO</sub> Under-<br>voltage  | $\rm V_{IO}$ is below the under–voltage threshold for longer than $\rm dUV_{IO}$                                                                                                                            | ${ m V_{IO}}$ is above the under–voltage threshold for longer than ${ m dBDRV_{IO}}$ or Wake flag becomes set                                                                                                       |                                                                           |

| Error                              | Any of the following status bits is set:  • Bus error  • Thermal Warning • Thermal Shutdown • TxEN Timeout • V <sub>BAT</sub> Under–voltage • V <sub>CC</sub> Under–voltage • V <sub>IO</sub> Under–voltage | All of the following status bits are reset:  • Bus error  • Thermal Warning  • Thermal Shutdown  • TxEN Timeout  • V <sub>BAT</sub> Under–voltage  • V <sub>CC</sub> Under–voltage  • V <sub>IO</sub> Under–voltage |                                                                           |

#### **Operating Mode Changes Caused by Internal Flags**

Changes of some internal flags described in Table 3 can force an operating mode transition complementing or overruling the operating mode control by the digital inputs STBN and EN which is shown in Figure 3:

- Setting the V<sub>BAT</sub> or V<sub>IO</sub> under–voltage flag causes a transition to the Sleep mode

- Setting the V<sub>CC</sub> under-voltage flag, while the bus driver is not in Sleep, causes a transition to the Standby mode

- Reset of the Under-voltage flag (i.e. recovery from under-voltage) re-enables the control of the chip by digital inputs STBN and EN.

- Setting of the Wake flag causes the reset of all under-voltage flags and the NCV7381 transitions to the Standby mode. The reset of the under-voltage flags allows the external power supplies to stabilize properly if, for example, they were previously switched off during Sleep mode.

#### FlexRay Bus Driver

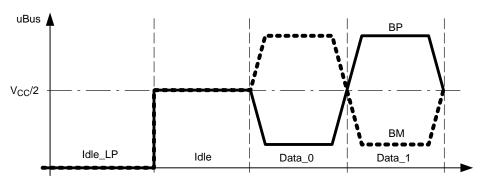

NCV7381 contains a fully—featured FlexRay bus driver compliant with Electrical Physical Layer Specification Rev. 3.0.1. The transmitter part translates logical signals on digital inputs TxEN, BGE and TxD into appropriate bus levels on pins BP and BM. A transmission cannot be started with Data\_1. In case the transmitter is enabled for longer than dBDTxActiveMax, the TxEN Timeout flag is set and the current transmission is disabled. The receiver part monitors bus pins BP and BM and signals the detected levels on digital outputs RxD and RxEN. The different bus levels are defined in Figure 5. The function of the bus driver and the related digital pins in different operating modes is detailed in Table 4 and Table 5.

- The transmitter can only be enabled if the activation of the transmitter is initiated in Normal mode.

- The receiver function is enabled by entering a normal–power mode.

Figure 5. FlexRay Bus Signals

Table 4. TRANSMITTER FUNCTION AND TRANSMITTER-RELATED PINS

| Operating Mode              | BGE | TxEN | TxD | Transmitted Bus Signal |

|-----------------------------|-----|------|-----|------------------------|

| Standby, Go-to-sleep, Sleep | х   | х    | х   | Idle_LP                |

| Receive-only                | х   | х    | х   | Idle                   |

| Normal                      | 0   | х    | х   | Idle                   |

|                             | 1   | 1    | х   | Idle                   |

|                             | 1   | 0    | 0   | Data_0                 |

|                             | 1   | 0    | 1   | Data_1                 |

Table 5. RECEIVER FUNCTION AND RECEIVER-RELATED PINS

| Operating Mode              | Signal on Bus | Wake flag | RxD  | RxEN |

|-----------------------------|---------------|-----------|------|------|

| Standby, Go-to-sleep, Sleep | х             | not set   | High | High |

|                             | Х             | set       | Low  | Low  |

| Normal,                     | Idle          | х         | High | High |

| Receive-only                | Data_0        | х         | Low  | Low  |

|                             | Data_1        | х         | High | Low  |

#### **Bus Guardian Interface**

The interface consists of the BGE digital input signal allowing a Bus Guardian unit to disable the transmitter and of the RxEN digital output signal used to signal whether the communication signal is Idle or not.

#### **Bus Driver Voltage Regulator Control**

NCV7381 provides a high–voltage output pin INH which can be used to control an external voltage regulator (see Figure 2). The pin INH is driven by a switch to  $V_{BAT}$  supply. In Normal, Receive–only, Standby and Go–to–Sleep modes, the switch is activated thus forcing a High level on pin INH. In the Sleep mode, the switch is open and INH pin remains floating. If a regulator is directly controlled by INH, it is then active in all operating modes with the exception of the Sleep mode.

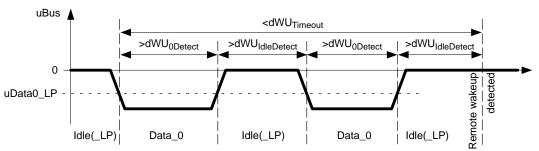

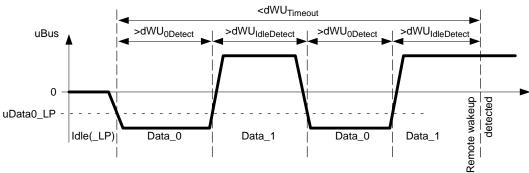

#### **Bus Driver Remote Wakeup Detection**

During a low-power mode and under the presence of V<sub>BAT</sub> voltage, a low-power receiver constantly monitors the activity on bus pins BP and BM. A valid remote wake-up is detected when either a wakeup pattern or a dedicated wakeup frame is received. A valid remote wake-up is also detected when wake-up pattern has been started in normal-power mode already.

A wakeup pattern is composed of two Data\_0 symbols separated by Data\_1 or Idle symbols. The basic wakeup pattern composed of Data\_0 and Idle symbols is shown in Figure 6; the wakeup pattern composed of Data\_0 and Data\_1 symbols – referred to as "alternative wakeup pattern" – is depicted in Figure 7.

Figure 6. Valid Remote Wakeup Pattern

Figure 7. Valid Alternative Remote Wakeup Pattern

A remote wakeup will be also detected if NCV7381 receives a full FlexRay frame at 10 Mbit/s with the following payload data:

0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0x00, 0x00, 0x00, 0x00, 0x00,

0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0x00, 0x00, 0x00, 0x00, 0x00,

0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0x00, 0x00, 0x00, 0x00, 0x00,

0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF

The wakeup pattern, the alternative wakeup pattern and the wakeup frame lead to identical wakeup treatment and signaling.

#### **Local Wakeup Detection**

The high-voltage input WAKE is monitored in low-power modes and under the condition of sufficient V<sub>BAT</sub> supply level. If a falling edge is recognized on WAKE pin, a local wakeup is detected. In order to avoid false wakeups, the Low level after the falling edge must be longer than *dWakePulseFilter* in order for the wakeup to be valid. The WAKE pin can be used, for example, for switch or contact monitoring.

Internal pull—up and pull—down current sources are connected to WAKE pin in order to minimize the risk of parasitic toggling. The current source polarity is automatically selected based on the WAKE input signal polarity — when the voltage on WAKE stays stable High (Low) for longer than *dWakePulseFilter*, the internal current source is switched to pull—up (pull—down).

#### **ERRN Pin and Status Register**

Provided  $V_{IO}$  supply is present together with either  $V_{BAT}$  or  $V_{CC}$ , the digital output ERRN indicates the state of the internal "Error" flag when in Normal mode and the state of the internal "Wake" flag when in Standby, Go–to–Sleep or Sleep. In Receive–only mode ERRN indicates either the

state of the internal "Error" or the wakeup source (See Table 6).

The polarity of the indication is reversed – ERRN pin is pulled Low when the "Error" flag is set. The signaling on pin ERRN functions in all operating modes.

**Table 6. SIGNALING ON ERRN PIN**

| STBN | EN   | Conditions                                        | Error flag | Wake flag  | ERRN |

|------|------|---------------------------------------------------|------------|------------|------|

| High | High | -                                                 | not set    | х          | High |

|      |      |                                                   | set        | х          | Low  |

| High | Low  | EN has been set to High after previous wakeup     | not set    | х          | High |

|      |      |                                                   | set        | х          | Low  |

|      |      | EN has not been set to High after previous wakeup | х          | Set local  | High |

|      |      |                                                   | х          | Set remote | Low  |

| Low  | х    | -                                                 | х          | not set    | High |

|      |      |                                                   | х          | set        | Low  |

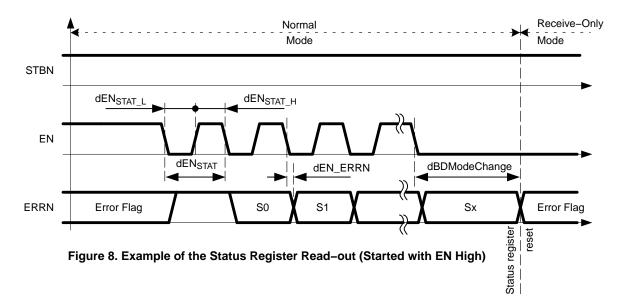

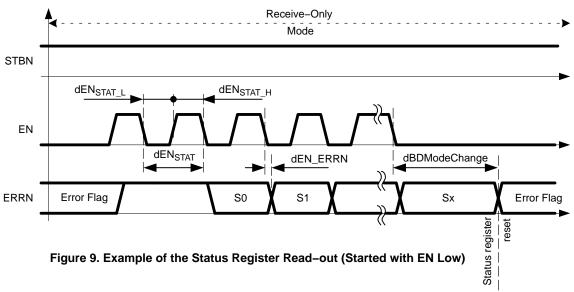

Additionally, a full set of internal bits referred to as status register can be read through ERRN pin with EN pin used as a clock signal – the status register content is described in Table 7 while an example of the read–out waveforms is shown in Figure 8 and Figure 9. The individual status bits are channeled to ERRN pin with reversed polarity (if a status bit is set, ERRN is pulled Low) at the falling edge on EN pin (the status register starts to be shifted only at the second falling edge). As long as the EN pin toggling period falls in the  $dEN_{STAT}$  range, the operating mode is not changed and the

read—out continues. As soon as the EN level is stable for more than *dBDModeChange*, the read—out is considered as finished and the operating mode is changed according the current EN value. At the same time, the status register bits S4 to S10 are reset provided the particular bits have been read—out and the corresponding flags are not set any more—see Table 7. The status register read—out always starts with bit S0 and the exact number of bits shifted to ERRN during the read—out is not relevant.

**Table 7. STATUS REGISTER**

| Bit Number | Status Bit Content                    | Note                                                                                             | Reset after Finished<br>Read-out               |

|------------|---------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------|

| S0         | Local wakeup flag                     | reflects directly the corresponding flag                                                         | no                                             |

| S1         | Remote wakeup flag                    |                                                                                                  |                                                |

| S2         | not used; always High                 |                                                                                                  | no                                             |

| S3         | Power-on status                       | the status bit is set if the corresponding flag                                                  | yes, if the                                    |

| S4         | Bus error status                      | was set previously (the respective High level of the flag is latched in its status counter–part) | corresponding flag is<br>reset and the bit was |

| S5         | Thermal shutdown status               |                                                                                                  | read-out                                       |

| S6         | Thermal warning status                |                                                                                                  |                                                |

| S7         | TxEN Timeout status                   |                                                                                                  |                                                |

| S8         | V <sub>BAT</sub> Under-voltage status |                                                                                                  |                                                |

| S9         | V <sub>CC</sub> Under-voltage status  |                                                                                                  |                                                |

| S10        | V <sub>IO</sub> Under-voltage status  |                                                                                                  |                                                |

| S11        | BGE Feedback                          | Normal mode: BGE pin logical state (Note 3)<br>Other modes: Low                                  | -                                              |

| S12-S15    | not used; always Low                  |                                                                                                  | no                                             |

| S16-S23    | Version of the NCV7381 analog part    | fixed values identifying the production masks                                                    | no                                             |

| S24-S31    | Version of the NCV7381 digital part   | version                                                                                          |                                                |

<sup>3.</sup> The BGE pin state is latched during status register read-out at rising edge of the EN pin.

Figure 9. Example of the Status Register Read-out (Started with EN Low)

**Table 8. ABSOLUTE MAXIMUM RATINGS**

| Symbol                    | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                               |                           | Min  | Max                   | Units |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|-----------------------|-------|

| uV <sub>BAT-MAX</sub>     | Battery voltage power supply                                                                                                                                                                                                                                                                                                                                                                                                            |                           | -0.3 | 50                    | V     |

| uV <sub>CC-MAX</sub>      | 5 V Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                      |                           | -0.3 | 5.5                   | V     |

| uV <sub>IO-MAX</sub>      | Supply voltage for V <sub>IO</sub> voltage level adaptation                                                                                                                                                                                                                                                                                                                                                                             |                           | -0.3 | 5.5                   | V     |

| uDigIn <sub>MAX</sub>     | DC voltage at digital inputs (BGE, EN, STBN, TXD, TXEN)                                                                                                                                                                                                                                                                                                                                                                                 |                           | -0.3 | 5.5                   | V     |

| uDigOut <sub>MAX</sub>    | DC voltage at digital outputs (ERRN, RxD, RxEN)                                                                                                                                                                                                                                                                                                                                                                                         |                           | -0.3 | V <sub>IO</sub> +0.3  | V     |

| iDigOut <sub>IN–MAX</sub> | Digital output pins input current (V <sub>IO</sub> = 0 V)                                                                                                                                                                                                                                                                                                                                                                               |                           | -10  | +10                   | mA    |

| uBM <sub>MAX</sub>        | DC voltage at pin BM                                                                                                                                                                                                                                                                                                                                                                                                                    |                           | -50  | 50                    | V     |

| uBP <sub>MAX</sub>        | DC voltage at pin BP                                                                                                                                                                                                                                                                                                                                                                                                                    |                           | -50  | 50                    | V     |

| uINH <sub>MAX</sub>       | DC voltage at pin INH                                                                                                                                                                                                                                                                                                                                                                                                                   |                           | -0.3 | V <sub>BAT</sub> +0.3 | V     |

| iINH <sub>MAX</sub>       | INH pin maximum load current                                                                                                                                                                                                                                                                                                                                                                                                            |                           | -10  | -                     | mA    |

| uWAKE <sub>MAX</sub>      | DC voltage at WAKE pin                                                                                                                                                                                                                                                                                                                                                                                                                  |                           | -0.3 | V <sub>BAT</sub> +0.3 | V     |

| $T_{J\_MAX}$              | Junction temperature                                                                                                                                                                                                                                                                                                                                                                                                                    |                           | -40  | 175                   | °C    |

| T <sub>STG</sub>          | Storage Temperature Range                                                                                                                                                                                                                                                                                                                                                                                                               |                           | -55  | 150                   | °C    |

| uESD <sub>IEC</sub>       | System HBM on pins BP and BM (as per IEC 61000–4–2; 150 pF / 330 $\Omega$ )                                                                                                                                                                                                                                                                                                                                                             |                           | -10  | +10                   | kV    |

| uESD <sub>EXT</sub>       | Component HBM on pins BP, BM, $V_{BAT}$ and WAKE (as per EIA–JESD22–A114–B; 100 pF / 1500 $\Omega$ )                                                                                                                                                                                                                                                                                                                                    |                           | -6   | +6                    | kV    |

| uESD <sub>INT</sub>       | Component HBM on all other pins (as per EIA–JESD22–A114–B; 100 pF / 1500 $\Omega$ )                                                                                                                                                                                                                                                                                                                                                     |                           | -4   | +4                    | kV    |

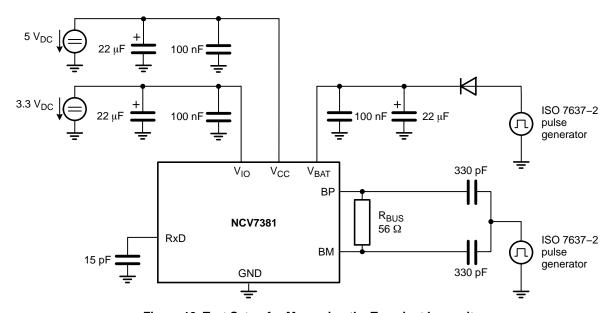

| uV <sub>TRAN</sub>        | Voltage transients, pins BP, BM, VBAT and WAKE.                                                                                                                                                                                                                                                                                                                                                                                         | test pulses 1             | -100 | -                     | V     |

|                           | According to ISO/637–2, Class C (Note 4)                                                                                                                                                                                                                                                                                                                                                                                                | test pulses 2a            | -    | +75                   | V     |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                         | test pulses 3a            | -150 | -                     | V     |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                         | test pulses 3b            | -    | +100                  | V     |

|                           | Voltage transients, pin VBAT.<br>According to ISO7637–2                                                                                                                                                                                                                                                                                                                                                                                 | test pulse 5<br>Load Dump | -    | 50                    | V     |

|                           | ESD <sub>IEC</sub> System HBM on pins BP and BM (as per IEC 61000–4–2; 150 pF / 330 Ω)  ESD <sub>EXT</sub> Component HBM on pins BP, BM, V <sub>BAT</sub> and WAKE (as per EIA–JESD22–A114–B; 100 pF / 1500 Ω)  ESD <sub>INT</sub> Component HBM on all other pins (as per EIA–JESD22–A114–B; 100 pF / 1500 Ω)  Voltage transients, pins BP, BM, VBAT and WAKE. According to ISO7637–2, Class C (Note 4)  Voltage transients, pin VBAT. | Jump Start                | -    | 50                    | V     |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### **Table 9. OPERATING RANGES**

| Symbol               | Parameter                                                              | Min  | Max             | Units |

|----------------------|------------------------------------------------------------------------|------|-----------------|-------|

| uV <sub>BAT-OP</sub> | Battery voltage power supply (Note 5)                                  | 5.5  | 50              | V     |

| uV <sub>CC-OP</sub>  | Supply voltage 5 V                                                     | 4.75 | 5.25            | V     |

| $uV_IO-OP$           | Supply voltage for V <sub>IO</sub> voltage level adaptation            | 2.3  | 5.25            | V     |

| uWAKE <sub>OP</sub>  | DC voltage at WAKE pin                                                 | 0    | $V_{BAT}$       | V     |

| uDigIO <sub>OP</sub> | DC voltage at digital pins (EN, TXD, TXEN, RXD, RXEN, BGE, STBN, ERRN) | 0    | V <sub>IO</sub> | V     |

| uBM <sub>OP</sub>    | DC voltage at pin BM                                                   | -50  | 50              | V     |

| uBP <sub>OP</sub>    | DC voltage at pin BP                                                   | -50  | 50              | V     |

| uINH <sub>OP</sub>   | DC voltage at pin INH                                                  | 0    | $V_{BAT}$       | V     |

| T <sub>AMB</sub>     | Ambient temperature (Note 6)                                           | -40  | 125             | °C    |

| T <sub>J_OP</sub>    | Junction temperature                                                   | -40  | 150             | °C    |

- Full functionality is guaranteed from 5.1 V. See also parameter uBDUVV<sub>BAT</sub>.

The specified range corresponds to T<sub>AMB\_Class1</sub>

Test is carried out according to setup in FlexRay Physical Layer EMC Measurement Specification, Version 3.0. This specification is referring to ISO7637. Test for higher voltages is planned.

#### THERMAL CHARACTERISTICS

Table 10. PACKAGE THERMAL RESISTANCE

| Symbol             | Rating                                             | Value | Unit |

|--------------------|----------------------------------------------------|-------|------|

| $R_{\theta JA\_1}$ | Thermal Resistance Junction-to-Air, JEDEC 1S0P PCB | 78    | °C/W |

| $R_{\theta JA\_2}$ | Thermal Resistance Junction-to-Air, JEDEC 2S2P PCB | 69    | °C/W |

#### **ELECTRICAL CHARACTERISTICS**

The characteristics defined in this section are guaranteed within the operating ranges listed in Table 9, unless otherwise specified. Positive currents flow into the respective pin.

**Table 11. CURRENT CONSUMPTION**

| Symbol                        | Parameter                                 | Conditions                                                                                                     | Min | Тур  | Max  | Unit |

|-------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| iV <sub>BAT-NORM</sub>        | Current consumption from V <sub>BAT</sub> | normal-power modes                                                                                             |     | 0.65 | 1.25 | mA   |

| iV <sub>BAT-LP</sub>          |                                           | low-power modes; T <sub>AMB</sub> =125°C                                                                       |     |      | 75   | μΑ   |

|                               |                                           | Sleep mode, $V_{IO} = V_{CC} = 0 \text{ V}$ ;<br>$T_{AMB} = 125^{\circ}\text{C}$                               |     |      | 80   | μΑ   |

|                               |                                           | low–power modes, $V_{IO}$ = $V_{CC}$ = 0 V, $V_{BAT}$ = 12 V, $T_{J}$ < 85°C (Note 7)                          |     |      | 55   | μΑ   |

| iV <sub>CC-NORM-IDLE</sub>    | Current consumption from V <sub>CC</sub>  | Normal mode – bus signals Idle                                                                                 |     |      | 15   | mA   |

| iV <sub>CC-NORM-</sub> ACTIVE |                                           | Normal mode – bus signals Data_0/1 $R_{BUS} = 40-55 \Omega$                                                    |     |      | 37   | mA   |

| iV <sub>CC-REC</sub>          |                                           | Receive-only mode                                                                                              |     |      | 15   | mA   |

| iV <sub>CC-LP</sub>           |                                           | low-power modes, T <sub>J</sub> < 85°C (Note 7)                                                                |     |      | 8    | μΑ   |

| iV <sub>IO-NORM</sub>         | Current consumption from V <sub>IO</sub>  | normal-power modes                                                                                             |     |      | 1    | mA   |

| iV <sub>IO-LP</sub>           |                                           | low-power modes, T <sub>J</sub> < 85°C (Note 7)                                                                |     |      | 6    | μΑ   |

| iTot_LP                       | Total current consumption –               | low–power modes; T <sub>AMB</sub> = 125°C                                                                      |     |      | 95   | μΑ   |

|                               | Sum from all supply pins                  | Sleep mode, $V_{IO} = V_{CC} = 5 \text{ V}$ , $V_{BAT} = 12 \text{ V}$ , $T_{J} < 85^{\circ}\text{C}$ (Note 7) |     |      | 65   | μΑ   |

|                               |                                           | Sleep mode, $V_{IO} = V_{CC} = 5 \text{ V}$ , $V_{BAT} = 12 \text{ V}$ , $T_{J} < 25^{\circ}\text{C}$ (Note 7) |     |      | 55   | μΑ   |

<sup>7.</sup> Values based on design and characterization, not tested in production

**Table 12. TRANSMISSION PARAMETERS**

| Symbol                                                         | Parameter                                                                               | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Min | Тур | Max   | Unit |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|------|

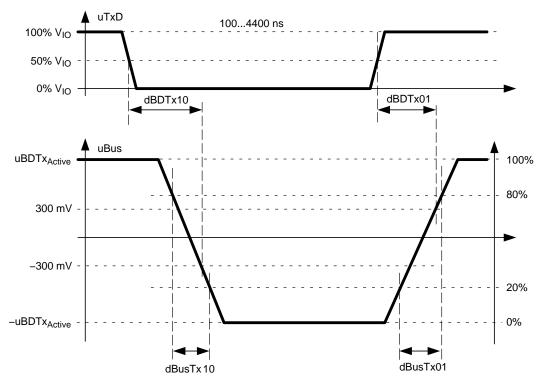

| uBDTx <sub>active</sub>                                        | Differential voltage  uBP-uBM  when sending symbol "Data_0" or "Data_1"                 | $R_{BUS} = 40-55 \Omega;$<br>$C_{BUS} = 100 pF$                                                                                                                                                                                                                                                                                                                                                                                                                       | 600 |     | 2000  | mV   |

| uBDTx <sub>Idle</sub>                                          | Differential voltage  uBP-uBM  when driving signal "Idle"                               | Parameters defined in Figure 10.                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0   |     | 30    | mV   |

| dBDTx10                                                        | Transmitter delay, negative edge                                                        | Test setup as per                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |     | 75    | ns   |

| dBDTx01                                                        | Transmitter delay, positive edge                                                        | Figure 17 with $R_{BUS} = 40 \Omega$ ;                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     | 75    | ns   |

| dBDTxAsym                                                      | Transmitter delay mismatch,<br> dBDTx10-dBDTx01  (Note 8)                               | Sum of TXD signal rise                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     | 4     | ns   |

| dBusTx10                                                       | Fall time of the differential bus voltage from 80% to 20%                               | (20%–80% V <sub>IO</sub> )<br>of up to 9 ns                                                                                                                                                                                                                                                                                                                                                                                                                           | 6   |     | 18.75 | ns   |

| dBusTx01                                                       | Rise time of the differential bus voltage from 20% to 80%                               | Parameters defined in Figure 10.                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6   |     | 18.75 | ns   |

| dBusTxDif                                                      | Differential bus voltage fall and rise time mismatch  dBusTx10-dBusTx01                 | $C_{BUS}$ = 100 pF  Parameters defined in Figure 10.  Test setup as per Figure 17 with R <sub>BUS</sub> = 40 Ω; C <sub>BUS</sub> = 100 pF  Sum of TXD signal rise and fall time (20%–80% V <sub>IO</sub> ) of up to 9 ns  Parameters defined in Figure 10.  Test setup as per Figure 17 with R <sub>BUS</sub> = 40 Ω; C <sub>BUS</sub> = 100 pF  Parameters defined in Figure 11.  RShortCircuit ≤ 1 Ω  RShortCircuit ≤ 1 Ω  RShortCircuit ≤ 1 Ω  RShortCircuit ≤ 1 Ω |     |     | 3     | ns   |

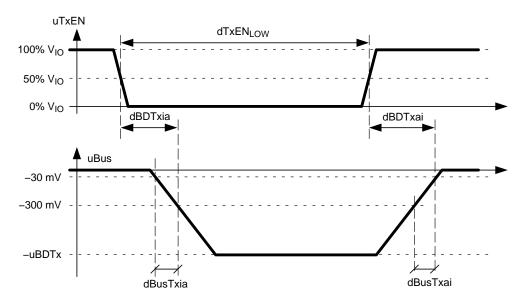

| dBDTxia                                                        | Transmitter delay idle -> active                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |     | 75    | ns   |

| dBDTxai                                                        | Transmitter delay active -> idle                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |     | 75    | ns   |

| dBDTxDM                                                        | Idle-active transmitter delay mismatch<br>  dBDTxia - dBDTxai                           | Figure 17 with  R <sub>BUS</sub> = 40 Ω;  C <sub>BUS</sub> = 100 pF  Parameters defined in                                                                                                                                                                                                                                                                                                                                                                            |     |     | 50    | ns   |

| dBusTxia                                                       | Transition time idle -> active                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |     | 30    | ns   |

| dBusTxai                                                       | Transition time active -> idle                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |     | 30    | ns   |

| dTxEN <sub>LOW</sub>                                           | Time span of bus activity                                                               | ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 550 |     | 650   | ns   |

| dBDTxActiveMax                                                 | Maximum length of transmitter activation                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 650 |     | 2600  | μS   |

| iBP <sub>BMShortMax</sub><br>iBM <sub>BPShortMax</sub>         | Absolute maximum output current when BP shorted to BM – no time limit                   | R <sub>ShortCircuit</sub> ≤ 1 Ω                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |     | 60    | mA   |

| iBP <sub>GNDShortMax</sub><br>iBM <sub>GNDShortMax</sub>       | Absolute maximum output current when shorted to GND – no time limit                     | R <sub>ShortCircuit</sub> ≤ 1 Ω                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |     | 60    | mA   |

| iBP <sub>–5VShortMax</sub><br>iBM <sub>–5VShortMax</sub>       | Absolute maximum output current when shorted to V <sub>BAT</sub> = -5 V - no time limit | R <sub>ShortCircuit</sub> ≤ 1 Ω                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |     | 60    | mA   |

| iBP <sub>BAT27</sub> ShortMax<br>iBM <sub>BAT27</sub> ShortMax | Absolute maximum output current when shorted to V <sub>BAT</sub> = 27 V – no time limit | R <sub>ShortCircuit</sub> ≤ 1 Ω                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |     | 60    | mA   |

| iBP <sub>BAT48</sub> ShortMax<br>iBM <sub>BAT48</sub> ShortMax | Absolute maximum output current when shorted to V <sub>BAT</sub> = 48 V – no time limit | R <sub>ShortCircuit</sub> ≤ 1 Ω                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |     | 72    | mA   |

| R <sub>BDTransmitter</sub>                                     | Bus interface equivalent output impedance (Bus driver simulation model parameter)       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31  | 105 | 500   | Ω    |

<sup>8.</sup> Guaranteed for ±300 mV and ±150 mV level of uBus

Figure 10. Transmission Parameters (TxEN is Low and BGE is High)

NOTE: TXD signal is constant for 100..4400 ns before the first edge.

All parameters values are valid even if the test is performed with opposite polarity.

Figure 11. Transmission Parameters for Transitions between Idle and Active (TXD is Low)

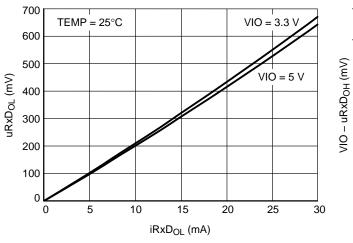

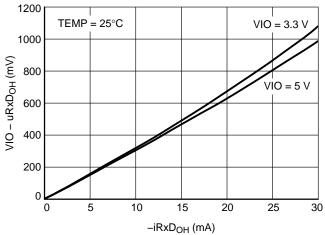

**Table 13. RECEPTION PARAMETERS**

| Symbol                                           | Parameter                                                                                                                  | Conditions                                          | Min  | Тур  | Max  | Unit |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------|------|------|------|

| uData0                                           | Receiver threshold for detecting Data_0                                                                                    | Activity detected previously.                       | -300 |      | -150 | mV   |

| uData1                                           | Receiver threshold for detecting Data_1                                                                                    | previously.<br> uBP–uBM  ≤ 3 V                      | 150  |      | 300  | mV   |

| uData1 - uData0                                  | Mismatch of receiver thresholds                                                                                            | (uBP+uBM)/2 = 2.5 V                                 | -30  |      | 30   | mV   |

| uData0_LP                                        | Low power receiver threshold for detecting Data_0                                                                          | uV <sub>BAT</sub> ≥ 7 V                             | -400 |      | -100 | mV   |

| uCM                                              | Common mode voltage range (with respect to GND) that does not disturb the receiver function and reception level parameters | uBP = (uBP+uBM)/2<br>(Note 9)                       | -10  |      | 15   | V    |

| uBias                                            | Bus bias voltage during bus state Idle in normal–power modes                                                               | $R_{BUS} = 40-55 \Omega;$<br>$C_{BUS} = 100 pF$     | 1800 | 2500 | 3200 | mV   |

|                                                  | Bus bias voltage during bus state Idle in low–power modes                                                                  | (Note 10)                                           | -200 | 0    | 200  | mV   |

| R <sub>CM1</sub> , R <sub>CM2</sub>              | Receiver common mode resistance                                                                                            | (Note 10)                                           | 10   |      | 40   | kΩ   |

| C_BP, C_BM                                       | Input capacitance on BP and BM pin (Note 11)                                                                               | f = 5 MHz                                           |      |      | 20   | pF   |

| C_Bus <sub>DIF</sub>                             | Bus differential input capacitance (Note 11)                                                                               | f = 5 MHz                                           |      |      | 5    | pF   |

| iBP <sub>LEAK</sub><br>iBM <sub>LEAK</sub>       | Absolute leakage current when driver is off                                                                                | uBP = uBM = 5 V<br>All other pins = 0 V             |      |      | 25   | μΑ   |

| iBP <sub>LEAKGND</sub><br>iBM <sub>LEAKGND</sub> | Absolute leakage current, in case of loss of GND                                                                           | uBP = uBM = 0 V<br>All other pins = 16 V            |      |      | 1600 | μΑ   |

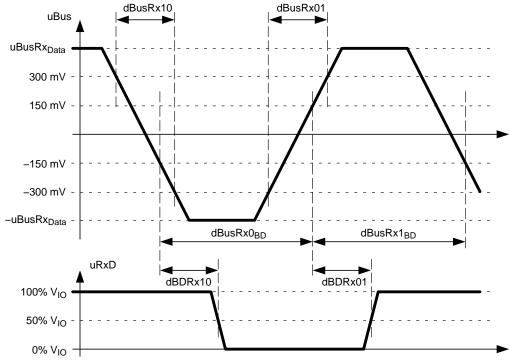

| uBusRx <sub>Data</sub>                           | Test signal parameters for reception                                                                                       | Test signal and parameters defined in Figure 12 and | 400  |      | 3000 | mV   |

| dBusRx0 <sub>BD</sub>                            | Figui                                                                                                                      |                                                     | 60   |      | 4330 | ns   |

| dBusRx1 <sub>BD</sub>                            |                                                                                                                            | Figure 13.                                          | 60   |      | 4330 | ns   |

| dBusRx10                                         |                                                                                                                            | RxD pin loaded with                                 |      |      | 22.5 | ns   |

| dBusRx01                                         |                                                                                                                            | 25 pF capacitor.                                    |      |      | 22.5 | ns   |

| dBDRx10                                          | Receiver delay, negative edge (Note 12)                                                                                    |                                                     |      |      | 75   | ns   |

| dBDRx01                                          | Receiver delay, positive edge (Note 12)                                                                                    |                                                     |      |      | 75   | ns   |

| dBDRxAsym                                        | Receiver delay mismatch<br>  dBDRx10- dBDRx01  (Note 12)                                                                   |                                                     |      |      | 5    | ns   |

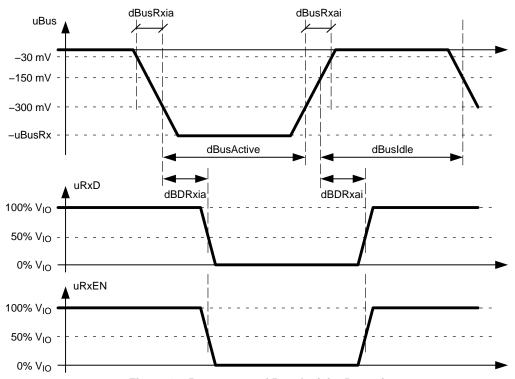

| uBusRx                                           | Test signal parameters for                                                                                                 |                                                     | 400  |      | 3000 | mV   |

| dBusActive                                       | bus activity detection                                                                                                     |                                                     | 590  |      | 610  | ns   |

| dBusIdle                                         |                                                                                                                            |                                                     | 590  |      | 610  | ns   |

| dBusRxia                                         |                                                                                                                            |                                                     | 18   |      | 22   | ns   |

| dBusRxai                                         |                                                                                                                            |                                                     | 18   |      | 22   | ns   |

| dBDIdleDetection                                 | Bus driver filter-time for idle detection                                                                                  |                                                     | 50   |      | 200  | ns   |

| dBDActivityDetection                             | Bus driver filter-time for activity detection                                                                              |                                                     | 100  |      | 250  | ns   |

| dBDRxai                                          | Bus driver idle reaction time                                                                                              | -                                                   | 50   |      | 275  | ns   |

| dBDRxia                                          | Bus driver activity reaction time                                                                                          |                                                     | 100  |      | 325  | ns   |

| dBDTxRxai                                        | Idle-Loopdelay                                                                                                             |                                                     |      |      | 325  | ns   |

<sup>9.</sup> Tested on a receiving bus driver. Sending bus driver has a ground offset voltage in the range of [–12.5 V to +12.5 V] and sends a 50/50 pattern.

10. Bus driver is connected to GND and uV<sub>CC</sub> = 5 V and uV<sub>BAT</sub> ≥ 7 V.

11. Values based on design and characterization, not tested in production.

12. Guaranteed for ±300 mV and ±150 mV level of uBus.

**Table 14. REMOTE WAKEUP DETECTION PARAMETERS**

| Symbol                                  | Parameter                                                                                                                        | Conditions | Min  | Тур | Max | Unit |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------|------|-----|-----|------|

| dWU <sub>0Detect</sub>                  | Detection time for Wakeup Data_0 symbol                                                                                          |            | 1    |     | 4   | μs   |

| dWU <sub>IdleDetect</sub>               | Detection time for Wakeup Idle/Data_1 symbol                                                                                     |            | 1    |     | 4   | μs   |

| dWU <sub>Timeout</sub>                  | Maximum accepted Wakeup pattern duration                                                                                         |            | 48   |     | 140 | μs   |

| dWU <sub>Interrupt</sub>                | Acceptance timeout for interruptions                                                                                             | (Note 13)  | 0.13 |     | 1   | μs   |

| uV <sub>BAT-WAKE</sub>                  | $\begin{array}{l} \mbox{Minimum supply voltage V}_{\mbox{BAT}} \mbox{ for remote wakeup} \\ \mbox{events detection} \end{array}$ |            | ı    |     | 5.5 | V    |

| dBDWakeup<br>Reaction <sub>remote</sub> | Reaction time after remote wakeup event                                                                                          |            | 7    |     | 35  | μs   |

<sup>13.</sup> The minimum value is only guaranteed, when the phase that is interrupted was continuously present for at least 870 ns.

**Table 15. TEMPERATURE MONITORING PARAMETERS**

|   | Symbol | Parameter               | Conditions | Min | Тур | Max | Unit |

|---|--------|-------------------------|------------|-----|-----|-----|------|

| Ī | Tjw    | Thermal warning level   |            | 125 | 140 | 150 | °C   |

| Ī | Tjsd   | Thermal shut-down level |            | 155 | 165 | 185 | °C   |

Figure 12. Reception Parameters

Figure 13. Parameters of Bus Activity Detection

**Table 16. WAKE PIN PARAMETERS**

| Symbol                                 | Parameter                                                                 | Conditions                                                   | Min | Тур                 | Max | Unit |

|----------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------|-----|---------------------|-----|------|

| uV <sub>BAT-WAKE</sub>                 | Minimum supply voltage V <sub>BAT</sub> for local wakeup events detection |                                                              |     |                     | 7   | V    |

| uWAKE <sub>TH</sub>                    | Threshold of wake comparator                                              |                                                              |     | V <sub>BAT</sub> /2 |     | V    |

| dBDWakePulseFilter                     | Wake pulse filter time (spike rejection)                                  |                                                              | 1   |                     | 500 | μS   |

| dBDWakeup<br>Reaction <sub>local</sub> | Reaction time after local wakeup event                                    |                                                              | 14  |                     | 50  | μS   |

| iWAKE <sub>PD</sub>                    | Internal pull-down current                                                | uWAKE = 0 V for longer<br>than dWakePulseFilter              | 3   |                     | 11  | μΑ   |

| iWAKE <sub>PU</sub>                    | Internal pull-up current                                                  | uWAKE = V <sub>BAT</sub> for longer<br>than dWakePulseFilter | -11 |                     | -3  | μΑ   |

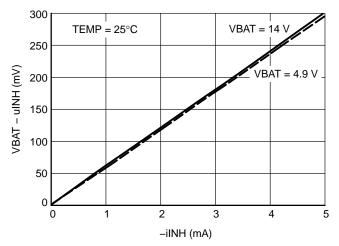

**Table 17. INH PIN PARAMETERS**

| Symbol                     | Parameter                                    | Conditions                                  | Min                        | Тур                        | Max                       | Unit |

|----------------------------|----------------------------------------------|---------------------------------------------|----------------------------|----------------------------|---------------------------|------|

| uINH1 <sub>Not_Sleep</sub> | Voltage on INH pin, when signaling Not_Sleep | iINH = -5  mA<br>$uV_{BAT} > 5.5 \text{ V}$ | uV <sub>BAT</sub> –<br>0.6 | uV <sub>BAT</sub><br>–0.27 | uV <sub>BAT</sub><br>–0.1 | V    |

| iINH1 <sub>LEAK</sub>      | Leakage current while signaling Sleep        |                                             | <b>-</b> 5                 |                            | 5                         | μΑ   |

**Table 18. POWER SUPPLY MONITORING PARAMETERS**

| Symbol                     | Parameter                                                                          | Conditions | Min | Тур | Max | Unit |

|----------------------------|------------------------------------------------------------------------------------|------------|-----|-----|-----|------|

| uBDUVV <sub>BAT</sub>      | V <sub>BAT</sub> under-voltage threshold                                           |            | 4   |     | 5.1 | V    |

| uBDUVV <sub>CC</sub>       | V <sub>CC</sub> under-voltage threshold                                            |            | 4   |     | 4.5 | V    |