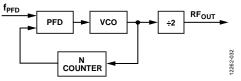

# Integer-N/Fractional-N PLL Synthesizer

Data Sheet ADF4155

#### **FEATURES**

Input frequency range: 500 MHz to 8000 MHz Fractional-N synthesizer and integer-N synthesizer Phase frequency detector (PFD) up to 125 MHz High resolution 38-bit modulus

Separate charge pump supply (V<sub>P</sub>) allows extended tuning voltage in 5 V systems

Programmable divide by 1, 2, 4, 8, 16, 32, or 64 output Differential and single-ended reference inputs

Power supply: 3.3 V ± 5% Logic compatibility: 1.8 V

Programmable dual-modulus prescaler (P) of 4/5 or 8/9

Programmable output power level

3-wire serial interface

Analog and digital lock detect

#### **APPLICATIONS**

Wireless infrastructure (W-CDMA, TD-SCDMA, WiMAX, GSM, PCS, DCS, DECT)

Point to point/point to multipoint microwave links

**Test equipment**

Wireless LANs, CATV equipment

**Clock generation**

#### **GENERAL DESCRIPTION**

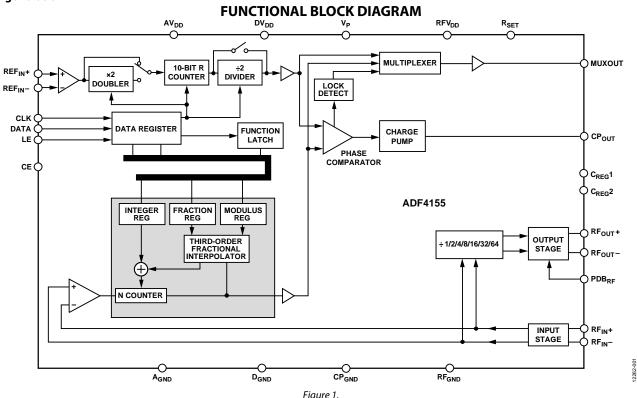

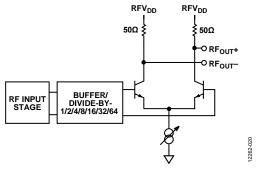

The ADF4155 allows implementation of fractional-N or integer-N phase-locked loop (PLL) frequency synthesizers when used with an external loop filter, external voltage controlled oscillator (VCO), and external reference frequency.

The ADF4155 is for use with external VCO parts up to an 8 GHz operating frequency. The high resolution programmable modulus allows synthesis of exact frequencies with 0 Hz error.

The VCO frequency can be divided by 1, 2, 4, 8, 16, 32, or 64 to allow the user to generate RF output frequencies as low as 7.8125 MHz.

Control of all on-chip registers is through a simple 3-wire interface. The device operates with a nominal power supply of  $3.3~V\pm5\%$  and can be powered down when not in use.

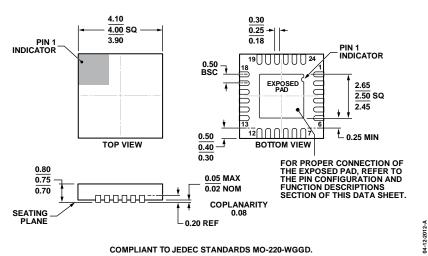

The ADF4155 is available in a 24-lead, 4 mm  $\times$  4 mm LFCSP package.

Rev. 0

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

# **TABLE OF CONTENTS**

| Features                                    | 1   |

|---------------------------------------------|-----|

| Applications                                | 1   |

| General Description                         | 1   |

| Functional Block Diagram                    | 1   |

| Revision History                            | 2   |

| Specifications                              | . 3 |

| Timing Characteristics                      | 5   |

| Absolute Maximum Ratings                    | 6   |

| Transistor Count                            | 6   |

| ESD Caution                                 | 6   |

| Pin Configuration and Function Descriptions | 7   |

| Typical Performance Characteristics         | 9   |

| Circuit Description1                        | 12  |

| Reference Input Section                     | 12  |

| RF N Counter1                               | 12  |

| Phase Frequency Detector and Charge Pump 1  | 13  |

| MUXOUT and Lock Detect1                     | 13  |

| Input Shift Registers1                      | 13  |

| Program Modes 1                             | 13  |

| Output Stage1                               | 4   |

| Register Maps                              |

|--------------------------------------------|

| Register 0                                 |

| Register 1                                 |

| Register 2                                 |

| Register 3                                 |

| Register 4                                 |

| Register 5                                 |

| Register 6                                 |

| Register 7                                 |

| Register 8                                 |

| Register Initialization Sequence           |

| RF Synthesizer—A Worked Example            |

| Reference Doubler and Reference Divider    |

| Cycle Slip Reduction for Faster Lock Times |

| Spurious Optimization                      |

| Spur Mechanisms                            |

| Applications Information                   |

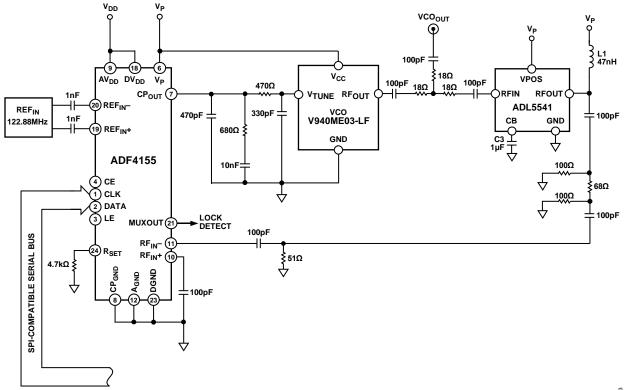

| Local Oscillator with RF Buffer            |

| Outline Dimensions                         |

| Ordering Guide                             |

# **REVISION HISTORY**

4/14—Revision 0: Initial Version

# **SPECIFICATIONS**

$AV_{DD} = DV_{DD} = RFV_{DD} = 3.3 \ V \pm 5\%, \ AV_{DD} \leq V_P \leq 5.5 \ V, \ A_{GND} = D_{GND} = RF_{GND} = CP_{GND} = 0 \ V, \ and \ T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise noted. Operating temperature range is <math>-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ .

Table 1.

| Parameter                                               | Min                    | Тур              | Max                | Unit     | Test Conditions/Comments                                                                                           |

|---------------------------------------------------------|------------------------|------------------|--------------------|----------|--------------------------------------------------------------------------------------------------------------------|

| REF <sub>IN</sub> +\REF <sub>IN</sub> - CHARACTERISTICS |                        |                  |                    |          |                                                                                                                    |

| Input Frequency                                         |                        |                  |                    |          | For f < 10 MHz, ensure slew rate > 21 V/µs                                                                         |

| Single-Ended Mode                                       | 10                     |                  | 250                | MHz      |                                                                                                                    |

| Differential Mode                                       | 10                     |                  | 600                | MHz      |                                                                                                                    |

| Input Sensitivity                                       |                        |                  |                    |          |                                                                                                                    |

| Single-Ended Mode                                       | 0.7                    |                  | $AV_DD$            | V p-p    | REF <sub>IN</sub> + biased at AV <sub>DD</sub> /2; ac coupling ensures AV <sub>DD</sub> /2 bias                    |

| Differential Mode                                       | 0.4                    |                  | 1.8                | V p-p    | LVDS and LVPECL compatible, REF <sub>IN</sub> +\REF <sub>IN</sub> -biased at 2.1 V; ac coupling ensures 2.1 V bias |

| Input Capacitance                                       |                        |                  |                    |          |                                                                                                                    |

| Single-Ended Mode                                       |                        | 6.9              |                    | pF       |                                                                                                                    |

| Differential Mode                                       |                        | 1.4              |                    | pF       |                                                                                                                    |

| Input Current                                           |                        |                  | ±60                | μΑ       |                                                                                                                    |

| PHASE DETECTOR                                          |                        |                  |                    |          |                                                                                                                    |

| Phase Detector Frequency                                |                        |                  | 125                | MHz      | Negative bleed on                                                                                                  |

|                                                         |                        |                  | 100                | MHz      | Pulsed bleed on                                                                                                    |

|                                                         |                        |                  | 125                | MHz      | Negative bleed off and pulsed bleed off                                                                            |

|                                                         |                        |                  | 75                 | MHz      | CSR enabled                                                                                                        |

| RF <sub>IN</sub> +\RF <sub>IN</sub> - CHARACTERISTICS   |                        |                  |                    |          | For lower frequencies, ensure that the slew rate > 400 V/µs                                                        |

| RF Input Frequency                                      | 0.5                    |                  | 6.0                | GHz      | –10 dBm minimum/0 dBm maximum                                                                                      |

| pat.requency                                            |                        |                  | 8.0                | GHz      | –5 dBm minimum/0 dBm maximum                                                                                       |

| Prescaler Output Frequency                              |                        |                  | 1.5                | GHz      |                                                                                                                    |

| CHARGE PUMP (CP)                                        |                        |                  |                    |          |                                                                                                                    |

| I <sub>CP</sub> Sink/Source                             |                        |                  |                    |          | $R_{SFT} = 4.7 \text{ k}\Omega$                                                                                    |

| High Value                                              |                        | 5                |                    | mA       |                                                                                                                    |

| Low Value                                               |                        | 0.31             |                    | mA       |                                                                                                                    |

| R <sub>SET</sub> Range                                  | 2.7                    | 4.7              | 10                 | kΩ       |                                                                                                                    |

| Sink and Source Current Matching                        |                        | 3                |                    | %        | $0.5 \text{ V} \le \text{V}_{CP} \le \text{V}_{P} - 0.5 \text{ V}$                                                 |

| I <sub>CP</sub> vs. V <sub>CP</sub>                     |                        | 3                |                    | %        | $0.5 \text{ V} \leq \text{V}_{\text{CP}} \leq \text{V}_{\text{P}} - 0.5 \text{ V}$                                 |

| I <sub>CP</sub> vs. Temperature                         |                        | 1.5              |                    | %        | $V_{CP} = 2.5 \text{ V}$                                                                                           |

| LOGIC INPUTS                                            |                        |                  |                    |          |                                                                                                                    |

| Input High Voltage, V <sub>INH</sub>                    | 1.5                    |                  |                    | V        | Compatible with 1.8 V and 3 V logic                                                                                |

| Input Low Voltage, V <sub>INL</sub>                     | 1.72                   |                  | 0.6                | V        |                                                                                                                    |

| Input Current, I <sub>INH</sub> /I <sub>INL</sub>       |                        |                  | ±1                 | μA       |                                                                                                                    |

| Input Capacitance, C <sub>IN</sub>                      |                        | 3.0              |                    | pF       |                                                                                                                    |

| LOGIC OUTPUTS                                           |                        | 3.0              |                    | Ρ.       |                                                                                                                    |

| Output High Voltage, V <sub>OH</sub>                    | DV <sub>DD</sub> - 0.4 | 1                |                    | V        | CMOS output selected                                                                                               |

| Output High Current, I <sub>OH</sub>                    | 0.1                    | l                | 500                | μΑ       | civios output selecteu                                                                                             |

| Output Low Voltage, Vol                                 |                        |                  | 0.4                | V        | Ι <sub>ΟL</sub> = 500 μΑ                                                                                           |

| POWER SUPPLIES                                          |                        |                  | O. F               | <b>-</b> | ιου 300 μπτ                                                                                                        |

| AV <sub>DD</sub>                                        | 3.135                  |                  | 3.465              | V        |                                                                                                                    |

| DV <sub>DD</sub>                                        | 5.155                  | $AV_DD$          | J. <del>T</del> UJ | V        | Voltage must equal AVDD                                                                                            |

| RFV <sub>DD</sub>                                       |                        | AV <sub>DD</sub> |                    | V        | Voltage must equal AV <sub>DD</sub>                                                                                |

| V <sub>P</sub>                                          | $AV_DD$                | ₩ DD             | 5.5                | V        | voitage must equal Avor                                                                                            |

| VP<br>IP                                                | TA DD                  | 4.1              | ر.ر                |          |                                                                                                                    |

| Output Dividers                                         |                        | 4.1<br>6 to 36   |                    | mA<br>mA | Each output divide by 2 consumes 6 mA; see                                                                         |

| Output Dividers                                         |                        | 0 10 30          |                    | IIIA     | Table 6 for details on the current consumption as a function of the output power and divider                       |

Rev. 0 | Page 3 of 32

| Parameter                                                                        | Min    | Тур       | Max  | Unit   | Test Conditions/Comments                                                                    |

|----------------------------------------------------------------------------------|--------|-----------|------|--------|---------------------------------------------------------------------------------------------|

| Total I <sub>DD</sub> (DI <sub>DD</sub> + AI <sub>DD</sub> + RFI <sub>DD</sub> ) |        | 38        | 47   | mA     | RF output (Bit DB6, Register 6) disabled,<br>3.6 GHz at VCO output                          |

|                                                                                  |        | 105       | 131  | mA     | $RF_{OUT}+/RF_{OUT}-=1800$ MHz, divide by 2 enabled, 5 dBm                                  |

| Low Power Sleep Mode                                                             |        | 10        | 22   | μΑ     | Hardware powered down using CE                                                              |

|                                                                                  |        | 500       | 530  | μΑ     | Software powered down, serial peripheral interface (SPI) powered up in low power sleep mode |

| RF <sub>OUT</sub> +/RF <sub>OUT</sub> - CHARACTERISTICS                          |        |           |      |        |                                                                                             |

| Maximum Output Frequency                                                         |        |           | 4000 | MHz    |                                                                                             |

| Minimum Output Frequency Using<br>Dividers                                       | 7.8125 |           |      | MHz    | 500 MHz fundamental output and divide by 64 selected                                        |

| Harmonic Content (Second)                                                        |        | -16       |      | dBc    | $RF_{OUT}+/RF_{OUT}-=2.9$ GHz, fundamental mode                                             |

|                                                                                  |        | -26       |      | dBc    | RFour+/RFour- = 2.9 GHz, divide by 2 enabled                                                |

| Harmonic Content (Third)                                                         |        | -22       |      | dBc    | RF <sub>OUT</sub> +/RF <sub>OUT</sub> - = 2.9 GHz, fundamental mode                         |

|                                                                                  |        | <b>-7</b> |      | dBc    | RFour+/RFour- = 2.9 GHz, divide by 2 enabled                                                |

| Minimum RF Output Power <sup>1</sup>                                             |        | -4        |      | dBm    | Programmable in 3 dB steps                                                                  |

| Maximum RF Output Power <sup>1</sup>                                             |        | 5         |      | dBm    |                                                                                             |

| NOISE CHARACTERISTICS                                                            |        |           |      |        | Negative bleed enabled                                                                      |

| Normalized Phase Noise Floor, PN <sub>SYNTH</sub> <sup>2</sup>                   |        |           |      |        | PLL bandwidth = 500 kHz                                                                     |

| Integer-N Mode                                                                   |        | -223      |      | dBc/Hz | FRAC = 0                                                                                    |

| Fractional-N-Mode                                                                |        | -218      |      | dBc/Hz |                                                                                             |

| Normalized 1/f Noise, PN <sub>1_f</sub> <sup>3</sup>                             |        | -116      |      | dBc/Hz | 10 kHz offset; normalized to 1 GHz                                                          |

| In-Band Phase Noise⁴                                                             |        | -98       |      | dBc/Hz | 10 kHz offset from 5.8 GHz carrier                                                          |

| Spurious Signals due to PFD                                                      |        | -110      |      | dBc/Hz | At 5.8 GHz VCO output, $f_{PFD} = 61.44$ MHz                                                |

| Frequency                                                                        |        | -112      |      | dBc/Hz | At 5.8 GHz VCO output, f <sub>PFD</sub> = 30.72 MHz                                         |

| Level of Signal with RF Mute Enabled                                             |        | -40       |      | dBm    |                                                                                             |

$<sup>^{1}</sup>$  Using an external 18 nH pull-up inductor to RFV  $_{DD}$  into a 50  $\Omega$  load.

<sup>&</sup>lt;sup>2</sup> The synthesizer phase noise floor is estimated by measuring the in-band phase noise at the output of the VCO and subtracting 20 logN (where N is the N counter value) and 10 logf<sub>PFD</sub>. PN<sub>SYNTH</sub> = PN<sub>TOT</sub> – 10 log f<sub>PFD</sub> – 20 logN.

<sup>3</sup> The PLL phase noise is composed of 1/f (flicker) noise plus the normalized PLL noise floor. The formula for calculating the 1/f noise contribution at an RF frequency (f<sub>RF</sub>)

<sup>&</sup>lt;sup>3</sup> The PLL phase noise is composed of 1/f (flicker) noise plus the normalized PLL noise floor. The formula for calculating the 1/f noise contribution at an RF frequency ( $f_{RF}$ ) and at a frequency offset (f) is given by PN =  $P_{1\_f}$  + 10log(10kHz/f) + 20log( $f_{RF}$ /1 GHz). Both the normalized phase noise floor and flicker noise are modeled in the ADIsimPLL design tool.

$<sup>^4</sup>$  f<sub>REFIN</sub> = 122.88 MHz, f<sub>PFD</sub> = 61.44 MHz, frequency offset = 10 kHz, VCO frequency = 5.8 GHz, RF<sub>OUT</sub> = 5.8 GHz, N = 94.40104167, loop bandwidth = 60 kHz, I<sub>CP</sub> = 0.938 mA, and I<sub>BLEED</sub> = 60 μA.

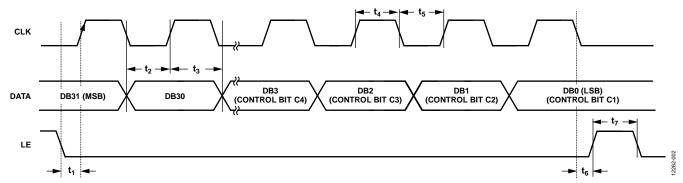

# **TIMING CHARACTERISTICS**

$AV_{DD} = DV_{DD} = RFV_{DD} = 3.3 \ V \pm 5\%, AV_{DD} \leq V_P \leq 5.5V, A_{GND} = D_{GND} = RF_{GND} = CP_{GND} = 0 \ V, 1.8 \ V \ and 3 \ V \ logic levels used, and $T_A = T_{MIN}$ to $T_{MAX}$, unless otherwise noted.}$

Table 2.

| Parameter             | Limit | Unit   | Description            |

|-----------------------|-------|--------|------------------------|

| t <sub>1</sub>        | 20    | ns min | LE setup time          |

| $t_2$                 | 10    | ns min | DATA to CLK setup time |

| t <sub>3</sub>        | 10    | ns min | DATA to CLK hold time  |

| t <sub>4</sub>        | 25    | ns min | CLK high duration      |

| <b>t</b> <sub>5</sub> | 25    | ns min | CLK low duration       |

| t <sub>6</sub>        | 10    | ns min | CLK to LE setup time   |

| <b>t</b> <sub>7</sub> | 20    | ns min | LE pulse width         |

# **Timing Diagram**

Figure 2. Timing Diagram

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 3.

| Parameter                                                     | Rating                                      |

|---------------------------------------------------------------|---------------------------------------------|

| AV <sub>DD</sub> to GND <sup>1</sup>                          | -0.3 V to +3.6 V                            |

| $AV_{DD}$ to $DV_{DD}$                                        | -0.3 V to +0.3 V                            |

| RFV <sub>DD</sub> to AV <sub>DD</sub>                         | -0.3 V to +0.3 V                            |

| RFV <sub>DD</sub> to DV <sub>DD</sub>                         | -0.3 V to +0.3 V                            |

| V <sub>P</sub> to GND¹                                        | -0.3 V to +5.8 V                            |

| $V_P$ to $AV_{DD}$                                            | -0.3 V to +2.5 V                            |

| Digital I/O Voltage to GND <sup>1</sup>                       | $-0.3 \text{ V to DV}_{DD} + 0.3 \text{ V}$ |

| Analog I/O Voltage to GND <sup>1</sup>                        | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$ |

| REF <sub>IN</sub> +, REF <sub>IN</sub> - to GND <sup>1</sup>  | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$  |

| REF <sub>IN</sub> + to REF <sub>IN</sub> -                    | ±2.1 V                                      |

| RF <sub>IN</sub> + to RF <sub>IN</sub> -                      | ±700 mV                                     |

| Operating Temperature Range                                   | −40°C to +85°C                              |

| Storage Temperature Range                                     | −65°C to +125°C                             |

| Maximum Junction Temperature                                  | 150°C                                       |

| LFCSP $\theta_{JA}$ , Thermal Impedance (Pad Soldered to GND) | 47.3°C/W                                    |

| Reflow Soldering                                              |                                             |

| Peak Temperature                                              | 260°C                                       |

| Time at Peak Temperature                                      | 40 sec                                      |

| ESD                                                           |                                             |

| Charged Device Model                                          | 1250 V                                      |

| Human Body Model                                              | 4000 V                                      |

$<sup>^{1}\,</sup>GND=A_{GND}=D_{GND}=RF_{GND}=CP_{GND}=0\,V.$

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

# **TRANSISTOR COUNT**

The transistor count for the ADF4155 is 31,190 (CMOS) and 1652 (bipolar).

# **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

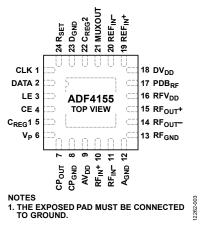

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic            | Description                                                                                                                                                                                                                                                     |

|---------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CLK                 | Serial Clock Input. Data is clocked into the 32-bit shift register on the CLK rising edge. This input is a high impedance CMOS input.                                                                                                                           |

| 2       | DATA                | Serial Data Input. The serial data is loaded MSB first with the four LSBs as the control bits. This input is a high impedance CMOS input.                                                                                                                       |

| 3       | LE                  | Load Enable Input. When LE goes high, the data stored in the shift register is loaded into the register that is selected by the four LSBs. This input is a high impedance CMOS input.                                                                           |

| 4       | CE                  | Chip Enable. A logic low on this pin powers down the device and puts the charge pump into three-state mode. A logic high on this pin powers up the device, depending on the status of the power-down bits.                                                      |

| 5       | C <sub>REG</sub> 1  | Output of Internal Low Dropout (LDO) Regulator. Supply voltage to digital circuits. Nominal voltage of 1.8 V. 100 nF decoupling capacitors to ground required.                                                                                                  |

| 6       | V <sub>P</sub>      | Charge Pump Power Supply. V <sub>P</sub> must have the same or greater value than AV <sub>DD</sub> up to 5.5 V. Connect decoupling capacitors, as close to this pin as possible, to the analog ground plane.                                                    |

| 7       | СРоит               | Charge Pump Output. When enabled, this output provides $\pm I_{CP}$ to the external loop filter. The output of the loop filter is connected to the $V_{TUNE}$ pin of the external VCO.                                                                          |

| 8       | CP <sub>GND</sub>   | Charge Pump Ground. This output is the ground return pin for the CPout pin.                                                                                                                                                                                     |

| 9       | $AV_DD$             | Analog Power Supply. This pin ranges from 3.135 V to 3.465 V. Connect decoupling capacitors, as close to this pin as possible, to the analog ground plane. AV <sub>DD</sub> must have the same value as DV <sub>DD</sub> and RFV <sub>DD</sub> .                |

| 10      | RF <sub>IN</sub> +  | RF Input. This small signal input must be ac-coupled to the external VCO.                                                                                                                                                                                       |

| 11      | RF <sub>IN</sub> —  | Complementary RF Input. Decouple this pin to the ground plane with a small bypass capacitor, typically 100 pF. If driven differentially, connect this input similar to RF <sub>IN</sub> +.                                                                      |

| 12      | A <sub>GND</sub>    | Analog Ground. Ground return pins for the analog circuitry.                                                                                                                                                                                                     |

| 13      | RF <sub>GND</sub>   | RF Ground. This output is the ground return pin for the RFV <sub>DD</sub> pin.                                                                                                                                                                                  |

| 14      | RFоит—              | Complementary RF Output. The output level is programmable. The VCO fundamental output or a divided-down version is available.                                                                                                                                   |

| 15      | RFour+              | RF Output. The output level is programmable. The VCO fundamental output or a divided-down version is available.                                                                                                                                                 |

| 16      | $RFV_DD$            | Analog Power Supply for RF Outputs. This pin ranges from 3.135 V to 3.465 V. Connect decoupling capacitors, as close to this pin as possible, to the analog ground plane. RFV <sub>DD</sub> must have the same value as AV <sub>DD</sub> and DV <sub>DD</sub> . |

| 17      | $PDB_{RF}$          | RF Power-Down. A logic low on this pin mutes the RF outputs. This function is also software controllable.                                                                                                                                                       |

| 18      | $DV_DD$             | Digital Power Supply. This pin must be at the same voltage as AV <sub>DD</sub> and RFV <sub>DD</sub> . Connect decoupling capacitors, as close to this pin as possible, to the ground plane.                                                                    |

| 19      | REF <sub>IN</sub> + | Reference Input.                                                                                                                                                                                                                                                |

| 20      | REF <sub>IN</sub> — | Complementary Reference Input.                                                                                                                                                                                                                                  |

| 21      | MUXOUT              | Multiplexer Output. The multiplexer output allows the lock detect, the scaled RF, or the scaled reference frequency to be externally accessed.                                                                                                                  |

| Pin No. | Mnemonic           | Description                                                                                                                                                                                                                                     |

|---------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22      | C <sub>REG</sub> 2 | Output of Internal LDO. Supply voltage to digital circuits. Nominal voltage of 1.8 V. 100 nF decoupling capacitors to ground required.                                                                                                          |

| 23      | $D_GND$            | Digital Ground. Ground return pins for the digital circuitry.                                                                                                                                                                                   |

| 24      | R <sub>SET</sub>   | Connect a resistor between this pin and ground to set the charge pump output current. The nominal voltage bias at the $R_{SET}$ pin is 0.55 V. The relationship between $I_{CP\_MAX}$ and $R_{SET}$ is as follows: $I_{CP\_MAX} = 23.5/R_{SET}$ |

|         |                    | where: $R_{SET} = 4.7 \text{ k}\Omega$ . $I_{CP} = 5 \text{ mA}$ .                                                                                                                                                                              |

|         | EPAD               | Exposed Pad. The exposed pad must be connected to ground.                                                                                                                                                                                       |

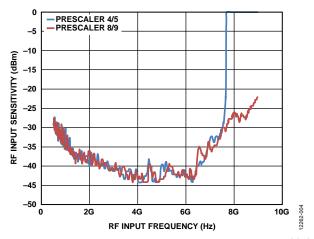

# TYPICAL PERFORMANCE CHARACTERISTICS

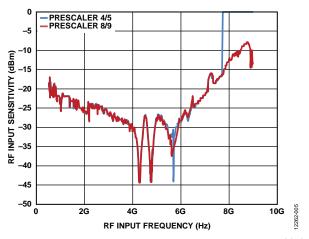

Figure 4. RF Input Sensitivity vs. RF Input Frequency, RF Output Disabled

Figure 5. RF Input Sensitivity vs. RF Input Frequency, RF Output Enabled, RF Divide-by-2 Selected

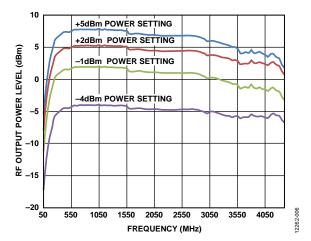

Figure .6. Single-Ended RF Output Power Level vs. Frequency and Power Setting, RF Output Pins Pulled Up to 3.3 V via 18 nH Inductors

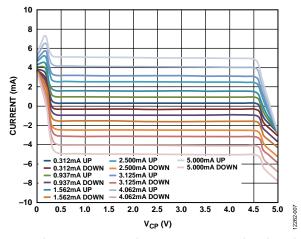

Figure 7. Charge Pump Output Characteristics,  $V_P = 5 V$ , Selected  $I_{CP}$  Values Between 0.312 mA (Minimum) and 5.000 mA (Maximum),  $R_{SET} = 4.7 \text{ k}\Omega$

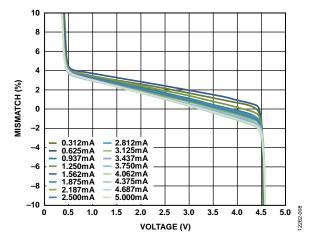

Figure 8. Charge Pump Output Mismatch vs.  $V_{CP}$ , Selected  $I_{CP}$  Values Between 0.312 mA (Minimum) and 5.000 mA (Maximum),  $R_{SET} = 4.7 \text{ k}\Omega$

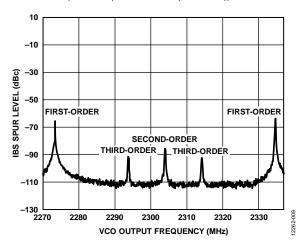

Figure 9. Integer Boundary Spurs (IBS) Spur Level vs. VCO Output Frequency,  $f_{PFD} = 61.44$  MHz, Sweep Resolution = 80 kHz

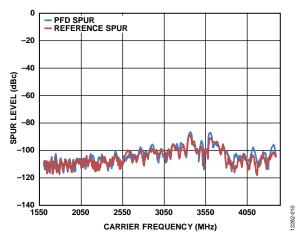

Figure 10. PFD and Reference Spur Level vs. Carrier Frequency Measured at VCO Output,  $f_{PFD}$  = 61.44 MHz, REF<sub>IN</sub>+/REF<sub>IN</sub>- = 122.88 MHz

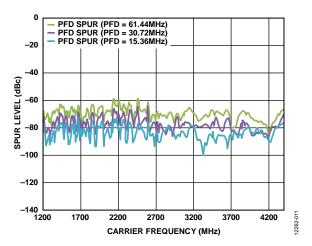

Figure 11. PFD Spur Level vs. Carrier Frequency Measured at RF Output,  $REF_{IN}+/REF_{IN}-=122.88$  MHz (Note the improvement in the PFD spurs when the PFD frequency is lower.)

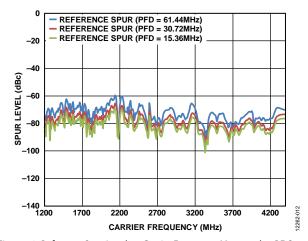

Figure 12. Reference Spur Level vs. Carrier Frequency Measured at RF Output,  $REF_{IN}+/REF_{IN}-=122.88$  MHz (Note the improvement in the PFD spurs when the PFD frequency is lowered.)

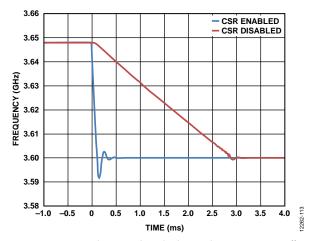

Figure 13. PLL Lock Time with Cycle Sleep Reduction (CSR) On/Off, Locking over 50 MHz Range (Jump from 3.648 GHz to 3.6 GHz),  $f_{PFD} = 61.44$  MHz, Loop Bandwidth = 15 kHz,  $I_{CP} = 0.31$  mA

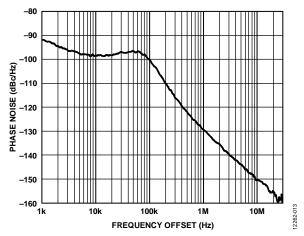

Figure 14. Integer-N Phase Noise and Spur Performance; VCO<sub>OUT</sub> = 5775.36 MHz, REF<sub>IN</sub>+/REF<sub>IN</sub>- = 122.88 MHz, f<sub>PFD</sub> = 61.44 MHz, Loop Filter Bandwidth= 60 kHz

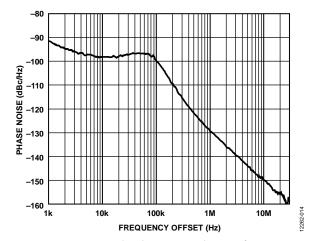

Figure 15. Fractional-N Phase Noise and Spur Performance,  $VCO_{OUT} = 5800$  MHz,  $REF_{IN} + /REF_{IN} - = 122.88$  MHz,  $f_{PFD} = 61.44$  MHz, Loop Filter Bandwidth = 60 kHz

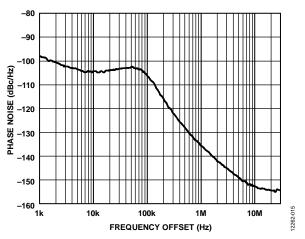

Figure 16. RF Output Phase Noise, RF Divider = 2 Enabled, Fractional-N, RF $_{OUT}$ + = 2900 MHz, REF $_{IN}$ +/REF $_{IN}$ - = 122.88 MHz,  $f_{PFD}$  = 61.44 MHz, Loop Filter Bandwidth = 60 kHz

# CIRCUIT DESCRIPTION REFERENCE INPUT SECTION

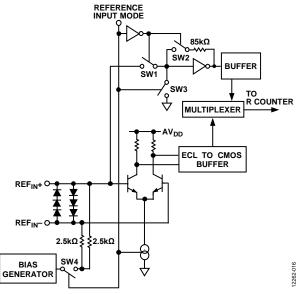

The reference input stage is shown in Figure 17. The reference input can accept both single-ended and differential signals, and the choice is controlled by the reference input mode bit (Bit DB30, Register 6). To use a differential signal for the reference input, this bit must be programmed high. In this case, the SW1 and SW2 switches are opened, the SW3 and SW4 switches are closed, and the current source driving the differential pair of the transistors is switched on. The differential signal is buffered, before it is fed to the emitter-coupled logic (ECL) to a CMOS converter. When a single-ended signal is used as the reference, Bit DB30 in Register 6 must be programmed to 0. In this case, the SW1 and SW2 switches are closed, the SW3 and SW4 switches are opened, and the current source driving the differential pair of transistors is switched off.

Figure 17. Reference Input Stage

# **RF N COUNTER**

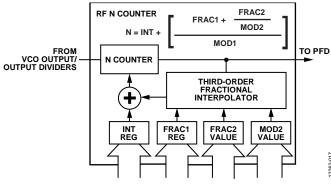

The RF N counter allows a division ratio in the PLL feedback path. The division ratio is determined by the INT, FRAC1, MOD1, FRAC2, and MOD2 values, which build up this divider (see Figure 18). Note that MOD1 is a fixed nonprogrammable value equal to 2<sup>24</sup>.

Figure 18. RF N Counter

# INT, FRAC, MOD, and R Counter Relationship

The INT, FRAC1, FRAC2, MOD1, and MOD2 values, in conjunction with the R counter, make it possible to generate output frequencies that are spaced by fractions of the PFD frequency ( $f_{PFD}$ ). For more information, see the RF Synthesizer—A Worked Example section.

Calculate the RF VCO frequency (RF<sub>OUT</sub>) by the following:

$$RF_{OUT} = f_{PFD} \times N \tag{1}$$

where:

$RF_{OUT}$  is the output frequency of the external VCO voltage controlled oscillator (without using the output divider).  $f_{PFD}$  is a frequency of phase frequency detector. N is the desired value of the feedback counter N.

Calculate the  $f_{PFD}$  by the following equation:

$$f_{PFD} = REF_{IN} \times \left[ (1+D)/(R \times (1+T)) \right] \tag{2}$$

where:

*REF*<sub>IN</sub> is the reference input frequency.

D is the REF<sub>IN</sub> doubler bit.

*R* is the preset divide ratio of the binary 10-bit programmable reference counter (1 to 1023).

T is the REF<sub>IN</sub> divide by 2 bit (0 or 1)

N comprises

$$N = INT + \frac{FRAC1 + \frac{FRAC2}{MOD2}}{MOD1}$$

(3)

where:

INT is the 16-bit integer value (23 to 32,767 for 4/5 prescaler, 75 to 65,535 for 8/9 prescaler).

*FRAC1* is the numerator of the primary modulus (1 - 16,777,215). *FRAC2* is the numerator of the 14-bit auxiliary modulus (1 - 16,383). *MOD2* is the programmable, 14-bit auxiliary fractional modulus (2 - 16,383).

MOD1 is a 24-bit primary modulus with a fixed value of  $2^{24}$  (16,777,216).

This results in a very fine frequency resolution with no residual frequency error. To apply this formula, take the following steps:

- 1. Calculate N by dividing RF<sub>OUT</sub>/f<sub>PFD</sub>.

- 2. The integer value of this number forms INT.

- 3. Subtract this value from the full N value.

- 4. Multiply the remainder by  $2^{24}$ .

- 5. The integer value of this number forms FRAC1.

- 6. Calculate the MOD2 basis on the channel spacing (f<sub>CHSP</sub>) by

$$MOD2 = f_{PFD}/GCD(f_{PFD}, f_{CHSP})$$

(4)

where

$f_{CHSP}$  is the desired channel spacing frequency.  $GCD(f_{PFD}, f_{CHSP})$  is a greatest common divider of the PFD frequency and the channel spacing frequency.

7. Calculate FRAC2 by the following equation:

$$FRAC2 = [(N - INT) \times 2^{24} - FRAC1)] \times MOD2$$

(5)

#### **INT N Mode**

If FRAC1 and FRAC2 = 0, the synthesizer operates in integer-N mode.

#### R Counter

The 10-bit R counter allows the input reference frequency,  $REF_{IN}$ , to be divided down to produce the reference clock to the PFD. Division ratios from 1 to 1023 are allowed.

#### PHASE FREQUENCY DETECTOR AND CHARGE PUMP

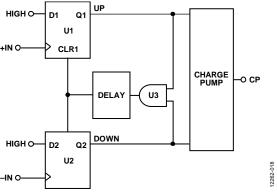

The phase frequency detector takes inputs from the R counter and N counter and produces an output proportional to the phase and frequency difference between them. Figure 19 is a simplified schematic of the phase frequency detector. The PFD includes a fixed delay element that sets the width of the antibacklash pulse (ABP), which is typically 2.6 ns. This pulse ensures that there is no dead zone in the PFD transfer function and provides a consistent reference spur level.

Figure 19. PFD Simplified Schematic

# **MUXOUT AND LOCK DETECT**

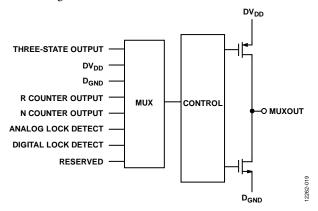

The output multiplexer on the ADF4155 allows the user to access various internal points on the chip. The state of MUXOUT is controlled by the M3, M2, and M1 bits in Register 4 (for further details, see Figure 28). Figure 20 shows the MUXOUT section in block diagram form.

Figure 20. MUXOUT Schematic

#### **INPUT SHIFT REGISTERS**

Data is clocked into the 32-bit shift register on each rising edge of CLK. The data is clocked in MSB first. Data is transferred from the shift register to one of the nine latches on the rising edge of LE.

The destination latch is determined by the state of the four control bits (C4, C3, C2, and C1) in the shift register. These are the four LSBs: DB3, DB2, DB1, and DB0, as shown in Figure 2. The truth table for these bits is shown in Table 5. Figure 22 and Figure 23 summarize how the latches are programmed.

Table 5. Truth Table for the C4, C3, C2, and C1 Control Bits

|    | Con | trol Bits |    |                 |

|----|-----|-----------|----|-----------------|

| C4 | C3  | C2        | C1 | Register        |

| 0  | 0   | 0         | 0  | Register 0 (R0) |

| 0  | 0   | 0         | 1  | Register 1 (R1) |

| 0  | 0   | 1         | 0  | Register 2 (R2) |

| 0  | 0   | 1         | 1  | Register 3 (R3) |

| 0  | 1   | 0         | 0  | Register 4 (R4) |

| 0  | 1   | 0         | 1  | Register 5 (R5) |

| 0  | 1   | 1         | 0  | Register 6 (R6) |

| 0  | 1   | 1         | 1  | Register 7 (R7) |

| 1  | 0   | 0         | 0  | Register 8 (R8) |

# **PROGRAM MODES**

Table 5 and Figure 24 through Figure 32 show how the program modes must be set up in the ADF4155.

The following ADF4155 settings are double buffered: the fractional value (FRAC1/FRAC2), the modulus value (MOD2), the reference doubler, the reference divide by 2 (RDIV2), the R counter value, the charge pump current setting, and the R divider select. This means that two events must occur before the device can use a new value for any of the double buffered settings. First, the new value must be latched into the device by writing to the appropriate register. Second, a new write must be performed on Register R0.

For example, any time that the modulus value is updated, Register 0 (R0) must be written to, to ensure that the modulus value is loaded correctly.

#### **OUTPUT STAGE**

For best spur performance, it is recommended to use the VCO output and disable the RF output (Bit DB6, Register 6) stage.

The RF output stage is used where lower frequency operation is required by enabling one of the output dividers.

The RF<sub>OUT</sub>+ and RF<sub>OUT</sub>- pins of the ADF4155 are connected to the collectors of an NPN differential pair driven by a signal from the RF divider block, as shown in Figure 21.

To optimize the output power requirements, the tail current of the differential pair is programmable using Bits[DB5:DB4] in Register 6 (R6). Four current levels can be set. These levels give output power levels of –4 dBm, –1 dBm, +2 dBm, and +5 dBm.

The current consumption as a function of the output power and the RF divider is shown in Table 6.

The output stage uses an internal 50  $\Omega$  resistor to RFV\_DD. An external pull-up inductor to RFV\_DD is necessary prior to ac coupling into a 50  $\Omega$  load. Alternatively, the output can be combined in a 1 + 1:1 transformer or a 180° microstrip coupler. If the outputs are used individually, the unused complimentary output must be terminated with a similar circuit to the used output.

Figure 21. Output Stage

Another feature of the ADF4155 is that the supply current to the RF output stage can be shut down until the device achieves lock as measured by the digital lock detect circuitry. This shutdown is enabled by using the mute till lock detect (MTLD) bit (DB11) in Register 6 (R6).

Table 6. Total  $I_{DD}$  (D $I_{DD}$  + A $I_{DD}$  + RF $I_{DD}$ )

| Divide By | RF <sub>OUT</sub> Off | $RF_{OUT} = -4 dBm$ | RF <sub>OUT</sub> = −1 dBm | RF <sub>OUT</sub> = +2 dBm | RF <sub>OUT</sub> = +5 dBm |

|-----------|-----------------------|---------------------|----------------------------|----------------------------|----------------------------|

| 1         | 37.4                  | 55.3                | 67.5                       | 83.9                       | 96.0                       |

| 2         | 46.5                  | 64.4                | 76.6                       | 93.0                       | 105.1                      |

| 4         | 53.1                  | 70.9                | 83.2                       | 99.6                       | 111.7                      |

| 8         | 61.3                  | 79.1                | 91.4                       | 107.8                      | 119.8                      |

| 16        | 66.3                  | 84.2                | 96.4                       | 112.8                      | 124.9                      |

| 32        | 70.4                  | 88.2                | 100.5                      | 116.9                      | 129.0                      |

| 64        | 72.9                  | 90.8                | 103.0                      | 119.4                      | 131.5                      |

# **REGISTER MAPS**

| _             |                                                                 |       |      |             |                                       |            |          |            |     |       |                                                 |       |      | RE   | GISTE            | R 0     |               |         |                             |                  |        |          |                        |                               |        |                  |          |       |         |         | _     |

|---------------|-----------------------------------------------------------------|-------|------|-------------|---------------------------------------|------------|----------|------------|-----|-------|-------------------------------------------------|-------|------|------|------------------|---------|---------------|---------|-----------------------------|------------------|--------|----------|------------------------|-------------------------------|--------|------------------|----------|-------|---------|---------|-------|

|               |                                                                 |       |      | RE          | SERVE                                 | ED.        |          |            |     |       | ชา<br>อย่า<br>ยัช<br>16-Bit integer value (int) |       |      |      |                  |         |               |         |                             |                  |        |          |                        | c                             | ONTROI | L BITS           |          |       |         |         |       |

| DB31          | DB30                                                            | DB29  | DB28 | DB27        | DB26                                  | DB25       | DB24     | DB23 D     | B22 | DB21  | DB20                                            | DB19  | DB18 | DB17 | DB16             | DB15 D  | B14           | DB13    | DB12                        | B11              | DB10   | DB9      | DB8                    | DB7                           | DB6    | DB5              | DB4      | DB3   | DB2     | DB1 [   | DB0   |

| 0             | 0                                                               | 0     | 0    | 0           | 0                                     | 0          | 0        | 0          | 0   | 0     | PR1                                             | N16   | N15  | N14  | N13              | N12     | N11           | N10     | N9                          | N8               | N7     | N6       | N5                     | N4                            | N3     | N2               | N1       | C4(0) | C3(0)   | C2(0) C | C1(0) |

|               |                                                                 |       |      |             |                                       |            |          |            |     |       |                                                 |       |      | RE   | GISTE            | R 1     |               |         |                             |                  |        |          |                        |                               |        |                  |          |       |         |         | _     |

|               | RESE                                                            | DVED  |      |             |                                       |            |          |            |     |       |                                                 |       |      |      |                  | VALUE ( | FRAC          | C1)     | ı                           | DBR <sup>1</sup> |        |          |                        |                               |        |                  |          |       | ONTROI  | L BITS  |       |

| DB31          |                                                                 |       | DB28 | DB27        | DB26                                  | DB25       | DB24     | DB23 D     | B22 | DB21  | DB20                                            | DB19  |      |      | DB16             |         |               | DB13    | DB12 I                      | B11              | DB10   | DB9      | DB8                    | DB7                           | DB6    | DB5              | DB4      | DB3   | DB2     | DB1 [   | DB0   |

| 0             | 0                                                               | 0     | 0    | F24         | F23                                   | F22        | F21      | -+         | 19  | F18   | F17                                             | F16   | F15  | F14  | F13              | -+      | F11           | F10     | F9                          | F8               | F7     | F6       | F5                     | F4                            | F3     | F2               | F1       | C4(0) |         | -       | C1(1) |

|               |                                                                 |       |      |             |                                       |            |          |            |     |       |                                                 |       |      | RF   | GISTE            | R 2     |               |         |                             |                  |        |          |                        |                               |        |                  | 1        | . (3) | .,,,    |         |       |

| $\overline{}$ |                                                                 |       |      |             |                                       |            |          |            |     |       |                                                 |       |      |      | 0.0.12           |         |               |         |                             |                  |        |          |                        |                               |        |                  |          |       |         |         |       |

|               | RESERVED 14-BIT AUXILIARY MODULUS VALUE (MOD2) DBR <sup>1</sup> |       |      |             |                                       |            |          |            |     |       |                                                 |       |      |      | c                | ONTROL  | . BITS        |         |                             |                  |        |          |                        |                               |        |                  |          |       |         |         |       |

| DB31          | DB30                                                            | DB29  | DB28 | DB27        | DB26                                  | DB25       | DB24     | DB23 D     | 322 | DB21  | DB20                                            | DB19  | DB18 | DB17 | DB16             | DB15 D  | B14           | DB13    | DB12 [                      | B11              | DB10   | DB9      | DB8                    | DB7                           | DB6    | DB5              | DB4      | DB3   | DB2 I   | DB1 [   | DB0   |

|               | 0                                                               | 0     | 0    | 0           | 0                                     | 0          | 0        | 0          | 0   | 0     | 0                                               | 0     | 0    | M14  | M13              | M12 I   | M11           | M10     | M9                          | м8               | М7     | М6       | M5                     | M4                            | МЗ     | M2               | M1       | C4(0) | C3(0) C | 2(1) C  | C1(0) |

| $\Box$        |                                                                 |       |      |             |                                       |            |          |            |     |       |                                                 |       |      | RE   | GISTE            | R 3     |               |         |                             |                  |        |          |                        |                               |        |                  |          |       |         |         |       |

|               |                                                                 |       |      |             |                                       | RESER      | VED      |            |     |       |                                                 |       |      |      |                  |         | 14-BI         | T AUXII | JARY FF                     | ACTI             | ONAL \ | WORD     | (FRA                   | C2)                           |        | DBR <sup>1</sup> |          |       | CONTRO  | L BITS  |       |

| DB31          | DB30                                                            | DB29  | DB28 | DB27        | DB26                                  | DB25       | DB24     | DB23 C     | B22 | DB21  | DB20                                            | DB19  | DB18 | DB17 | DB16             | DB15 [  | DB14          | DB13    | DB12                        | DB11             | DB10   | DB9      | DB8                    | DB7                           | DB6    | DB               | 5 DB4    | DB3   | DB2     | DB1     | DB0   |

| l -           | 0                                                               | 1     | 0    | 0           | 0                                     | 0          | 0        | 0          | 0   | 0     | 0                                               | 0     | 0    | P14  | P13              | P12     | P11           | P10     | P9                          | P8               | P7     | P6       | P5                     | P4                            | Р3     | P2               | P1       | C4(0) | C3(0)   | C2(1) C | C1(1) |

|               |                                                                 |       |      |             |                                       |            |          |            |     |       |                                                 |       |      | RE   | GISTE            | R 4     |               |         | <u> </u>                    |                  |        |          | _                      |                               |        | 1                | <u> </u> |       |         |         |       |

| RESERVED      | DITHER 2                                                        |       | MUXO | UT          | REFERENCE<br>DOUBLER DBR <sup>1</sup> | RDIV2 DBR1 |          |            |     | 10-   | BIT R                                           | COUNT | rer  |      | DBR <sub>1</sub> |         | DOUBLE BUFFER | Cŀ      | IARGE F<br>CURREI<br>SETTIN | UMP<br>NT<br>G D | DBR 1  | RESERVED | MUXOUT<br>LEVEL SELECT | PHASE<br>DETECTOR<br>POLARITY | PD     | CHARGE PUMP      | COUNTER  |       | CONTRO  | L BITS  |       |

| DB31          | DB30                                                            | DB29  | DB28 | DB27        | DB26                                  | DB25       | DB24     | DB23 C     | B22 | DB21  | DB20                                            | DB19  | DB18 | DB17 | DB16             | DB15    | DB14          | DB13    | DB12                        | DB11             | DB10   | DB9      | DB8                    | DB7                           | DB6    | DB5              | DB4      | DB3   | DB2     | DB1     | DB0   |

| C             | L2                                                              | МЗ    | M2   | M1          | RD2                                   | RD1        | R10      | R9         | R8  | R7    | R6                                              | R5    | R4   | R3   | R2               | R1      | D1            | CP4     | СРЗ                         | CP2              | CP1    | 0        | LVS                    | U4                            | U3     | U2               | U1       | C4(0) | C3(1)   | C2(0)   | C1(0) |

|               |                                                                 |       |      |             |                                       |            |          |            |     |       |                                                 |       |      | RE   | GISTE            | R 5     |               |         |                             |                  |        |          |                        |                               |        |                  |          |       |         |         | _     |

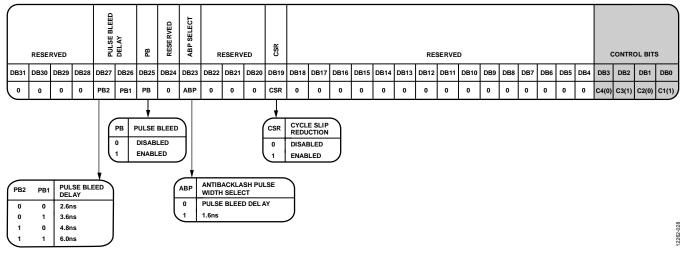

|               |                                                                 | ERVED |      | PULSE BLEED | DELAY                                 | - BB       | RESERVED | ABP SELECT | RE  | SERVE | ĒD                                              | CSR   |      |      |                  |         |               |         | RES                         | ERVE             | ED.    |          |                        |                               |        |                  |          |       | CONTRO  | L BITS  |       |

|               | RESE                                                            |       |      |             |                                       |            |          |            |     |       |                                                 |       |      |      |                  |         |               |         |                             | _                |        |          |                        |                               |        |                  |          |       |         |         |       |

| DB31          | l                                                               | DB29  | DB28 | DB27        | DB26                                  | DB25       | DB24     | $\vdash$   | B22 | DB21  | DB20                                            | DB19  | DB18 | DB17 | DB16             | DB15    | DB14          | DB13    | DB12                        | DB11             | DB10   | DB9      | DB8                    | DB7                           | DB6    | DB               | 5 DB4    | DB3   | DB2     | DB1     | DB0   |

$<sup>^{\</sup>rm 1}\,{\rm DBR}$  = DOUBLE BUFFERED REGISTER—BUFFERED BY THE WRITE TO REGISTER 0.

Figure 22. Register Summary (Register 0 to Register 5)

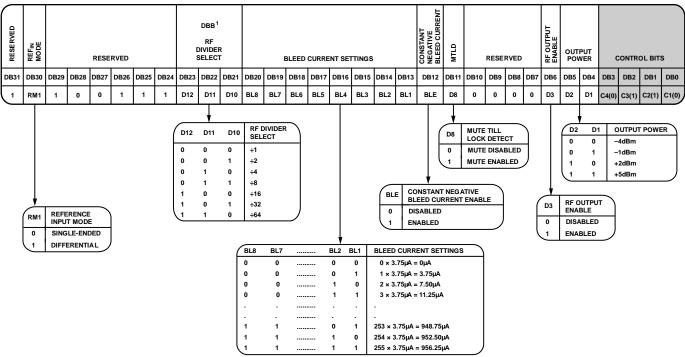

|          |                           |      |      |      |      |      |      |      |                                            |      |                        |      |      | RE   | GIST | ER 6 |           |      |      |      |      |     |                                                |     |     |              |       |       |       |       |     |

|----------|---------------------------|------|------|------|------|------|------|------|--------------------------------------------|------|------------------------|------|------|------|------|------|-----------|------|------|------|------|-----|------------------------------------------------|-----|-----|--------------|-------|-------|-------|-------|-----|

| RESERVED | REF <sub>IN</sub><br>MODE |      |      | RESE | RVED |      |      |      | DBB <sup>1</sup> RF DIVIDER SELECT         | ₹    | BLEED CURRENT SETTINGS |      |      |      |      |      | NEG BLEED | MTLD |      | RESE | RVED |     | RF OUTPUT<br>ENABLE<br>DAMON<br>AMON<br>TURNON |     |     | CONTROL BITS |       |       |       |       |     |

| DB31     | DB30                      | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22                                       | DB21 | DB20                   | DB19 | DB18 | DB17 | DB16 | DB15 | DB14      | DB13 | DB12 | DB11 | DB10 | DB9 | DB8                                            | DB7 | DB6 | DB5          | DB4   | DB3   | DB2   | DB1   | DB0 |

| 1        | RM1                       | 1    | 0    | 0    | 1    | 1    | 1    | D12  | D11 D10 BL8 BL7 BL6 BL5 BL4 BL3 BL2 BL1 BL |      |                        |      |      |      |      |      |           | BLE  | D8   | 0    | 0    | 0   | 0                                              | D3  | D2  | D1           | C4(0) | C3(1) | C2(1) | C1(0) |     |

|          |                           |      |      |      |      |      |      |      |                                            |      |                        |      |      | RE   | GIST | ER 7 |           |      |      |      |      |     |                                                |     |     |              |       |       |       |       |     |

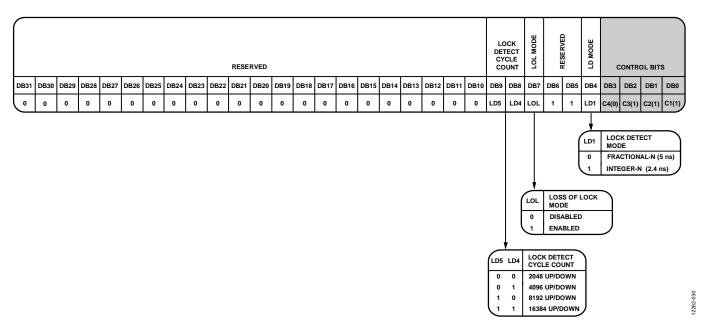

|      |      |      |      |      |      |      |      |      |      |      |      |      |      |      | OIO I |      |      |      |      |      |      |           |                            |          |          |          |         |       |        |         |       |

|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-------|------|------|------|------|------|------|-----------|----------------------------|----------|----------|----------|---------|-------|--------|---------|-------|

|      |      |      |      |      |      |      |      |      |      | RESE | RVED |      |      |      |       |      |      |      |      |      |      | DE1<br>CY | OCK<br>TECT<br>CLE<br>OUNT | TOL MODE | divarian | KESEKVED | LD MODE | c     | CONTRO | OL BITS |       |

| DB31 | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16  | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9       | DB8                        | DB7      | DB6      | DB5      | DB4     | DB3   | DB2    | DB1     | DB0   |

| G    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0    | 0    | 0    | 0    | 0    | 0    | LD5       | LD4                        | LOL      | 1        | 1        | LD1     | C4(0) | C3(1)  | C2(1)   | C1(1) |

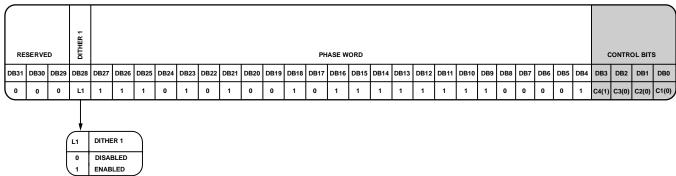

|      | REGISTER 8 |      |      |      |      |      |      |      |      |      |      |      |      |      |        |      |      |      |      |      |      |     |     |     |     |     |     |       |       |         |       |

|------|------------|------|------|------|------|------|------|------|------|------|------|------|------|------|--------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-------|-------|---------|-------|

|      |            |      |      |      |      |      |      |      |      |      |      |      |      |      |        |      |      |      |      |      |      |     |     |     |     |     |     |       |       |         |       |

|      |            |      | 1.   |      |      |      |      |      |      |      |      |      |      |      |        |      |      |      |      |      |      |     |     |     |     |     |     |       |       |         |       |

| RE   | SERVE      | D    | ОТНЕ |      |      |      |      |      |      |      |      |      |      | PH   | IASE W | ORD  |      |      |      |      |      |     |     |     |     |     |     | c     | ONTRO | OL BITS | s     |

| DB31 | DB30       | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16   | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3   | DB2   | DB1     | DB0   |

| Ū    | 0          | 0    | L1   | 1    | 1    | 1    | 0    | 1    | 0    | 1    | 0    | 0    | 1    | 0    | 1      | 1    | 1    | 1    | 1    | 1    | 1    | 1   | 0   | 0   | 0   | 0   | 1   | C4(1) | C3(0) | C2(0)   | C1(0) |

<sup>&</sup>lt;sup>1</sup> DBB = DOUBLE BUFFERED BITS—BUFFERED BY THE WRITE TO REGISTER 0 IF, AND ONLY IF, DB14 OF REGISTER 4 IS HIGH.

Figure 23. Register Summary (Register 6 to Register 8)

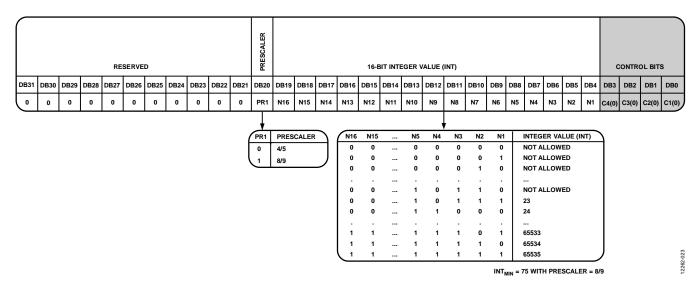

#### **REGISTER 0**

# **Register 0 Control Bits**

With Bits[C4:C1] set to 0000, Register 0 is programmed. Figure 24 shows the input data format for programming this register.

# 16-Bit Integer Value (INT)

The 16 bits [DB19:DB4] set the INT value, which determines the integer part of the feedback division factor. The INT value is used in Equation 3 (see the INT, FRAC, MOD, and R Counter Relationship section). All integer values from 23 to 32,767 are allowed for 4/5 prescaler. For prescaler 8/9, the minimum integer value is 75, and the maximum integer value value is 65,535.

# Prescaler (P) Value

The dual-modulus prescaler (P/P + 1), along with the INT, FRAC1, MOD1, FRAC2, and MOD2 counters, determines the overall division ratio from the VCO output to the PFD input.

Operating at CML levels, the prescaler takes the clock from the VCO output and divides it down for the counters. It is based on a synchronous 4/5 core. When the prescaler is set to 4/5, the maximum RF frequency allowed is 6 GHz. Therefore, when operating the ADF4155 above 6 GHz, set the prescaler to 8/9. The prescaler limits the INT value to the following:

- P = 4/5,  $INT_{MIN} = 23$ ,  $INT_{MAX} = 32,767$

- P = 8/9,  $INT_{MIN} = 75$ ,  $INT_{MAX} = 65,535$

In the ADF4155, the PR1 bit (DB20) in Register 0 sets the prescaler value.

Figure 24. Register 0 (R0)

# **REGISTER 1**

# **Register 1 Control Bits**

With Bits[C4:C1] set to 0001, Register 1 is programmed. Figure 25 shows the input data format for programming this register.

# 24-Bit Main Fractional Value (FRAC1)

The 24 FRAC1 bits [DB27:DB4] together with FRAC2 and MOD2 set the numerator of the fraction that is input to the  $\Sigma$ - $\Delta$

modulator. This fraction, along with the INT value, specifies the new frequency channel that the synthesizer locks to, as shown in the RF Synthesizer—A Worked Example section. FRAC1 values from 0 to  $(2^{24}-1)$  cover channels over a frequency range equal to the PFD reference frequency.

| $\bigcap$ |      |      |      |      |      |      |      |      |      |      |                                        |                     |        |         |                                                                  |        |                                   |                   |      |                  |       |     |     |     |     |     |     |       |       |        |       |

|-----------|------|------|------|------|------|------|------|------|------|------|----------------------------------------|---------------------|--------|---------|------------------------------------------------------------------|--------|-----------------------------------|-------------------|------|------------------|-------|-----|-----|-----|-----|-----|-----|-------|-------|--------|-------|

|           | RESE | RVED |      |      |      |      |      |      |      |      |                                        | 24                  | -BIT M | AIN FR  | ACTIO                                                            | NAL VA | LUE (FF                           | RAC1)             |      | DBR <sup>1</sup> |       |     |     |     |     |     |     | 0     | ONTRO | DL BIT | S     |

| DB31      | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20                                   | DB19                | DB18   | DB17    | DB16                                                             | DB15   | DB14                              | DB13              | DB12 | DB11             | DB10  | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3   | DB2   | DB1    | DB0   |

| ( o       | 0    | 0    | 0    | F24  | F23  | F22  | F21  | F20  | F19  | F18  | F17                                    | F16                 | F15    | F14     | F13                                                              | F12    | F11                               | F10               | F9   | F8               | F7    | F6  | F5  | F4  | F3  | F2  | F1  | C4(0) | C3(0) | C2(0)  | C1(1) |

|           |      |      |      |      |      |      |      |      |      |      | F2:<br>0<br>0<br>0<br>0<br>1<br>1<br>1 | 4 F23 0 0 0 0 1 1 1 |        | F 0 1 1 | ) (1) (1) (1) (1) (2) (3) (4) (4) (4) (4) (4) (4) (4) (4) (4) (4 |        | MAIN I  0  1  2  3  167772 167772 | 212<br>213<br>214 | ONAL | VALUE            | (FRAC | 1)  |     |     |     |     |     |       |       |        |       |

$^{\rm 1}$  DBR = DOUBLE BUFFERED REGISTER—BUFFERED BY THE WRITE TO REGISTER 0.

Figure 25. Register 1 (R1)

#### **REGISTER 2**

# **Register 2 Control Bits**

With Bits[C4:C1] set to 0010, Register 2 is programmed. Figure 26 shows the input data format for programming this register.

# 14-Bit Auxiliary Modulus Value (MOD2)

The 14 MOD2 bits [DB17:DB4] set the auxiliary fractional modulus. The auxiliary fractional modulus is used to correct any residual error due to the main fractional modulus. For more information, see the RF Synthesizer—A Worked Example section.

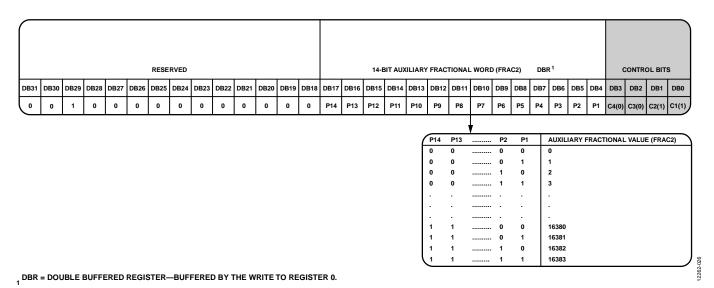

#### **REGISTER 3**

# **Register 3 Control Bits**

With Bits[C4:C1] set to 0011, Register 3 is programmed. Figure 27 shows the input data format for programming this register.

# 14-Bit Auxiliary Fractional Value (FRAC2)

The auxiliary fractional value bits [DB17:DB4] control the auxiliary fractional word. The word must be less than the MOD2 value programmed in Register 2.

|                    |      |      | RESER | RVED |      |      |      |      |      |      |      |      | 1    | 4-BIT A | <b>NUXILIA</b> | RY MO                                 | DULUS                     | S VALUI | E (MOI | D2)                  | DBI        | R <sup>1</sup>   |                   |       | c     | ONTRO  | OL BIT | s    |

|--------------------|------|------|-------|------|------|------|------|------|------|------|------|------|------|---------|----------------|---------------------------------------|---------------------------|---------|--------|----------------------|------------|------------------|-------------------|-------|-------|--------|--------|------|

| DB31 DB30 DB29 DB2 | DB27 | DB26 | DB25  | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14    | DB13           | DB12                                  | DB11                      | DB10    | DB9    | DB8                  | DB7        | DB6              | DB5               | DB4   | DB3   | DB2    | DB1    | DB0  |

| 0 0 0 0            | 0    | 0    | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | M14  | M13  | M12  | M11     | M10            | М9                                    | М8                        | M7      | М6     | М5                   | М4         | МЗ               | M2                | М1    | C4(0) | C3(0)  | C2(1)  | C1(0 |

|                    |      |      |       |      |      |      |      |      |      |      |      |      |      |         |                | M1<br>0<br>0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>0<br>0<br>0<br> |         |        | 0<br>0<br>1<br>1<br> | M1 0 1 0 1 | 0<br>1<br>2<br>3 | 380<br>381<br>382 | RY MO | DULU  | S VALU | JE (MO | D2)  |

Figure 26. Register 2 (R2)

Figure 27. Register 3 (R3)

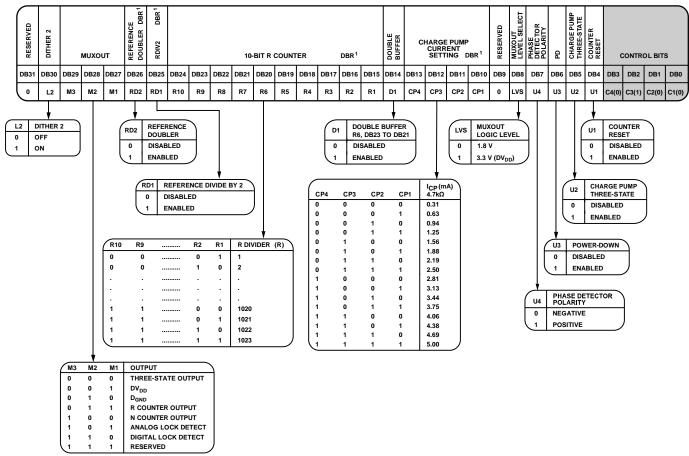

#### **REGISTER 4**

# **Register 4 Control Bits**

With Bits[C4:C1] set to 0100, Register 4 is programmed. Figure 28 shows the input data format for programming this register.

#### Dither 2

Dither to the second stage of the main  $\Sigma$ - $\Delta$  modulator can be activated on the ADF4155 by setting Bit DB30 in Register 4 (see Figure 28) to 1. This feature allows the user to optimize a design for improved spurious performance.

Dither randomizes the fractional quantization noise so that it resembles white noise rather than spurious noise. As a result, the device is optimized for improved spurious performance. This operation is normally used for fast locking applications when the PLL closed-loop bandwidth is wide.

#### **MUXOUT**

The on-chip multiplexer is controlled by Bits[DB29:DB27] (see Figure 28).

#### Reference Doubler

Setting DB26 to 0 feeds the reference frequency input (REF $_{\rm IN}$ ) directly to the 10-bit R counter, disabling the doubler. Setting this bit to 1 multiplies the REF $_{\rm IN}$  by a factor of 2 before feeding it into the 10-bit R counter. When the doubler is disabled, the REF $_{\rm IN}$  falling edge is the active edge at the PFD input to the fractional synthesizer. When the doubler is enabled, both the rising and falling edges of REF $_{\rm IN}$  become active edges at the PFD input.

When the doubler is enabled and the dither is enabled, the in-band phase noise performance is sensitive to the REF  $_{\rm IN}$  duty cycle. The phase noise degradation can be as much as 5 dB for REF  $_{\rm IN}$  duty cycles outside a 45% to 55% range. The phase noise is insensitive to the REF  $_{\rm IN}$  duty cycle when the dither is switched off and when the doubler is disabled.

The maximum allowable REF $_{\rm IN}$  frequency when the reference doubler is enabled is 80 MHz.

# RDIV2

Setting the DB25 bit to 1 inserts a divide by 2 toggle flip-flop between the R counter and PFD, which extends the maximum REF $_{\rm IN}$  input rate. This function allows a 50% duty cycle signal to appear at the PFD input, which is necessary for cycle slip reduction.

### 10-Bit R Counter

The 10-bit R counter allows the input reference frequency ( $REF_{IN}$ ) to be divided down to produce the reference clock to the PFD. Division ratios from 1 to 1023 are allowed.

# Double Buffer

The DB14 bit enables or disables double buffering of Bits[DB23:DB21] in Register 6. The Program Modes section explains how double buffering works.

#### **Charge Pump Current Setting**

Bits[DB13:DB10] set the charge pump current. Set this value to the charge pump current that the loop filter is designed with (see Figure 28).

# **MUXOUT Level Select**

The DB8 bit sets the voltage level used on the MUXOUT output. If the bit is programmed to 0, the MUXOUT uses a value of 1.8 V as the high level. When this bit is set to 1, the high level on the MUXOUT output is equal to  $DV_{DD}$  (3.3 V  $\pm$  5%).