# Intel® Atom<sup>™</sup> Processor Z3600 and Z3700 Series

**Specification Update**

May 2015

**Revision 009**

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No computer system can be absolutely secure. Check with your system manufacturer or retailer or learn more at intel.com.

Intel technologies may require enabled hardware, specific software, or services activation. Check with your system manufacturer or retailer.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or visit www.intel.com/design/literature.htm.

Intel, the Intel logo, and Intel Atom are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

© 2015 Intel Corporation. All rights reserved.

# **Contents**

| Preface                       | 5  |

|-------------------------------|----|

| Summary Tables of Changes     | 7  |

| Identification Information    | 15 |

| Component Marking Information | 18 |

| Errata                        | 19 |

| Specification Changes         | 46 |

| Specification Clarifications  | 47 |

| Documentation Changes         | 48 |

# §

# **Revision History**

| Document<br>Number | Revision Numbe | Description                                                                                                                                                                                                                                                                                                    | Revision Date  |

|--------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 329475             | 001            | · Initial release                                                                                                                                                                                                                                                                                              | September 2013 |

| 329475             | 002            | <ul> <li>Changed title of the Specification Update collateral</li> <li>Added SKUs</li> <li>Added B-3 stepping errata</li> <li>Errata <ul> <li>Changed Status of VLT5, VLT6, VLT39, VLT43, VLT44, VLT45</li> </ul> </li> <li>Added VLT46-VLT57.</li> </ul>                                                      | November 2013  |

| 329475             | 003            | Errata     Added VLT58-VLT64                                                                                                                                                                                                                                                                                   | January 2014   |

| 329475             | 004            | <ul> <li>Changed the title of the Specification Update collateral</li> <li>Added SKUs: Z3745, Z3745D, Z3735D, Z3735E, Z3795, Z3775D, Z3735G, Z3735F.</li> <li>Added C-0 stepping</li> <li>Errata <ul> <li>Changed Status of VLT6, VLT39, VLT43, VLT44, VLT45</li> <li>Added VLT65-VLT68</li> </ul> </li> </ul> | May 2014       |

| 329475             | 005            | <ul> <li>Added SKU: Z3785, Z3736F, Z3736G.</li> <li>Errata <ul> <li>Added VLT69-VLT76</li> </ul> </li> <li>Specification Clarifications <ul> <li>Added VLT1</li> </ul> </li> </ul>                                                                                                                             | September 2014 |

| 329475             | 006            | · No change                                                                                                                                                                                                                                                                                                    | December 2014  |

| 329475             | 007            | <ul> <li>Added SKU: Z3785, Z3736F, Z3736G.</li> <li>Errata</li> <li>Added VLT77-VLT79</li> </ul>                                                                                                                                                                                                               | January 2015   |

| 329475             | 008            | <ul> <li>Errata</li> <li>Added VLT80-VLT81</li> </ul>                                                                                                                                                                                                                                                          | February 2015  |

| 329475             | 009            | <ul> <li>Errata</li> <li>Added VLT82-VLT83</li> </ul>                                                                                                                                                                                                                                                          | May 2015       |

# Preface

This document is an update to the specifications contained in the documents listed in the following Affected Documents table. It is a compilation of device and document errata and specification clarifications and changes, and is intended for hardware system manufacturers and for software developers of applications, operating system, and tools.

Information types defined in the Nomenclature section of this document are consolidated into this document and are no longer published in other documents. This document may also contain information that has not been previously published.

*Note:* Throughout this document Intel® Atom<sup>™</sup> Processor Z3600 and Z3700 Series SoC is referred as Processor or SoC.

# **Affected Documents**

| Document Title                                                                         | Document Number <sup>1</sup> |

|----------------------------------------------------------------------------------------|------------------------------|

| Intel® Atom <sup>™</sup> Processor Z3600 and Z3700 Series Datasheet<br>(Volume 1 of 2) | 329474                       |

| Intel® Atom <sup>™</sup> Processor Z3600 and Z3700 Series Datasheet<br>(Volume 2 of 2) | 329518                       |

**NOTE:** <sup>1</sup> Contact local Intel representative for the latest document number.

# **Related Documents**

Please refer to the following documents which may be beneficial when reading this document or for additional information:

| Document                                                       | Document Number                                               |

|----------------------------------------------------------------|---------------------------------------------------------------|

| Intel® 64 and IA-32 Architectures Software Developer's Manuals |                                                               |

| Volume 1: Basic Architecture                                   |                                                               |

| Volume 2A: Instruction Set Reference, A-M                      |                                                               |

| Volume 2B: Instruction Set Reference, N-Z                      | http://www.intel.com/products/<br>processor/manuals/index.htm |

| Volume 3A: System Programming Guide                            |                                                               |

| Volume 3B: System Programming Guide                            |                                                               |

| Document                                                                            | Document Number                                                                                                                           |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Intel® 64 and IA-32 Architectures Software Developer's Manual Documentation Changes | http://www.intel.com/content/w<br>ww/us/en/architecture-and-<br>technology/64-ia-32-<br>architectures-software-<br>developers-manual.html |

# Nomenclature

**Errata** are design defects or errors in engineering samples. Errata may cause the processor behavior to deviate from published specifications. Hardware and software designed to be used with any given stepping assumes that all errata documented for that stepping are present on all devices.

**S-Spec Number** is a five-digit code used to identify products. Products are differentiated by their unique characteristics, that is, core speed, L2 cache size, and package type as described in the processor identification information table. Read all notes associated with each S-Spec number.

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in any new release of the specification.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in any new release of the specification.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

*Note:* Errata remain in the specification update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications, and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, and so forth).

§

# **Summary Tables of Changes**

The following table indicates the Specification Changes, Errata, Specification Clarifications, or Documentation Changes, which apply to the listed steppings. Intel intends to fix some of the errata in a future stepping of the component, and to account for the other outstanding issues through documentation or Specification Changes as noted. This table uses the following notations:

# Codes Used in Summary Table

# Stepping

**X**: Erratum, Specification Change or Clarification that applies to this stepping.

**(No mark) or (Blank Box)**: This erratum is fixed in listed stepping or specification change does not apply to list stepping.

# **Status**

**Doc**: Document change or update that will be implemented.

Plan Fix: This erratum may be fixed in a future stepping of the product.

Fixed: This erratum has been previously fixed.

**No Fix**: There is no plan to fix this erratum.

# Row

| Number | Stepping |     |     | Chathan | Errata Title                                                                             |

|--------|----------|-----|-----|---------|------------------------------------------------------------------------------------------|

| Number | B-2      | B-3 | C-0 | Status  | Enala Inte                                                                               |

| VLT1   | Х        | Х   | Х   | No Fix  | Accessing Unimplemented ISP MMIO<br>Space May Cause a System Hang                        |

| VLT2   | х        | х   | Х   | No Fix  | Quad Word Transactions in Violation of<br>Programming Model May Result in<br>System Hang |

| VLT3   | Х        | Х   | Х   | No Fix  | GPIO Registers Do Not Support 8 or 16-bit Transactions                                   |

| Number | Stepping |     |     | - Status | Errata Title                                                                                      |

|--------|----------|-----|-----|----------|---------------------------------------------------------------------------------------------------|

| Number | B-2      | B-3 | C-0 | Status   | Enala fille                                                                                       |

| VLT4   | Х        | Х   | х   | No Fix   | CSI Interface May Not Correct Certain<br>Single-bit Errors                                        |

| VLT5   | х        | -   | -   | Fixed    | ULPI Bus Marginality for USB Device<br>Mode                                                       |

| VLT6   | х        | Х   | -   | Fixed    | Anomalies in USB xHCI PME Enable<br>and PME Status                                                |

| VLT7   | Х        | х   | х   | No Fix   | eMMC Asynchronous Abort May Cause<br>a Hang                                                       |

| VLT8   | х        | х   | х   | No Fix   | SD Host Controller Incorrectly Reports<br>Supporting of Suspend/ Resume<br>Feature                |

| VLT9   | Х        | х   | х   | No Fix   | SD Host Controller Error Status<br>Registers May be Incorrectly Set                               |

| VLT10  | Х        | х   | х   | No Fix   | SD Host Controller Registers Are Not<br>Cleared by Software Reset                                 |

| VLT11  | х        | Х   | х   | No Fix   | Timing Specification Violation on SD<br>Card Interface                                            |

| VLT12  | х        | х   | х   | No Fix   | SD Card Controller Does Not Disable<br>Clock During Card Power Down                               |

| VLT13  | х        | х   | х   | No Fix   | Reset Sequence May Take longer Than<br>Expected When ACG is Enabled in SD<br>And SDIO Controllers |

| VLT14  | Х        | х   | х   | No Fix   | xHCI Port Assigned Highest SlotID<br>When Resuming From Sx Issue                                  |

| VLT15  | Х        | х   | х   | No Fix   | LFPS Detect Threshold                                                                             |

| VLT16  | Х        | Х   | х   | No Fix   | Set Latency Tolerance Value Command<br>Completion Event Issue                                     |

| VLT17  | х        | Х   | х   | No Fix   | xHCI Data Packet Header and Payload<br>Mismatch Error Condition                                   |

| VLT18  | Х        | Х   | х   | No Fix   | USB xHCI SuperSpeed Packet with<br>Invalid Type Field Issue                                       |

| Number | Stepping |     |     | Status | Erroto Titlo                                                                                 |

|--------|----------|-----|-----|--------|----------------------------------------------------------------------------------------------|

| Number | B-2      | B-3 | C-0 | Status | Errata Title                                                                                 |

| VLT19  | Х        | Х   | x   | No Fix | USB xHCI Behaviour with Three<br>Consecutive Failed U3 Entry Attempts                        |

| VLT20  | Х        | х   | x   | No Fix | USB xHCI Max Packet Size and<br>Transfer Descriptor Length Mismatch                          |

| VLT21  | х        | Х   | х   | No Fix | USB EHCI RMH Port Disabled Due to<br>Device Initiated Remote Wake                            |

| VLT22  | х        | Х   | x   | No Fix | USB EHCI Isoch In Transfer Error<br>Issue                                                    |

| VLT23  | Х        | Х   | x   | No Fix | USB EHCI Babble Detected with SW<br>Overscheduling                                           |

| VLT24  | х        | Х   | x   | No Fix | USB EHCI Full-/low-speed EOP Issue                                                           |

| VLT25  | Х        | Х   | х   | No Fix | USB EHCI Asynchronous Retries<br>Prioritized Over Periodic Transfers                         |

| VLT26  | Х        | Х   | x   | No Fix | USB EHCI FS/LS Incorrect Number of Retries                                                   |

| VLT27  | Х        | Х   | x   | No Fix | USB EHCI RMH Think Time Issue                                                                |

| VLT28  | Х        | х   | x   | No Fix | USB EHCI Full-/low-speed Device<br>Removal Issue                                             |

| VLT29  | Х        | х   | х   | No Fix | Reported Memory Type May Not Be<br>Used to Access the VMCS and<br>Referenced Data Structures |

| VLT30  | Х        | х   | х   | No Fix | A Page Fault May Not be Generated<br>When the PS bit is set to "1" in a<br>PML4E or PDPTE    |

| VLT31  | Х        | Х   | x   | No Fix | CS Limit Violations May Not be<br>Detected After VM Entry                                    |

| VLT32  | Х        | Х   | x   | No Fix | IA32_DEBUGCTL.FREEZE_PERFMON_O<br>N_PMI is Incorrectly Cleared by SMI                        |

| VLT33  | Х        | Х   | х   | No Fix | PEBS Record EventingIP Field May be<br>Incorrect After CS.Base Change                        |

| Number | Stepping |     |     | Status | Erroto Titlo                                                                                                                   |

|--------|----------|-----|-----|--------|--------------------------------------------------------------------------------------------------------------------------------|

| Number | B-2      | B-3 | C-0 | Status | Errata Title                                                                                                                   |

| VLT34  | Х        | х   | ×   | No Fix | Some Performance Counter Overflows<br>May Not be Logged in<br>IA32_PERF_GLOBAL_STATUS When<br>FREEZE_PERFMON_ON_PMI is Enabled |

| VLT35  | Х        | Х   | х   | No Fix | MOVNTDQA From WC Memory May<br>Pass Earlier Locked Instructions                                                                |

| VLT36  | Х        | х   | х   | No Fix | Unsynchronized Cross-Modifying Code<br>Operations Can Cause Unexpected<br>Instruction Execution Results                        |

| VLT37  | Х        | Х   | х   | No Fix | SDIO Host Controller Does Not Control the SDIO Bus Power                                                                       |

| VLT38  | Х        | Х   | х   | No Fix | USB HSIC Ports Incorrectly Reported as Removable                                                                               |

| VLT39  | Х        | х   | -   | Fixed  | Multiple Threads That Access the ISP<br>Concurrently May Lead to a System<br>Hang                                              |

| VLT40  | х        | x   | х   | No Fix | Premature Asynchronous Interrupt<br>Enabling May Lead to Loss of SDIO Wi-<br>Fi Functionality                                  |

| VLT41  | Х        | x   | х   | No Fix | Paging Structure Entry May be Used<br>Before Accessed And Dirty Flags Are<br>Updated                                           |

| VLT42  | х        | x   | х   | No Fix | Certain eMMC Host Controller<br>Registers Are Not Cleared by Software<br>Reset                                                 |

| VLT43  | Х        | Х   | -   | Fixed  | The Display May Flicker After an MIPI-<br>DSI LP to HS Transition                                                              |

| VLT44  | Х        | х   | -   | Fixed  | LPDDR3 Power-Up Timing                                                                                                         |

| VLT45  | Х        | Х   | -   | Fixed  | Using MIPI DSI in LP Mode May Result<br>in Unpredictable Display Behavior                                                      |

| VLT46  |          | X   | х   | No Fix | USB Device Mode Controller May Not<br>Successfully Switch to High Speed<br>Data Rate                                           |

| Number | Stepping |     |     | - Status | Emoto Title                                                                                           |

|--------|----------|-----|-----|----------|-------------------------------------------------------------------------------------------------------|

| Number | B-2      | B-3 | C-0 | Status   | Errata Title                                                                                          |

| VLT47  |          | x   | x   | No Fix   | USB Device Mode Controller Response<br>Time May Exceed The Specification                              |

| VLT48  |          | х   | х   | No Fix   | USB Device Mode Controller May Not<br>Enter the SS.Inactive State                                     |

| VLT49  |          | x   | х   | No Fix   | USB EHCI Full-/Low-speed Port Reset<br>or Clear TT Buffer Request                                     |

| VLT50  |          | x   | х   | No Fix   | USB Device Mode Controller LFPS<br>Transmission Period Does Not Meet<br>USB3.0 Specification          |

| VLT51  | Х        | х   | х   | No Fix   | Performance Monitor Instructions<br>Retired Event May Not Count<br>Consistently                       |

| VLT52  | Х        | Х   | х   | No Fix   | MTF VM Exit May be Delayed Following<br>a VM Entry That Injects a Software<br>Interrupt               |

| VLT53  | Х        | Х   | х   | No Fix   | LBR Stack And Performance Counter<br>Freeze on PMI May Not Function<br>Correctly                      |

| VLT54  | Х        | x   | x   | No Fix   | USB Legacy Support SMI Not Available<br>from xHCI Controller                                          |

| VLT55  | Х        | х   | x   | No Fix   | SD Card UHS-I Mode is Not Fully<br>Supported                                                          |

| VLT56  | Х        | x   | Х   | No Fix   | EOI Transactions May Not be Sent if<br>Software Enters Core C6 During an<br>Interrupt Service Routine |

| VLT57  | Х        | x   | x   | No Fix   | USB xHCI May Execute a Stale<br>Transfer Request Block (TRB)                                          |

| VLT58  | Х        | x   | x   | No Fix   | Certain MIPI CSI Sensors May Not<br>Operate Correctly At Low Clock<br>Frequencies                     |

| VLT59  | Х        | x   | x   | No Fix   | SD Card Initialization Sequence May<br>Fail When ACG is Enabled in SD<br>Controller                   |

| VLT60  | Х        | х   | x   | No Fix   | Reset Sequence May Not Complete<br>Under Certain Conditions                                           |

| Number | Stepping |     |     | - Status | Errata Title                                                                                                   |

|--------|----------|-----|-----|----------|----------------------------------------------------------------------------------------------------------------|

| Number | B-2      | B-3 | C-0 | Status   |                                                                                                                |

| VLT61  | Х        | Х   | Х   | No Fix   | Multiple Drivers That Access the GPIO<br>Registers Concurrently May Result in<br>Unpredictable System Behavior |

| VLT62  | Х        | Х   | х   | No Fix   | Boot May Not Complete When SMI<br>Occurs during Boot                                                           |

| VLT63  | Х        | х   | х   | No Fix   | Interrupts That Target an APIC That is<br>Being Disabled May Result in a System<br>Hang                        |

| VLT64  | Х        | Х   | х   | No Fix   | Corrected or Uncorrected L2 Cache<br>Machine Check Errors May Log<br>Incorrect Address in IA32_MCi_ADDR        |

| VLT65  | х        | х   | х   | No Fix   | Software-initiated Partition Reset May<br>Cause a System Hang                                                  |

| VLT66  | Х        | Х   | х   | No Fix   | Write-1-Clear Bits in PMC Registers<br>May be Unexpectedly Cleared                                             |

| VLT67  | Х        | х   | х   | No Fix   | Port Reset on USB2 Port0 And Port1<br>May Cause a Reset on HSIC Port0 and<br>Port1 Respectively                |

| VLT68  | Х        | х   | х   | No Fix   | Frequency Reported by CPUID<br>Instruction May Not Match Published<br>Frequency                                |

| VLT69  | Х        | Х   | х   | No Fix   | Machine Check Status Overflow Bit<br>May Not be Set                                                            |

| VLT70  | Х        | х   | х   | No Fix   | Attempts to Clear Performance<br>Counter Overflow Bits May Not<br>Succeed                                      |

| VLT71  | Х        | Х   | х   | No Fix   | SMI in 64 Bit Mode May Store an<br>Incorrect RIP to SMRAM When CS has<br>a Non-Zero Base                       |

| VLT72  | Х        | Х   | х   | No Fix   | VM Exit May Set IA32_EFER.NXE When IA32_MISC_ENABLE Bit 34 is Set to 1                                         |

| VLT73  | Х        | Х   | х   | No Fix   | Top Swap Mechanism May Become<br>Incorrectly Configured                                                        |

| Number |     | Stepping |     | Status | Errata Title                                                                                                             |

|--------|-----|----------|-----|--------|--------------------------------------------------------------------------------------------------------------------------|

| Number | B-2 | B-3      | C-0 | Status | Errata fitte                                                                                                             |

| VLT74  | Х   | Х        | х   | No Fix | Certain Peripheral I/O Controllers May<br>Hang After an Unexpectedly Long<br>Latency Memory Transaction                  |

| VLT75  | Х   | Х        | х   | No Fix | Disabling SDIO or SDCARD May Lead<br>To a System Hang                                                                    |

| VLT76  | Х   | х        | х   | No Fix | System May Hang When Attempting to Exit an S0ix Idle State                                                               |

| VLT77  | Х   | х        | х   | No Fix | TLB Entries May Not Be Invalidated<br>Properly When Bit 8 Is Set in EPT<br>Paging-Structure Entries                      |

| VLT78  | Х   | Х        | х   | No Fix | System May Hang During Entry to S0ix                                                                                     |

| VLT79  | Х   | х        | х   | No Fix | CPUID Instruction Leaf OAH May<br>Return an Unexpected Value                                                             |

| VLT80  | Х   | х        | ×   | No Fix | VM Exits During Execution of INTn in<br>Virtual-8086 Mode with Virtual-Mode<br>Extensions May Save RFLAGS<br>Incorrectly |

| VLT81  | Х   | Х        | х   | No Fix | Clearing IA32_MC0_CTL[5] May<br>Prevent Machine Check Notification                                                       |

| VLT82  | Х   | Х        | х   | No Fix | System May Unexpectedly Reboot<br>After Shutdown                                                                         |

| VLT83  | Х   | х        | х   | No Fix | APIC Timer Interrupt May Not Wake<br>The System From CS                                                                  |

| Number | Specification Changes        |

|--------|------------------------------|

|        | None                         |

| Number | Specification Clarifications |

| VLT1   | Top Swap Feature             |

| Number | Documentation Changes        |

|        | None                         |

§

# **Identification Information**

Intel® Atom<sup>™</sup> Processor Z3600 and Z3700 Series samples on 22-nm process processor signature can be identified by the following registers contents:

| Reserved | Extended<br>Family <sup>1</sup> | Extended<br>Model <sup>2</sup> | Reserved | Processor<br>Type <sup>3</sup> | Family<br>Code <sup>4</sup> | Model<br>Number <sup>5</sup> | Stepping<br>I D <sup>6</sup> |

|----------|---------------------------------|--------------------------------|----------|--------------------------------|-----------------------------|------------------------------|------------------------------|

| 31:28    | 27:20                           | 19:16                          | 15:13    | 12                             | 11:8                        | 7:4                          | 3:0                          |

| 0000     | 0000000b                        | 0011b                          | 000b     | Ob                             | 0110b                       | 0111b                        | 1000b                        |

#### NOTES:

- 1. The Extended Family, Bits [27:20] are used in conjunction with the Family Code, specified in Bits [11:8], to indicate whether the processor belongs to the Intel386<sup>™</sup>, Intel486<sup>™</sup>, Pentium®, Pentium® Pro, Pentium® 4, Intel® Core<sup>™</sup>2, or Intel® Atom<sup>™</sup> processor series.

- 2. The Extended Model, Bits [19:16] in conjunction with the Model Number, specified in Bits [7:4], are used to identify the model of the processor within the processor's family.

- 3. The Processor Type, specified in Bits [13:12] indicates whether the processor is an original OEM processor, an OverDrive processor, or a dual processor (capable of being used in a dual processor system).

- 4. The Family Code corresponds to Bits [11:8] of the EDX register after RESET, Bits [11:8] of the EAX register after the CPUID instruction is executed with a 1 in the EAX register, and the generation field of the Device ID register is accessible through Boundary Scan.

- 5. The Model Number corresponds to Bits [7:4] of the EDX register after RESET, Bits [7:4] of the EAX register after the CPUID instruction is executed with a 1 in the EAX register, and the model field of the Device ID register is accessible through Boundary Scan.

- 6. The Stepping ID in Bits [3:0] indicates the revision number of that model.

When EAX is initialized to a value of 1, the CPUID instruction returns the Extended Family, Extended Model, Type, Family, Model and Stepping value in the EAX register.

*Note:* The EDX processor signature value after reset is equivalent to the processor signature output value in the EAX register.

| S-Spec | Stepping | Processor<br>Number | Core Speed                          |                                    |                                   | s<br>S                 | Integrated Graphics<br>Core Speed |                   |                  |                  |

|--------|----------|---------------------|-------------------------------------|------------------------------------|-----------------------------------|------------------------|-----------------------------------|-------------------|------------------|------------------|

|        |          |                     | Burst<br>Frequency<br>Mode<br>(BFM) | High<br>Frequency<br>Mode<br>(HFM) | Low<br>Frequency<br>Mode<br>(LFM) | Memory<br>Frequency    | Burst<br>Frequency                | Base<br>Frequency | H-DID/<br>H-RID1 | G-DID/<br>G-RID2 |

| SR1M3  | B-2      | Z3770               | 2.4 GHz                             | 1.46 GHz                           | 532 MHz                           | LPDDR3 -<br>1067MT/s   | 667 MHz                           | 311 MHz           | 0F00h/09h        | 0F31h/09h        |

| SR1M5  | B-2      | Z3740               | 1.8 GHz                             | 1.33 GHz                           | 532 MHz                           | LPDDR3 -<br>1067MT/s   | 667 MHz                           | 311 MHz           | 0F00h/09h        | 0F31h/09h        |

| SR1M7  | B-2      | Z3770D              | 2.4 GHz                             | 1.5 GHz                            | 500 MHz                           | DDR3L-RS<br>– 1333MT/s | 688 MHz                           | 313 MHz           | 0F00h/09h        | 0F31h/09h        |

| SR1M9  | B-2      | Z3740D              | 1.83 GHz                            | 1.33 GHz                           | 500 MHz                           | DDR3L-RS<br>– 1333MT/s | 688 MHz                           | 313 MHz           | 0F00h/09h        | 0F31h/09h        |

| SR1RU  | В-3      | Z3770               | 2.39 GHz                            | 1.46 GHz                           | 532 MHz                           | LPDDR3 –<br>1067 MT/s  | 667 MHz                           | 311 MHz           | 0F00h/0Bh        | 0F31h/0Bh        |

| SR1RW  | В-3      | Z3740               | 1.86 GHz                            | 1.33 GHz                           | 532 MHz                           | LPDDR3 –<br>1067 MT/s  | 667 MHz                           | 311 MHz           | 0F00h/0Bh        | 0F31h/0Bh        |

| SR1S2  | В-3      | Z3680               | 2.0 GHz                             | 1.33 GHz                           | 532 MHz                           | LPDDR3 –<br>1067 MT/s  | 667 MHz                           | 311 MHz           | 0F00h/0Bh        | 0F31h/0Bh        |

| SR1RY  | B-3      | Z3770D              | 2.4 GHz                             | 1.5 GHz                            | 500 MHz                           | DDR3L-RS<br>– 1333MT/s | 688 MHz                           | 313 MHz           | 0F00h/0Bh        | 0F31h/0Bh        |

| SR1S0  | B-3      | Z3740D              | 1.83 GHz                            | 1.33 GHz                           | 500 MHz                           | DDR3L-RS<br>– 1333MT/s | 688 MHz                           | 313 MHz           | 0F00h/0Bh        | 0F31h/0Bh        |

| SR1S4  | В-3      | Z3680D              | 2.0 GHz                             | 1.33 GHz                           | 500 MHz                           | DDR3L-RS<br>– 1333MT/s | 688 MHz                           | 313 MHz           | 0F00h/0Bh        | 0F31h/0Bh        |

| SR1SP  | C-0      | Z3745               | 1.86 GHz                            | 1.33 GHz                           | 532 MHz                           | LPDDR3 -<br>1067MT/s   | 778 MHz                           | 311 MHz           | 0F00h/0Dh        | 0F31h/0Dh        |

| SR1ST  | C-0      | Z3745D              | 1.83Ghz                             | 1.33 GHz                           | 500MHz                            | DDR3L-RS<br>– 1333MT/s | 792 MHz                           | 313 MHz           | 0F00h/0Dh        | 0F31h/0Dh        |

| SR1U7  | C-0      | Z3735D              | 1.83Ghz                             | 1.33 GHz                           | 500MHz                            | DDR3L-RS<br>– 1333MT/s | 646 MHz                           | 313 MHz           | 0F00h/0Dh        | 0F31h/0Dh        |

| SR1U9  | C-0      | Z3735E              | 1.83Ghz                             | 1.33 GHz                           | 500MHz                            | DDR3L-RS<br>– 1333MT/s | 646 MHz                           | 313 MHz           | 0F00h/0Dh        | 0F31h/0Dh        |

| SR1SK  | C-0      | Z3795               | 2.39 GHz                            | 1.66 GHz                           | 532 MHz                           | LPDDR3 -<br>1067MT/s   | 778 MHz                           | 311 MHz           | 0F00h/0Dh        | 0F31h/0Dh        |

| SR1SM  | C-0      | Z3775               | 2.39 GHz                            | 1.46 GHz                           | 532 MHz                           | LPDDR3 -<br>1067MT/s   | 778 MHz                           | 311 MHz           | 0F00h/0Dh        | 0F31h/0Dh        |

| SR1SR  | C-0      | Z3775D              | 2.416 GHz                           | 1.5 GHz                            | 500 MHz                           | DDR3L-RS<br>– 1333MT/s | 792 MHz                           | 313 MHz           | 0F00h/0Dh        | 0F31h/0Dh        |

| SR1UD  | C-0      | Z3735G              | 1.83 GHz                            | 1.33 GHz                           | 500 MHz                           | DDR3L-RS<br>– 1333MT/s | 646 MHz                           | 313 MHz           | 0F00h/0Dh        | 0F31h/0Dh        |

# Table 2. Identification Table for Intel® Atom™ Processor Z3600 and Z3700 Series

| S-Spec | 6        | Processor<br>Number | Core Speed                          |                                    |                                   | <u>,</u>               | Integrated Graphics<br>Core Speed |                   |                  |                  |

|--------|----------|---------------------|-------------------------------------|------------------------------------|-----------------------------------|------------------------|-----------------------------------|-------------------|------------------|------------------|

|        | Stepping |                     | Burst<br>Frequency<br>Mode<br>(BFM) | High<br>Frequency<br>Mode<br>(HFM) | Low<br>Frequency<br>Mode<br>(LFM) | Memory<br>Frequency    | Burst<br>Frequency                | Base<br>Frequency | H-DID/<br>H-RID1 | G-DID/<br>G-RID2 |

| SR1UB  | C-0      | Z3735F              | 1.83 GHz                            | 1.33 GHz                           | 500 MHz                           | DDR3L-RS<br>– 1333MT/s | 646 MHz                           | 313 MHz           | 0F00h/0Dh        | 0F31h/0Dh        |

| SR1V9  | C-0      | Z3785               | 2.416 GHz                           | 1.5 GHz                            | 500 MHz                           | LPDDR3 -<br>1333MT/s   | 833 MHz                           | 313 MHz           | 0F00h/0Dh        | 0F31h/0Dh        |

| SR20D  | C-0      | Z3736F              | 2.16 GHz                            | 1.33 GHz                           | 500 MHz                           | DDR3L-RS<br>– 1333MT/s | 646 MHz                           | 313 MHz           | 0F00h/0Dh        | 0F31h/0Dh        |

| SR20E  | C-0      | Z3736G              | 2.16 GHz                            | 1.33 GHz                           | 500 MHz                           | DDR3L-RS<br>– 1333MT/s | 646 MHz                           | 313 MHz           | 0F00h/0Dh        | 0F31h/0Dh        |

NOTES:

H-DID – Host Device ID; H-RID – Host Revision ID (H-RID are last three Bits of H-DID)

G-DID – Graphics Device ID; G-RID – Graphics Revision ID (G-RID are last three Bits

of G-DID)

# §

# **Component Marking Information**

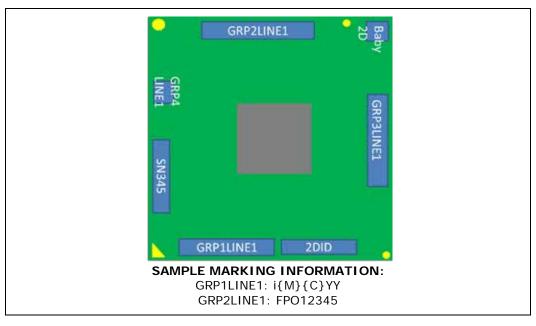

Processor shipments can be identified by the following component markings and example pictures.

Figure 1. Intel® Atom™ Processor Z3600 and Z3700 Component Marking Information

§

# Errata

# VLT1 Accessing Unimplemented ISP MMIO Space May Cause a System Hang

**Problem:** Access to unimplemented ISP (Image Signal Processor) registers should result in a software error. Due to this erratum, the transaction may not complete.

Implication: When this erratum occurs, the system may hang.

Workaround: Do not access unimplemented ISP MMIO space.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

- VLT2 Quad Word Transactions in Violation of Programming Model May Result in System Hang

- **Problem:** Quad word (64 bit data) transactions to access two adjacent 32-bit registers of SoC internal devices may cause system hang.

- **Implication:** Due to this erratum, violations of a device programming model may result in a hang instead of a fatal Target Abort / Completer Abort error. Software written in compliance to correct programming model will not be affected.

- Workaround: Software must be written and compiled in compliance to correct programming model.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

#### VLT3 GPIO Registers Do Not Support 8 or 16 bit Transactions

- **Problem:** Due to this erratum, only aligned DWord accesses to GPIO registers function correctly. This erratum applies to GPIO registers whether in MMIO space or IO space.

- Implication: GPIO register transactions using byte or word accesses or unaligned DWord accesses will not work correctly.

- Workaround: Always use aligned 32 bit transactions when accessing GPIO registers.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

## VLT4 CSI Interface May Not Correct Certain Single bit Errors

- **Problem:** The CSI (Camera Serial Interface) ECC (Error Correcting Code) implementation may not correctly handle single-bit errors in the ECC field and may incorrectly flag as double-bit errors.

- **Implication:** Due to this erratum, some single-bit errors may be treated as double-bit errors. Intel has not observed this erratum with any commercially available software or system.

Workaround: None identified.

**Status:** For the steppings affected, see the Summary Tables of Changes.

## VLT5 ULPI Bus Marginality for USB Device Mode

**Problem:** USB device mode is supported by the SoC via the ULPI (UTMI + Low Pin Interface) bus. The ULPI bus may exhibit read timing marginalities resulting in a hold time violation.

Implication: Due to this erratum, the SoC ULPI reads may be unreliable.

Workaround: None identified.

**Status:** For the steppings affected, see the Summary Tables of Changes.

#### VLT6 Anomalies in USB xHCI PME Enable and PME Status

- **Problem:** The PME\_En (bit 8) and PME\_Status (bit 15) in xHCI's PCI PMCSR (Bus 0, Device 20, Function 0, Offset 0x74) do not comply with the PCI specification.

- **Implication:** If a standard bus driver model for this register is applied, wake issues and system slowness may happen.

- Workaround: Use Intel-provided BIOS ASL code or refer to Intel-provided xHCI driver reference code.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

### VLT7 eMMC Asynchronous Abort May Cause a Hang

- **Problem:** Use of an Asynchronous Abort command to recover from an eMMC transfer error or use of a high priority interrupt STOP\_TRANSMISSION command may result in a hang.

- **Implication:** Using Asynchronous Abort command may cause a hang. Intel has not observed this erratum to impact the operation of any commercially available system.

- **Workaround:** The eMMC driver should use High Priority Interrupt SEND\_STATUS mode per JEDEC STANDARD eMMC, version 4.5. A minimum wait time of 128us between getting an error interrupt and issuing a software reset will avoid this erratum.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

# VLT8 SD Host Controller Incorrectly Reports Supporting of Suspend/ Resume Feature

- **Problem:** SDIO, SD Card, and eMMC Controllers should not indicate the support of optional Suspend/Resume feature documented in the SD Host Controller Standard Specification Version 3.0. Due to this erratum, the default value in the Capabilities Register (offset 040H) incorrectly indicates to the software that this feature is supported.

- **Implication:** If software utilizes the Suspend/Resume feature, data may not be correctly transferred between memory and SD device.

- **Workaround:** A BIOS code change has been identified and may be implemented as a workaround for this erratum.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

#### VLT9 SD Host Controller Error Status Registers May be Incorrectly Set

- **Problem:** This erratum impacts SDIO, SD Card, and eMMC SD Host Controllers. Auto CMD Error Status Register (offset 03CH, Bits [7:1]) may be incorrectly set for software-issued commands (for example: CMD13) that generate errors when issued close to the transmission of an Auto CMD12 command. In addition, the Error Interrupt Status Register Bits (offset 032H) are similarly affected.

- Implication: Software may not be able to interpret SD Host controller error status.

- **Workaround:** Software should follow the same error recovery flow whenever an error status bit is set. Alternatively, don't use software-issued commands which have Auto CMD12 enabled.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

#### VLT10 SD Host Controller Registers Are Not Cleared by Software Reset

**Problem:** This erratum impacts SDIO, SD Card, and eMMC SD Host Controllers. When Software Reset is asserted, registers such as SDMA System Address / Argument 2 (offset 00H) in SD Host Controller are not cleared, failing to comply with the SD Host Controller Specification 3.0.

**Implication:** Intel has not observed this erratum to impact any commercially available software.

Workaround: Driver is expected to reprogram these registers before issuing a new command.

**Status:** For the steppings affected, see the Summary Tables of Changes.

VLT11 Timing Specification Violation on SD Card Interface

- **Problem:** SD Card interface IO circuitry is not optimized for platform conditions during operation at 3.3V.

- Implication: Due to this erratum, there is an increased risk of a transfer error.

Workaround: A BIOS code change has been identified and may be implemented as a workaround for this erratum.

# VLT12 SD Card Controller Does Not Disable Clock during Card Power Down

- **Problem:** The clock and power control of the SD card controller are not linked. Therefore, the SD card controller does not automatically disable the SD card clock when the SD card power is disabled.

- **Implication:** When an SD card is inserted into the system and powered off, the clock to the SD card will continue to be driven. Although this behavior is common, it is a violation of the SD Card Spec 3.0.

- Workaround: To address this problem, the SD card clock should be enabled/disabled in conjunction with SD card power.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

### VLT13 Reset Sequence May Take Longer Than Expected When ACG is Enabled in SD and SDIO Controllers

- **Problem:** When ACG (Auto Clock Gating) is enabled in SD and SDIO controllers, the reset sequence may take longer than expected, possibly resulting in a software timeout.

- **Implication:** Due to this erratum, a longer response time may be observed after a softwareinitiated controller reset.

- **Workaround:** A BIOS code change has been identified and may be implemented as a workaround for this erratum.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

#### VLT14 xHCI Port Assigned Highest SlotID When Resuming from Sx Issue

- **Problem:** If a device is attached while the platform is in S3 or S4 and the device is assigned the highest assignable Slot ID upon resume, the xHCI may attempt to access an unassigned main memory address.

- **Implication:** Accessing unassigned main memory address may cause a system software timeout leading to possible system hang.

- Workaround: System SW can detect the timeout and perform a host controller reset prior to avoid a system hang.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

# VLT15 LFPS Detect Threshold

- **Problem:** The USB 3.0 host and device controllers' LFPS (Low Frequency Periodic Signal) detect threshold is higher than the USB 3.0 specification maximum of 300 mV.

- Implication: The USB 3.0 host and device controllers may not recognize LFPS from SuperSpeed devices transmitting at the minimum low power peak-to-peak differential voltage (400 mV) as defined by USB 3.0 specification for the optional capability for Low-Power swing mode. Intel has not observed this erratum to impact the operation of any commercially available system.

Workaround: None identified.

**Status:** For the steppings affected, see the Summary Tables of Changes.

## VLT16 Set Latency Tolerance Value Command Completion Event Issue

**Problem:** The xHCI controller does not return a value of '0' for slot ID in the command completion event TRB (Transfer Request Block) for a set latency tolerance value command.

*Note:* This violates the command completion event TRB description in section 6.4.2.2 of the eXtensible Host Controller Interface for Universal Serial Bus (xHCI) specification, revision 1.0.

Implication: There are no known functional failures due to this issue.

*Note:* Set latency tolerance value command is specific to the controller and not the slot. Software knows which command was issued and which fields are valid to check for the event.

*Note:* xHCI CV compliance test suite: Test TD4.10: Set Latency Tolerance Value Command Test may issue a warning.

#### Workaround: None identified

**Status:** For the steppings affected, see the Summary Tables of Changes.

#### VLT17 xHCI Data Packet Header and Payload Mismatch Error Condition

**Problem:** If a SuperSpeed device sends a DPH (Data Packet Header) to the xHCI with a data length field that specifies less data than is actually sent in the DPP (Data Packet Payload), the xHCI will accept the packet instead of discarding the packet as invalid.

*Note:* The USB 3.0 specification requires a device to send a DPP matching the amount of data specified by the DPH.

**Implication:** The amount of data specified in the DPH will be accepted by the xHCI and the remaining data will be discarded and may result in anomalous system behavior.

*Note:* This issue has only been observed in a synthetic test environment with a synthetic device.

#### Workaround: None identified

# VLT18 USB xHCI SuperSpeed Packet with Invalid Type Field Issue

**Problem:** If the encoding for the "type" field for a SuperSpeed packet is set to a reserved value and the encoding for the "subtype" field is set to "ACK", the xHCI may accept the packet as a valid acknowledgement transaction packet instead of ignoring the packet.

*Note:* The USB 3.0 specification requires that a device never set any defined fields to reserved values.

**Implication:** System implication is dependent on the misbehaving device and may result in anomalous system behavior.

*Note:* This issue has only been observed in a synthetic test environment with a synthetic device.

#### Workaround: None identified

**Status:** For the steppings affected, see the Summary Tables of Changes.

## VLT19 USB xHCI Behavior with Three Consecutive Failed U3 Entry Attempts

- **Problem:** The xHCI does not transition to the SS.Inactive USB 3.0 LTSSM (Link Training and Status State Machine) state after a SuperSpeed device fails to enter U3 upon three consecutive attempts.

- Note: The USB 3.0 specification requires a SuperSpeed device to enter U3 when directed.

- **Implication:** The xHCI will continue to try to initiate U3. The implication is driver and operating system dependent.

- Workaround: None identified

- **Status:** For the steppings affected, see the Summary Tables of Changes.

#### VLT20 USB xHCI Max Packet Size and Transfer Descriptor Length Mismatch

- **Problem:** The xHCI may incorrectly handle a request from a low-speed or full-speed device when all the following conditions are true:

- The sum of the packet fragments equals the length specified by the TD (Transfer Descriptor)

- · The TD length is less than the MPS (Max Packet Size) for the device

- The last packet received in the transfer is "0" or babble bytes

- **Implication:** The xHCI will halt the endpoint if all the above conditions are met. All functions associated with the endpoint will stop functioning until the device is unplugged and reinserted.

Workaround: None identified

# VLT21 USB EHCI RMH Port Disabled Due to Device Initiated Remote Wake

**Problem:** During resume from Global Suspend, the RMH controller may not send SOF soon enough to prevent a device from entering suspend again. A collision on the port may occur if a device initiated remote wake occurs before the RMH controller sends SOF.

*Note:* Intel has only observed this issue when two USB devices on the same RMH controller send remote wake within 30 ms window while RMH controller is resuming from Global Suspend

Implication: The RMH host controller may detect the collision as babble and disable the port.

- Workaround: Intel recommends system software to check bit 3 (Port Enable/Disable Change) together with bit 7 (Suspend) of Port N Status and Control PORTC registers when determining which port(s) have initiated remote wake. Intel recommends the use of the USB xHCI controller which is not affected by this erratum.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

#### VLT22 USB EHCI Isoch in Transfer Error Issue

- **Problem:** If a USB full-speed inbound isochronous transaction with a packet length 190 bytes or greater is started near the end of a microframe the SoC may see more than 189 bytes in the next microframe.

- **Implication:** If the SoC sees more than 189 bytes for a microframe an error will be sent to software and the isochronous transfer will be lost. If a single data packet is lost no perceptible impact for the end user is expected.

*Note:* Intel has only observed the issue in a synthetic test environment where precise control of packet scheduling is available, and has not observed this failure in its compatibility validation testing.

- Isochronous traffic is periodic and cannot be retried thus it is considered good practice for software to schedule isochronous transactions to start at the beginning of a microframe. Known software solutions follow this practice.

- To sensitize the system to the issue additional traffic such as other isochronous transactions or retries of asynchronous transactions would be required to push the inbound isochronous transaction to the end of the microframe.

- Workaround: Intel recommends the use of the USB xHCI controller which is not affected by this erratum.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

#### VLT23 USB EHCI Babble Detected with SW Overscheduling

- **Problem:** If software violates USB periodic scheduling rules for full-speed isochronous traffic by overscheduling, the RMH may not handle the error condition properly and return a completion split with more data than the length expected.

- **Implication:** If the RMH returns more data than expected, the endpoint will detect packet babble for that transaction and the packet will be dropped. Since overscheduling occurred to create the error condition, the packet would be dropped regardless of RMH behavior.

If a single isochronous data packet is lost, no perceptible impact to the end user is expected.

*Note:* USB software overscheduling occurs when the amount of data scheduled for a microframe exceeds the maximum budget. This is an error condition that violates the USB periodic scheduling rule.

*Note:* This failure has only been recreated synthetically with USB software intentionally overscheduling traffic to hit the error condition.

Workaround: Intel recommends the use of the USB xHCI controller which is not affected by this erratum.

**Status:** For the steppings affected, see the Summary Tables of Changes.

#### VLT24 USB EHCI Full-/low-speed EOP Issue

- **Problem:** If the EOP of the last packet in a USB Isochronous split transaction (Transaction >189 bytes) is dropped or delayed 3 ms or longer the following may occur:

- If there are no other pending low-speed or full-speed transactions the RMH will not send SOF, or Keep-Alive. Devices connected to the RMH will interpret this condition as idle and will enter suspend.

- If there is other pending low-speed or full-speed transactions, the RMH will drop the isochronous transaction and resume normal operation.

- **Implication:** If there are no other transactions pending, the RMH is unaware a device has entered suspend and may start sending a transaction without waking the device. The implication is device dependent, but a device may stall and require a reset to resume functionality. If there are other transactions present, only the initial isochronous transaction may be lost. The loss of a single isochronous transaction may not result in end user perceptible impact.

*Note:* Intel has only observed this failure when using software that does not comply with the USB specification and violates the hardware isochronous scheduling threshold by terminating transactions that are already in progress

Workaround: Intel recommends the use of the USB xHCI controller which is not affected by this erratum.

**Status:** For the steppings affected, see the Summary Tables of Changes.

- VLT25 USB EHCI Asynchronous Retries Prioritized Over Periodic Transfers

- **Problem:** The integrated USB RMH incorrectly prioritizes full-speed and low-speed asynchronous retries over dispatchable periodic transfers.

- **Implication:** Periodic transfers may be delayed or aborted. If the asynchronous retry latency causes the periodic transfer to be aborted, the impact varies depending on the nature of periodic transfer:

- If a periodic interrupt transfer is aborted, the data may be recovered by the next instance of the interrupt or the data could be dropped.

- If a periodic isochronous transfer is aborted, the data will be dropped. A single dropped periodic transaction should not be noticeable by end user.

*Note:* This issue has only been seen in a synthetic environment. The USB spec does not consider the occasional loss of periodic traffic a violation

- Workaround: Intel recommends the use of the USB xHCI controller which is not affected by this erratum.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

#### VLT26 USB EHCI FS/LS Incorrect Number of Retries

- **Problem:** A USB low-speed transaction may be retried more than three times, and a USB fullspeed transaction may be retried less than three times if all of the following conditions are met:

- A USB low-speed transaction with errors or the first retry of the transaction occurs near the end of a microframe, and there is not enough time to complete another retry of the low-speed transaction in the same microframe.

- There is pending USB full-speed traffic and there is enough time left in the microframe to complete one or more attempts of the full-speed transaction.

- Both the low-speed and full-speed transactions must be asynchronous (Bulk/Control) and must have the same direction either in or out.

*Note:* Per the USB EHCI Specification a transaction with errors should be attempted a maximum of 3 times if it continues to fail.

- Implication: For low-speed transactions the extra retry(s) allow a transaction additional chance(s) to recover regardless of if the full-speed transaction has errors or not. If the full-speed transactions also have errors, the SoC may retry the transaction fewer times than required, stalling the device prematurely. Once stalled, the implication is software dependent, but the device may be reset by software.

- Workaround: Intel recommends the use of the USB xHCI controller which is not affected by this erratum.

27

## VLT27 USB EHCI RMH Think Time Issue

- **Problem:** The USB RMH Think Time may exceed its declared value in the RMH hub descriptor register of 8 full-speed bit times.

- **Implication:** If the USB driver fully subscribes a USB microframe, LS/FS transactions may exceed the microframe boundary.

- Note: No functional failures have been observed.

- Workaround: Intel recommends the use of the USB xHCI controller which is not affected by this erratum.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

#### VLT28 USB EHCI Full-/low-speed Device Removal Issue

- **Problem:** If two or more USB full-/low-speed devices are connected to the EHCI USB controller, the devices are not suspended, and one device is removed, one or more of the devices remaining in the system may be affected by the disconnect.

- **Implication:** The implication is device dependent. A device may experience a delayed transaction, stall and be recovered via software, or stall and require a reset such as a hot plug to resume normal functionality.

- Workaround: Intel recommends the use of the USB xHCI controller which is not affected by this erratum.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

## VLT29 Reported Memory Type May Not Be Used to Access the VMCS and Referenced Data Structures

- **Problem:** Bits 53:50 of the IA32\_VMX\_BASIC MSR report the memory type that the processor uses to access the VMCS and data structures referenced by pointers in the VMCS. Due to this erratum, a VMX access to the VMCS or referenced data structures will instead use the memory type that the MTRRs (memory-type range registers) specify for the physical address of the access.

- Implication: Bits 53:50 of the IA32\_VMX\_BASIC MSR report that the WB (write-back) memory type will be used but the processor may use a different memory type.

- **Workaround:** Software should ensure that the VMCS and referenced data structures are located at physical addresses that are mapped to WB memory type by the MTRRs.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

# VLT30 A Page Fault May Not be Generated When the PS bit is set to "1" in a PML4E or PDPTE

- Problem: On processors supporting Intel® 64 architecture the PS bit (Page Size bit 7) is reserved in PML4Es and PDPTEs. If the translation of the linear address of a memory access encounters a PML4E or a PDPTE with PS set to 1 a page fault should occur. Due to this erratum, PS of such an entry is ignored and no page fault will occur due to its being set.

- **Implication:** Software may not operate properly if it relies on the processor to deliver page faults when reserved Bits are set in paging-structure entries.

- Workaround: Software should not set bit 7 in any PML4E or PDPTE that has Present bit (bit 0) set to "1".

- **Status:** For the steppings affected, see the Summary Tables of Changes.

## VLT31 CS Limit Violations May Not be detected after VM Entry

- **Problem:** The processor may fail to detect a CS limit violation on fetching the first instruction after VM entry if the first byte of that instruction is outside the CS limit but the last byte of the instruction is inside the limit.

- **Implication:** The processor may erroneously execute an instruction that should have caused a general protection exception.

- **Workaround:** When a VMM emulates a branch instruction it should inject a general protection exception if the instruction's target EIP is beyond the CS limit.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

- VLT32 IA32\_DEBUGCTL.FREEZE\_PERFMON\_ON\_PMI is Incorrectly Cleared by SMI

- **Problem:** FREEZE\_PERFMON\_ON\_PMI (bit 12) in the IA32\_DEBUGCTL MSR (1D9H) is erroneously cleared during delivery of an SMI (system-management interrupt).

- **Implication:** As a result of this erratum the performance monitoring counters will continue to count after a PMI occurs in SMM (system-management Mode).

Workaround: None identified.

# VLT33 PEBS Record Eventing IP Field May be Incorrect after CS.Base Change

- **Problem:** Due to this erratum a PEBS (Precise Event Base Sampling) record generated after an operation which changes CS.Base may contain an incorrect address in the EventingIP field.

- **Implication:** Software attempting to identify the instruction which caused the PEBS event may identify the incorrect instruction when non-zero CS.Base is supported and CS.Base is changed. Intel has not observed this erratum to impact the operation of any commercially available system.

Workaround: None identified.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

- VLT34 Some Performance Counter Overflows May Not be logged in IA32\_PERF\_GLOBAL\_STATUS When FREEZE\_PERFMON\_ON\_PMI is enabled

- Problem: When enabled, FREEZE\_PERFMON\_ON\_PMI bit 12 in IA32\_DEBUGCTL MSR (1D9H) freezes PMCs (performance monitoring counters) on a PMI (Performance Monitoring Interrupt) request by clearing the IA32\_PERF\_GLOBAL\_CTRL MSR (38FH). Due to this erratum, when FREEZE\_PERFMON\_ON\_PMI is enabled and two or more PMCs overflow within a small window of time and PMI is requested, then subsequent PMC overflows may not be logged in IA32\_PERF\_GLOBAL\_STATUS MSR (38EH).

- Implication: On a PMI, subsequent PMC overflows may not be logged in IA32\_PERF\_GLOBAL\_STATUS MSR.

- Workaround: Re-enabling the PMCs in IA32\_PERF\_GLOBAL\_CTRL will log the overflows that were not previously logged in IA32\_PERF\_GLOBAL\_STATUS.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

- VLT35 MOVNTDQA from WC Memory May Pass Earlier Locked Instructions

- **Problem:** An execution of MOVNTDQA that loads from WC (write combining) memory may appear to pass an earlier locked instruction to a different cache line.

- **Implication:** Software that expects a lock to fence subsequent MOVNTDQA instructions may not operate properly. If the software does not rely on locked instructions to fence the subsequent execution of MOVNTDQA then this erratum does not apply.

- Workaround: Software that requires a locked instruction to fence subsequent executions of MOVNTDQA should insert an LFENCE instruction before the first execution of MOVNTDQA following the locked instruction. If there is already fencing or serializing instruction between the locked instruction and the MOVNTDQA, then an additional LFENCE is not necessary.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

# VLT36 Unsynchronized Cross-Modifying Code Operations Can Cause Unexpected Instruction Execution Results

- **Problem:** The act of one processor or system bus master writing data into a currently executing code segment of a second processor with the intent of having the second processor execute that data as code is called cross-modifying code (XMC). XMC that does not force the second processor to execute a synchronizing instruction prior to execution of the new code is called unsynchronized XMC. Software using unsynchronized XMC to modify the instruction byte stream of a processor can see unexpected or unpredictable execution behavior from the processor that is executing the modified code.

- Implication: In this case the phrase "unexpected or unpredictable execution behavior" encompasses the generation of most of the exceptions listed in the Intel Architecture Software Developer's Manual Volume 3: System Programming Guide including a General Protection Fault (GPF) or other unexpected behaviors. In the event that unpredictable execution causes a GPF the application executing the unsynchronized XMC operation would be terminated by the operating system.

- **Workaround:** In order to avoid this erratum programmers should use the XMC synchronization algorithm as detailed in the Intel Architecture Software Developer's Manual Volume 3: System Programming Guide Section: Handling Self- and Cross-Modifying Code.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

- VLT37 SDIO Host Controller Does Not Control the SDIO Bus Power

- **Problem:** The SD Bus Power bit in Power Control Register (Bus 0; Device 17; Function 0; Offset 029H) is not connected to any SOC IO pin that can reset the SDIO bus power. Due to this erratum, SDIO device Power-On-Reset cannot be controlled by Power Control Register. SDIO Controller may fail to comply with SD Host Controller Specification Version 3.00.

- Implication: SDIO devices may not be powered up and initialized correctly.

- Workaround: Software should be configured to use a GPIO pin on the platform to enable or disable the SDIO bus power. Please refer to Bay Trail-T SoC External Design Specification (EDS) document.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

- VLT38 USB HSIC Ports Incorrectly Reported as Removable

- **Problem:** The DR (Device Removable) bit in the PORTSC registers of the two USB HSIC ports incorrectly indicates that devices on these ports may be removed.

- **Implication:** Software that relies solely on the state of DR bits will consider fixed devices to be removable. This may lead the software to improper actions (e.g. requesting the user remove a fixed device).

- **Workaround:** In conjunction with the DR bits, software should use BIOS-configured ACPI tables and factor in the CONNECTABLE field of the USB Port Capabilities object when determining whether a port is removable.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

## VLT39 Multiple Threads That Access the ISP Concurrently May Lead to a System Hang

- **Problem:** The ISP (Image Signal Processor) may not be able to process concurrent accesses.

- **Implication:** If multiple software threads access the ISP concurrently, it may lead to system hang during video recording, still image capture or preview modes.

- Workaround: Avoid using multiple threads that may concurrently access the ISP. The Intel-provided drivers implement this workaround.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

- VLT40 Premature Asynchronous Interrupt Enabling May Lead to Loss of SDIO Wi-Fi Functionality

- **Problem:** Setting the SDIO controller's Host Control 2 Register Asynchronous Interrupt Enable (Bus 0; Device 17; Function 0; Offset 03EH, bit 14) to '1' before the signal voltage switch sequence completion may result in SDIO card initialization failure.

- Implication: SDIO card initialization failure may lead to software time out and loss of Wi-Fi device functionality. Currently released common operating system drivers do not use Asynchronous Interrupt mode.

- Workaround: The SDIO driver should either use SDIO Synchronous Interrupt Mode or enable SDIO Asynchronous Interrupt Mode after the SDIO card signal voltage switch sequence completes.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

## VLT41 Paging Structure Entry May be Used Before Accessed And Dirty Flags Are Updated

- **Problem:** If software modifies a paging structure entry while the processor is using the entry for linear address translation, the processor may erroneously use the old value of the entry to form a translation in a TLB (or an entry in a paging structure cache) and then update the entry's new value to set the accessed flag or dirty flag. This will occur only if both the old and new values of the entry result in valid translations.

- **Implication:** Incorrect behavior may occur with algorithms that atomically check that the accessed flag or the dirty flag of a paging structure entry is clear and modify other parts of that paging structure entry in a manner that results in a different valid translation.

- **Workaround:** Affected algorithms must ensure that appropriate TLB invalidation is done before assuming that future accesses do not use translations based on the old value of the paging structure entry.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

# VLT42 Certain eMMC Host Controller Registers Are Not Cleared by Software Reset

- **Problem:** Due to this erratum, when an eMMC Host Controller software reset is requested by setting bit 0 of the Software Reset Register (Offset 2FH), the Command Response Register (Offset 10H) and ADMA Error Status Register (Offset 54H) are not cleared. This does not comply with the SD Host Controller Specification 3.0.

- Implication: Intel has not observed this erratum to impact any commercially available software.

- Workaround: Software should not read these registers until a response is received from the eMMC device.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

#### VLT43 The Display May Flicker After an MIPI-DSI LP to HS Transition

- **Problem:** Due to this erratum, when the MIPI (Mobile Industry Processor Interface) display PHY switches from LP (low power) mode to HS (high speed) mode, there is a brief interval (50 ns) where the four MIPI DSI (Display Serial Interface) data lanes may not be synchronized.

- Implication: The effects are MIPI Panel dependent. Intel has observed display flicker on some MIPI Panels.

- Workaround: Workaround for this erratum is panel dependent and can be implemented in firmware or software.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

- VLT44 LPDDR3 Power-Up Timing

- **Problem:** JEDEC Standard JESD209-3 requires a minimum additional time (denoted by tMRRI) after an "exit from standby, idle power-down mode" before any MRR (Mode Register Read) command can be issued. Due to this erratum, the SoC may not comply with the tMRRI specification.

- **Implication:** Intel has not observed this erratum to impact the functionality or performance of any commercially available LPDDR3 memory parts operating at speeds up to 1067MT/s.

Workaround: None identified.

### VLT45 Using MIPI DSI in LP Mode May Result in Unpredictable Display Behavior

- **Problem:** DSI (Display Serial Interface) commands sent in LP (low power) mode to the MIPI (Mobile Industry Processor Interface) DSI controller may fail to execute if the controller is configured to be clocked by the DSI PLL.

- Implication: When this erratum occurs, the display panel will behave unpredictably.

- Workaround: The display driver can avoid the conditions necessary for this erratum by either using HS (High Speed) mode for sending all DSI commands or selecting PLL Bypass Mode for all LP mode operations and DSI PLL for HS mode. The Intel display drivers implement this workaround.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

### VLT46 USB Device Mode Controller May Not Successfully Switch to High Speed Data Rate

- **Problem:** The USB Device Mode Controller may initiate speed change to High Speed data rate immediately following a reset of a discrete ULPI (UTMI+ Low Pin Interface) compliant PHY (physical layer) device.

- **Implication:** Some ULPI-compliant PHYs may not recognize the USB Device Mode Controller speed change and thus may not be able to support USB High Speed operation.

Workaround: None identified.

**Status:** For the steppings affected, see the Summary Tables of Changes.

## VLT47 USB Device Mode Controller Response Time May Exceed The Specification

- **Problem:** The USB ULPI specification allocates 112 bit times for the USB Device Mode controller to respond to requests. Due to this erratum, the SoC's Device Mode controller may exceed this specification.

- **Implication:** USB response time may exceed specifications in configurations with maximal total USB cable length, resulting in communication failure.

- **Workaround:**Limit the total cable length used to connect to the host to less than 24m to compensate for the additional controller response time.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

## VLT48 USB Device Mode Controller May Not Enter the SS.Inactive State

- **Problem:** When operating at SuperSpeed rates, the PENDING\_HP\_TIMER is used to detect lost or corrupted acknowledgements. The USB3.0 specification requires a USB port to transition to the SS.Inactive state on the fourth consecutive timeout. Due to this erratum, the USB device mode controller in device mode will continue to enter Recovery state and not enter the SS.Inactive state.

- **Implication:** This behavior does not comply with the USB3.0 specification. Intel has not observed this erratum to impact the operation of any commercially available system.

Workaround: None identified.

**Status:** For the steppings affected, see the Summary Tables of Changes.

#### VLT49 USB EHCI Full-/Low-speed Port Reset or Clear TT Buffer Request

- **Problem:** One or more full-/low-speed USB devices on the same RMH controller may be affected if the devices are not suspended and either (a) software issues a Port Reset OR (b) software issues a Clear TT Buffer request to a port executing a split full-/low-speed Asynchronous Out command. The small window of exposure for full-speed device is around 1.5 microseconds and around 12 microseconds for a low-speed device.

- **Implication:** The affected port may stall or receive stale data for a newly arrived split transfer occurring at the time of the Port Reset or Clear TT Buffer request.

*Note*: This issue has only been observed in a synthetic test environment.

- Workaround: Intel recommends the use of the USB xHCI controller which is not affected by this erratum.

- **Status:** For the steppings affected, see the Summary Tables of Changes.

- VLT50 USB Device Mode Controller LFPS Transmission Period Does Not Meet USB3.0 Specification