# Parallel Input 8-channel Sink Driver with Flip-Flops

# **■FEATURES**

- •8-channel Parallel Input Parallel Output

- •Built-in Flip-Flops for latching Input data

- Supply Voltage

- V<sub>DD</sub>=4.0 to 5.5V

- Output Voltage

- V<sub>DS</sub>=up to 40V (45V Rating)

- Output Current

- 300mA(DC) / ch.

- 600mA(Peak) / ch. •Built-in Noise Filter (CLRb Pin)

- OCP, TSD Protection Circuit

- •Output Slew Rate Control

- Topr=-40 to 125°C •Operating Temperature

- Package Outline

- SDIP22

#### ■GENERAL DESCRIPTION

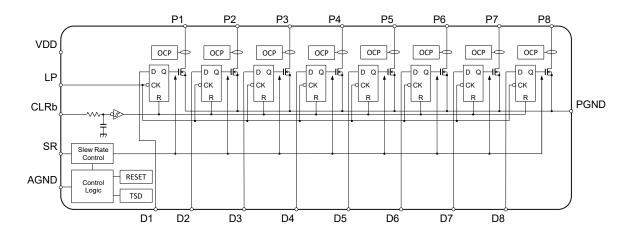

The NJW4828-A is 8-channel sink driver with 600mA output.

The input circuits have built-in flip-flops, and they can latch the input data signals by using the LP signal as trigger.

The CLRb input has built-in filter for noise immunity. Supply voltage and input voltage correspond to 5V logic, maximum rating of output voltage is 45V.

The protection circuits have over current protection (OCP) and thermal shutdown (TSD).

Moreover, because it has built-in output slew rate adjustment function, it can be applied as EMI countermeasure.

#### ■APPLICATION

LED applications Relay and solenoid applications for industrial equipment

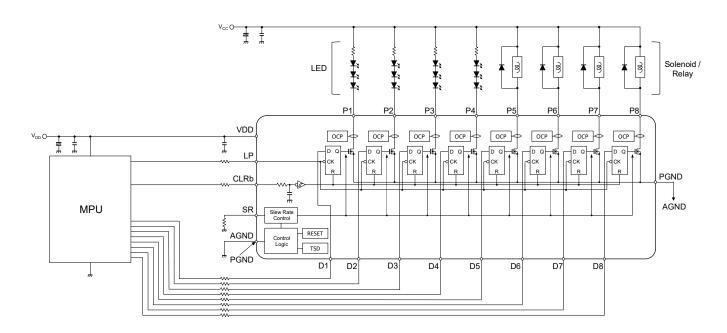

#### **TYPICAL APPLICATION**

New Japan Radio Co., Ltd.

## BLOCK DIAGRAM

## ■PIN CONFIGURATION

| LP 1    | 22 VDD       |

|---------|--------------|

| D1 2    | <u>21</u> P1 |

| D2 3    | 20 P2        |

| D3 4    | <u>19</u> P3 |

| D4 5    | 18 P4        |

| D5 6    | 17 P5        |

| D6 7    | 16 P6        |

| D7 8    | 15 P7        |

| D8 9    | 14 P8        |

| CLRb 10 | 13 PGND      |

| SR 11   | 12 AGND      |

| PIN NO. | SYMBOL | I/O | DESCRIPTION                  |

|---------|--------|-----|------------------------------|

| 1       | LP     | Ι   | Latch Signal Input Pin       |

| 2       | D1     | I   |                              |

| 3       | D2     | I   |                              |

| 4       | D3     | I   |                              |

| 5       | D4     | 1   | Parallel Data Input Pin      |

| 6       | D5     | I   | r arallet Data Iriput r iri  |

| 7       | D6     | I   |                              |

| 8       | D7     | I   |                              |

| 9       | D8     | I   |                              |

| 10      | CLRb   | 1   | Clear Signal Input Pin       |

| 11      | SR     | -   | Output Slew Rate Setting Pin |

| 12      | AGND   | -   | Control Block Ground Pin     |

| 13      | PGND   | -   | Output Block Ground Pin      |

| 14      | P8     | 0   |                              |

| 15      | P7     | 0   |                              |

| 16      | P6     | 0   |                              |

| 17      | P5     | 0   | Parallel Output Pin          |

| 18      | P4     | 0   |                              |

| 19      | P3     | 0   |                              |

| 20      | P2     | 0   |                              |

| 21      | P1     | 0   |                              |

| 22      | VDD    | -   | Power Supply Pin             |

New Japan Radio Co., Ltd.

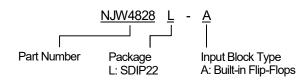

# ■PRODUCT NAME INFORMATION

#### **■ORDERING INFORMATION**

| PRODUCT NAME | PACKAGE<br>OUTLINE | RoHS | HALOGEN-<br>FREE | TERMINAL<br>FINISH | MARKING   | WEIGHT<br>(mg) | MOQ(pcs) |

|--------------|--------------------|------|------------------|--------------------|-----------|----------------|----------|

| NJW4828L-A   | SDIP22             | yes  | -                | Sn2Bi              | NJW4828LA | 1080           | 1000     |

#### ■ABSOLUTE MAXIMUM RATINGS

| PARAMETER                   | SYMBOL          | RATINGS            | UNIT | NOTE                   |

|-----------------------------|-----------------|--------------------|------|------------------------|

| Supply Voltage              | V <sub>DD</sub> | -0.3 to +7         | V    | VDD Pin                |

| Output Pin Voltage          | V <sub>DS</sub> | -0.3 to +45        | V    | P1 to P8 Pin           |

| Input Pin Voltage           | V <sub>IN</sub> | -0.3 to $V_{DD}$   | V    | D1 to D8, LP, CLRb Pin |

| Output Current              | I <sub>DS</sub> | 600                | mA   | P1 to P8 Pin           |

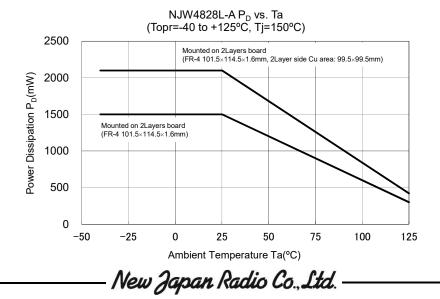

| Power Dissipation (Ta=25°C) | р               | 1.5 <sup>(1)</sup> | W    |                        |

| SDIP22                      | P <sub>D</sub>  | 2.1 <sup>(2)</sup> | vv   |                        |

| Junction Temperature Range  | Tj              | -40 to +150        | °C   |                        |

| Operating Temperature Range | Topr            | -40 to +125        | °C   |                        |

| Storage Temperature Range   | Tstg            | -50 to +150        | °C   |                        |

(1): Mounted on glass epoxy board. (101.5×114.5×1.6mm: based on EIA/JEDEC standard, 2Layers FR-4)

(2): Mounted on glass epoxy board. (101.5×114.5×1.6mm: NJRC original board, 2Layers FR-4, 2Layer side Cu area 99.5×99.5mm)

#### ■RECOMMENDED OPERATING CONDITIONS

| PARAMETER                     | SYMBOL          | RATINGS    | UNIT |

|-------------------------------|-----------------|------------|------|

| Supply Voltage                | V <sub>DD</sub> | 4.0 to 5.5 | V    |

| Output Pin Voltage            | V <sub>DS</sub> | 0 to 40    | V    |

| Output Current <sup>(3)</sup> | I <sub>DS</sub> | 0 to 300   | mA   |

(3): Caution that the total power consumption of P1 to P8 does not exceed the power dissipation of rating.

*New Japan Radio Co., Ltd.* www.njr.com/

| ELECTRICAL CHARACTERIST                   | rameter) (Unless otherwise | e noted, $V_D$                                                          | <sub>d</sub> =5V, R <sub>SF</sub> | <sub>R</sub> =500kΩ, | Ta=25°C)           |      |

|-------------------------------------------|----------------------------|-------------------------------------------------------------------------|-----------------------------------|----------------------|--------------------|------|

| PARAMETER                                 | SYMBOL                     | TEST CONDITION                                                          | MIN.                              | TYP.                 | MAX.               | UNIT |

| Quiescent Current 1                       | I <sub>Q1</sub>            | All outputs OFF                                                         | -                                 | 1.4                  | 2.8                | mA   |

| Quiescent Current 2                       | I <sub>Q2</sub>            | All outputs ON                                                          | -                                 | 1.6                  | 3.2                | mA   |

| H level Input Voltage                     | V <sub>IH</sub>            | LP, CLRb, D1 to D8 Pin                                                  | $0.7V_{DD}$                       | -                    | $V_{DD}$           | V    |

| L level Input Voltage                     | VIL                        | LP, CLRb, D1 to D8 Pin                                                  | 0                                 | -                    | $0.3V_{\text{DD}}$ | V    |

| H level Input Current                     | IIH                        | V <sub>DD</sub> =5.5V, V <sub>IN</sub> =5.5V,<br>LP, CLRb, D1 to D8 Pin | -                                 | -                    | 1                  | μA   |

| L level Input Current                     | IL                         | V <sub>DD</sub> =5.5V, V <sub>IN</sub> =0V,<br>LP, CLRb, D1 to D8 Pin   | -                                 | -                    | 1                  | μA   |

| Output ON Resistance                      | R <sub>ON_P</sub>          | $V_{SR}$ =0V, $I_{DS}$ =100mA, P1 to P8 Pin                             | -                                 | 0.9                  | 2.7                | Ω    |

| Maximum Output Current                    | I <sub>DMAX_P</sub>        | V <sub>SR</sub> =0V, P1 to P8 Pin                                       | 600                               | -                    | -                  | mA   |

| Output Leak Current                       | $I_{LEAK_P}$               | V <sub>DS</sub> =40V, P1 to P8 Pin                                      | -                                 | -                    | 1                  | μA   |

| Thermal Shutdown Operating<br>Temperature | $T_{TSD\_DET}$             |                                                                         | -                                 | 170                  | -                  | °C   |

| Thermal Shutdown Recovery<br>Temperature  | T <sub>TSD_REV</sub>       |                                                                         | -                                 | 150                  | -                  | °C   |

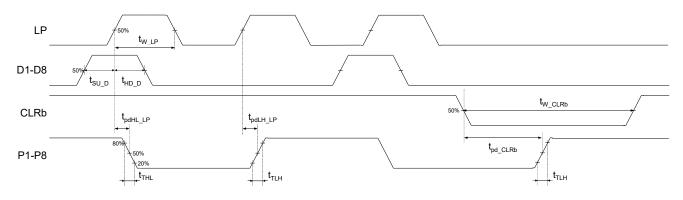

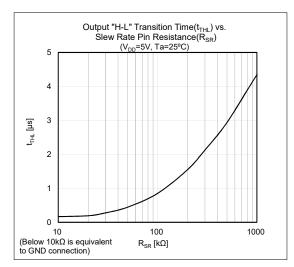

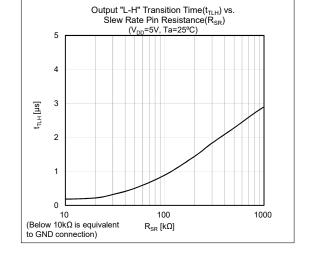

# ■ELECTRICAL CHARACTERISTICS (Switching Parameter)

| (L                           | (Unless otherwise noted, $V_{DD}$ =5V, $V_{CC}$ =24V, CL=30pF(P-PGND), R <sub>L</sub> =240 $\Omega$ (P-V <sub>CC</sub> ), Ta=25°C |                                          |      |      |      |      |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------|------|------|------|--|

| PARAMETER                    | SYMBOL                                                                                                                            | TEST CONDITION                           | MIN. | TYP. | MAX. | UNIT |  |

| Output "H-L" Transition Time | t <sub>THL</sub>                                                                                                                  | R <sub>sR</sub> =500kΩ                   | -    | 2.5  | -    | μs   |  |

| Output "L-H" Transition Time | t <sub>TLH</sub>                                                                                                                  | R <sub>sR</sub> =500kΩ                   | -    | 1.8  | -    | μs   |  |

| Output "H-L" Propagation     | +                                                                                                                                 | t <sub>pdHL_LP</sub> V <sub>SR</sub> =0V | -    | 0.2  | -    | μs   |  |

| Delay Time (LP-P)            | <sup>L</sup> pdHL_LP                                                                                                              |                                          |      |      |      |      |  |

| Output "L-H" Propagation     | +                                                                                                                                 | <sub>pdLH_LP</sub> V <sub>SR</sub> =0V   | -    | 0.9  | -    | μs   |  |

| Delay Time (LP-P)            | <sup>L</sup> pdLH_LP                                                                                                              |                                          |      |      |      |      |  |

| D Setup Time for LP          | t <sub>SU_D</sub>                                                                                                                 |                                          | 30   | -    | -    | ns   |  |

| D Hold Time for LP           | t <sub>HD_D</sub>                                                                                                                 |                                          | 15   | -    | -    | ns   |  |

| LP "H" Pulse Width           | t <sub>w_LP</sub>                                                                                                                 |                                          | 90   | -    | -    | ns   |  |

| CLRb "L" Pulse Width         | t <sub>w_CLRb</sub>                                                                                                               |                                          | 5    | -    | -    | μs   |  |

# ■THERMAL CHARACTERISTICS

| PARAMETER                  | SYMBOL | VALUE             | UNIT |

|----------------------------|--------|-------------------|------|

| Junction to ambient        | 0ie    | 83 <sup>(4)</sup> | °CW  |

| thermal resistance         | θja    | 59 <sup>(5)</sup> | C/VV |

| Junction to top of package |        | 23 <sup>(4)</sup> | °CW  |

| characterization parameter | ψjt    | 22 <sup>(5)</sup> | C/VV |

(4): Mounted on glass epoxy board. (101.5×114.5×1.6mm: based on EIA/JEDEC standard, 2Layers FR-4)

(5): Mounted on glass epoxy board. (101.5×114.5×1.6mm: NJRC original board, 2Layers FR-4, 2Layer side Cu area 99.5×99.5mm)

New Japan Radio Co., Ltd. – www.njr.com/

# ■APPLICATION NOTE / GLOSSARY

#### Truth Table

|        | INPUT P OUTPUT |             | P OUTPUT                | OPERATION                                                  |

|--------|----------------|-------------|-------------------------|------------------------------------------------------------|

| CLRb   | LP             | D           | (with pull-up resistor) | OFENATION                                                  |

| L      | Х              | Х           | All OFF (H)             | Reset all data of the input circuit and protection circuit |

|        | 1              | L           | OFF (H)                 | Set "L" to the input latch circuit                         |

| Н      | 1              | Н           | ON (L)                  | Set "H" to the input latch circuit                         |

| ↓ X    |                | Х           | P0                      | Input data can't be imported                               |

| ↑ · Ch | nange fro      | m "I " to " | H"H · High Level        | X · Don't Care                                             |

H : High L : Change from L to H : Change from "H" to "L" L : Low Level

P0: The P output level just before input condition in the above table

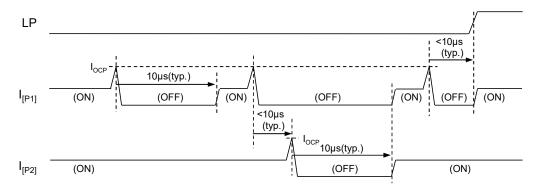

#### •Timing Chart / Timing Definition

•Over Current Protection Circuit (OCP)

Overcurrent detection operates for each P1 - P8 output.

When overcurrent is detected, the corresponding P output is turned OFF.

After overcurrent is detected, when data is reset or passage of internal recovery time(10µs typ.), it returns to normal operation. In the condition of the P output is already overcurrent detected and turned off, if another P output is detected continuously, all the recovery timing of the corresponding P outputs will be all taken over.

# Thermal Shutdown Circuit (TSD)

When the junction temperature inside the IC exceeds  $T_{TSD_{DET}}$ , all P outputs are turned OFF. When the internal junction temperature drops to T<sub>TSD REV</sub> or less, it returns to normal operation state. Input signals other than CLRb are not accepted while the thermal shutdown circuit is operating.

*New Japan Radio Co., Ltd.* www.njr.com/

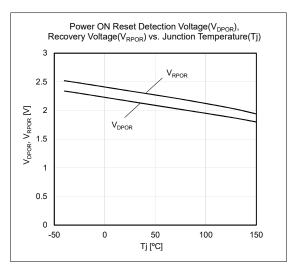

• Power ON Reset Function

The power supply pin has built-in power on reset function. When the  $V_{DD}$  voltage below  $V_{DPOR}$  (typ.), all outputs are turned off and all internal states are initialized.

When the V<sub>DD</sub> voltage exceeds V<sub>RPOR</sub> (typ.), it operates normally, but the V<sub>DD</sub> voltage should be used within the recommended operating voltage range (V<sub>DD</sub>=4.0V to 5.5V)

•Output Slew Rate Setting Function (SR Pin)

The SR function can set the rise time and fall time of the gate voltage of the output FETs by connecting a pull-down resistor to the SR pin.

The pull-down resistance can be set from 0  $\Omega$  (connected to AGND) to 1M  $\Omega$ . It should not be open.

When this function is not used, connect the SR pin to AGND.

•Power Dissipation vs. Ambient Temperature

www.njr.com/

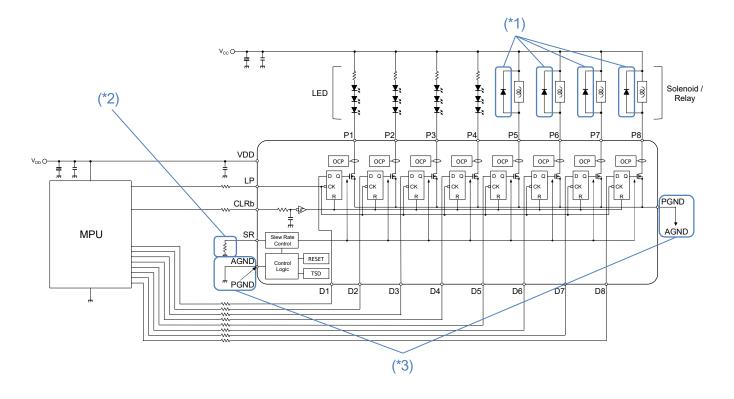

# **TYPICAL APPLICATION**

(\*1): The output pins don't have clamp circuits.

Therefore, when driving inductive loads such as solenoids and relays, connect a diode to the outside and secure path of recirculation current at turn-off.

- (\*2): When SR function is not used, connect the SR pin to AGND and it should not be open.

- (\*3): It should be wired the board so that there is no potential difference between AGND and PGND.

*New Japan Radio Co., Ltd.* www.njr.com/

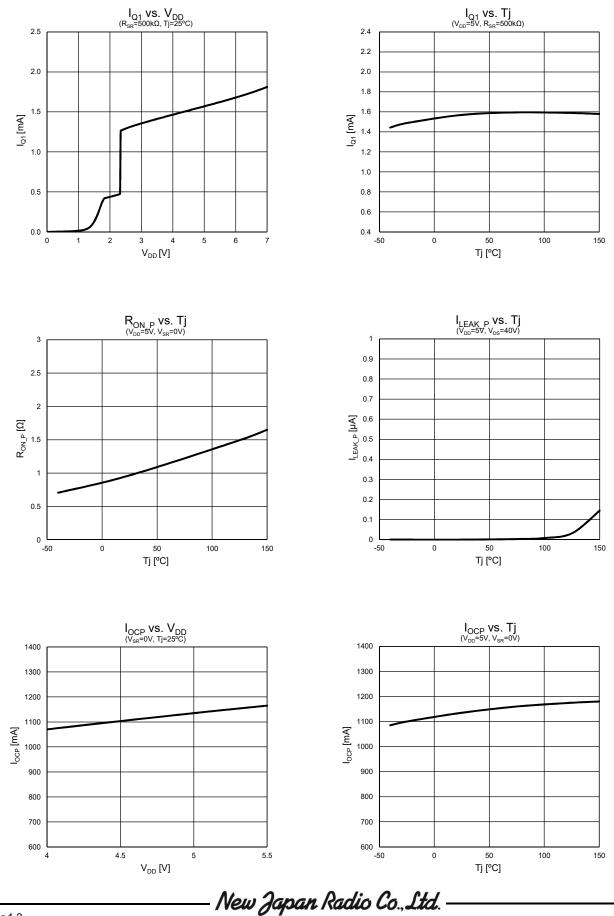

# **TYPICAL CHARACTERISTICS**

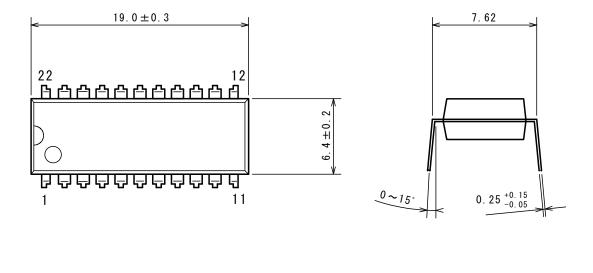

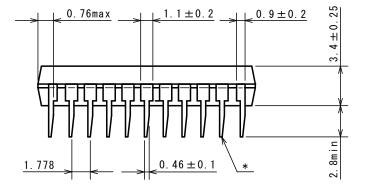

SDIP22

Unit: mm

#### ■PACKAGE DIMENSIONS

\*There are device mixed with taper on the right and the left.

New Japan Radio Co., Ltd.

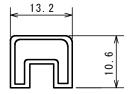

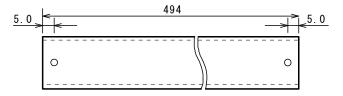

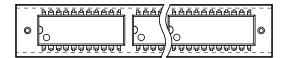

#### ■PACKING SPEC

#### STICK STATE

Stick (Max.25pcs) Material: PVC Stopper: Stick pin

Direction of 1pin.

PACKING STATE

New Japan Radio Co., Ltd.

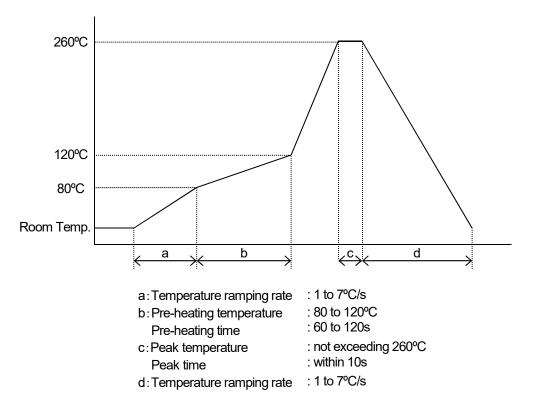

#### **■RECOMMENDED MOUNTING METHOD**

#### FLOW SOLDERING METHOD

\*flow soldering procedure

The temperature indicates at the lead terminal.

New Japan Radio Co., Ltd.

# **REVISION HISTORY**

| Date        | Revision | Changes                                                                                                                                                                              |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05.Jan.2018 | Ver.1.0  | New Release                                                                                                                                                                          |

| 21.Jun.2018 | Ver.1.1  | Corrected of GENERAL DESCRIPTION, APPLICATION NOTE (Power ON Reset Function) and<br>ELECTRICAL CHARACTERISTICS (Test conditions of Output ON Resistance and Maximum Output Current). |

| 23.Jul.2018 | Ver.1.2  | Corrected of APPLICATION NOTE (Truth Table)                                                                                                                                          |

- New Japan Radio Co.,Ltd. —

# [CAUTION]

- 1. New JRC strives to produce reliable and high quality semiconductors. New JRC's semiconductors are intended for specific applications and require proper maintenance and handling. To enhance the performance and service of New JRC's semiconductors, the devices, machinery or equipment into which they are integrated should undergo preventative maintenance and inspection at regularly scheduled intervals. Failure to properly maintain equipment and machinery incorporating these products can result in catastrophic system failures

- 2. The specifications on this datasheet are only given for information without any guarantee as regards either mistakes or omissions. The application circuits in this datasheet are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights. All other trademarks mentioned herein are property of their respective companies.

- 3. To ensure the highest levels of reliability, New JRC products must always be properly handled. The introduction of external contaminants (e.g. dust, oil or cosmetics) can result in failures of semiconductor products.

- 4. New JRC offers a variety of semiconductor products intended for particular applications. It is important that you select the proper component for your intended application. You may contact New JRC's Sale's Office if you are uncertain about the products listed in this catalog.

- 5. Special care is required in designing devices, machinery or equipment which demand high levels of reliability. This is particularly important when designing critical components or systems whose failure can foreseeably result in situations that could adversely affect health or safety. In designing such critical devices, equipment or machinery, careful consideration should be given to amongst other things, their safety design, fail-safe design, back-up and redundancy systems, and diffusion design.

- 6. The products listed in the catalog may not be appropriate for use in certain equipment where reliability is critical or where the products may be subjected to extreme conditions. You should consult our sales office before using the products in any of the following types of equipment.

Aerospace Equipment Equipment Used in the Deep sea Power Generator Control Equipment (Nuclear, Steam, Hydraulic) Life Maintenance Medical Equipment Fire Alarm/Intruder Detector Vehicle Control Equipment (airplane, railroad, ship, etc.) Various Safety devices

- 7. New JRC's products have been designed and tested to function within controlled environmental conditions. Do not use products under conditions that deviate from methods or applications specified in this catalog. Failure to employ New JRC products in the proper applications can lead to deterioration, destruction or failure of the products. New JRC shall not be responsible for any bodily injury, fires or accident, property damage or any consequential damages resulting from misuse or misapplication of its products. Products are sold without warranty of any kind, either express or implied, including but not limited to any implied warranty of merchantability or fitness for a particular purpose.

- 8. Warning for handling Gallium and Arsenic(GaAs) Products (Applying to GaAs MMIC, Photo Reflector). This Products uses Gallium(Ga) and Arsenic(As) which are specified as poisonous chemicals by law. For the prevention of a hazard, do not burn, destroy, or process chemically to make them as gas or power. When the product is disposed, please follow the related regulation and do not mix this with general industrial waste or household waste.

- 9. The product specifications and descriptions listed in this catalog are subject to change at any time, without notice.

New Japan Radio Co., Ltd.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

NJR: NJW4828L-A