**Features**

25V V<sub>CC</sub> rating

**Mechanical Data**

Case: SO-8

100V Drain voltage rating

Operation up to 500kHz

•

.

٠

٠

A Product Line of Diodes Incorporated

# **ZXGD3105N8**

#### SYNCHRONOUS MOSFET CONTROLLER IN SO-8

Proportional gate drive to minimize body diode conduction

Critical Conduction Mode (CrCM) & Continuous Mode (CCM)

Totally Lead-Free & Fully RoHS compliant (Notes 1 & 2)

Halogen and Antimony free. "Green" Device (Note 3)

Qualified to AEC-Q101 Standards for High Reliability

Case material: molded plastic. "Green" molding compound.

Terminals: Finish - Matte Tin Plated Leads, Solderable per

SO-8

Top View

Pin-Out

GATE

GND

DNC

REF

C

UL Flammability Classification Rating 94V-0

Moisture Sensitivity: Level 1 per J-STD-020

Solderable per MIL-STD-202, Method 208

MIL-STD-202, Method 208 @3

Weight: 0.074 grams (approximate)

Vcc 🖂

DNC

BIAS

DRAIN

Low standby power with quiescent supply current < 1mA

4.5V operation enables low voltage supply

Compliant with Eco-design directive

#### Description

ZXGD3105N8 synchronous controller is designed for driving a MOSFET as an ideal rectifier. This is to replace a diode for increasing the power transfer efficiency.

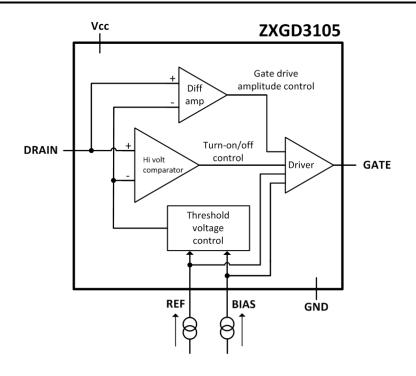

Proportional Gate drive control monitors the reverse voltage of the MOSFET such that if body diode conduction occurs a positive voltage is applied to the MOSFET's Gate pin. Once the positive voltage is applied to the Gate the MOSFET switches on allowing reverse current flow. The controllers' output voltage is then proportional to the MOSFET Drain-Source voltage and this is applied to the Gate via the driver. This action minimizes body diode conduction whilst enabling a rapid MOSFET turn off as Drain current decays to zero.

### **Applications**

Flyback Converters in:

- Low Voltage AC / DC Adaptors

- Set Top Box

- PoE power devices

Resonant Converters in:

- Telecoms PSU

- Laptop Adaptors

- Computing Power Supplies ATX and Server PSU

### Ordering Information (Note 4)

| Product      | Marking  | Reel size (inches) | Tape width (mm) | Quantity per reel |

|--------------|----------|--------------------|-----------------|-------------------|

| ZXGD3105N8TC | ZXGD3105 | 13                 | 12              | 2500              |

1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant.

2. See http://www.diodes.com for more information about Diodes Incorporated's definitions of Halogen and Antimony free, "Green" and Lead-Free. 3. Halogen and Antimony free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and

<1000ppm antimony compounds.

4. For packaging details, go to our website at http://www.diodes.com

## Marking Information

Notes:

7XGD = Product Type Marking Code, Line 1 3105 = Product Type Marking Code, Line 2 YΥ

- = Year (ex: 11 = 2011)

- = Week (01 53)

ww

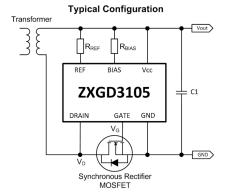

# **Functional Block Diagram**

| Pin<br>Number | Pin<br>Name | Pin Function and Description                                                                                                                                                             |

|---------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | Vcc         | Power supply<br>This supply pin should be closely decoupled to ground with a ceramic capacitor.                                                                                          |

| 2             | DNC         | Do not connect<br>Leave pin floating.                                                                                                                                                    |

| 3             | BIAS        | Bias<br>Connect this pin to $V_{CC}$ via $R_{BIAS}$ resistor. Select $R_{BIAS}$ to source 0.54mA into this pin.<br>Refer to Table 1 and 2, in Application Information section.           |

| 4             | DRAIN       | Drain sense<br>Connect directly to the synchronous MOSFET drain terminal.                                                                                                                |

| 5             | REF         | <b>Reference</b><br>Connect this pin to $V_{CC}$ via $R_{REF}$ resistor. Select $R_{REF}$ to source 1.02mA into this pin.<br>Refer to Table 1 and 2, in Application Information section. |

| 6             | DNC         | Do not connect<br>Leave pin floating.                                                                                                                                                    |

| 7             | GND         | Ground<br>Connect this pin to the synchronous MOSFET source terminal and ground reference point.                                                                                         |

| 8             | GATE        | Gate drive<br>This pin sinks and sources the I <sub>SINK</sub> and I <sub>SOURCE</sub> current to the synchronous MOSFET<br>gate.                                                        |

#### Maximum Ratings (@T<sub>A</sub> = +25°C, unless otherwise specified.)

| Characteristic                  | Symbol              | Value                    | Unit |

|---------------------------------|---------------------|--------------------------|------|

| Supply voltage, relative to GND | V <sub>CC</sub>     | 25                       | V    |

| Drain pin voltage               | V <sub>D</sub>      | -3 to +100               | V    |

| Gate output voltage             | VG                  | -3 to V <sub>CC</sub> +3 | V    |

| Gate Driver peak source current | I <sub>SOURCE</sub> | 4                        | A    |

| Gate Driver peak sink current   | I <sub>SINK</sub>   | 9                        | A    |

| Reference voltage               | V <sub>REF</sub>    | V <sub>CC</sub>          | V    |

| Reference current               | I <sub>REF</sub>    | 25                       | mA   |

| Bias voltage                    | V <sub>BIAS</sub>   | V <sub>CC</sub>          | V    |

| Bias current                    | I <sub>BIAS</sub>   | 100                      | mA   |

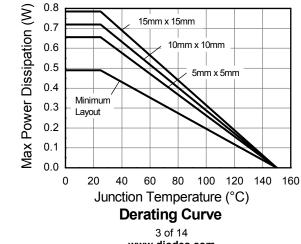

### Thermal Characteristics (@T<sub>A</sub> = +25°C, unless otherwise specified.)

| Characteristic                           |          | Symbol           | Value       | Unit  |

|------------------------------------------|----------|------------------|-------------|-------|

|                                          | (Note 5) |                  | 490<br>3.92 |       |

| Power Dissipation                        | (Note 6) |                  | 655<br>5.24 | mW    |

| Linear derating factor                   | (Note 7) | PD PD            | 720<br>5.76 | mW/°C |

|                                          | (Note 8) |                  | 785<br>6.28 |       |

|                                          | (Note 5) |                  | 255         |       |

| Thermal Desistance Investige to Archient | (Note 6) |                  | 191         | °C/W  |

| Thermal Resistance, Junction to Ambient  | (Note 7) | R <sub>0JA</sub> | 173         | C/W   |

|                                          | (Note 8) |                  | 159         |       |

| Thermal Resistance, Junction to Lead     | (Note 9) | R <sub>θJL</sub> | 135         | °C /W |

| Operating Temperature Range              |          | TJ               | -40 to +150 | *0    |

| Storage Temperature Range                |          | T <sub>STG</sub> | -50 to +150 | - °C  |

#### ESD Ratings (Note 10)

| Characteristic                             | Symbol  | Value | Unit | JEDEC Class |

|--------------------------------------------|---------|-------|------|-------------|

| Electrostatic Discharge - Human Body Model | ESD HBM | 4,000 | V    | 3A          |

| Electrostatic Discharge - Machine Model    | ESD MM  | 200   | V    | В           |

Notes: 5. For a device surface mounted on minimum recommended pad layout FR4 PCB with high coverage of single sided 1oz copper, in still air conditions; the device is measured when operating in a steady-state condition.

Same as note (5), except pin 1 (V<sub>cc</sub>) and pin 7 (GND) are both connected to separate 5mm x 5mm 1oz copper heatsinks.

Same as note (6), except both heatsinks are 10mm x 10mm.

8. Same as note (6), except both heatsinks are 15mm x 15mm.

9. Thermal resistance from junction to solder-point at the end of each lead on pin 1 (V<sub>cc</sub>) and pin 7 (GND).

10. Refer to JEDEC specification JESD22-A114 and JESD22-A115.

### **Thermal Derating Curve**

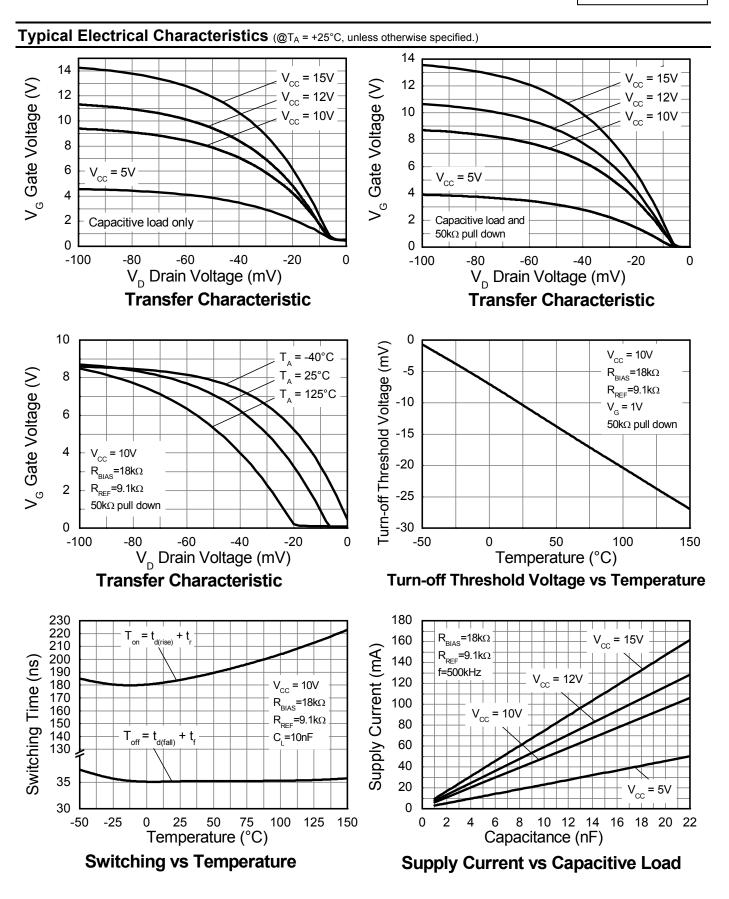

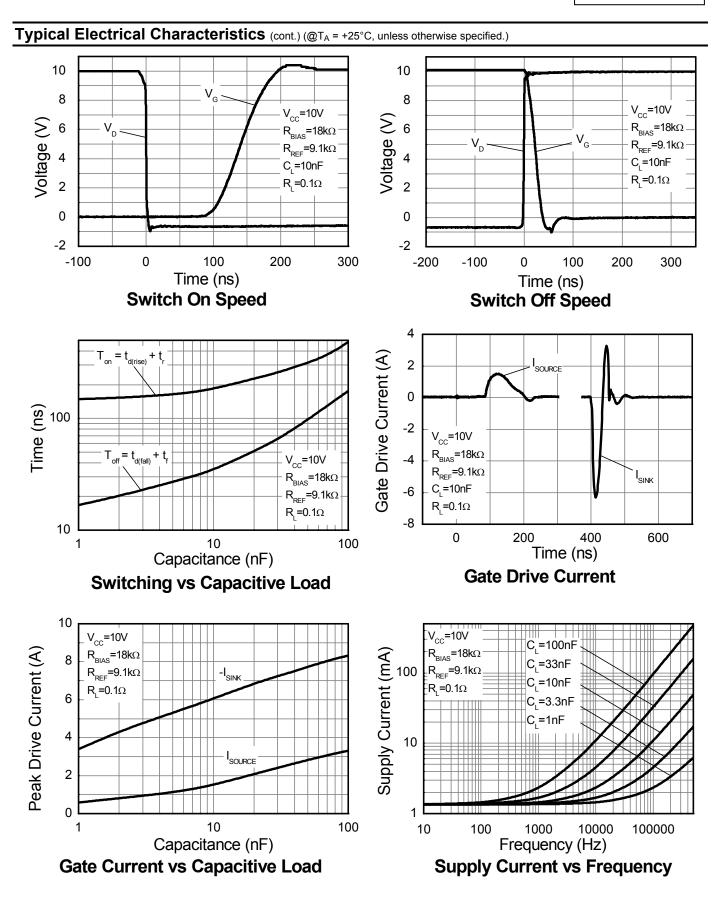

## Electrical Characteristics (@T<sub>A</sub> = +25°C, unless otherwise specified.)

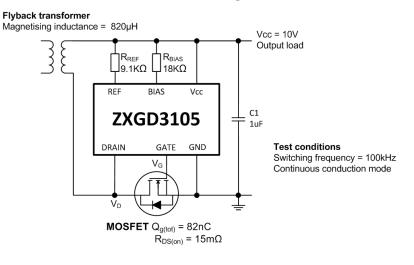

#### $V_{CC} = 10V; R_{BIAS} = 18k\Omega (I_{BIAS} = 0.54mA); R_{REF} = 9.1k\Omega (I_{REF} = 1.02mA)$

| Characteristic              | Symbol                        | Min | Тур                     | Max                  | Unit | Test Condition                         |                   |

|-----------------------------|-------------------------------|-----|-------------------------|----------------------|------|----------------------------------------|-------------------|

| Input Supply                |                               |     |                         |                      |      |                                        |                   |

| Quiescent current           | lq                            | —   | 1.56                    | _                    | mA   | V <sub>DRAIN</sub> ≥ 0mV               |                   |

| Gate Driver                 |                               |     |                         |                      |      |                                        |                   |

| Gate peak source current    | ISOURCE                       | —   | 2                       | _                    | А    | Capacitive load: C <sub>L</sub> = 20nF |                   |

| Gate peak sink current      | Isink                         | _   | 7                       | -                    | A    |                                        |                   |

| Detector under DC condition |                               |     |                         |                      |      |                                        |                   |

| Turn-off Threshold Voltage  | VT                            | -20 | -10                     | 0                    | mV   | V <sub>G</sub> = 1V                    |                   |

|                             | V <sub>G(off)</sub> — 0.2 0.6 |     | V <sub>DRAIN</sub> ≥ 1V | Capacitive load only |      |                                        |                   |

| Gate output voltage         |                               | 5.0 | 7.8                     | -                    | V    | V <sub>DRAIN</sub> = -50mV             |                   |

|                             | V <sub>G</sub>                | 8.0 | 9.4                     | _                    |      | V <sub>DRAIN</sub> = -100mV            |                   |

| Switching Performance       |                               |     |                         |                      |      |                                        |                   |

| Turn-on propagation delay   | t <sub>d(rise)</sub>          | —   | 70                      | _                    |      | Rise and fall measured 10% to 90%      |                   |

| Gate rise time              | tr                            | _   | 175                     | _                    |      |                                        |                   |

| Turn-off propagation delay  | t <sub>d(fall)</sub>          | _   | 15                      |                      | ns   | Refer to application                   | est circuit below |

| Gate fall time              | t <sub>f</sub>                | _   | 20                      | _                    |      |                                        |                   |

**Test Circuit for Switching Performance**

# Application Information

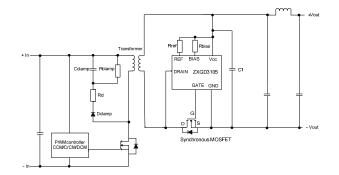

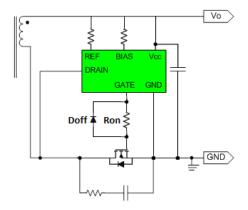

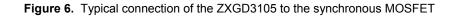

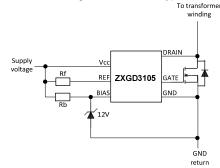

The purpose of the ZXGD3105 is to drive a MOSFET as a low-V<sub>F</sub> Schottky diode replacement in isolated AC/DC converter. When combined with a low  $R_{DS(ON)}$  MOSFET, the controller can yield significant power efficiency improvement, whilst maintaining design simplicity and incurring minimal component count. Figure 1 shows the typical configuration of ZXGD3105 for synchronous rectification in a low output voltage Flyback converter.

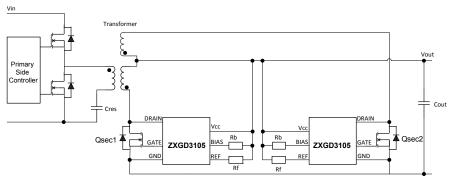

A typical circuit configuration of synchronous rectification with ZXGD3105 for use in resonant converter is shown in Figure 2. Two ZXGD3105 together with two synchronous MOSFETs should be used on the secondary side of the center tapped transformer winding.

Figure 1. Typical Flyback application schematic

Figure 2. Synchronous rectification in resonant converter

#### **Threshold Voltage and Resistor Setting**

Proper selection of external resistors  $R_{REF}$  and  $R_{BIAS}$  is important for optimum device operation.  $R_{REF}$  and  $R_{BIAS}$  supply fixed current into the  $I_{REF}$  and  $I_{BIAS}$  pin of the controller.  $I_{REF}$  and  $I_{BIAS}$  combines to set the turn-off threshold voltage level,  $V_T$ . In order to set  $V_T$  to -10mV, the recommended  $I_{REF}$  and  $I_{BIAS}$  are 1.02mA and 0.54mA respectively.

The values for  $R_{REF}$  and  $R_{BIAS}$  are selected based on the  $V_{CC}$  voltage. If the  $V_{CC}$  pin is connected to the power converter's output, the resistors should be selected based on the nominal converter's output voltage. Table 1 provides the recommended resistor values for different Vcc voltages.

| Supply, V <sub>CC</sub> | Bias Resistor, R <sub>BIAS</sub> | Reference Resistor, R <sub>REF</sub> |

|-------------------------|----------------------------------|--------------------------------------|

| 5 V                     | 9.6 kΩ                           | 4.3 kΩ                               |

| 10V                     | 18 kΩ                            | 9.1 kΩ                               |

| 12V                     | 24 kΩ                            | 11 kΩ                                |

| 15V                     | 30 kΩ                            | 15 kΩ                                |

#### Functional Descriptions for Flyback Converter

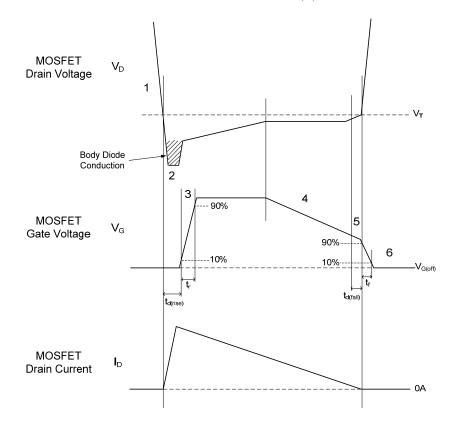

The operation of the device is described step-by-step with reference to the timing diagram in Figure 3.

- 1. The detector stage monitors the MOSFET Drain-Source voltage.

- 2. When, due to transformer action, the MOSFET body diode is forced to conduct there is a negative voltage on the Drain pin due to the body diode forward voltage.

- 3. When the negative Drain voltage crosses the turn-off Threshold voltage V<sub>T</sub>, the detector stage outputs a positive voltage with respect to ground after the turn-on delay time t<sub>d(fall)</sub>. This voltage is then fed to the MOSFET driver stage and current is sourced out of the GATE pin.

- 4. The controller goes into proportional gate drive control the GATE output voltage is proportional to the MOSFET on-resistanceinduced Drain-Source voltage. Proportional gate drive ensures that MOSFET conducts during the majority of the conduction cycle to minimize power loss in the body diode.

- 5. As the Drain current decays linearly toward zero, proportional gate drive control reduces the Gate voltage so the MOSFET can be turned off rapidly at zero current crossing. The GATE voltage falls to 1V when the Drain-Source voltage crosses the detection threshold voltage to minimize reverse current flow.

- 6. At zero Drain current, the controller GATE output voltage is pulled low to  $V_{G(off)}$  to ensure that the MOSFET is off.

Figure 3. Timing diagram for a critical conduction mode Flyback converter

#### Functional Descriptions for Resonant Converter

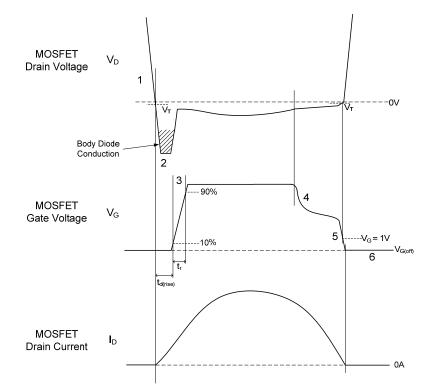

The operation of the ZXGD3105 in resonant converter is described with reference to Figure 4.

- 1. The detector stage monitors the MOSFET Drain-GND voltage.

- 2. When, due to transformer action, the MOSFET body diode is forced to conduct there is a negative voltage on the Drain pin due to the body diode forward voltage.

- When the negative Drain voltage crosses the Threshold voltage V<sub>T</sub>, the detector stage outputs a positive voltage with respect to ground after the turn-on delay time t<sub>d(rise)</sub>. This voltage is then fed to the MOSFET driver stage and current is sourced out of the GATE pin.

- 4. The controller goes into Proportional Gate Drive control. The GATE voltage now varies according to the MOSFET's Drain-GND voltage. During this phase, the relationship of V<sub>G</sub> vs. V<sub>D</sub> is shown by the transfer characteristic curve in page xx of this datasheet. As the Drain current decays linearly, the Gate voltage reduces so the MOSFET can be turned off rapidly at zero current crossing. Proportional Gate Drive also ensures that gate voltage is supplied to the MOSFET gate until the Drain current is virtually zero. This eliminates any parasitic diode conduction after the MOSFET switches off.

- 5. The GATE voltage falls to 1V when the Drain-GND voltage reaches V<sub>T</sub>. The MOSFET is turned off precisely when the sinusoidal current goes to zero, with little or no reverse current. Threshold voltage V<sub>T</sub> is defined as the Drain voltage V<sub>D</sub> level at which Gate voltage V<sub>G</sub> is 1V (refer to electrical characteristic section in page 4).

- 6. At zero Drain current, the GATE voltage is pulled low to  $V_{G(off)}$  to ensure that the MOSFET is off.

Figure 4. Timing diagram of synchronous rectification in the resonant converter

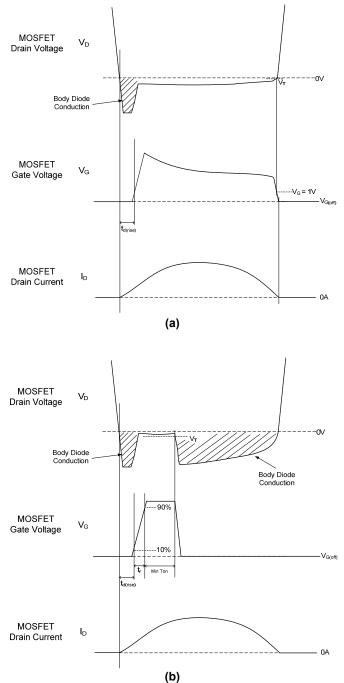

Besides that, Proportional Gate Drive improves the rectifier efficiency even at light to medium load condition by ensuring that the MOSFETs conduct during majority of the conduction cycle as shown in Figure 5a.

At reduced load condition, early termination of the gate drive voltage is likely for digital level gate drive due to the low current, which means that the threshold  $V_T$  is breached. With the early termination of the gate drive voltage, MOSFET turns off and the body diode conducts, see Figure 5. This is shown by an increase in Drain-GND voltage for the remaining time of the current waveform. With the current flowing through the body diode there will be an increase in power developed within the MOSFET. The efficiency impact due to early termination of digital level gate driver increases with lower  $R_{DS(on)}$  MOSFET and/or higher operating frequency.

Figure 5. Timing diagram of synchronous rectification in the resonant converter (a) Proportional Gate Drive and (b) Digital Level Gate Drive

#### **Gate Driver**

The controller is provided with single channel high current gate drive output, capable of driving one or more N-channel power MOSFETs. The controller can operate from Vcc of 4.5V to drive both standard MOSFETs and logic level MOSFETs.

The Gate pins should be as close to the MOSFET's gate as possible. A resistor in series with GATE pin helps to control the rise time and decrease switching losses due to gate voltage oscillation. A diode in parallel to the resistor is typically used to maintain fast discharge of the MOSFET's gate.

#### **Quiescent Current Consumption**

The quiescent current consumption of the controller is the sum of  $I_{REF}$  and  $I_{BIAS}$ . For an application that requires ultra-low standby power consumption,  $I_{REF}$  and  $I_{BIAS}$  can be further reduced by increasing the value of resistor  $R_{REF}$  and  $R_{BIAS}$ .

| Bias Current | Ref Current      | Bias Resistor     | Ref Resistor     | Quiescent Current |

|--------------|------------------|-------------------|------------------|-------------------|

| IBIAS        | I <sub>REF</sub> | R <sub>BIAS</sub> | R <sub>REF</sub> | Ι <sub>Q</sub>    |

| 0.25mA       | 0.61mA           | 39.2KΩ            | 15.4KΩ           | 0.86mA            |

| 0.35mA       | 0.81mA           | 28.0KΩ            | 11.5KΩ           | 1.16mA            |

| 0.46mA       | 0.99mA           | 21.5KΩ            | 9.3KΩ            | 1.45mA            |

| 0.50mA       | 1.00mA           | 19.6KΩ            | 8.9ΚΩ            | 1.50mA            |

| 0.55mA       | 1.13mA           | 17.8ΚΩ            | 8.1ΚΩ            | 1.68mA            |

| 0.80mA       | 1.66mA           | 12.1KΩ            | 5.6ΚΩ            | 2.46mA            |

Table 2. Quiescent current consumption for different resistor values at Vcc=10V

$I_{REF}$  also controls the gate driver peak sink current whilst  $I_{BIAS}$  controls the peak source current. At the default current value of  $I_{REF}$  and  $I_{BIAS}$  of 1.02mA and 0.54mA, the gate driver is able to provide 2A source and 6A sink current. The gate current decreases if  $I_{REF}$  and  $I_{BIAS}$  are reduced. Care must be taken in reducing the controller quiescent current so that sufficient drive current is still delivered to the MOSFET particularly for high switching frequency application.

#### Layout Guidelines

When laying out the PCB, care must be taken in decoupling the ZXGD3105 closely to  $V_{CC}$  and ground with 1µF low-ESR, low-ESL X7R type ceramic bypass capacitor. If the converter's output voltage is higher than 20V, a 12V zener diode should be connected from the bias pin to GND to clamp the Gate voltage and protect the synchronous MOSFET. Figure 7 shows the typical connection diagram.

Figure 7. Zener Voltage Clamp Arrangement

GND is the ground reference for the internal high voltage amplifier as well as the current return for the gate driver. So the ground return loop should be as short as possible. Sufficient PCB copper area should be allocated to the Vcc and GND pin for heat dissipation especially for high switching frequency application.

Any stray inductance involved by the load current may cause distortion of the drain-to-source voltage waveform, leading to premature turn-off of the synchronous MOSFET. In order to avoid this issue, drain voltage sensing should be done as physically close to the drain terminals as possible. The PCB track length between the controller Drain pin and the MOSFET's terminal should be kept less than 10mm. MOSFET packages with low internal wire bond inductance are preferred for high switching frequency power conversion to minimize body diode conduction.

After the primary MOSFET turns off, its Drain voltage oscillates due to reverse recovery of the snubber diode. These high frequency oscillations are reflected across the transformer to the Drain terminal of the synchronous MOSFET. The synchronous controller senses the Drain voltage ringing, causing its gate output voltage to oscillate. The synchronous MOSFET cannot be fully enhanced until the Drain voltage stabilizes.

In order to prevent this issue, the oscillations on the primary MOSFET can be damped with either a series resistor Rd to the snubber diode or an R-C network across the diode (refer Figure 8). Both methods reduce the oscillations by softening the snubber diode's reverse recovery characteristic.

Figure 8. Primary Side Snubber Network to Reduce Drain Voltage Oscillations

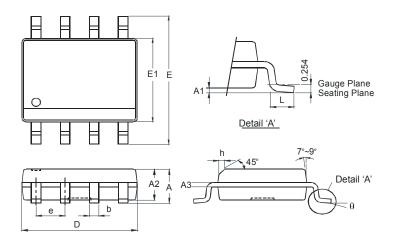

# Package Outline Dimensions

Please see AP02002 at http://www.diodes.com/datasheets/ap02002.pdf for latest version.

|        | SO-8                 |      |  |  |  |

|--------|----------------------|------|--|--|--|

| Dim    | Min                  | Max  |  |  |  |

| Α      | -                    | 1.75 |  |  |  |

| A1     | 0.10                 | 0.20 |  |  |  |

| A2     | 1.30                 | 1.50 |  |  |  |

| A3     | 0.15                 | 0.25 |  |  |  |

| b      | 0.3                  | 0.5  |  |  |  |

| D      | 4.85                 | 4.95 |  |  |  |

| E      | 5.90                 | 6.10 |  |  |  |

| E1     | 3.85                 | 3.95 |  |  |  |

| е      | 1.27                 | Тур  |  |  |  |

| h      | -                    | 0.35 |  |  |  |

| L      | 0.62                 | 0.82 |  |  |  |

| θ      | 0°                   | 8°   |  |  |  |

| All Di | All Dimensions in mm |      |  |  |  |

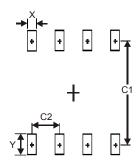

# **Suggested Pad Layout**

Please see AP02001 at http://www.diodes.com/datasheets/ap02001.pdf for the latest version.

| Dimensions | Value (in mm) |

|------------|---------------|

| Х          | 0.60          |

| Y          | 1.55          |

| C1         | 5.4           |

| C2         | 1.27          |

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2013, Diodes Incorporated

www.diodes.com