# ICM7211AM

4-Digit, LCD Display Driver

FN3158 Rev.8.01 Jul 15, 2020

The ICM7211AM device is a non-multiplexed four-digit seven-segment CMOS LCD display decoder-driver.

This device is configured to drive conventional LCD displays by providing a complete RC oscillator, divider chain, backplane driver, and 28 segment outputs.

It also has a microprocessor compatible input configuration, which provides data input latches and Digit Address latches under control of high-speed Chip Select inputs. These devices simplify the task of implementing a cost-effective alphanumeric seven-segment display for microprocessor systems, without requiring extensive ROM or CPU time for decoding and display updating.

The ICM7211AM provides the "Code B" output code, i.e., 0-9, dash, E, H, L, P, blank, but will correctly decode true BCD to seven-segment decimal outputs.

### Features

- Four Digit Non-Multiplexed 7 Segment LCD Display Outputs with Backplane Driver

- Complete Onboard RC Oscillator to Generate Backplane Frequency

- Backplane Input/Output Allows Simple Synchronization of Slave-Devices to a Master

- Provides Data and Digit Address Latches Controlled by Chip Select Inputs to Provide a Direct High Speed Processor Interface

- Decodes Binary to Code B (0-9, Dash, E, H, L, P, Blank)

- Pb-Free Plus Anneal Available (RoHS Compliant)

## **Ordering Information**

| PART NUMBER                                                                             | PART MARKING  | DISPLAY<br>TYPE | DISPLAY<br>DECODING | INPUT<br>INTERFACING | DISPLAY<br>DRIVE TYPE | TEMP.<br>RANGE (°C) | PACKAGE                  | PKG.<br>DWG.# |

|-----------------------------------------------------------------------------------------|---------------|-----------------|---------------------|----------------------|-----------------------|---------------------|--------------------------|---------------|

| ICM7211AMIM44 (No<br>longer available,<br>recommended<br>replacement:<br>ICM7211AMIPLZ) | ICM7211AMIM44 | LCD             | Code B              | Microprocessor       | Direct Drive          | -40 to 85           | 44 Ld MQFP               | Q44.10x10     |

| ICM7211AMIPLZ<br>(Note)                                                                 | ICM7211AMIPLZ | LCD             | Code B              | Microprocessor       | Direct Drive          | -40 to 85           | 40 Ld PDIP*<br>(Pb-free) | E40.6         |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

\*Pb-free PDIPs can be used for through hole wave solder processing only. They are not intended for use in Reflow solder processing applications.

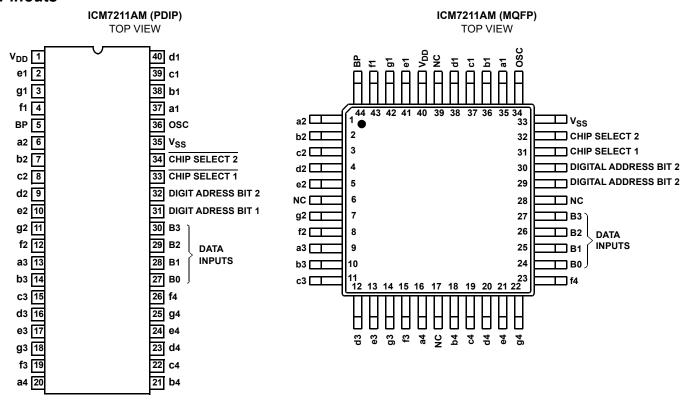

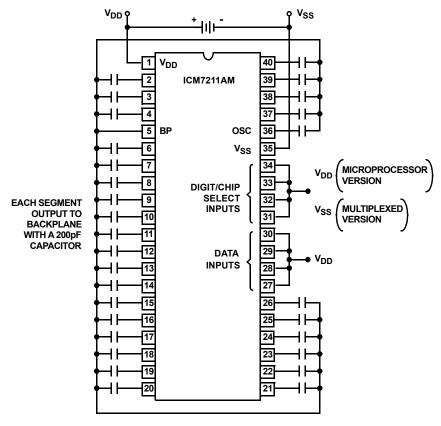

## **Pinouts**

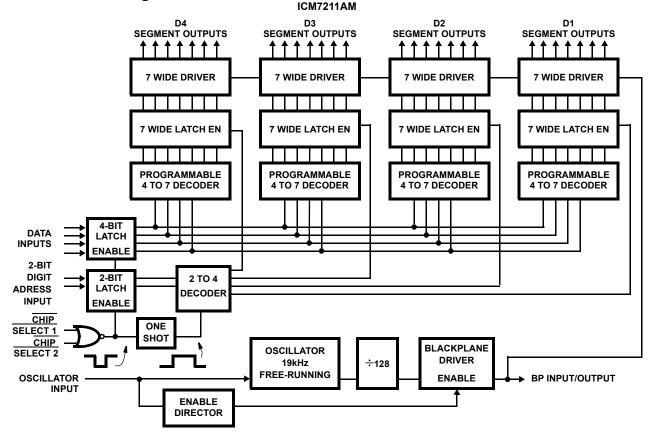

# Functional Block Diagram

### **Absolute Maximum Ratings**

Supply Voltage (V $_{DD}$  - V $_{SS}$ ). . . . . . . . . . . . . . . . . . 6.5V Input Voltage (Any Terminal) (Note 1) . . . V $_{SS}$  - 0.3V to V $_{DD}$ , + 0.3V

### **Operating Conditions**

### **Thermal Information**

| Thermal Resistance (Typical, Note 2)      | $\theta_{JA}$ (°C/W) |

|-------------------------------------------|----------------------|

| PDIP Package*                             | 60                   |

| MQFP Package                              | 70                   |

| Maximum Junction Temperature              |                      |

| Maximum Storage Temperature Range659      | c°C to 150°C         |

| Maximum Lead Temperature (Soldering, 10s) | 300°C                |

\*Pb-free PDIPs can be used for through hole wave solder processing only. They are not intended for use in Reflow solder processing applications.

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES

- Due to the SCR structure inherent in the CMOS process, connecting any terminal to voltages greater than V<sub>DD</sub> or less than V<sub>SS</sub> may cause

destructive device latchup. For this reason, it is recommended that no inputs from external sources not operating on the same power supply be

applied to the device before its supply is established, and that in multiple supply systems, the supply to the ICM7211AM be turned on first.

- 2.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

### **Electrical Specifications**

| PARAMETER                                                                                                         | TEST CONDITIONS                                               | MIN | TYP   | MAX | UNITS |  |  |

|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----|-------|-----|-------|--|--|

| CHARACTERISTICS V <sub>DD</sub> = 5V ±10%, T <sub>A</sub> = 25°C, V <sub>SS</sub> = 0V Unless Otherwise Specified |                                                               |     |       |     |       |  |  |

| Operating Supply Voltage Range (V <sub>DD</sub> - V <sub>SS</sub> ), V <sub>SUPPLY</sub>                          |                                                               | 3   | 5     | 6   | V     |  |  |

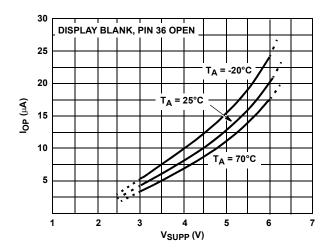

| Operating Current, I <sub>DD</sub>                                                                                | Test circuit, Display blank                                   | -   | 10    | 50  | μА    |  |  |

| Oscillator Input Current, I <sub>OSCI</sub>                                                                       | Pin 36                                                        | -   | ±2    | ±10 | μА    |  |  |

| Segment Rise/Fall Time, t <sub>r</sub> , t <sub>f</sub>                                                           | C <sub>L</sub> = 200pF                                        | -   | 0.5   | -   | μs    |  |  |

| Backplane Rise/Fall Time, $t_{\rm f}$ , $t_{\rm f}$                                                               | C <sub>L</sub> = 5000pF                                       | -   | 1.5   | -   | μs    |  |  |

| Oscillator Frequency, f <sub>OSC</sub>                                                                            | Pin 36 Floating                                               | -   | 19    | -   | kHz   |  |  |

| Backplane Frequency, f <sub>BP</sub>                                                                              | Pin 36 Floating                                               | -   | 150   | -   | Hz    |  |  |

| INPUT CHARACTERISTICS                                                                                             |                                                               |     | 1     | I.  | 1     |  |  |

| Logical "1" Input Voltage, V <sub>IH</sub>                                                                        |                                                               | 4   | -     | -   | V     |  |  |

| Logical "0" Input Voltage, V <sub>IL</sub>                                                                        |                                                               | -   | -     | 1   | V     |  |  |

| Input Leakage Current, I <sub>ILK</sub>                                                                           | Pins 27-34                                                    | -   | ±0.01 | ±1  | μА    |  |  |

| Input Capacitance, C <sub>IN</sub>                                                                                | Pins 27-34                                                    | -   | 5     | -   | pF    |  |  |

| BP/Brightness Input Leakage, I <sub>BPLK</sub>                                                                    | Measured at Pin 5 with Pin 36 at V <sub>SS</sub>              | -   | ±0.01 | ±1  | μА    |  |  |

| BP/Brightness Input Capacitance, C <sub>BPI</sub>                                                                 | All Devices                                                   | -   | 200   | -   | pF    |  |  |

| AC CHARACTERISTICS                                                                                                |                                                               |     | 1     | I.  | 1     |  |  |

| Chip Select Active Pulse Width, t <sub>WL</sub>                                                                   | Other Chip Select Either Held Active, or Both Driven Together | 200 | -     | -   | ns    |  |  |

| Data Setup Time, t <sub>DS</sub>                                                                                  |                                                               | 100 | -     | -   | ns    |  |  |

| Data Hold Time, t <sub>DH</sub>                                                                                   |                                                               | 10  | 0     | -   | ns    |  |  |

| Inter-Chip Select Time, t <sub>ICS</sub>                                                                          |                                                               | 2   | -     | -   | μS    |  |  |

$\begin{tabular}{ll} \textbf{In this table}, V_{DD} \ and \ V_{SS} \ are \ considered \ to \ be \ normal \ operating \ input \ logic \ levels. Actual \ input \ low \ and \ high \ levels \ are \ specified \ under \ Operating \ Characteristics. For lowest power \ consumption, input \ signals \ should \ swing \ over \ the \ full \ supply.$

| INPUT                                                                                                              | DIP TERMINAL | CONDITIONS                                                      | FUNCTION                  |                  |  |

|--------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------|---------------------------|------------------|--|

| В0                                                                                                                 | 27           | V <sub>DD</sub> = Logical One<br>V <sub>SS</sub> = Logical Zero | Ones (Least Significant)  |                  |  |

| B1                                                                                                                 | 28           | V <sub>DD</sub> = Logical One<br>V <sub>SS</sub> = Logical Zero | Twos                      | Data In aut Bita |  |

| B2                                                                                                                 | 29           | V <sub>DD</sub> = Logical One<br>V <sub>SS</sub> = Logical Zero | Fours                     | Data Input Bits  |  |

| B3                                                                                                                 | 30           | V <sub>DD</sub> = Logical One<br>V <sub>SS</sub> = Logical Zero | Eights (Most Significant) | _                |  |

| osc                                                                                                                | 36           | Floating or with External Capacitor to V <sub>DD</sub>          | Oscillator Input          |                  |  |

| V <sub>SS</sub> Disables BP output devices, allowing segments to external signal input at the BP terminal (Pin 5). |              |                                                                 |                           |                  |  |

## **Interface Input Configuration**

| INPUT | DESCRIPTION                  | DIP TERMINAL | CONDITIONS                                                      | FUNCTION                                                                                                                                                                              |

|-------|------------------------------|--------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DA1   | Digit Address<br>Bit 1 (LSB) | 31           | V <sub>DD</sub> = Logical One<br>V <sub>SS</sub> = Logical Zero | DA1 and DA2 serve as a 2-bit Digit Address Input DA2, DA1 = 00 selects D4                                                                                                             |

| DA2   | Digit Address<br>Bit 2 (MSB) | 32           | V <sub>DD</sub> = Logical One<br>V <sub>SS</sub> = Logical Zero | DA2, DA1 = 01 selects D3 DA2, DA1 = 10 selects D2 DA2, DA1 = 11 selects D1                                                                                                            |

| CS1   | Chip Select 1                | 33           | V <sub>DD</sub> = Inactive<br>V <sub>SS</sub> = Active          | When both $\overline{\text{CS1}}$ and $\overline{\text{CS2}}$ are taken low, the data at the Data and Digit Select code inputs are written into the input latches. On the rising edge |

| CS2   | Chip Select 2                | 34           | V <sub>DD</sub> = Inactive<br>V <sub>SS</sub> = Active          | of either Chip Select, the data is decoded and written into the output latches.                                                                                                       |

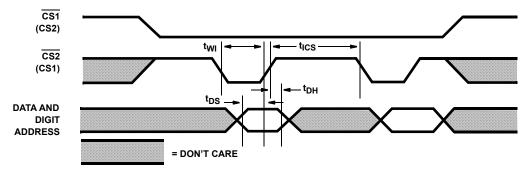

# **Timing Diagram**

FIGURE 1. MICROPROCESSOR INTERFACE INPUT

# Typical Performance Curves

FIGURE 2. OPERATING SUPPLY CURRENT AS A FUNCTION OF SUPPLY VOLTAGE

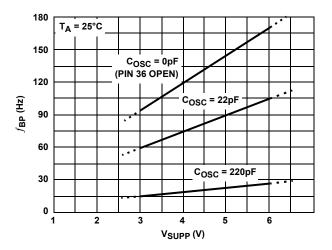

FIGURE 3. BACKPLANE FREQUENCY AS A FUNCTION OF SUPPLY VOLTAGE

## **Description of Operation**

### **Device**

The ICM7211AM provides outputs suitable for driving conventional four-digit, seven-segment LCD displays. These devices include 28 individual segment drivers, backplane driver, and a self-contained oscillator and divider chain to generate the backplane frequency.

The segment and backplane drivers each consist of a CMOS inverter, with the N-Channel and P-Channel devices ratioed to provide identical on resistances, and thus equal rise and fall times. This eliminates any DC component, which could arise from differing rise and fall times, and ensures maximum display life.

The backplane output devices can be disabled by connecting the OSCillator input (pin 36) to VSS. This allows the 28 segment outputs to be synchronized directly to a signal input at the BP terminal (pin 5). In this manner, several slave devices may be cascaded to the backplane output of one master device, or the backplane may be derived from an external source. This allows the use of displays with characters in multiples of four and a single backplane. A slave device represents a load of approximately 200pF (comparable to one additional segment). Thus the limitation of the number of devices that can be slaved to one master device backplane driver is the additional load represented by the larger backplane of displays of more than four digits. A good rule of thumb to observe in order to minimize power consumption is to keep the backplane rise and fall times less than about 5µs. The backplane output driver should handle the backplane to a display of 16 one-half inch characters. It is recommended, if more than four devices are to be slaved together, the backplane signal be derived externally and all the ICM7211AM devices be slaved to it. This external signal should be capable of driving very large capacitive loads with short (1 - 2μs) rise and fall times. The maximum frequency for a backplane signal should be about 150Hz although this may be too fast for optimum display response at lower display temperatures, depending on the display type.

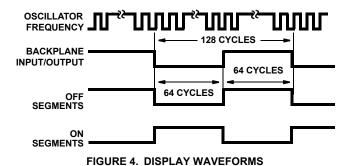

The onboard oscillator is designed to free run at approximately 19kHz at microampere current levels. The oscillator frequency is divided by 128 to provide the backplane frequency, which will be approximately 150Hz with the oscillator free-running; the oscillator frequency may be reduced by connecting an external capacitor between the OSCillator terminal and  $V_{\mbox{\scriptsize DD}}$ .

The oscillator may also be overdriven if desired, although care must be taken to ensure that the backplane driver is not disabled during the negative portion of the overdriving signal (which could cause a DC component to the display). This can be done by driving the OSCillator input between the positive supply and a level out of the range where the backplane disable is sensed (about one fifth of the supply voltage above  $V_{SS}$ ).

Another technique for overdriving the oscillator (with a signal swinging the full supply) is to skew the duty cycle of the overdriving signal such that the negative portion has a duration shorter than about one microsecond. The backplane disable sensing circuit will not respond to signals of this duration.

### Input Configurations and Output Codes

The ICM7211AM accepts a four-bit true binary (i.e., positive level = logical one) input at pins 27 thru 30, least significant bit at pin 27 ascending to the most significant bit at pin 30. It decodes the binary input into seven-segment alphanumeric "Code B" output, i.e., 0-9, dash, E, H, L, P, blank. These codes are shown explicitly in Table 1. It will correctly decode true BCD to a seven-segment decimal output.

**TABLE 1. OUTPUT CODES**

|    | BIN |    |    |                     |

|----|-----|----|----|---------------------|

| В3 | B2  | B1 | во | CODE B<br>ICM7211AM |

| 0  | 0   | 0  | 0  | П                   |

| 0  | 0   | 0  | 1  | 1                   |

| 0  | 0   | 1  | 0  | 2                   |

| 0  | 0   | 1  | 1  | 3                   |

| 0  | 1   | 0  | 0  | 4                   |

| 0  | 1   | 0  | 1  | 5                   |

| 0  | 1   | 1  | 0  | 5                   |

| 0  | 1   | 1  | 1  | 7                   |

| 1  | 0   | 0  | 0  | 8                   |

| 1  | 0   | 0  | 1  | 9                   |

| 1  | 0   | 1  | 0  | -                   |

| 1  | 0   | 1  | 1  | E                   |

**TABLE 1. OUTPUT CODES (Continued)**

|    | BIN | 2005.0 |    |                     |

|----|-----|--------|----|---------------------|

| В3 | B2  | B1     | во | CODE B<br>ICM7211AM |

| 1  | 1   | 0      | 0  | Н                   |

| 1  | 1   | 0      | 1  | <u> </u>            |

| 1  | 1   | 1      | 0  | P                   |

| 1  | 1   | 1      | 1  | BLANK               |

The ICM7211AM is intended to accept data from a data bus under processor control.

In these devices, the four data input bits and the two-bit digit address (DA1 pin 31, DA2 pin 32) are written into input buffer latches when both chip select inputs (CS1 pin 33, CS2

pin 34) are taken low. On the rising edge of either chip select input, the content of the data input latches is decoded and stored in the output latches of the digit selected by the contents of the digit address latches.

An address of 00 writes into D4, DA2 = 0, DA1 = 1 writes into D3, DA2 = 1, DA1 = 0 writes into D2, and 11 writes into D1. The timing relationships for inputting data are shown in Figure 1, and the chip select pulse widths and data setup and hold times are specified under Operating Characteristics.

FIGURE 5. SEGMENT ASSIGNMENT

## **Test Circuit**

FIGURE 6.

# **Typical Application**

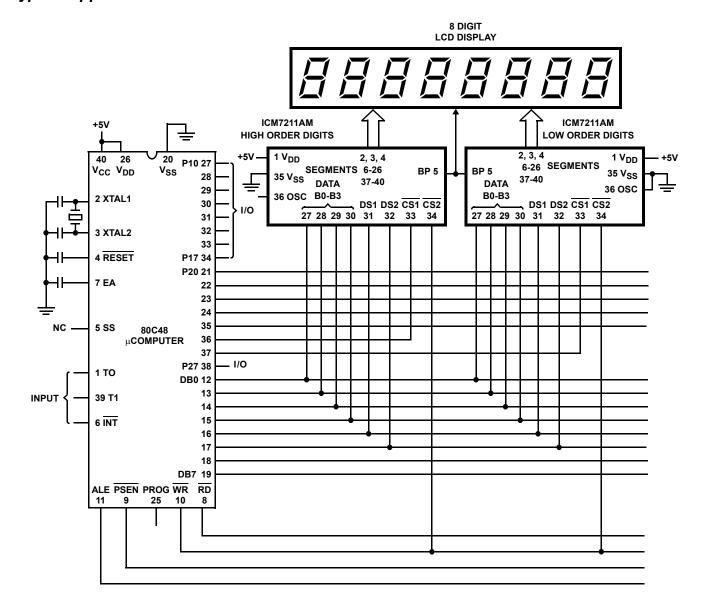

FIGURE 7. 80C48 MICROPROCESSOR INTERFACE

# **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to the web to make sure that you have the latest revision.

| DATE         | REVISION | CHANGE                                                                                               |

|--------------|----------|------------------------------------------------------------------------------------------------------|

| Jul 15, 2020 | 8.01     | Updated Ordering Information Table on page 1. Removed About Intersil section. Updated disclaimer.    |

| Oct 22, 2015 | 8.00     | Updated Ordering Information Table on page 1. Added Revision History. Added About Intersil Verbiage. |

### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

# **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/