# AS7265x

Smart 18-Channel VIS to NIR Spectral\_ ID 3-Sensor Chipset with Electronic Shutter

## **General Description**

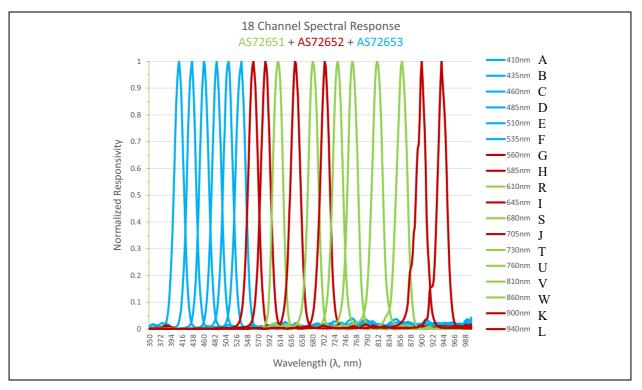

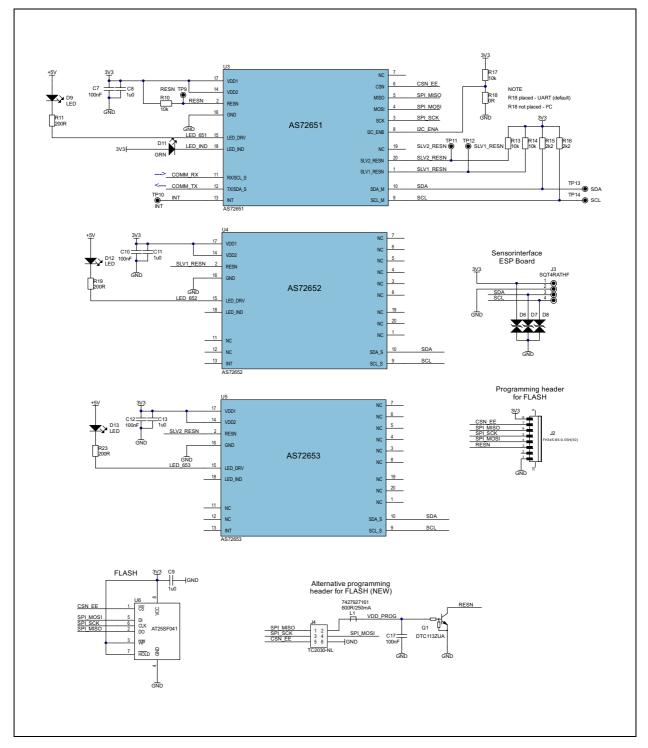

The AS7265x chipset consists of three sensor devices AS72651 with master capability, AS72652 and AS72653. The multispectral sensors can be used for spectral identification in a range from visible to NIR. Every of the three sensor devices has 6 independent on-device optical filters whose spectral response is defined in a range from 410nm to 940nm with FWHM of 20nm. The AS72651, combined with the AS72652 (spectral response from 560nm to 940nm) and the AS72653 (spectral response from 410nm to 535nm) form an AS7265x 18-channel multi-spectral sensor chip-set. Using the AS7265x chipset requires the use of firmware. It must be loaded into a serial flash via a UART interface. The list of **ams** tested serial flash memories can be found in Figure 56. The components AS72651, AS72652 and AS72653 are pre-calibrated with a specific light source. The information about the conditions of the performed calibration (for example light source, gain, integration time) can be found in the table of optical characteristics of the respective component. Any operation other than these conditions might require a new calibration in the application.

Each AS7265x device has two integrated LED drivers with programmable current and can be timed for electronic shutter applications.

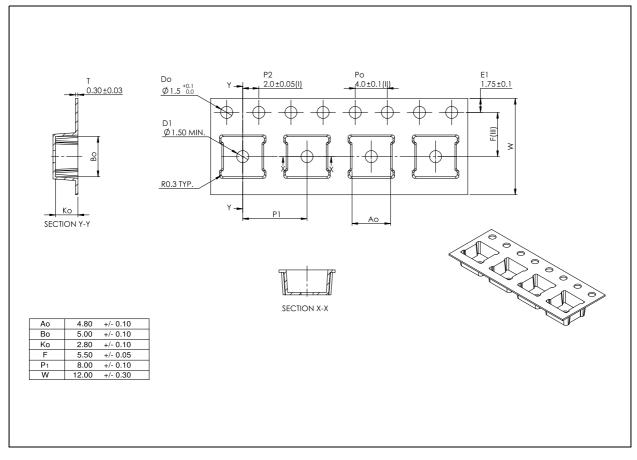

The device family integrates Gaussian filters into standard CMOS silicon via nano-optic deposited interference filter technology in LGA packages that also provide built-in apertures to control the light entering the sensor array.

Ordering Information and Content Guide appear at end of datasheet.

#### **Key Benefits & Features**

The benefits and features of AS7265x, Smart 18-Channel VIS to NIR Spectral\_ID 3-Sensor Chipset with Electronic Shutter are listed below:

## Figure 1:

AS7265x Chip-Set Benefits and Features

| Benefits                                      | Features                                                                                                                                      |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Compact 18-channel spectrometry chip-set      | <ul> <li>3 chip set including master device delivering 18<br/>visible and NIR channels from 410nm to 940nm<br/>each with 20nm FWHM</li> </ul> |

| solution                                      | UART or I <sup>2</sup> C slave digital Interface                                                                                              |

|                                               | Visible filter set realized by silicon interference filters                                                                                   |

|                                               | 16-bit ADC with digital access                                                                                                                |

| No additional signal conditioning required    | Programmable LED drivers                                                                                                                      |

|                                               | • 2.7V to 3.6V with I <sup>2</sup> C interface                                                                                                |

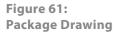

| Small, robust package, with built-in aperture | <ul> <li>20-pin LGA package 4.5mm x 4.7mm x 2.5mm</li> <li>-40°C to 85°C temperature range</li> </ul>                                         |

## Applications

The AS7265x applications include:

- Product/Brand authentication

- Anti-counterfeiting

- Portable spectroscopy

- Product safety/adulteration detection

- Horticultural and specialty lighting

- Material analysis

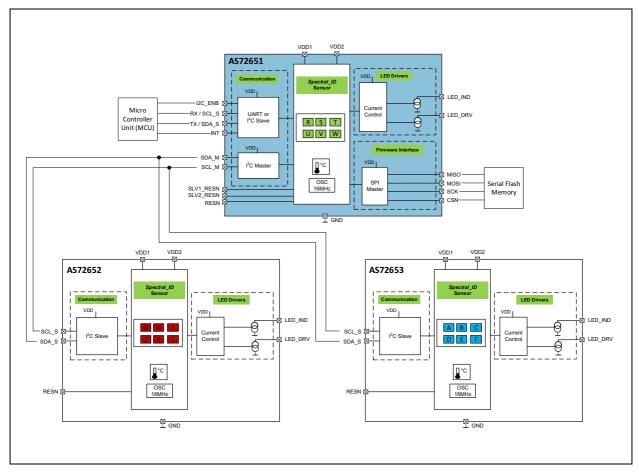

## **Block Diagram**

The functional blocks of this device are shown below:

#### Note(s):

1. Refer to the Application Diagram in Figure 60.

## **Pin Assignments**

#### The device pin assignments are described below.

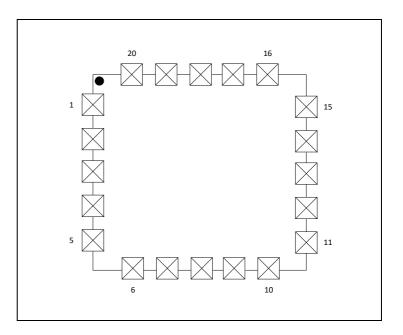

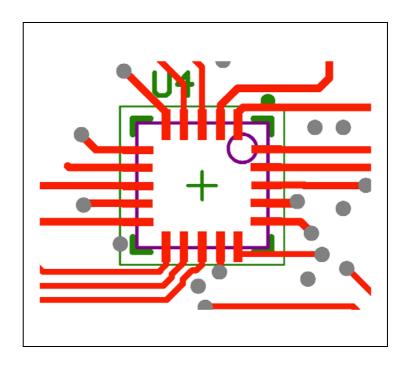

Figure 3: Pin Diagram of AS7265x (Top View)

#### Figure 4: AS72651 Pin Description

| Pin No. | Pin Name  | Pin Type                 | Description                                                              |

|---------|-----------|--------------------------|--------------------------------------------------------------------------|

| 1       | SLV1_RESN | Digital Input and Output | Reset pin for Slave 1 e.g. AS72652, active low                           |

| 2       | RESN      | Digital Input            | Reset pin, active low (with internal pull-up to VDD)                     |

| 3       | SCK       | Digital Output           | SPI serial clock                                                         |

| 4       | MOSI      | Digital Input and Output | SPI MOSI                                                                 |

| 5       | MISO      | Digital Input and Output | SPI MISO                                                                 |

| 6       | CSN       | Digital Output           | Chip select for external flash                                           |

| 7       | NC        |                          | Not functional, no connect                                               |

| 8       | I2C_ENB   | Digital Input            | Selects UART (low) or I <sup>2</sup> C (high) operation                  |

| 9       | SCL_M     | Digital Output           | I <sup>2</sup> C master clock for communication with AS72652 and AS72653 |

| 10      | SDA_M     | Digital Input and Output | I <sup>2</sup> C master data for communication with AS72652 and AS72653  |

| Pin No. | Pin Name   | Pin Type                 | Description                                                              |

|---------|------------|--------------------------|--------------------------------------------------------------------------|

| 11      | RX / SCL_S | Digital Input and Output | RX (UART) or SCL_S (I <sup>2</sup> C slave) depending on I2C_ENB setting |

| 12      | TX / SDA_S | Digital Input and Output | TX (UART) or SDA_S (I <sup>2</sup> C slave) depending on I2C_ENB setting |

| 13      | INT        | Digital Output           | INT is active low                                                        |

| 14      | VDD2       | Voltage Supply           | Voltage supply                                                           |

| 15      | LED_DRV    | Analog Output            | LED driver output for driver LED, current sink                           |

| 16      | GND        | Supply                   | Ground                                                                   |

| 17      | VDD1       | Voltage Supply           | Voltage supply                                                           |

| 18      | LED_IND    | Analog Output            | LED driver output for indicator LED, current sink                        |

| 19      | NC         |                          | Not functional, no connect                                               |

| 20      | SLV2_RESN  | Digital Output           | Reset pin for slave 2 e.g. AS72653, active low                           |

#### Note(s):

1. Pin out is valid for firmware versions from 11 and later.

Figure 5: AS72652 and AS72653 Pin Description

| Pin No. | Pin Name | Pin Type                 | Description                                                           |

|---------|----------|--------------------------|-----------------------------------------------------------------------|

| 1       | NC       |                          | Not functional, no connect                                            |

| 2       | RESN     | Digital Input            | Reset pin, active low (with internal pull-up to VDD)                  |

| 3       | NC       |                          | Not functional, no connect                                            |

| 4       | NC       |                          | Not functional, no connect                                            |

| 5       | NC       |                          | Not functional, no connect                                            |

| 6       | NC       |                          | Not functional, no connect                                            |

| 7       | NC       |                          | Not functional, no connect                                            |

| 8       | NC       |                          | Not functional, no connect                                            |

| 9       | SCL_S    | Digital Input and Output | I <sup>2</sup> C slave clock for communication with master<br>AS72651 |

| 10      | SDA_S    | Digital Input and Output | I <sup>2</sup> C slave data for communication with master<br>AS72651  |

| Pin No. | Pin Name | Pin Type       | Description                                       |

|---------|----------|----------------|---------------------------------------------------|

| 11      | NC       |                | Not functional, no connect                        |

| 12      | NC       |                | Not functional, no connect                        |

| 13      | INT      | Digital Output | INT is active low                                 |

| 14      | VDD2     | Voltage Supply | Voltage supply                                    |

| 15      | LED_DRV  | Analog Output  | LED driver output for driver LED, current sink    |

| 16      | GND      | Supply         | Ground                                            |

| 17      | VDD1     | Voltage Supply | Voltage supply                                    |

| 18      | LED_IND  | Analog Output  | LED driver output for indicator LED, current sink |

| 19      | NC       |                | Not functional, no connect                        |

| 20      | NC       |                | Not functional, no connect                        |

## Absolute Maximum Ratings

Stresses beyond those listed under Absolute Maximum Ratings of AS7265x may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under Electrical Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. The device is not designed for high energy UV (ultraviolet) environments, including upward looking outdoor applications, which could affect long term optical performance.

## Figure 6:

Absolute Maximum Ratings of AS7265x

| Symbol               | Parameter                             | Min        | Max          | Unit     | Comments                                                                                                                                                                                                                                         |  |  |  |  |

|----------------------|---------------------------------------|------------|--------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                      | Elec                                  | ctrical Pa | rameters     |          |                                                                                                                                                                                                                                                  |  |  |  |  |

| V <sub>DD1_MAX</sub> | Supply Voltage VDD1                   | -0.3       | 5            | V        | Pin VDD1 to GND                                                                                                                                                                                                                                  |  |  |  |  |

| V <sub>DD2_MAX</sub> | Supply Voltage VDD2                   | -0.3       | 5            | V        | Pin VDD2 to GND                                                                                                                                                                                                                                  |  |  |  |  |

| V <sub>DD_IO</sub>   | Input/Output Pin Voltage              | -0.3       | VDD+0.3      | V        | Input/Output Pin to GND                                                                                                                                                                                                                          |  |  |  |  |

| I <sub>SCR</sub>     | Input Current (latch-up<br>immunity)  | 1          | - 100        | mA       | JESD78D                                                                                                                                                                                                                                          |  |  |  |  |

|                      | Electrostatic Discharge               |            |              |          |                                                                                                                                                                                                                                                  |  |  |  |  |

| ESD <sub>HBM</sub>   | Electrostatic Discharge HBM           | <u>+</u>   | 1000         | V        | JS-001-2014                                                                                                                                                                                                                                      |  |  |  |  |

| ESD <sub>CDM</sub>   | Electrostatic Discharge CDM           | -          | ±500         | V        | JESD22-C101F                                                                                                                                                                                                                                     |  |  |  |  |

|                      | Temperature Ra                        | anges an   | d Storage Co | nditions |                                                                                                                                                                                                                                                  |  |  |  |  |

| T <sub>STRG</sub>    | Storage Temperature Range             | -40        | 85           | °C       |                                                                                                                                                                                                                                                  |  |  |  |  |

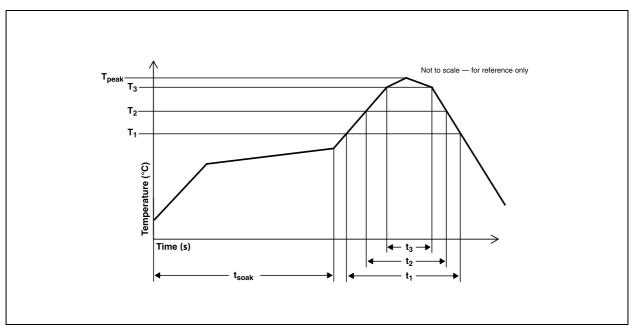

| T <sub>BODY</sub>    | Package Body Temperature              |            | 260          | °C       | IPC/JEDEC J-STD-020. The<br>reflow peak soldering<br>temperature (body<br>temperature) is specified<br>according IPC/JEDEC<br>J-STD-020 "Moisture/Reflow<br>Sensitivity Classification for<br>Non-hermetic Solid State<br>Surface Mount Devices" |  |  |  |  |

| RH <sub>NC</sub>     | Relative Humidity<br>(non-condensing) | 5          | 85           | %        |                                                                                                                                                                                                                                                  |  |  |  |  |

| MSL                  | Moisture Sensitivity Level            | 3          |              |          | Represents a 168 hour max.<br>floor lifetime                                                                                                                                                                                                     |  |  |  |  |

## **Electrical Characteristics**

All limits are guaranteed with VDD = VDD1 = VDD2 = 3.3V,  $T_{AMB} = 25^{\circ}$ C. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

VDD1 and VDD2 should be sourced from the same power supply output.

#### Figure 7: Electrical Characteristics of AS7265x

| Symbol                             | Parameter                                                       | Conditions                 | Min  | Тур | Max  | Unit |  |  |

|------------------------------------|-----------------------------------------------------------------|----------------------------|------|-----|------|------|--|--|

| General Operating Conditions       |                                                                 |                            |      |     |      |      |  |  |

| VDD1<br>/VDD2                      | Voltage Operating<br>Supply                                     | UART Interface             | 2.97 | 3.3 | 3.6  | v    |  |  |

| VDD1<br>/VDD2                      | Voltage Operating<br>Supply                                     | I <sup>2</sup> C Interface | 2.7  | 3.3 | 3.6  | V    |  |  |

| T <sub>AMB</sub>                   | Operating Temperature                                           |                            | -40  | 25  | 85   | °C   |  |  |

| I <sub>VDD</sub>                   | Operating Current                                               |                            |      |     | 5    | mA   |  |  |

|                                    |                                                                 | Internal RC Oscillator     |      |     |      |      |  |  |

| F <sub>OSC</sub>                   | Internal RC Oscillator<br>Frequency                             |                            | 15.7 | 16  | 16.3 | MHz  |  |  |

| t <sub>JITTER</sub> <sup>(1)</sup> | Internal Clock Jitter                                           | @25°C                      |      |     | 1.2  | ns   |  |  |

|                                    | •                                                               | Temperature Sensor         |      | 1   | I    |      |  |  |

| D <sub>TEMP</sub>                  | Absolute Accuracy of the<br>Internal Temperature<br>Measurement |                            | -8.5 |     | 8.5  | °C   |  |  |

|                                    |                                                                 | Indicator LED              |      | •   |      |      |  |  |

| I <sub>IND</sub>                   | LED Current                                                     |                            | 1    |     | 8    | mA   |  |  |

| I <sub>ACC</sub>                   | Accuracy of Current                                             |                            | -30  |     | 30   | %    |  |  |

| V <sub>LED</sub>                   | Voltage Range of<br>Connected LED                               | Vds of current sink        | 0.3  |     | VDD  | V    |  |  |

|                                    | LED_DRV                                                         |                            |      |     |      |      |  |  |

| I <sub>LED1</sub>                  | LED Current                                                     |                            | 12.5 |     | 100  | mA   |  |  |

| I <sub>ACC</sub>                   | Accuracy of Current                                             |                            | -10  |     | 10   | %    |  |  |

| V <sub>LED</sub>                   | Voltage Range of<br>Connected LED                               | Vds of current sink        | 0.3  |     | VDD  | V    |  |  |

| Symbol                            | Parameter                  | Conditions    | Min         | Тур | Мах         | Unit |  |  |  |

|-----------------------------------|----------------------------|---------------|-------------|-----|-------------|------|--|--|--|

|                                   | Digital Inputs and Outputs |               |             |     |             |      |  |  |  |

| I <sub>IH</sub> , I <sub>IL</sub> | Logic Input Current        | Vin=0V or VDD | -1          |     | 1           | μΑ   |  |  |  |

| V <sub>IH</sub>                   | CMOS Logic High Input      |               | 0.7*<br>VDD |     | VDD         | V    |  |  |  |

| V <sub>IL</sub>                   | CMOS Logic Low Input       |               | 0           |     | 0.3*<br>VDD | V    |  |  |  |

| V <sub>OH</sub>                   | CMOS Logic High Output     | I=1mA         |             |     | VDD-<br>0.4 | V    |  |  |  |

| V <sub>OL</sub>                   | CMOS Logic Low Output      | I=1mA         |             |     | 0.4         | V    |  |  |  |

| t <sub>RISE</sub> <sup>(1)</sup>  | Current Rise Time          | C(Pad)=30pF   |             |     | 5           | ns   |  |  |  |

| t <sub>FALL</sub> (1)             | Current Fall Time          | C(Pad)=30pF   |             |     | 5           | ns   |  |  |  |

#### Note(s):

1. Guaranteed by design, not tested in production.

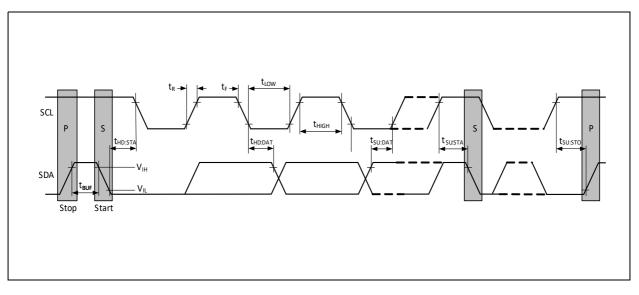

## **Timing Characteristics**

Figure 8: AS7265x I<sup>2</sup>C Slave Timing Characteristics

| Symbol                     | Parameter                              | Conditions                                         | Min | Тур | Max | Unit |  |  |

|----------------------------|----------------------------------------|----------------------------------------------------|-----|-----|-----|------|--|--|

| l <sup>2</sup> C Interface |                                        |                                                    |     |     |     |      |  |  |

| f <sub>SCLK</sub>          | SCL Clock Frequency                    |                                                    | 0   |     | 400 | kHz  |  |  |

| t <sub>BUF</sub>           | Bus Free Time Between a STOP and START |                                                    | 1.3 |     |     | μs   |  |  |

| t <sub>HS:STA</sub>        | Hold Time (Repeated) START             |                                                    | 0.6 |     |     | μs   |  |  |

| t <sub>LOW</sub>           | LOW Period of SCL Clock                |                                                    | 1.3 |     |     | μs   |  |  |

| t <sub>HIGH</sub>          | HIGH Period of SCL Clock               |                                                    | 0.6 |     |     | μs   |  |  |

| t <sub>SU:STA</sub>        | Setup Time for a Repeated START        |                                                    | 0.6 |     |     | μs   |  |  |

| t <sub>HS:DAT</sub>        | Data Hold Time                         |                                                    | 0   |     | 0.9 | μs   |  |  |

| t <sub>SU:DAT</sub>        | Data Setup Time                        |                                                    | 100 |     |     | ns   |  |  |

| t <sub>R</sub>             | Rise Time of Both SDA and SCL          |                                                    | 20  |     | 300 | ns   |  |  |

| t <sub>F</sub>             | Fall Time of Both SDA and SCL          |                                                    | 20  |     | 300 | ns   |  |  |

| t <sub>SU:STO</sub>        | Setup Time for STOP Condition          |                                                    | 0.6 |     |     | μs   |  |  |

| C <sub>B</sub>             | Capacitive Load for Each Bus Line      | CB - total<br>capacitance of one<br>bus line in pF |     |     | 400 | pF   |  |  |

| C <sub>I/O</sub>           | I/O Capacitance (SDA, SCL)             |                                                    |     |     | 10  | pF   |  |  |

#### Figure 9: I<sup>2</sup>C Slave Timing Diagram

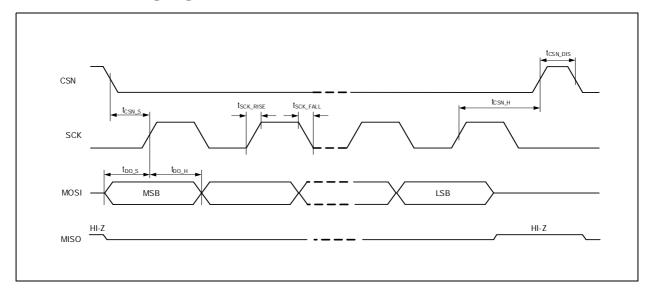

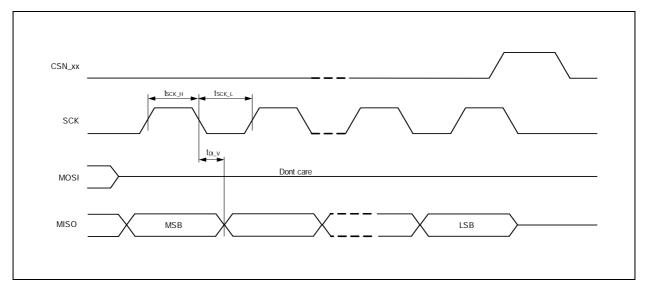

Figure 10: AS72651 SPI Timing Characteristics

| Symbol                | Parameter           | Conditions                                                              | Min | Тур | Max | Unit |  |  |  |

|-----------------------|---------------------|-------------------------------------------------------------------------|-----|-----|-----|------|--|--|--|

|                       | SPI Interface       |                                                                         |     |     |     |      |  |  |  |

| f <sub>SCK</sub>      | Clock Frequency     |                                                                         | 0   |     | 16  | MHz  |  |  |  |

| t <sub>SCK_H</sub>    | Clock High Time     |                                                                         | 40  |     |     | ns   |  |  |  |

| t <sub>SCK_L</sub>    | Clock Low Time      |                                                                         | 40  |     |     | ns   |  |  |  |

| t <sub>SCK_RISE</sub> | SCK Rise Time       |                                                                         | 5   |     |     | ns   |  |  |  |

| t <sub>SCK_FALL</sub> | SCK Fall Time       |                                                                         | 5   |     |     | ns   |  |  |  |

| t <sub>CSN_S</sub>    | CSN Setup Time      | Time between CSN high-low<br>transition to first SCK high<br>transition | 50  |     |     | ns   |  |  |  |

| t <sub>CSN_H</sub>    | CSN Hold Time       | Time between last SCK<br>falling edge and CSN<br>low-high transition    | 100 |     |     | ns   |  |  |  |

| t <sub>CSN_DIS</sub>  | CSN Disable Time    |                                                                         | 100 |     |     | ns   |  |  |  |

| t <sub>DO_S</sub>     | Data-Out Setup Time |                                                                         | 5   |     |     | ns   |  |  |  |

| t <sub>DO_H</sub>     | Data-Out Hold Time  |                                                                         | 5   |     |     | ns   |  |  |  |

| t <sub>DI_V</sub>     | Data-In Valid       |                                                                         | 10  |     |     | ns   |  |  |  |

dm

#### Figure 11: SPI Master Write Timing Diagram

Figure 12: SPI Master Read Timing Diagram

## Typical Operating Characteristics

## **Optical Characteristics**

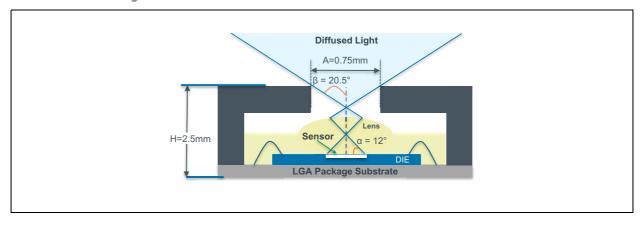

All optical characteristics are optimized for diffused light. When using a point light source or collimated light on the sensor, the sensor opening must be covered by a lambertian diffuser with achromatic characteristics. Diffusor of Tsujiden like D121UP have been successfully tested at **ams**. If in the application diffused light, e.g. used by a reflective surface, no additional diffuser is required.

Figure 13: AS7265x LGA Average Field of View

#### Figure 14: AS7265x 18-Channel Spectral Responsivity

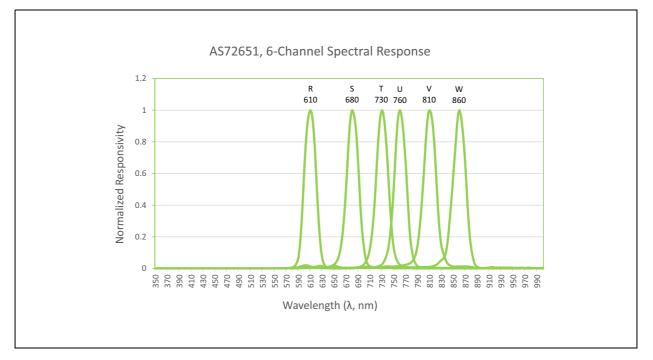

#### Figure 15: AS72651 Spectral Responsivity

#### Figure 16:

#### Optical Characteristics of AS72651 (Pass Band)<sup>(1)</sup>

| Symbol | Parameter              | Test Conditions                 | Channel<br>(nm) | Min | Тур                   | Max | Unit                             |

|--------|------------------------|---------------------------------|-----------------|-----|-----------------------|-----|----------------------------------|

| R      | Channel R              | Incandescent <sup>(2),(4)</sup> | 610             |     | 35 <sup>(3),(4)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| S      | Channel S              | Incandescent <sup>(2),(4)</sup> | 680             |     | 35 <sup>(3),(4)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| т      | Channel T              | Incandescent <sup>(2),(4)</sup> | 730             |     | 35 <sup>(3),(4)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| U      | Channel U              | Incandescent <sup>(2),(4)</sup> | 760             |     | 35 <sup>(3),(4)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| V      | Channel V              | Incandescent <sup>(2),(4)</sup> | 810             |     | 35 <sup>(3),(4)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| W      | Channel W              | Incandescent <sup>(2),(4)</sup> | 860             |     | 35 <sup>(3),(4)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| FWHM   | Full Width Half<br>Max |                                 |                 |     | 20                    |     | nm                               |

| Wacc   | Wavelength<br>Accuracy |                                 |                 | +10 |                       | -10 | nm                               |

| Symbol | Parameter                | Test Conditions                                               | Channel<br>(nm) | Min | Тур   | Max | Unit   |

|--------|--------------------------|---------------------------------------------------------------|-----------------|-----|-------|-----|--------|

| dark   | Dark Channel<br>Counts   | GAIN=64,<br>T <sub>AMB</sub> =25°C<br>t <sub>int</sub> =165ms |                 |     |       | 5   | counts |

| AFOV   | Average Field<br>of View |                                                               |                 |     | ±20.5 |     | deg    |

#### Note(s):

1. Calibration and measurements are made using diffused light.

2. Each channel is tested with GAIN = 16x, Integration Time (INT\_T) = 166ms and VDD = VDD1 = VDD2 = 3.3V,  $T_{AMB} = 25^{\circ}C$ .

3. The accuracy of the channel counts/ $\mu$ W/cm<sup>2</sup> is ±12%.

4. The light source is an incandescent light with an irradiance of  ${\sim}1500 \mu W/cm^2$  (300-1000nm).

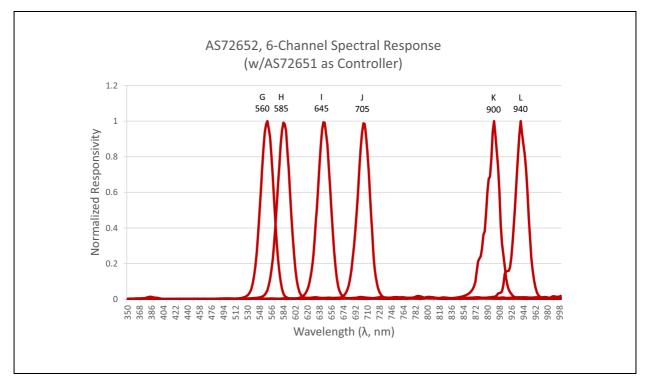

#### Figure 17: AS72652 Spectral Responsivity

### Figure 18:

Optical Characteristics of AS72652 (Pass Band)<sup>(1)</sup>

| Symbol | Parameter                 | Conditions                                                  | Channel<br>(nm) | Min | Тур               | Max | Unit                             |

|--------|---------------------------|-------------------------------------------------------------|-----------------|-----|-------------------|-----|----------------------------------|

| G      | Channel G                 | 3300K White LED <sup>(2)</sup>                              | 560             |     | 35 <sup>(3)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| н      | Channel H                 | 3300K White LED <sup>(2)</sup>                              | 585             |     | 35 <sup>(3)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| I      | Channel I                 | 3300K White LED <sup>(2)</sup>                              | 645             |     | 35 <sup>(3)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| J      | Channel J                 | 3300K White LED <sup>(2)</sup>                              | 705             |     | 35 <sup>(3)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| к      | Channel K                 | Incandescent <sup>(2)</sup>                                 | 900             |     | 35 <sup>(3)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| L      | Channel L                 | 940nm LED <sup>(2)</sup>                                    | 940             |     | 35 <sup>(3)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| FWHM   | Full Width<br>Half Max    |                                                             |                 |     | 20                |     | nm                               |

| Wacc   | Wavelength<br>Accuracy    |                                                             |                 | -10 |                   | +10 | nm                               |

| dark   | Dark<br>Channel<br>Counts | GAIN=64, T <sub>AMB</sub> =25°C<br>t <sub>int</sub> = 165ms |                 |     |                   | 5   | counts                           |

| AFOV   | Average<br>Field of View  |                                                             |                 |     | ±20.5             |     | deg                              |

#### Note(s):

1. Calibration and measurements are made using diffused light.

2. Each channel is tested with GAIN = 16x, Integration Time (INT\_T) = 166ms and VDD = VDD1 = VDD2 = 3.3V,  $T_{AMB} = 25^{\circ}C$ .

3. The accuracy of the channel counts/ $\mu$ W/cm<sup>2</sup> is ±12%.

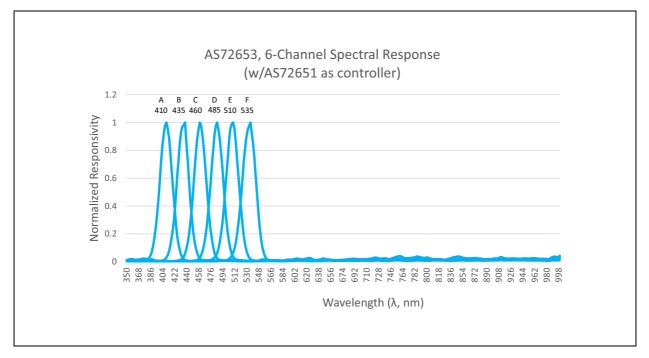

#### Figure 19: AS72653 Spectral Responsivity

#### Figure 20:

**Optical Characteristics of AS72653 (Pass Band)**<sup>(1)</sup>

| Symbol | Parameter                | Conditions                                                  | Channel<br>(nm) | Min | Тур               | Max | Unit                             |

|--------|--------------------------|-------------------------------------------------------------|-----------------|-----|-------------------|-----|----------------------------------|

| А      | Channel A                |                                                             | 410             |     | 35 <sup>(3)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| В      | Channel B                |                                                             | 435             |     | 35 <sup>(3)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| С      | Channel C                | LED: <sup>(2)</sup><br>395nm<br>415nm                       | 460             |     | 35 <sup>(3)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| D      | Channel D                | 4131111<br>428nm<br>5600K white                             | 485             |     | 35 <sup>(3)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| E      | Channel E                |                                                             | 510             |     | 35 <sup>(3)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| F      | Channel F                |                                                             | 535             |     | 35 <sup>(3)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| FWHM   | Full Width<br>Half Max   |                                                             |                 |     | 20                |     | nm                               |

| Wacc   | Wavelength<br>Accuracy   |                                                             |                 | -10 |                   | +10 | nm                               |

| dark   | Dark Channel<br>Counts   | GAIN=64, T <sub>AMB</sub> =25°C<br>t <sub>int</sub> = 165ms |                 |     |                   | 5   | counts                           |

| AFOV   | Average Field<br>of View |                                                             |                 |     | ±20.5             |     | deg                              |

#### Note(s):

1. Calibration and measurements are made using diffused light.

2. Each channel is tested with GAIN = 16x, Integration Time (INT\_T) = 166ms and VDD = VDD1 = VDD2 = 3.3V,  $T_{AMB} = 25^{\circ}C$ .

3. The accuracy of the channel counts/ $\mu\text{W/cm}^2$  is  $\pm 12\%$ .

## **Detailed Description**

## AS7265x 18-Channel *Spectral\_ID* Detector Overview

Each of the three AS7265x *Spectral\_ID* devices are next-generation digital 6-channel spectral sensor devices. Each of the 6 channels has a Gaussian filter characteristic with a full width half maximum (FWHM) bandwidth of 20nm. The filters use an interference topology design providing high stability in terms of drift in time and temperature. The drifts are so small that it is undetectable in the measurement. The temperature drift of the device is largely determined by the drift of the sensor and the electronics. To compensate for the temperature drift in the application, every device of the AS7265x chipset includes an integrated temperature sensor.

Filter accuracy will be affected by the angle of incidence which itself is limited by integrated aperture and internal micro-lens structure. The aperture-limited average field of view is  $\pm 20.5^{\circ}$ to deliver specified accuracy. All optical characteristics are optimized for using diffused light.

Each device contains an analog-to-digital converter (16-bit resolution ADC) which integrates the current from each channel's photodiode. Upon completion of the conversion cycle, the integrated result is transferred to the corresponding data registers. The transfers are double-buffered to ensure data integrity is maintained.

The external MCU interface control via  $l^2C$  registers or AT commands, transparently controls the AS72652 and/or AS72653.

A serial flash is a required operating companion for this device and enables factory calibration/normalization of the filters. Supported device types are noted in Ordering & Contact Information at the end of this document.

Required operating code can be downloaded at download.ams.com.

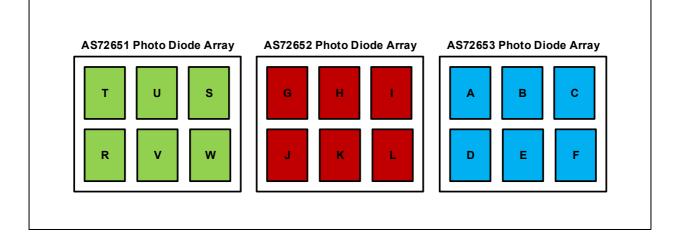

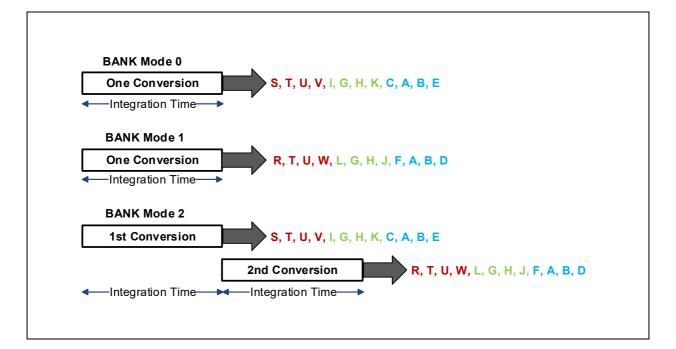

# Channel Data Conversion of the AS7265x Devices

All three of these 6 channel devices use conversion implemented via two photodiode banks in each device. Refer to Figure 21 and Figure 22. Bank 1 consists of register data from 4 of the 6 photodiodes, with 2 registers zeroed and Bank 2 consists of data from a different set of 4 of the 6 photodiodes, with 2 different registers zeroed. Spectral conversion requires the integration time (IT in ms) set to complete. If both photodiode banks are required to complete the conversion, the 2<sup>nd</sup> bank requires an additional IT ms. Minimum IT for a single bank conversion is 2.8 ms. If data is required from all 6 photodiodes then the device must perform 2 full conversions (2 x Integration Time).

This spectral data conversion process operates continuously, new data is available after each IT ms period.

The conversion process is controlled with BANK Mode settings in the AS72651 as follows:

#### BANK Mode 0 Registers:

AS72651 data will be in S, T, U & V registers (R & W will be zero) AS72652 data will be in G, H, K & I registers (J & L will be zero) AS72653 data will be in A, B, E & C registers (D & F will be zero)

#### **BANK Mode 1 Registers:**

AS72651 data will be in R, T, U & W registers (S & V will be zero) AS72652 data will be in G, H, J & L registers (I & K will be zero) AS72653 data will be in F, A, B & D registers (C & E will be zero)

#### BANK Mode 2 Registers:

AS72651 data will be in S, T, U, V, R & W registers

AS72652 data will be in G, H, K, I, J & L registers

AS72653 data will be in A, B, C, D, E & F registers

For BANK Mode 2, care should be taken to assure prompt interrupt servicing so integration values from both banks are all derived from the same spectral conversion cycle.

Figure 21: AS7265x Photo Diode Arrays

#### Figure 22: Bank Mode and Data Conversion

## **RC Oscillator**

The timing generation circuit consists of on-chip 16MHz, temperature compensated oscillators, which provide the individual master clocks of the AS7625x devices

#### **Temperature Sensor**

The AS7265x internal temperature sensors are constantly measuring on-chip temperature to enable temperature compensation procedures, and can be read via I<sup>2</sup>C registers or AT commands in the AS72651.

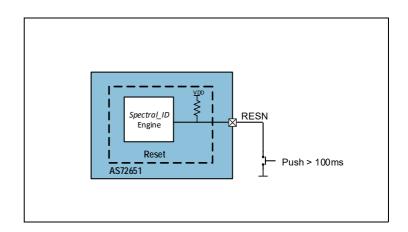

#### Reset

Pulling down the RESN pin for longer than 100ms resets the AS72651 which proceed to reset the AS72562 and the same RESN signal shown below can be used directly to reset the AS72653.

Figure 23: Reset Circuit

## AS7265x LED\_IND Controls

There are LED\_IND pins on all AS7265x devices. An LED connected to LED\_IND can be used as a general power indicator and will automatically be used to indicate a Flash firmware update is occurring.

The LED\_IND can then be setup as needed. Each AS7265x LED\_IND source can be turned on/off via AT commands or I<sup>2</sup>C register control, and LED\_IND sink current is programmable to 1mA, 2mA, 4mA or 8mA. This LED\_IND control can also be used in applications just like the LED\_DRV control (described below), if the lower current sink of the LED\_IND control is appropriate.

## Electronic Shutter with AS7265x LED\_DRV Driver Control

There are LED\_DRV pins on all AS7265x devices. The LED\_DRV pin can be used to control external LED sources as needed for sensor applications. LED\_DRV can sink a programmable current of 12.5mA, 25mA, 50mA or 100mA. The control can be turned on/off via I<sup>2</sup>C registers or AT commands, and as such it provides the AS7265x device with an electronic shutter.

#### **Interrupt Operation**

Interrupt operation is only needed for AS72651 as it transparently controls data collection from the AS72652 (if used) or AS72653 (if used). If BANK is set in the AS72651 to Mode 0 or Mode 1, data is ready after the 1<sup>st</sup> integration time. If BANK is set to Mode 2, data is ready after two integration times.

For interrupt operation using I<sup>2</sup>C registers, if interrupts are enabled and data is ready, the INT pin is set low and DATA\_RDY is set to 1. Reading the raw or calibration data releases (returns high) the interrupt. For multi-byte sensor data (2 or 4 bytes), after the 1st byte is read the remaining bytes are shadow protected in case an integration cycle completes just after the 1st byte is read. The sensors continue to gather information at the rate of the integration time, hence if the sensor registers are not read when the interrupt line goes low, it will stay low and the next cycle's sensor data will be available in the registers at the end of the next integration cycle.

For interrupt operation using AT Commands, if interrupts are enabled and data is ready the INT pin is set low and is released (returns high) after any sensor data is read.

#### **Required Flash Memory**

Serial flash is a required operating companion for this device, and enables the I<sup>2</sup>C and UART interfaces, as well as enabling calibrated data results. Supported device types are noted in Ordering & Contact Information at the end of this document. Required operating code can be downloaded at download.ams.com.

## I<sup>2</sup>C Slave Interface

If selected by the I2C\_ENB pin setting, interface and control can be accomplished through an I<sup>2</sup>C compatible slave interface to a set of registers that provide access to device control functions and output data. These registers on the AS72651 are, in reality, implemented as *virtual* registers in software. The actual I<sup>2</sup>C slave hardware registers number only three and are described in the table below. The steps necessary to access the virtual registers defined in the following are explained in pseudocode for external I<sup>2</sup>C master writes and reads below.

#### I<sup>2</sup>C Feature List

- Fast mode (400kHz).

- 7+1-bit addressing mode.

- Write format: Byte.

- Read format: Byte.

- SDA input delay and SCL spike filtering by integrated RC-components.

#### Figure 24:

I<sup>2</sup>C Slave Device Address and Physical Registers

| Entity               | Description                                                     | Note                                                                                                                                                                                                                                                                                                                |

|----------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device Slave Address | 8-bit slave address                                             | <ul> <li>Byte = 1001001x (device address = 49 hex)</li> <li>x = 1 for Master Read (byte = 93 hex)</li> <li>x = 0 for Master Write (byte = 92 hex)</li> </ul>                                                                                                                                                        |

| STATUS Register      | l <sup>2</sup> C slave interface STATUS<br>register. Read-only. | <ul> <li>Register Address = 0x00</li> <li>Bit 1: TX_VALID</li> <li>0 - New data may be written to WRITE register</li> <li>1 -WRITE register occupied. Do NOT write.</li> <li>Bit 0: RX_VALID</li> <li>0 -No data is ready to be read in READ register.</li> <li>1 -Data byte available in READ register.</li> </ul> |

| WRITE Register       | l <sup>2</sup> C slave interface WRITE<br>register. Write-only. | <ul> <li>Register Address = 0x01</li> <li>8-Bits of data written by the l<sup>2</sup>C Master intended for receipt by the l<sup>2</sup>C slave. Used for both <i>virtual</i> register addresses and write data.</li> </ul>                                                                                          |

| READ Register        | l <sup>2</sup> C slave interface<br>READ register. Read-only.   | Register Address = 0x02<br>• 8-Bits of data to be read by the I <sup>2</sup> C Master.                                                                                                                                                                                                                              |

## I<sup>2</sup>C Virtual Register Write Access

I<sup>2</sup>C Virtual Resister Byte Write, detailed below, shows the pseudocode necessary to write virtual registers on the AS72651. Note that, because the actual registers of interest are realized as virtual registers, a means of indicating whether there is a pending read or write operation of a given virtual register is needed. To convey this information, the most significant bit of the virtual register address is used as a marker. If it is 1, then a write is pending, otherwise the slave is expecting a virtual read operation. The pseudocode illustrates the proper technique for polling of the I<sup>2</sup>C slave status register to ensure the slave is ready for each transaction.

#### I<sup>2</sup>C Virtual Register Byte Write

#### Pseudocode

Poll I<sup>2</sup>C slave STATUS register;

If TX\_VALID bit is 0, a write can be performed on the interface;

Send a virtual register address and set the MSB of the register address to 1 to indicate the pending write;

Poll I<sup>2</sup>C slave STATUS register;

If TX\_VALID bit is 0, the virtual register address for the write has been received and the data may now be written; Write the data.

#### Sample Code:

| #define I2C_AS72XX_SLAVE_STATUS_REG | 0x00 |

|-------------------------------------|------|

| #define I2C_AS72XX_SLAVE_WRITE_REG  | 0x01 |

| #define I2C_AS72XX_SLAVE_READ_REG   | 0x02 |

| #define I2C_AS72XX_SLAVE_TX_VALID   | 0x02 |

| #define I2C_AS72XX_SLAVE_RX_VALID   | 0x01 |

```

void i2cm_AS72xx_write(uint8_t virtualReg, uint8_t d)

```

```

{

```

volatile uint8\_tstatus;

```

while (1)

```

```

{

```

// Read slave l<sup>2</sup>C status to see if the write buffer is ready.

status = i2cm\_read(I2C\_AS72XX\_SLAVE\_STATUS\_REG);

```

if ((status & I2C_AS72XX_SLAVE_TX_VALID) == 0)

```

// No inbound TX pending at slave. Okay to write now.

break ;

#### }

// Send the virtual register address (enabling bit 7 to indicate a write).

i2cm\_write(I2C\_AS72XX\_SLAVE\_WRITE\_REG, (virtualReg | 0x80));

```

while (1)

```

```

{

```

// Read the slave I<sup>2</sup>C status to see if the write buffer is ready.

status = i2cm\_read(I2C\_AS72XX\_SLAVE\_STATUS\_REG);

```

if ((status & I2C_AS72XX_SLAVE_TX_VALID) == 0)

```

// No inbound TX pending at slave. Okay to write data now.

break;

#### }

// Send the data to complete the operation.

i2cm\_write(I2C\_AS72XX\_SLAVE\_WRITE\_REG, d);

```

}

```

I<sup>2</sup>C Virtual Register Read access

ams Datasheet [v1-04] 2018-Jul-09

I<sup>2</sup>C Virtual Register Byte Read, detailed below, shows the pseudocode necessary to read virtual registers on the AS72651. Note that in this case, reading a virtual register, the register address is not modified.

#### I<sup>2</sup>C Virtual Register Byte Read

Pseudocode

Poll I<sup>2</sup>C slave STATUS register;

If TX\_VALID bit is 0, the virtual register address for the read may be written;

Send a virtual register address;

Poll I<sup>2</sup>C slave STATUS register;

If RX\_VALID bit is 1, the read data is ready;

Read the data.

#### Sample Code

```

uint8_t i2cm_AS72xx_read(uint8_t virtualReg)

```

#### {

volatile uint8\_t status, d;

while (1)

#### {

// Read slave l<sup>2</sup>C status to see if the read buffer is ready.

status = i2cm\_read(l2C\_AS72XX\_SLAVE\_STATUS\_REG);

```

if ((status & I2C_AS72XX_SLAVE_TX_VALID) == 0)

// No inbound TX pending at slave. Okay to write now.

break;

```

#### }

// Send the virtual register address (disabling bit 7 to indicate a read).

i2cm\_write(I2C\_AS72XX\_SLAVE\_WRITE\_REG, virtualReg);

```

while (1)

```

{

// Read the slave l<sup>2</sup>C status to see if our read data is available.

status = i2cm\_read(l2C\_AS72XX\_SLAVE\_STATUS\_REG);

```

if ((status & I2C_AS72XX_SLAVE_RX_VALID)!= 0) // Read data is ready.

```

break;

}

```

// Read the data to complete the operation.

d = i2cm_read(I2C_AS72XX_SLAVE_READ_REG);

return d:s

```

}

The details of the i2cm\_read() and i2cm\_write() functions in previous figures are dependent upon the nature and implementation of the external I<sup>2</sup>C master device.

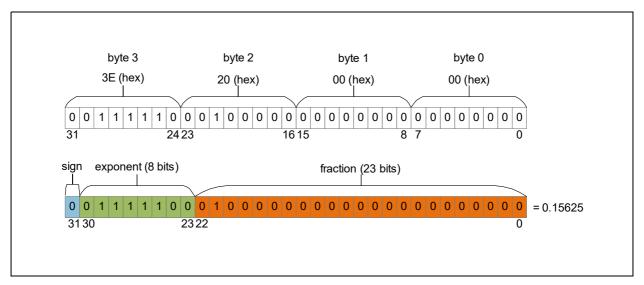

## 4-Byte Floating-Point (FP) Registers

Several 4 byte registers (hex) are used by the AS72651. Here is an example of how these registers are used to represent floating point data (based on the IEEE 754 standard).

#### Figure 25: Example of the IEEE 754 Standard

The floating point (FP) value assumed by 32 bit **binary32 data** with a biased exponent **e** (the 8 bit unsigned integer) and a **23 bit fraction** is (for the above example):

(EQ1) FPvalue =

$$(-1)^{sign} \cdot \left(1 + \sum_{i=1}^{23} b_{23-i} \cdot 2^{-i}\right) \cdot 2^{(e-127)}$$

FPvalue =

$$(-1)^{0} \cdot \left(1 + \sum_{i=1}^{23} b_{23-i} \cdot 2^{-i}\right) \cdot 2^{(124 - 127)}$$

FPvalue =

$$1 \cdot (1 + 2^{-2}) \cdot 2^{-3} = 0.15625$$

## I<sup>2</sup>C Virtual Register Set

The figure below provides a summary of the AS72651 I<sup>2</sup>C register set for the AS72651 which serves as the master interface of the 3 device AS7265x set. Figures after that provide additional register details. All register data is hex, and all multi-byte entities are Big Endian (most significant byte is situated at the lowest register address).

Multiple byte registers (2 byte integer, or, 4 byte floating point) must be read in the order of ascending register addresses (low to high) and if capable of being written to, must also be written in the order ascending register addresses.

Figure 26: AS72651 I<sup>2</sup>C Master Device Virtual Register Set Overview

| Addr | Name                 | <d7></d7>    | <d6></d6>    | <d5></d5>   | <d4></d4> | <d3></d3>              | <d2></d2> | <d1></d1> | <d0></d0>              |

|------|----------------------|--------------|--------------|-------------|-----------|------------------------|-----------|-----------|------------------------|

| 0x00 | HW Version           |              | HW Version H |             |           |                        |           |           |                        |

| 0x01 |                      |              | HW Version L |             |           |                        |           |           |                        |

| 0x02 | FW Version           |              |              |             | FW Ve     | rsion H                |           |           |                        |

| 0x03 |                      |              |              |             | FW Ve     | rsion L                |           |           |                        |

| 0x04 | Configuration        | SRST         | I            | NT          | GAIN      | BANK                   | DATA      | _RDY      | FRST                   |

| 0x05 | Integration Time     |              |              |             | Integrat  | ion Time               |           |           |                        |

| 0x06 | Temperature          |              |              |             | Tempe     | erature                |           |           |                        |

| 0x07 | LED<br>Configuration | READ_<br>ERR |              | LED_<br>DRV |           | ENA-<br>BLELED<br>_DRV | LED.      | _INT      | ENABL<br>E LED_<br>INT |

| 0x08 | RAW value R, G, A    |              |              |             | RAW v     | alue H                 |           |           |                        |

| 0x09 | RAW value R, G, A    |              |              |             | RAW       | /alue L                |           |           |                        |

| 0x0A | RAW value S, H, B    |              |              |             | RAW       | alue H                 |           |           |                        |

| 0x0B | RAW value S, H, B    |              |              |             | RAW       | /alue L                |           |           |                        |

| 0x0C | RAW value T, I, C    |              |              |             | RAW       | alue H                 |           |           |                        |

| 0x0D | RAW value T, I, C    |              |              |             | RAW       | /alue L                |           |           |                        |

| 0x0E | RAW value U, J, D    |              |              |             | RAW       | alue H                 |           |           |                        |

| 0x0F | RAW value U, J, D    | RAW value L  |              |             |           |                        |           |           |                        |

| 0x10 | RAW value V, K, E    | RAW value H  |              |             |           |                        |           |           |                        |

| 0x11 | RAW value V, K, E    | RAW value L  |              |             |           |                        |           |           |                        |

| 0x12 | RAW value W, L, F    | RAW value H  |              |             |           |                        |           |           |                        |

| 0x13 | RAW value W, L, F    |              |              |             | RAW       | /alue L                |           |           |                        |

| Addr | Name                                | <d7></d7>   | <d6></d6>   | <d5></d5> | <d4></d4> | <d3></d3> | <d2></d2> | <d1></d1> | <d0></d0> |

|------|-------------------------------------|-------------|-------------|-----------|-----------|-----------|-----------|-----------|-----------|

| 0x14 | Calibrated value<br>channel R, G, A |             |             |           | CAL CH    | IAN0_0    | -         |           |           |

| 0x15 | Calibrated value<br>channel R, G, A | CAL CHAN0_1 |             |           |           |           |           |           |           |

| 0x16 | Calibrated value<br>channel R, G, A |             | CAL CHAN0_2 |           |           |           |           |           |           |

| 0x17 | Calibrated value<br>channel R, G, A |             |             |           | CAL CH    | IAN0_3    |           |           |           |

| 0x18 | Calibrated value channel S, H, B    |             |             |           | CAL CH    | IAN0_0    |           |           |           |

| 0x19 | Calibrated value channel S, H, B    |             |             |           | CAL CH    | IAN0_1    |           |           |           |

| 0x1A | Calibrated value channel S, H, B    |             |             |           | CAL CH    | IAN0_2    |           |           |           |

| 0x1B | Calibrated value channel S, H, B    |             |             |           | CAL CH    | IAN0_3    |           |           |           |

| 0x1C | Calibrated value<br>channel T, I, C |             |             |           | CAL CH    | IAN0_0    |           |           |           |

| 0x1D | Calibrated value<br>channel T, I, C |             |             |           | CAL CH    | IAN0_1    |           |           |           |

| 0x1E | Calibrated value<br>channel T, I, C |             |             |           | CAL CH    | IAN0_2    |           |           |           |

| 0x1F | Calibrated value<br>channel T, I, C |             |             |           | CAL CH    | IAN0_3    |           |           |           |

| 0x20 | Calibrated value<br>channel U, J, D |             |             |           | CAL CH    | IAN0_0    |           |           |           |

| 0x21 | Calibrated value<br>channel U, J, D |             |             |           | CAL CH    | IAN0_1    |           |           |           |

| 0x22 | Calibrated value<br>channel U, J, D |             |             |           | CAL CH    | IAN0_2    |           |           |           |

| 0x23 | Calibrated value<br>channel U, J, D |             | CAL CHAN0_3 |           |           |           |           |           |           |

| 0x24 | Calibrated value<br>channel V, K, E |             |             |           | CAL CH    | IAN0_0    |           |           |           |

| 0x25 | Calibrated value<br>channel V, K, E | CAL CHAN0_1 |             |           |           |           |           |           |           |

| 0x26 | Calibrated value<br>channel V, K, E |             |             |           | CAL CH    | IAN0_2    |           |           |           |

| Addr | Name                                | <d7></d7>   | <d6></d6> | <d5></d5>                 | <d4></d4>      | <d3></d3>  | <d2></d2> | <d1></d1> | <d0></d0>  |

|------|-------------------------------------|-------------|-----------|---------------------------|----------------|------------|-----------|-----------|------------|

| 0x27 | Calibrated value<br>channel V, K, E | CAL CHAN0_3 |           |                           |                |            |           |           |            |

| 0x28 | Calibrated value<br>channel W, L, F |             |           |                           | CAL CH         | IAN0_0     |           |           |            |

| 0x29 | Calibrated value<br>channel W, L, F |             |           |                           | CAL CH         | IAN0_1     |           |           |            |

| 0x2A | Calibrated value<br>channel W, L, F |             |           |                           | CAL CH         | IAN0_2     |           |           |            |

| 0x2B | Calibrated value<br>channel W, L, F |             |           |                           | CAL CH         | IAN0_3     |           |           |            |

| 0x48 | FW control                          | START       | STOP      | BYTES_<br>TRANSF<br>ERRED | LOCK           | SWITC<br>H | BANK1     | ERROR     | CHKSU<br>M |

| 0x49 | FW byte count                       |             |           |                           | FW_BYTE_       | _COUNT_H   |           |           |            |

| 0x4A | FW byte count                       |             |           |                           | FW_BYTE_       | _COUNT_L   |           |           |            |

| 0x4B | FW payload                          |             |           |                           | HW ve          | rsion H    |           |           |            |

| 0x4F | DEV SEL                             |             |           | Second<br>Slave           | First<br>Slave |            |           | SELEC     | T DATA     |

| 0x50 | COEF DATA                           |             |           |                           | COEF_I         | DATA_0     |           |           |            |

| 0x51 | COEF DATA                           |             |           |                           | COEF_I         | DATA_1     |           |           |            |

| 0x52 | COEF DATA                           | COEF_DATA_2 |           |                           |                |            |           |           |            |

| 0x53 | COEF DATA                           | COEF_DATA_3 |           |                           |                |            |           |           |            |

| 0x54 | COEF READ                           |             | COEF_READ |                           |                |            |           |           |            |

| 0x55 | COEF WRITE                          |             |           |                           | COEF_          | WRITE      |           |           |            |

## **Detailed Register Descriptions**

#### Figure 27: HW Version Registers

| Addr: | 0x00,0x01    |         |        | HW Version      |

|-------|--------------|---------|--------|-----------------|

| Bit   | Bit Name     | Default | Access | Bit Description |

| 15:8  | HW version H | 0x40    | R      | Device type     |

| 7:0   | HW version L | 0x41    | R      | HW version      |

Figure 28: FW Version Registers

| Addr: | 0x02,0x03    |         |        | FW Version                                                                          |

|-------|--------------|---------|--------|-------------------------------------------------------------------------------------|

| Bit   | Bit Name     | Default | Access | Bit Description                                                                     |

| 15:8  | FW version H | 0       | R/W    | Set register 0x02, 0x03 to 0x01 to 0x03 to get each firmware positions high byte    |

| 7:0   | FW version L | 0       | R/W    | 0x01: MAJOR version [158]<br>0x02: PATCH version [158]<br>0x03: BUILD version [158] |

Figure 29: Configuration Register

| Ado | dr: 0x04 |         |        | Configuration                                                                                                                                   |

|-----|----------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name | Default | Access | Bit Description                                                                                                                                 |

| 7:0 | SRST     | 0       | W      | [W] software reset [R] gain error                                                                                                               |

| 6   | INT      | 0       | R/W    | Enable interrupt pin                                                                                                                            |

| 5:4 | GAIN     | 01      | R/W    | Gain configuration: b00=1x; b01=3.7x; b10=16x;<br>b11=64x                                                                                       |

| 3:2 | BANK     | 10      | R/W    | Measurement mode:<br>b00=Mode 0: 4 channels<br>b01=Mode 1: 4 channels<br>b10=Mode 2: All 6 channels<br>b11=Mode 3: One-Shot operation of mode 2 |

| 1   | DATA_RDY | 0       | R      | Data ready to read                                                                                                                              |

| 0   | FRST     | 0       | W      | Factory reset                                                                                                                                   |

The maximum sensitivity value depends on the integration time. For every 2.78ms of integration time, the maximum sensitivity value increases by 1024 counts. This means that to be able to reach the full sensitivity scale, the sensitivity has to be at least 64\*2.78ms.

Figure 30: Integration Time Register

| Ą   | Addr: 0x05           |         |        |                                                 | Integration Time      |                     |                         |        |      |

|-----|----------------------|---------|--------|-------------------------------------------------|-----------------------|---------------------|-------------------------|--------|------|

| Bit | Bit Name             | Default | Access |                                                 | Bit Description       |                     |                         |        |      |

|     |                      |         | -      | n time = <value<br>; value: 1-255;Re</value<br> |                       |                     |                         |        |      |

|     |                      |         |        | Value                                           | Integration<br>Cycles | Integration<br>Time | Maximum<br>ADC<br>Value |        |      |

|     |                      |         |        |                                                 | 0x00                  | 1                   | 2.78ms                  | 1023   |      |

| 7:0 | INTEGRATION_<br>TIME | 20      | R/W    | R/W                                             | R/W                   | 0x01                | 2                       | 5.56ms | 2047 |

|     |                      |         |        |                                                 |                       |                     |                         |        |      |

|     |                      |         |        | 0x11                                            | 18                    | 50ms                | 18431                   |        |      |

|     |                      |         |        | 0x40                                            | 65                    | 181ms               | 65535                   |        |      |

|     |                      |         |        |                                                 |                       |                     |                         |        |      |

|     |                      |         |        | 0xFF                                            | 256                   | 711ms               | 65535                   |        |      |

Figure 31: Temperature Register

| Ad  | dr: 0x06    |         |        | Temperature                                                                                                                                          |

|-----|-------------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name    | Default | Access | Bit Description                                                                                                                                      |

| 7:0 | Temperature | -       | R      | Temperature of the device in °C<br>Read value from every device in dependency of<br>register DEV_SEL<br>From -127 to 127<br>Return -128: Means error |

#### Figure 32: LED Configuration Register

| Ade | dr: 0x07           |         |        | LED Configuration                                                                                         |

|-----|--------------------|---------|--------|-----------------------------------------------------------------------------------------------------------|

| Bit | Bit Name           | Default | Access | Bit Description                                                                                           |

| 7   | READ_ERR           | 0       | R      | Error while reading status                                                                                |

| 5:4 | LED_DRV            | 00      | R/W    | LED_DRV current limit: b00=12.5mA; b01=25mA;<br>b10=50mA; b11=100mA<br>Device depends on register DEV_SEL |

| 3   | ENABLE LED_<br>DRV | 0       | R/W    | Enable LED DRV<br>Device depends on register DEV_SEL                                                      |

| 2:1 | LED_INT            | 01      | R/W    | Current limit: b00=1mA; b01=2mA; b10=4mA;<br>b11=8mA<br>Device depends on register DEV_SEL                |

| 0   | ENABLE LED_<br>INT | 0       | R/W    | Enable LED IND<br>Device depends on register DEV_SEL                                                      |

Figure 33: RAW Value Channel R,G,A Register

| Addr: 0x08,0x09 |             |         | RAW Value Channel R,G,A |                                                 |  |

|-----------------|-------------|---------|-------------------------|-------------------------------------------------|--|

| Bit             | Bit Name    | Default | Access                  | Bit Description                                 |  |

| 15:8            | RAW value H | -       | R                       | Channel R or J or D depends on register DEV_SEL |  |

| 7:0             | Raw value L | -       | R                       |                                                 |  |

Figure 34: RAW Value Channel S,H,B Register

| Addr: 0x0A,0x0B |             |         | RAW Value Channel S,H,B |                                                 |  |

|-----------------|-------------|---------|-------------------------|-------------------------------------------------|--|

| Bit             | Bit Name    | Default | Access                  | Bit Description                                 |  |

| 15:8            | RAW value H | -       | R                       | Channel S or I or C depends on register DEV_SEL |  |

| 7:0             | Raw value L | -       | R                       |                                                 |  |

#### Figure 35: RAW Value Channel T,I,C Register

| Addr: 0x0C/0x0D |             |         | RAW Value Channel T,I,C |                                              |  |

|-----------------|-------------|---------|-------------------------|----------------------------------------------|--|

| Bit             | Bit Name    | Default | Access                  | Bit Description                              |  |

| 15:8            | RAW value H | -       | R                       | Channel T or G or A depends on register DEV_ |  |

| 7:0             | Raw value L | -       | R                       | SEL                                          |  |

Figure 36:

RAW Value Channel U,J,D Register

| Addr: 0x0E,0x0F |             |         | RAW Value Channel U,J,D |                                              |  |

|-----------------|-------------|---------|-------------------------|----------------------------------------------|--|

| Bit             | Bit Name    | Default | Access                  | Bit Description                              |  |

| 15:8            | RAW value H | -       | R                       | Channel U or H or B depends on register DEV_ |  |

| 7:0             | Raw value L | -       | R                       | SEL                                          |  |

Figure 37: RAW Value Channel V,K,E Register

| Addr: 0x10,0x011 |             |         | RAW Value Channel V,K,E |                                                 |  |

|------------------|-------------|---------|-------------------------|-------------------------------------------------|--|

| Bit              | Bit Name    | Default | Access                  | Bit Description                                 |  |

| 15:8             | RAW value H | -       | R                       | Channel V or K or E depends on register DEV_SEL |  |

| 7:0              | Raw value L | -       | R                       |                                                 |  |

Figure 38:

RAW Value Channel W,L,F Register

| Addr: 0x12,0x013 |             | RAW Value Channel W,L,F |        |                                              |  |

|------------------|-------------|-------------------------|--------|----------------------------------------------|--|

| Bit              | Bit Name    | Default                 | Access | Bit Description                              |  |

| 15:8             | RAW value H | -                       | R      | Channel W or L or F depends on register DEV_ |  |

| 7:0              | Raw value L | -                       | R      | SEL                                          |  |

#### Figure 39: Calibrated Value Channel R,G,A Register

| Addr:<br>0x17,0x016,0x15,0x014 |             | Calibrated Value Channel R,G,A |        |                                              |  |

|--------------------------------|-------------|--------------------------------|--------|----------------------------------------------|--|

| Bit                            | Bit Name    | Default                        | Access | Bit Description                              |  |

| 31:24                          | CAL CHAN0_3 | FF                             | R      |                                              |  |

| 23:16                          | CAL CHAN0_2 | FF                             | R      | Channel R or J or D depends on register DEV_ |  |

| 15:8                           | CAL CHAN0_1 | FF                             | R      | SEL                                          |  |

| 7:0                            | CAL CHAN0_0 | FF                             | R      |                                              |  |

Figure 40:

Calibrated Value Channel S, H, B Register

| Addr:<br>0x1B,0x01A,0x19,0x018 |             | Calibrated Value Channel S,H,B |        |                                              |  |

|--------------------------------|-------------|--------------------------------|--------|----------------------------------------------|--|

| Bit                            | Bit Name    | Default                        | Access | Bit Description                              |  |

| 31:24                          | CAL CHAN1_3 | FF                             | R      |                                              |  |

| 23:16                          | CAL CHAN1_2 | FF                             | R      | Channel S or I or C depends on register DEV_ |  |

| 15:8                           | CAL CHAN1_1 | FF                             | R      | SEL                                          |  |

| 7:0                            | CAL CHAN1_0 | FF                             | R      |                                              |  |

Figure 41:

Calibrated Value Channel T, I, C Register

| Addr:<br>0x1F,0x01E,0x1D,0x01C |             | Calibrated Value Channel T,I,C |        |                                              |  |

|--------------------------------|-------------|--------------------------------|--------|----------------------------------------------|--|

| Bit                            | Bit Name    | Default                        | Access | Bit Description                              |  |

| 31:24                          | CAL CHAN2_3 | FF                             | R      |                                              |  |

| 23:16                          | CAL CHAN2_2 | FF                             | R      | Channel T or G or A depends on register DEV_ |  |

| 15:8                           | CAL CHAN2_1 | FF                             | R      | SEL                                          |  |

| 7:0                            | CAL CHAN2_0 | FF                             | R      |                                              |  |

#### Figure 42: Calibrated Value Channel U, J, D Register

| Addr:<br>0x23,0x022,0x21,0x20 |             | Calibrated Value Channel U,J,D |        |                                              |  |

|-------------------------------|-------------|--------------------------------|--------|----------------------------------------------|--|

| Bit                           | Bit Name    | Default                        | Access | Bit Description                              |  |

| 31:24                         | CAL CHAN3_3 | FF                             | R      |                                              |  |

| 23:16                         | CAL CHAN3_2 | FF                             | R      | Channel U or H or B depends on register DEV_ |  |

| 15:8                          | CAL CHAN3_1 | FF                             | R      | SEL                                          |  |

| 7:0                           | CAL CHAN3_0 | FF                             | R      |                                              |  |

Figure 43:

Calibrated Value Channel V, K, E Register

| Addr:<br>0x27,0x026,0x25,0x24 |             | Calibrated Value Channel V,K,E |        |                                              |  |

|-------------------------------|-------------|--------------------------------|--------|----------------------------------------------|--|

| Bit                           | Bit Name    | Default                        | Access | Bit Description                              |  |

| 31:24                         | CAL CHAN4_3 | FF                             | R      |                                              |  |

| 23:16                         | CAL CHAN4_2 | FF                             | R      | Channel V or K or E depends on register DEV_ |  |

| 15:8                          | CAL CHAN4_1 | FF                             | R      | SEL                                          |  |

| 7:0                           | CAL CHAN4_0 | FF                             | R      |                                              |  |

Figure 44:

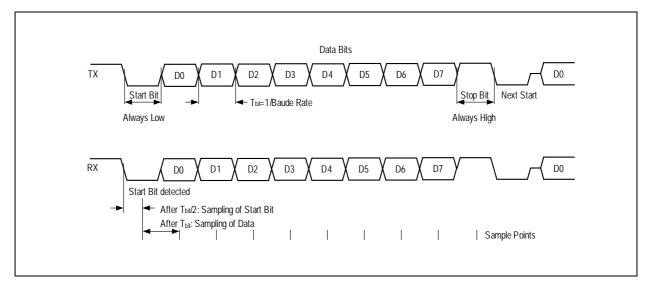

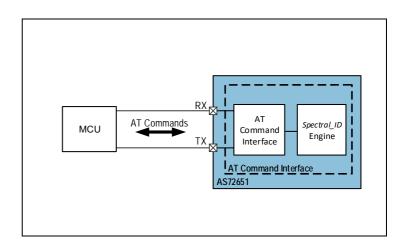

Calibrated Value Channel W, L, F Register