# 3-Channel, Max 38V Output, Linear/Exponential, Analog Dimming, Step-Up WLED Driver with I<sup>2</sup>C

#### **DESCRIPTION**

The MP3313 is a step-up, white, LED converter. The MP3313 uses peak-current mode and a 3-channel current sink to regulate the LED current with up to 25mA on each channel (100mA at flash mode) with 2.7 - 5.5V input voltage.

The MP3313 integrates a  $300m\Omega$ , 42V MOSFET and supports selectable over-voltage protection (17/23/30/38V). The MP3313 can drive up to 10 LEDs in series for LCD panels greater than 5".

The MP3313 achieves ultra-high resolution analog dimming by converting the pulse-width input signal or internal register code to an 11-bit brightness code. The MP3313 is designed with two types of LED current dimming mapping: linear and exponential mapping.

An auto-switching frequency function is integrated to optimize efficiency performance. Full protection features include LED open and short protection, cycle-by-cycle current-limit protection, and thermal shutdown.

The I<sup>2</sup>C interface can set the internal register to program the MP3313 for flexible applications, such as dimming mode, LED current slope, and protection threshold.

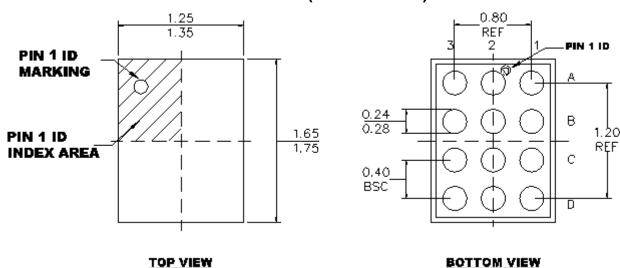

The MP3313 is available in a small WLCSP-12 (1.3mmx1.7mm) package.

#### **FEATURES**

- 2.7 5.5V Input Voltage

- 300mΩ, 42V Internal MOSFET

- 3-Channel Current Sink, Each Channel Enable/Disable Respectively

- LED Current up to 25mA in Backlighting Mode

- LED Current up to 100mA in Flash Mode

- 250µA 25mA LED Current with ±3% Accuracy

- ±1% Typical Current Matching

- Linear or Exponential Analog Dimming

- 11-Bit Dimming Resolution

- Selectable Switching Frequency: 500kHz or 1MHz with Optional -12% Shift

- Auto-Switching Frequency (250kHz, 500kHz, 1MHz)

- High-Speed I<sup>2</sup>C Interface (1.2MHz)

- I<sup>2</sup>C Address External Selectable (A0 Pin)

- Internal Soft Start (SS) to Reduce Inrush Current

- Current-Limit Protection (0.75/1/1.25/1.5A)

- LED Open Protection (17/23/30/38V)

- LED Short Protection (2/3/5V)

- Available in a WLCSP-12 (1.3mmx1.7mm) Package

#### **APPLICATIONS**

- Smart Phones

- Tablets

- GPS Receivers

- LCD Video Displays with One-Cell Li-Ion Battery

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

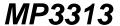

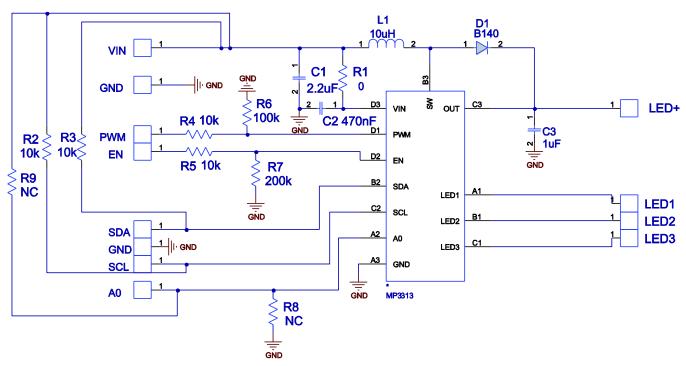

# **TYPICAL APPLICATION**

# **ORDERING INFORMATION**

| Part Number* | Package                | Top Marking |

|--------------|------------------------|-------------|

| MP3313GC     | WLCSP-12 (1.3mmx1.7mm) | See Below   |

<sup>\*</sup> For Tape & Reel, add suffix –Z (e.g. MP3313GC–Z)

## **TOP MARKING**

GAY

LLL

GA: Product code of MP3313GC

Y: Year code LLL: Lot number

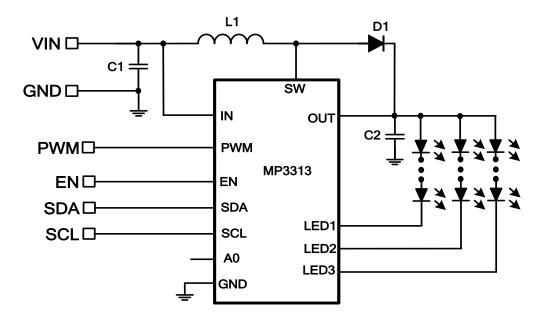

# **PACKAGE REFERENCE**

#

# Thermal Resistance (4) θ<sub>JA</sub> θ<sub>JC</sub> WLCSP-12 (1.3mmx1.7mm) ... 110... 12... °C/W

#### NOTE:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) = ( $T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

VIN = 3.6V,  $V_{EN} = V_{PWM} = high$ , typical values are at  $T_A = 25$ °C, unless otherwise noted.

| Parameters                    | Symbol               | Condition                                                                                    | Min | Тур  | Max  | Unit |

|-------------------------------|----------------------|----------------------------------------------------------------------------------------------|-----|------|------|------|

| Power Supply                  |                      |                                                                                              |     |      |      |      |

| Operating input voltage       | V <sub>IN</sub>      |                                                                                              | 2.7 |      | 5.5  | V    |

| Supply current (quiescent)    | ΙQ                   | VIN = 3.6V, V <sub>EN</sub> = V <sub>PWM</sub> = high, no switching, I <sup>2</sup> C active |     | 2.4  | 2.7  | mA   |

| Supply current (shutdown)     | Ist                  | $V_{EN} = 0V$ , $VIN = 3.6V$                                                                 |     |      | 1    | μΑ   |

| Input UVLO threshold          | V <sub>IN_UVLO</sub> | Rising edge                                                                                  |     | 2.4  | 2.6  | V    |

| Input UVLO hysteresis         |                      |                                                                                              |     | 200  |      | mV   |

| Oscillator                    |                      |                                                                                              |     |      |      |      |

| Switching frequency           | f <sub>SW</sub>      | FS bit = 1                                                                                   | 950 | 1000 | 1050 | kHz  |

|                               | .000                 | FS bit = 0                                                                                   | 475 | 500  | 525  | kHz  |

| Maximum duty cycle            | D <sub>MAX</sub>     | F <sub>SW</sub> = 500kHz                                                                     | 93  | 95   |      | %    |

| , ,                           |                      | F <sub>SW</sub> = 1.0MHz                                                                     | 90  | 93   |      | %    |

| Minimum on time               | T <sub>ON_MIN</sub>  |                                                                                              |     | 100  |      | ns   |

| Power Switch                  |                      |                                                                                              |     |      |      |      |

| Switch on resistance          | RDSON                | VIN = 3.6V                                                                                   |     | 300  |      | mΩ   |

| Current Regulation            |                      |                                                                                              |     |      |      |      |

| Minimum output current        | I <sub>LED_min</sub> | Linear/exponential mode                                                                      |     | 50   |      | μΑ   |

| Maximum output current        | I <sub>LED_max</sub> | Linear/exponential mode                                                                      |     | 25   |      | mΑ   |

| LEDy regulation voltage       | \/                   | I <sub>LED</sub> = 25mA                                                                      |     | 220  |      | mV   |

| LEDx regulation voltage       | $V_{REG}$            | I <sub>LED</sub> = 5mA                                                                       |     | 130  |      | mV   |

| Current accuracy              |                      | I <sub>LED</sub> = 250μA - 25mA, 2.7 - 5V,<br>linear/exponential dimming                     | -3  | 0.1  | 3    | %    |

| Current matching (5)          |                      | I <sub>LED</sub> = 5 - 25mA, 2.7 - 5V,<br>linear/exponential dimming                         | -1  | 0.1  | 1    | %    |

| Current matering (9)          |                      | I <sub>LED</sub> = 250μA - 5mA, 2.7 - 5V,<br>linear/exponential dimming                      | -1  | 0.1  | 2    | %    |

| EN and PWM Logic              |                      |                                                                                              |     |      |      |      |

| PWM input low threshold       | V <sub>PWM_LO</sub>  | V <sub>PWM</sub> falling                                                                     |     |      | 0.4  | V    |

| PWM input high threshold      | V <sub>PWM_HI</sub>  | V <sub>PWM</sub> rising                                                                      | 1.2 |      |      | V    |

| EN low voltage                | V <sub>EN_LOW</sub>  | V <sub>EN</sub> falling                                                                      |     |      | 0.4  | V    |

| EN high voltage               | V <sub>EN_HIGH</sub> | V <sub>EN</sub> rising                                                                       | 1.2 |      |      | V    |

| EN and PWM pull-down resistor | R <sub>PD</sub>      |                                                                                              |     | 1    |      | МΩ   |

© 2017 MPS. All Rights Reserved.

# **ELECTRICAL CHARACTERISTICS** (continued)

VIN = 3.6V,  $V_{EN} = V_{PWM} = \text{high}$ , typical values are at  $T_A = 25^{\circ}\text{C}$ , unless otherwise noted.

| Parameters                   | Symbol               | Condition                      | Min | Тур  | Max   | Unit |

|------------------------------|----------------------|--------------------------------|-----|------|-------|------|

| Protection                   |                      |                                |     |      |       |      |

|                              |                      | OVP1:0 bit = 00                | 16  | 17   | 18    | V    |

| OVP voltage                  | $V_{OVP}$            | OVP1:0 bit = 01                | 22  | 23   | 24    | V    |

| OVF voltage                  | VOVP                 | OVP1:0 bit = 10                | 29  | 30   | 31    | V    |

|                              |                      | OVP1:0 bit = 11                | 37  | 38   | 39    | V    |

| OUT under-voltage protection | V <sub>ОUТ_UV</sub>  |                                |     | 1.2  |       | V    |

|                              |                      | OCP1:0 bit = 00                | 0.6 | 0.75 | 0.9   | Α    |

| Cycle-cycle current limit    | I <sub>LIM</sub>     | OCP1:0 bit = 01                | 0.8 | 1    | 1.2   | Α    |

| Cycle-cycle current limit    | ILIM                 | OCP1:0 bit = 10                | 1.0 | 1.25 | 1.5   | Α    |

|                              |                      | OCP1:0 bit = 11                | 1.2 | 1.5  | 1.8   | Α    |

| LEDX over-voltage threshold  | $V_{OVP\_LED}$       |                                | 4.5 | 5    | 5.5   | V    |

| LEDX under-voltage threshold | V <sub>LEDX_UV</sub> |                                |     | 40   |       | mV   |

| Thermal shutdown threshold   | T <sub>ST</sub>      |                                |     | 150  |       | °C   |

| Thermal shutdown hysteresis  |                      |                                |     | 25   |       | °C   |

| PWM Input <sup>(6)</sup>     |                      |                                |     |      |       |      |

| Minimum PWM frequency        | F <sub>PWML</sub>    |                                |     |      | 50    | Hz   |

| Maximum PWM frequency        | F <sub>PWMH</sub>    | 24MHz sample rate              | 50  |      |       | kHz  |

|                              |                      | 24MHz sample rate              |     |      | 183.3 | ns   |

| Minimum on time              | $T_{MIN\_ON}$        | 4MHz sample rate               |     |      | 1100  | ns   |

|                              |                      | 800kHz sample rate             |     |      | 5500  | ns   |

|                              |                      | 24MHz sample rate              |     |      | 183.3 | ns   |

| Minimum off time             | T <sub>MIN_OFF</sub> | 4MHz sample rate               |     |      | 1100  | ns   |

|                              |                      | 800kHz sample rate             |     |      | 5500  | ns   |

|                              |                      | 24MHz sample rate              |     | 0.6  |       | ms   |

| PWM shutdown time            | $T_{PWM\_SD}$        | 4MHz sample rate               |     | 3    |       | ms   |

|                              |                      | 800kHz sample rate             |     | 25   |       | ms   |

|                              |                      | FILTER1:0 bit = 01             |     | 80   |       | ns   |

| PWM input glitch rejection   | $T_GLITCH$           | FILTER1:0 bit = 10             |     | 160  |       | ns   |

| , -                          |                      | FILTER1:0 bit = 11             |     | 240  |       | ns   |

| Delay time at power-on       | T <sub>POWERON</sub> | EN power-on to start switching |     | 3.5  | 5     | ms   |

© 2017 MPS. All Rights Reserved.

# **ELECTRICAL CHARACTERISTICS** (continued)

VIN = 3.6V,  $V_{EN} = V_{PWM} = high$ , typical values are at  $T_A = 25$ °C, unless otherwise noted.

| Parameters                                                             | Symbol              | Condition        | Min              | Тур | Max  | Unit |

|------------------------------------------------------------------------|---------------------|------------------|------------------|-----|------|------|

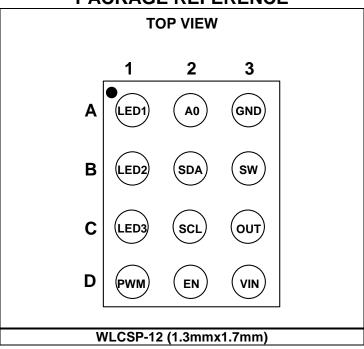

| I <sup>2</sup> C Interface                                             |                     | _                | •                |     |      |      |

| Input logic low                                                        | VIL                 |                  |                  |     | 0.4  | V    |

| Input logic high                                                       | V <sub>IH</sub>     |                  | 1.3              |     |      | V    |

| Output logic low                                                       | V <sub>OL</sub>     | $I_{LOAD} = 3mA$ |                  |     | 0.4  | V    |

| SCLH clock frequency                                                   | fscL                |                  |                  |     | 1200 | kHz  |

| Set-up time for (repeated) start condition                             | tsu,sta             |                  | 160              |     |      | ns   |

| Hold time for (repeated) start condition                               | t <sub>HD,STA</sub> |                  | 160              |     |      | ns   |

| Low time for SCLH clock                                                | $t_{LOW}$           |                  | 160              |     |      | ns   |

| High time for SCLH clock                                               | thigh               |                  | 60               |     |      | ns   |

| Data set-up time                                                       | <b>t</b> su,dat     |                  | 10               |     |      | ns   |

| Data hold time                                                         | t <sub>HD,DAT</sub> |                  | 0 <sup>(7)</sup> |     | 70   | ns   |

| Rise time of SCLH clock                                                | t <sub>R,SCL</sub>  |                  | 10               |     | 40   | ns   |

| Rise time of SCLH clock<br>after repeated start and<br>acknowledge bit | t <sub>R,SCL1</sub> |                  | 10               |     | 80   | ns   |

| Fall time of SCLH clock                                                | t <sub>F,SCL</sub>  |                  | 10               |     | 40   | ns   |

| Rise time of SDAH data                                                 | <b>t</b> R,SDA      |                  | 10               |     | 80   | ns   |

| Fall time of SDAH data                                                 | <b>t</b> F,SDA      |                  | 10               |     | 80   | ns   |

| Set-up time for stop condition                                         | t <sub>SU,STO</sub> |                  | 160              |     |      | ns   |

| Capacitive load for SDAH line and SCLH line                            | C <sub>B</sub> (8)  |                  |                  |     | 100  | pF   |

| Capacitive load for<br>SDAH+SDA line and<br>SCLH+SCL line              | Св                  |                  |                  |     | 400  | pF   |

#### NOTES:

- 5) Matching is defined as the difference of the maximum to minimum current divided by 2 times average currents.

- 6) Guaranteed by design.

- 7) A device must provide a data hold time internally to bridge the undefined part between VIL and VIH of the falling edge of the SCLH signal. An input circuit with a threshold as low as possible for the falling edge of SCLH signal minimizes the hold time.

- 8) For the bus line-load CB between 100pF and 400pF, the timing parameters must be increased linearly.

Sr: Repeated START Condition P: STOP Condition

I<sup>2</sup>C-Compatible Interface Timing Diagram

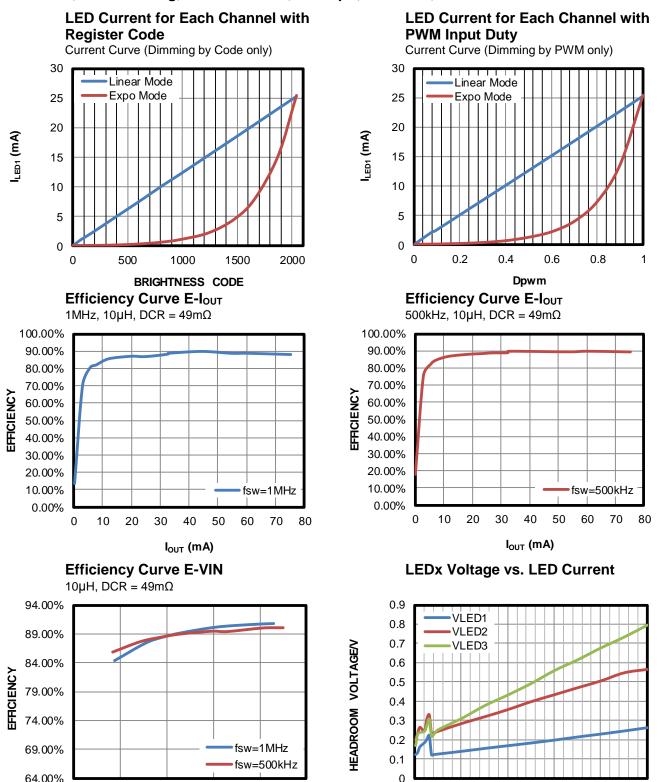

## TYPICAL PERFORMANCE CHARACTERISTICS

VIN = 3.6V, 8\*LEDs/string,  $I_{LED}/Ch$  = 20mA, L =  $10\mu H$ ,  $T_A$  = 25°C, unless otherwise noted.

3

2.5

3.5

$V_{IN}(V)$

4

4.5

5

5

10

15

I<sub>LED</sub>/string (mA)

20

0

25

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

VIN = 3.6V, 8\*LEDs/string, I<sub>LED</sub>/Ch = 20mA, L = 10μH, T<sub>A</sub> = 25°C, unless otherwise noted.

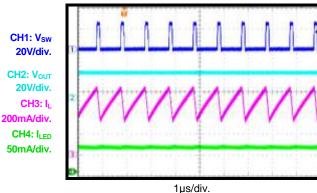

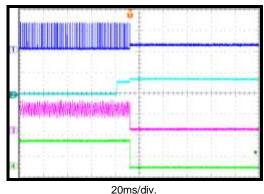

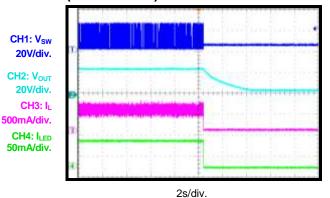

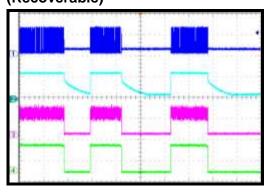

#### **Steady State**

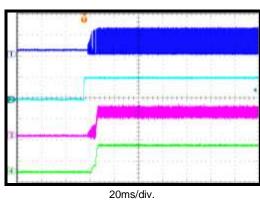

# **EN Power-On**

CH1: V<sub>SW</sub> 20V/div. CH2: V<sub>EN</sub> 5V/div. CH3: IL 500mA/div. CH4: I<sub>LED</sub> 50mA/div.

CH1: V<sub>SW</sub>

CH2: Vout

20V/div.

CH3: IL

500mA/div.

CH4: I<sub>LED</sub>

50mA/div.

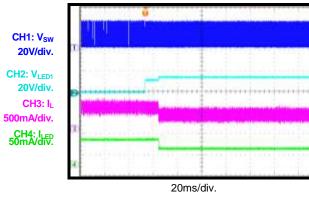

CH1: Vsw

CH2: V<sub>LED1</sub>

500mA/div.

CH4: I<sub>LED</sub>

50mA/div.

20V/div.

20V/div.

CH3: IL

20V/div.

#### **VIN Power On**

CH1: V<sub>SW</sub> 20V/div. CH2: V<sub>IN</sub> 2V/div. CH3: IL 500mA/div. CH4: I<sub>LED</sub> 50mA/div. 20ms/div.

#### Flash Mode

Flash Time = 300ms, Flash Current = 40mA/ch

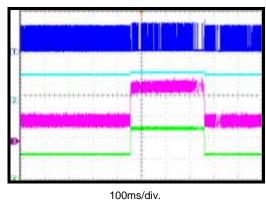

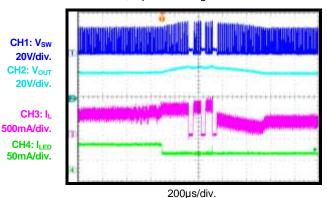

#### Short LED Protection (Mark Off)

Short one string

# **Short LED Protection (IC Latch Off)**

Short LED1 String

CH1: V<sub>SW</sub>

20V/div.

20V/div.

CH3: IL

500mA/div.

CH4: I<sub>LED</sub>

50mA/div.

CH1: V<sub>SW</sub>

CH2: V<sub>OUT</sub>

500mA/div.

CH4: I<sub>LED</sub>

50mA/div.

20V/div.

20V/div.

CH3: I<sub>L</sub>

CH2: V<sub>OUT</sub>

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

VIN = 3.6V, 8\*LEDs/string, I<sub>LED</sub>/Ch = 20mA, L = 10μH, T<sub>A</sub> = 25°C, unless otherwise noted.

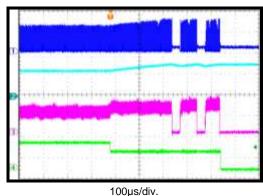

## **Open LED Protection (Mark Off)**

Vovp = 30V, Open 1 String

**Open LED Protection (IC latch Off)**

V<sub>OVP</sub> = 30V, Open 1 String

### **Thermal Shutdown Protection** (IC Latch Off)

Thermal Shutdown Protection (Recoverable)

2s/div.

# **PIN FUNCTIONS**

|       | .0110110 |     |                                                                                                                                                                                                                                        |

|-------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin # | Name     | I/O | Description                                                                                                                                                                                                                            |

| A1    | LED1     | I   | Current sink for LED1.                                                                                                                                                                                                                 |

| A2    | A0       | I   | LSB of I <sup>2</sup> C interface address select. If A0 is floating, it must be pulled up or down externally. If A0 is pulled low, the I <sup>2</sup> C address LSB is 0. If A0 is pulled high, the I <sup>2</sup> C address LSB is 1. |

| А3    | GND      | I   | Ground.                                                                                                                                                                                                                                |

| B1    | LED2     | I   | Current sink for LED2.                                                                                                                                                                                                                 |

| B2    | SDA      | I/O | I <sup>2</sup> C interface data signal input.                                                                                                                                                                                          |

| В3    | SW       | I   | Drain connection of the internal low-side MOSFET for boost converter.                                                                                                                                                                  |

| C1    | LED3     | I   | Current sink for LED3.                                                                                                                                                                                                                 |

| C2    | SCL      | I   | I <sup>2</sup> C interface clock signal input.                                                                                                                                                                                         |

| C3    | OUT      | 0   | Boost converter output connection.                                                                                                                                                                                                     |

| D1    | PWM      | I   | <b>PWM dimming input signal.</b> Apply a 50Hz to 50kHz PWM pulse to the PWM pin for analog dimming.                                                                                                                                    |

| D2    | EN       | I   | IC enable input. Drive EN to logic high to enable the IC. Drive EN to logic low longer than 2.5ms to shut down the IC.                                                                                                                 |

| D3    | VIN      | I   | <b>Power supply input with 2.7V to 5.5V.</b> Connect a ceramic capacitor close to VIN to bypass the IC.                                                                                                                                |

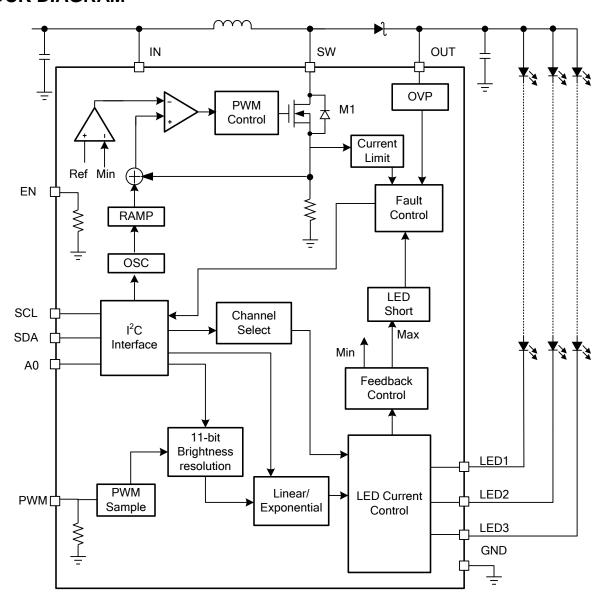

# **BLOCK DIAGRAM**

**Figure 1: Functional Block Diagram**

#### **OPERATION**

The MP3313 is a step-up converter with peak-current-mode control architecture that employs three channels of current sink to drive three strings of white LED for an LCD panel. The MP3313 supports 11-bit resolution analog dimming via an internal register or external pulse-width modulation (PWM) input signal.

#### **Boost Converter Switching Frequency**

The MP3313 has two selectable switching frequencies (FS) through the  $I^2C$  interface. When the register bit FS = 1, the switching frequency is set to 1MHz. When the register bit FS = 0, the switching frequency is set to 500kHz. Additionally, the switching frequency can be shifted down 12% by the register FS SHFT.

#### **Auto-Switching Frequency**

To optimize the efficiency in different loads, the MP3313 can select the switching frequency automatically by comparing the auto-switching frequency low threshold (register 0x16) and auto-switching frequency high threshold (register 0x15) to 8MSBs of the brightness code (register 0x19).

The auto-switching frequency function includes three different working frequency points: 1MHz, 500kHz, and 250kHz. At the high threshold, the device switches from 1MHz to 500kHz. At the low threshold, the device switches from 250kHz from 500kHz (see Table 1).

**Table 1: Switching Frequency Auto-Function**

| 8MSBs of Brightness Code (register 0x19)                                                                                                  | Switching<br>Frequency |

|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| <auto frequency="" low<br="" switching="">threshold (register 0x16)</auto>                                                                | 250kHz                 |

| >auto switching frequency low<br>threshold (register 0x16)<br><auto frequency="" high<br="" switching="">threshold (register 0x15)</auto> | 500kHz                 |

| >auto switching frequency high threshold (register 0x15)                                                                                  | 1MHz                   |

To disable auto-frequency, both the auto-switching frequency high threshold and low threshold must be set to zero. Once the auto-function is disabled, the MP3313 works at a fixed frequency set by the FS bit. The auto-frequency function can be enabled by setting a non-zero code for any one of auto-switching frequency thresholds.

Note that the switching frequency -12% shift is still active when the auto-switching frequency function is enabled.

#### **Minimum Inductor Selection**

To optimize the boost converter control loop, the minimum inductance is limited for the MP3313, which is set by the minimum inductor L\_MIN bit. When the L\_MIN bit is set to 0, the minimum inductor is  $4.7\mu H$ . When the L\_MIN bit is set to 1, the minimum inductor is  $10\mu H$ .

#### **System Start-Up**

If input voltage is higher than the under-voltage lockout (UVLO) threshold and EN is pulled high, the MP3313 enters standby mode. In this mode, only the I<sup>2</sup>C is active and ready to communicate with the host. Meanwhile, the MP3313 monitors the topology connection and safety limits, including two checks:

- The MP3313 checks whether the OUT pin connection is correct or not. An OUT voltage (V<sub>OUT</sub>) of less than 1.2V cannot implement device switching and sets the FT\_UVP bit to 1.

- The MP3313 checks if the device has triggered LED open/short protection, over-current limit protection, or over-temperature protection (OTP). If all protections pass, the MP3313 then starts boosting the step-up converter with an internal soft start.

To prevent a large inrush current, it is recommended that the power-on sequence be from VIN power-on to PWM power-on to EN power-on. If the external EN pin is always pulled high or to VIN by a resistor, it is requested to write EN to 1 after VIN powers on. When dimming is done by the internal code only, the PWM signal can be ignored.

#### **Boost Converter Operation**

The MP3313 uses peak-current mode to control the output voltage. At the start of the internal oscillator cycle, the low-side MOSFET (LS-FET) (M1) is turned on. To prevent sub-harmonic oscillation at duty cycles greater than 50%, a stabilizing ramp is added to the output of the current sense amplifier, and the result is fed into the positive input of the PWM generation comparator. When this voltage equals the

output voltage of the error amplifier, the LS-FET is turned off. Then the inductor current flows through the free-wheeling diode, which forces the inductor current to decrease. The output voltage of the internal error amplifier is an amplified signal of the difference between the reference voltage and the feedback voltage from the LED load cathode. The converter chooses the lowest active LEDx pin voltage automatically to provide a high enough bus voltage to power all of the LED arrays. If the feedback voltage drops below the reference, the output of the error amplifier increases. This results in more current flowing through the LS-FET and delivers more power to the output. This forms a closed control loop that regulates the output voltage.

#### **LED String Selection**

There are three LED strings for the MP3313, and each string has an independent EN bit. This allows for 1-string, 2-string, or 3-string application. By default, all three strings are enabled.

#### Flash Mode

The MP3313 can also work in flash mode by setting the FL\_EN bit to 1. The flash time depends on the FL\_T bit and ranges from 50 - 800ms. The flash current is set by I\_FL bit.

When flash mode is enabled, the inductor peak-current limit value jumps to the flash current limit automatically, which is set by the FL\_CL bit (2.5A/3A selectable), and the LED current jumps to the flash current. When the flash is timed out, the LED current and inductor peak current limit returns to backlight mode, and the FL\_EN bit is reset to 0. When protection is triggered during the flash, flash mode ends, and the FL\_EN bit is reset.

#### **Dimming Control**

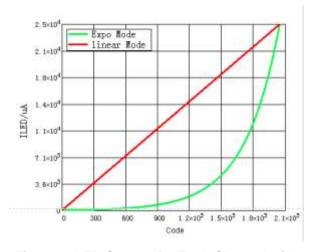

The MP3313 supports ultra-high resolution analog dimming by converting the PWM input signal or internal register code to the 11-bit brightness code. Two kinds of LED current dimming curve are available: linear and exponential mapping.

The MP3313 converts the external PWM signal into an internal reference via the duty detection

circuit to regulate the current linearly or exponentially.

Calculate the linear analog dimming with Equation (1):

$$I_{\parallel ED} = 40.806 \mu A + 12.195 \mu A \times Code$$

(1)

Where Code ranges from 1 to 2047. Code 0 sets the LED current to 0.

Calculate the exponential analog dimming with Equation (2):

$$I_{\parallel ED} = 51.1 \mu A \times 1.003040572^{Code}$$

(2)

Where Code ranges from 1 to 2047. Code 0 sets the LED current to 0.

Figure 2 shows the linear and exponential dimming curve for the LED current.

Figure 2: LED Current for Each Channel with Brightness Code

#### **LED Current Ramp Up/Down**

The LED current ramps up and down step-by-step from one brightness code to the next when the LED current slope function is enabled by setting the SLPEN bit to 1. The ramp time can be calculated with Equation (3):

$$t_{RAMP} = RAMP \times (Code1 - Code0 - 1)$$

(3)

Where RAMP is the slope rate set by the TSLP bit, Code 0 is the original brightness point, and Code 1 is the target brightness point.

#### **PWM Sample Frequency**

Three different sample frequencies can be chosen for the input PWM dimming signal for the MP3313.

- PWMSR1:0 bit = 00, sample frequency = 800kHz.

- PWMSR1:0 bit = 01, sample frequency = 4MHz (default).

- PWMSR1:0 bit = 1x, sample frequency = 24MHz.

Choose a PWM sample frequency based on the required dimming resolution, input dimming frequency, and efficiency (the higher the sample frequency, the higher the input consumption current is). A low-level PWM signal that lasts for a certain amount of time can disable the device (see Table 2). The lower the PWM sample frequency is, the longer the PWM shutdown time is.

Table 2: PWM Shutdown Time vs. Sample Frequency

| f <sub>sample</sub> (Hz) | T <sub>PWM_SD</sub> (ms) |

|--------------------------|--------------------------|

| 24M                      | 0.6                      |

| 4M                       | 3                        |

| 800k                     | 25                       |

### **PWM Hysteresis**

To prevent the input PWM dimming signal jitter from causing LED flicker, the MP3313 offers selectable PWM hysteresis.

- HYS2:0 = 000: no hysteresis

- HYS2:0 = 001: 1 clock

- HYS2:0 = 100: 4 clock (default)

- HYS2:0 = 110: 6 clock

Where 1 clock = 1/fsample. Different sample rates produce different clocks.

The PWM hysteresis is active only when the direction of the LED brightness changes. Once the LED brightness direction changes, the input PWM signal must overcome the hysteresis, and then the brightness changes. Otherwise, if the LED brightness changing direction remains the same, the PWM signal hysteresis function is unused.

#### **Brightness Control Mode**

The LED current is controlled either by the input PWM dimming signal or internal brightness register. Five different brightness control modes can be selected and set by the BRTMD2:0 bit.

1. <u>Internal register only:</u> When the brightness control mode bits are set to 000, the LED current is controlled by the internal brightness register only without the PWM signal. The LED current changes only when the eight MSBs are written. Write three LSBs first, then write eight MSBs for 11-bit brightness change.

In linear mapping mode, the LEDs can be calculated with Equation (4) and Equation (5):

$$I_{\mu ED0} = 40.806 \mu A + 12.195 \mu A \times Code0$$

(4)

$$I_{\mu ED1} = 40.806 \mu A + 12.195 \mu A \times Code1$$

(5)

In exponential mapping mode, the LEDs can be calculated with Equation (6) and Equation (7):

$$I_{\text{II, EDO}} = 51.1 \mu A \times 1.003040572^{\text{Code0}}$$

(6)

$$I_{\mu \, \text{ED1}} = 51.1 \mu \text{A} \times 1.003040572^{\text{Code1}} \tag{7}$$

The ramp time in either mapping mode can be calculated with Equation (8):

$$t_{RAMP} = RAMP \times (Code1 - Code0 - 1)$$

(8)

2. Input PWM duty only: When the brightness control mode bits are set to 001, the LED current is controlled by the input dimming signal only. The internal brightness code is ignored. The MP3313 samples the PWM signal and translates it into an 11-bit code to regulate the current. Choose the corresponding PWM frequency based on the PWM sample rate and resolution request.

In linear mapping mode, the LEDs can be calculated with Equation (9) and Equation (10):

$$I_{\parallel FD0} = 40.806 \mu A + 12.195 \mu A \times 2047 \times D_{PWM0}$$

(9)

$$I_{\mu ED1} = 40.806 \mu A + 12.195 \mu A \times 2047 \times D_{PWM}$$

(10)

In exponential mapping mode, the LEDs can be calculated with Equation (11) and Equation (12):

$$I_{\text{II,EDO}} = 51.1 \mu A \times 1.003040572^{2047 \times DPWMO}$$

(11)

$$I_{\text{II} \text{ FD1}} = 51.1 \mu\text{A} \times 1.003040572^{2047 \times \text{DPWM1}} (12)$$

The ramp time in either mapping mode can be calculated with Equation (13):

$$t_{RAMP} = RAMP \times |2047 \times D_{PWM1} - 2047 \times D_{PWM0} - 1|$$

(13)

3. Internal register multiplies PWM duty before ramping: LED slope step controlled by internal register and PWM duty. When the brightness control mode bits are set to 010, the LED current is controlled by the input PWM dimming duty multiplied by the internal brightness register. The slope step is also controlled by the PWM dimming duty multiplied by the brightness register.

In linear mode, the LEDs can be calculated with Equation (14) and Equation (15):

$$I_{\text{ILEDO}} = 40.806 \mu A + 12.195 \mu A \times \text{Code} 0 \times D_{\text{PWMO}}$$

(14)

$$I_{ILED1} = 40.806\mu A + 12.195\mu A \times Code1 \times D_{PWM1}$$

(15)

In exponential mode, the LEDs can be calculated with Equation (16) and Equation (17):

$$I_{\text{ILEDO}} = 51.1 \mu A \times 1.003040572^{\text{Code0} \times \text{DPWMO}} \quad (16)$$

$$I_{\text{ILED1}} = 51.1 \mu A \times 1.003040572^{\text{Code1} \times \text{DPWM1}} \quad (17)$$

The ramp time in either mapping mode can be calculated with Equation (18):

$$t_{RAMP} = RAMP \times |Code1 \times D_{PWM1} - Code0 \times D_{PWM0} - 1|$$

(18)

4. Ramp before internal register multiplies input PWM dimming duty, LED slope step controlled by internal register only: When the brightness control mode bits are set to 011, the LED current is controlled by the input PWM dimming duty multiplied by the internal brightness register. The slope step is controlled by the internal brightness register only.

In this mode, the LED current jumps immediately when the external PWM dimming duty changes. Then the LED current changes step-by-step to the new brightness register.

In linear mapping mode, the original current can be calculated with Equation (19):

$$I_{\text{ILEDO-}} = 40.806 \mu A + 12.195 \mu A \times Code0 \times D_{PWM0}$$

(19)

The LED current jumps immediately when the duty changes, as shown in Equation (20):

$$I_{\text{ILED0+}} = 40.806 \mu A + 12.195 \mu A \times \text{Code0} \times D_{\text{PWM1}}$$

(20)

The LED current follows the code changes shown in Equation (21):

$$I_{ILED1} = 40.806\mu A + 12.195\mu A \times Code1 \times D_{PWM1}$$

(21)

In exponential mapping mode, the original current can be calculated with Equation (22):

$$I_{\text{II} \text{ EDO}} = 51.1 \mu A \times 1.003040572^{\text{Code0} \times \text{DPWM0}} (22)$$

The LED current jumps immediately when the duty changes, as shown in Equation (23):

$$I_{\text{ILED0+}} = 51.1 \mu A \times 1.003040572^{\text{Code0} \times \text{DPWM1}} \ \ (23)$$

Then, the LED current follows the code changes shown in Equation (24):

$$I_{\text{ILED1}} = 51.1 \mu A \times 1.003040572^{\text{Code1} \times \text{DPWM1}} \ \ (24)$$

The ramp time in either mode can be calculated with Equation (25):

$$t_{RAMP} = RAMP \times |Code1 - Code0 - 1|$$

(25)

For example, the PWM duty changes from 50% to 100%, and the brightness register changes from 1024 to 2047, the slope is 1ms/step in linear analog dimming.

The original LED current can be calculated with Equation (26):

$$I_{\text{ILEDO}} = 40.806 \mu A + 12.195 \mu A \times (1024 \times 0.5) = 6.28 mA \text{ (26)}$$

Then the LED current jumps immediately, as shown in Equation (27):

$$I_{\text{ILEDO+}} = 40.806 \mu A + 12.195 \mu A \times (1024 \times 1) = 12.52 m A$$

(27)

The LED current rise up step-by-step, shown in Equation (28):

$$I_{\text{II}} = 40.806 \mu A + 12.195 \mu A \times (2047 \times 1) = 25 \text{mA}$$

(28)

The ramp-up time can be calculated with Equation (29):

$$t_{RAMP} = 1 ms/step \times |2047 - 1024 - 1| = 1022 ms$$

(29)

5. LED current multiplied by the input PWM duty, LED slope step controlled by the internal register only: When the brightness control mode bits are set to 100, the LED current is dimmed by the input PWM dimming duty, and slope step is controlled by the internal brightness register only.

In linear mode, the LEDs can be calculated with Equation (30) and Equation (31):

$$I_{ILEDO} = (40.806\mu A + 12.195\mu A \times Code0) \times D_{PWMO}$$

(30)

$$I_{\mu ED1} = (40.806 \mu A + 12.195 \mu A \times Code1) \times D_{PWM1}$$

(31)

In exponential mode, the LEDs can be calculated with Equation (32) and Equation (33):

$$I_{\text{II,EDO}} = 51.1 \mu A \times 1.003040572^{\text{Code0}} \times D_{\text{PWMO}}$$

(32)

$$I_{\text{II} \text{ FD1}} = 51.1 \mu\text{A} \times 1.003040572^{\text{Code1}} \times D_{\text{PWM1}}$$

(33)

The ramp time in either mode can be calculated with Equation (34):

$$t_{RAMP} = RAMP \times |Code1 - Code0 - 1|$$

(34)

## **Cycle-by-Cycle Current Limit**

To prevent the external components from exceeding the current stress rating, the MP3313 uses a cycle-by-cycle current limit protection. The limit value can be selected by the register bit CL1:0. When the internal LS-FET current exceeds the current limit threshold, the MOSFET turns off until the next clock cycle begins.

#### **Over-Current Protection (OCP)**

The FT OCP flag is set when over-current protection (OCP) occurs. To prevent the transient over-current from setting the FT\_OCP bit, the MP3313 designs an OCP counter. If the inductor current always reaches the threshold in a 128µs period, the counter increases by 1. Every eight 128µs periods, if the OCP counter is higher than 2, the FT OCP bit is set to 1.

If OCP SD = 0, the IC latches off when OCP is triggered. If OCP\_SD = 1, the IC is recoverable when OCP is triggered.

#### Over-Voltage Protection and Open-String **Protection**

When V<sub>OUT</sub> is higher than the over-voltage protection (OVP) threshold. OVP is triggered. the IC stops switching, and the FT\_OVP bit is set. When the output voltage drops low, switching recovers.

The OVP threshold is set by the internal register OVP1:0. Four different thresholds can be selected.

- OVP1:0 = 00: 17V

- OVP1:0 = 01: 23V

- OVP1:0 = 10: 30V

- OVP1:0 = 11: 38V (default)

If the LED string is open, the feedback voltage is lower than the reference voltage, and V<sub>OUT</sub> rises up and continues charging the output capacitor until OUT reaches the protection point (V<sub>OVP</sub>), and OVP is triggered. The IC also monitors the LEDx voltage. When the LEDx voltage is lower than 40mV, open LED protection is triggered. Three different actions can be set by OVP\_MD1:0 through the I<sup>2</sup>C after a fault is triggered.

- OVP MD1:0 = 00: FT OVP is set, and FT OLP is set.

- OVP\_MD1:0 = 01: FT\_OVP is set, FT\_OLP is set, and the string is marked off with LEDx < 40mV.

- OVP\_MD1:0 = 10: FT\_OVP is set, and the IC latches off when the OVP fault is detected.

#### **Short LED Protection**

The MP3313 monitors the LEDx voltage to determine if a short string has occurred. If a short occurs, the respective LEDx pin is pulled up and can tolerate high voltage stress. If the LEDx voltage is higher than the short-protection threshold and lasts for 2ms, a short string fault is detected. The threshold is set by S TH1:0.

Short LED protection is programmed by SLP\_MD1:0.

- SLP\_MD1:0 = 00: The short LED fault detection is disabled.

- SLP\_MD1:0 = 01: The short LED fault detection is enabled, and the FT\_SLP is set when the fault is detected.

- SLP\_MD1:0 = 10: The short LED fault detection is enabled, the FT\_SLP is set, and the string is marked off with the LEDx voltage that is higher than the threshold.

- SLP\_MD1:0 = 11: FT\_SLP is set, and the IC latch off when the fault is detected.

#### **Thermal Shutdown Protection**

To prevent the IC from operating at an exceedingly high temperature, thermal shutdown is implemented in the MP3313 by detecting the silicon die temperature. When the die temperature exceeds the upper threshold ( $T_{ST}$ ), the IC shuts down and resumes normal operation when the die temperature drops below the lower threshold. Typically, the hysteresis value is 25°C. If OTP\_SD = 0, the IC latches off when OTP is triggered.

### I<sup>2</sup>C Chip Address

The 7-bit MSB device address is 0x36 - 0x37 selected by A0. If A0 is floating, it must be pulled up or down externally to set the address.

After the start condition, the I<sup>2</sup>C-compatible master sends a 7-bit address followed by an eighth read (1) or write (0) bit. The following bit indicates the register address to or from which the data is written or read (see Figure 3).

Figure 3: The I<sup>2</sup>C Compatible Device Address

To avoid a glitch in the operation, the following bit changes only when the IC EN bit (0x10, bit[0]) or the three LED channel enable bits (0x10, bit[3:1]) are set to 0.

The following bit should contain these bits:

- 1. Mapping mode bit (MAPMOD, 0x11, bit[7])

- 2. Brightness mode bits (BRTMD2:0, 0x11, bit[6:4])

- 3. Slope enable bit (SLPEN, 0x11, bit[3])

- 4. Slope time bit (TSLP2:0, 0x11, bit[2:0])

- PWM sample rate bit (PWMSR1:0, 0x12, bit[7:6])

- 6. PWM polarity bit (PWM\_P, 0x12, bit[5])

- 7. PWM hysteresis bit (HYS2:0, 0x12, bit [4:2])

- 8. PWM filter bit (FILTER1:0, 0x12, bit[1:0])

- 9. Auto frequency high threshold bit (FS\_AUTOH7:0, 0x15, bit[7:0])

- 10. Auto frequency low threshold bit (FS\_AUTOL7:0, 0x16, bit[7:0])

#### **Table 3: Register Mapping**

| Add | D7             | D6               | D5       | D4       | D3      | D2       | D1      | D0      |

|-----|----------------|------------------|----------|----------|---------|----------|---------|---------|

| 00H | DEV_ID3        | DEV_ID2          | DEV_ID1  | DEV_ID0  | REV_ID3 | REV_ID2  | REV_ID1 | REV_ID0 |

| 01H |                |                  |          | RESERVED |         |          |         | SRST    |

| 10H |                | RESE             | RVED     |          | CH3EN   | CH2EN    | CH1EN   | EN      |

| 11H | MAPMD          |                  | BRTMD2:0 |          | SLPEN   |          | TSLP2:0 |         |

| 12H | PWMSR1:0 PWM_P |                  |          |          | HYS2:0  |          | FILT    | ER1:0   |

| 13H | NA             | FS_SHFT FS L_MIN |          |          | OVF     | P1:0     | С       | L1:0    |

| 14H | FL_CL IFL6:0   |                  |          |          |         |          |         |         |

| 15H |                |                  |          | FS_Al    | JTOH7:0 |          |         |         |

| 16H |                |                  |          | FS_AI    | JTOL7:0 |          |         |         |

| 17H |                | FL_              | T3:0     |          |         | RESERVED |         | FL_EN   |

| 18H |                |                  | RESERVED |          |         |          | BRT2:0  |         |

| 19H | BRT10:3        |                  |          |          |         |          |         |         |

| 1EH | S_1            | _TH1:0 SLP_MD1:0 |          |          | OVP_I   | MD1:0    | OTP_SD  | OCP_SD  |

| 1FH | RESE           | ERVED            | FT_UVP   | FT_OLP   | FT_SLP  | FT_OTP   | FT_OCP  | FT_OVP  |

## **Table 4: Chip ID Register**

|     | Addr: 0x00 |        |         |              |  |  |  |

|-----|------------|--------|---------|--------------|--|--|--|

| Bit | Bit Name   | Access | Default | Description  |  |  |  |

| 7:4 | DEV_ID     | r      | 000     | Device ID.   |  |  |  |

| 3:0 | REV_ID     | r      | 0001    | Revision ID. |  |  |  |

#### **Table 5: Software Reset Register**

|     | Addr: 0x01 |        |                         |                                                                                                                                        |  |  |  |

|-----|------------|--------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit | Bit Name   | Access | ess Default Description |                                                                                                                                        |  |  |  |

| 7:1 | N/A        | r      | N/A Reserved.           |                                                                                                                                        |  |  |  |

| 0   | SRST       | r/w    | 0                       | Software reset bit. 0: normal operation 1: device resets, all registers are reset to default (this bit automatically resets back to 0) |  |  |  |

## Table 6: Enable Register

|     |          |        |         | Addr: 0x10                                        |

|-----|----------|--------|---------|---------------------------------------------------|

| Bit | Bit Name | Access | Default | Description                                       |

| 7:4 | N/A      | r      | N/A     | Reserved.                                         |

| 3   | CH3EN    | r/w    | 1       | LED3 enable bit. 1: LED3 enabled 0: LED3 disabled |

| 2   | CH2EN    | r/w    | 1       | LED2 enable bit. 1: LED2 enabled 0: LED2 disabled |

| 1   | CH1EN    | r/w    | 1       | LED1 enable bit. 1: LED1 enabled 0: LED1 disabled |

| 0   | EN       | r/w    | 1       | IC enable bit 1: IC enabled 0: IC disabled        |

## **Table 7: Brightness Control Register**

|     | Addr: 0x11 |        |         |                                                                                                                                                                                                                                        |  |  |

|-----|------------|--------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit | Bit Name   | Access | Default | Description                                                                                                                                                                                                                            |  |  |

| 7   | MAPMD      | r/w    | 0       | LED current mapping mode bit. 0: linear mapping 1: exponential mapping                                                                                                                                                                 |  |  |

| 6:4 | BRTMD2:0   | r/w    | 011     | Brightness mode control bits.  000: brightness register only 001: PWM duty only 010: brightness register multiplies PWM duty before ramp 011: ramp before brightness register multiplies PWM duty 100: LED current multiplies PWM duty |  |  |

| 3   | SLPEN      | r/w    | 0       | LED current slope enable bit. 0: LED current slope disabled 1: LED current slope enabled                                                                                                                                               |  |  |

| 2:0 | TSLP2:0    | r/w    | 000     | LED current slope time for each step.  000: 0.125ms/step  001: 0.25ms/step  010: 0.5ms/step  011: 1ms/step  100: 2ms/step  101: 4ms/step  110: 8ms/step  111: 16ms/step                                                                |  |  |

## **Table 8: PWM Control Register**

|     | Addr: 0x12 |        |         |                                                                                                                                                 |  |  |  |

|-----|------------|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit | Bit Name   | Access | Default | Description                                                                                                                                     |  |  |  |

| 7:6 | PWMSR      | r/w    | 01      | PWM sample frequency set bits.  00: 800kHz 01: 4MHz 1x: 24MHz                                                                                   |  |  |  |

| 5   | PWM_P      | r/w    | 1       | PWM input polarity set bit. 0: active low 1: active high                                                                                        |  |  |  |

| 4:2 | HYS2:0     | r/w    | 100     | PWM hysteresis set bits.  000: no hysteresis  001: 1 clock  010: 2 clock  011: 3 clock  100: 4 clock  101: 5 clock  110: 6 clock  111: reserved |  |  |  |

| 1:0 | FILTER1:0  | r/w    | 11      | PWM input filter bits. 00: no filter 01: 80ns 10: 160ns 11: 240ns                                                                               |  |  |  |

## **Table 9: Boost Control Register**

|     |          |        | Addr: 0x13 |                                                                       |

|-----|----------|--------|------------|-----------------------------------------------------------------------|

| Bit | Bit Name | Access | Default    | Description                                                           |

| 7   | N/A      | r      | N/A        | Reserved.                                                             |

| 6   | FS_SHFT  | r/w    | 1          | Switching frequency shift bit. 0: -12% shift 1: no shift              |

| 5   | FS       | r/w    | 1          | Boost switching frequency set bit. 0: 500kHz 1: 1MHz                  |

| 4   | L_MIN    | r/w    | 0          | Minimum inductor select bit.<br>0: 4.7μH<br>1: 10μH                   |

| 3:2 | OVP1:0   | r/w    | 11         | Over-voltage protection set bits.  00: 17V  01: 23V  10: 30V  11: 38V |

| 1:0 | CL1:0    | r/w    | 11         | Current limit set bits. 00: 0.75A 01: 1A 10: 1.25A 11: 1.5A           |

#### **Table 10: Flash Current Set Register**

|     | Addr: 0x14 |        |         |                                                                                                                       |  |  |

|-----|------------|--------|---------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| Bit | Bit Name   | Access | Default | Description                                                                                                           |  |  |

| 7   | FL_CL      | r/w    | 0       | Current limit in flash mode. 0: 2.5A 1: 3A                                                                            |  |  |

| 6:0 | IFL6:0     | r/w    | 0101000 | Flash current set register. 1mA/step.  0x0A: 10mA  0x0B: 11mA   0x28: 40mA (default)   0x64: 100mA  0x64~7F: reserved |  |  |

#### **Table 11: Auto-Switching Frequency High Threshold**

|     | Addr: 0x15 |        |          |                                                                                                                                                                                   |  |  |  |

|-----|------------|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit | Bit Name   | Access | Default  | Description                                                                                                                                                                       |  |  |  |

| 7:0 | FS_AUTOH   | r/w    | 00000000 | Auto-switching frequency high threshold (500kHz to 1MHz). Compared with the 8 MSBs of the brightness code. The function is disabled when both FS_AUTOH and FS_AUTOL are set to 0. |  |  |  |

#### **Table 12: Auto-Switching Frequency Low Threshold**

|     |          |        |          | Addr: 0x16                                                                                                                                                                         |

|-----|----------|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name | Access | Default  | Description                                                                                                                                                                        |

| 7:0 | FS_AUTOL | r/w    | 00000000 | Auto-switching frequency low threshold (250kHz to 500kHz). Compared with the 8 MSBs of the brightness code. The function is disabled when both FS_AUTOH and FS_AUTOL are set to 0. |

## **Table 13: Flash Mode Control Register**

|     | Addr: 0x17 |        |                 |                                                                                                                                |  |  |

|-----|------------|--------|-----------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit | Bit Name   | Access | Default         | Description                                                                                                                    |  |  |

| 7:4 | FL_T       | r/w    | 0101<br>(300ms) | Flash time set register. 50ms/step. 0000: 50ms 0001: 100ms 1111: 800ms                                                         |  |  |

| 3:1 | N/A        | r      | 000             | Reserved.                                                                                                                      |  |  |

| 0   | FL_EN      | r/w    | 0               | Backlight flash mode enable bit. 0: disable 1: enable Automatically resets to 0 when flash timeout or protection is triggered. |  |  |

#### **Table 14: Brightness Register LSB**

|     | Addr: 0x18 |        |         |                                       |  |  |

|-----|------------|--------|---------|---------------------------------------|--|--|

| Bit | Bit Name   | Access | Default | Description                           |  |  |

| 7:3 | N/A        | r      | N/A     | Reserved.                             |  |  |

| 2:0 | BRT2:0     | r/w    | 111     | 3-bit LSB of the brightness register. |  |  |

## Table 15: Brightness Register MSB

|                                         | Addr: 0x19 |     |          |                                       |  |  |

|-----------------------------------------|------------|-----|----------|---------------------------------------|--|--|

| Bit Bit Name Access Default Description |            |     |          | Description                           |  |  |

| 7:0                                     | BRT10:3    | r/w | 11111111 | 8-bit MSB of the brightness register. |  |  |

#### **Table 16: Fault Control Register**

|     | Addr: 0x1E |        |         |                                                                                                                                                                                                                        |  |  |  |

|-----|------------|--------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit | Bit Name   | Access | Default | Description                                                                                                                                                                                                            |  |  |  |

| 7:6 | S_TH       | r/w    | 01      | LED short-protection threshold setting. If the LEDx voltage is higher than the threshold, short protection is triggered.  00: 2V  01: 3V  10: 5V  11: reserved                                                         |  |  |  |

| 5:4 | SLP_MD     | r/w    | 00      | LED short protection mode selection.  00: LED short protection is disabled  01: FT_SLP is set when a fault is detected  10: FT_SLP is set and the fault string is marked off  11: FT_SLP is set and the IC latches off |  |  |  |

| 3:2 | OVP_MD     | r/w    | 00      | Over-voltage protection mode selection.  00: FT_OVP is set when a fault is detected  01: FT_OVP is set and the open string is marked off  10: FT_OVP is set and the IC latches off  11: reserved                       |  |  |  |

| 1   | OTP_SD     | r/w    | 1       | Thermal shutdown latch off disable bit.  0: IC latches off when OTP is triggered  1: no latch off                                                                                                                      |  |  |  |

| 0   | OCP_SD     | r/w    | 1       | Over-current protection latch off disable bit.  0: IC latches off when OCP is triggered  1: no latch off                                                                                                               |  |  |  |

## **Table 17: Fault Flag Register**

|     | 100 100 100 100 100 100 100 100 100 100 |        |         |                                                                                |  |  |  |

|-----|-----------------------------------------|--------|---------|--------------------------------------------------------------------------------|--|--|--|

|     | Addr: 0x1F                              |        |         |                                                                                |  |  |  |

| Bit | Bit Name                                | Access | Default | Description                                                                    |  |  |  |

| 7:6 | N/A                                     | r      | N/A     | Reserved.                                                                      |  |  |  |

| 5   | FT_UVP                                  | r      | 0       | Output under-voltage fault flag. 0: no fault 1: fault, clear after readback    |  |  |  |

| 4   | FT_OLP                                  | r      | 0       | LED open fault flag. 0: no fault 1: fault, clear after readback                |  |  |  |

| 3   | FT_SLP                                  | r      | 0       | LED short fault flag. 0: no fault 1: fault, clear after readback               |  |  |  |

| 2   | FT_OTP                                  | r      | 0       | Thermal shutdown fault flag. 0: no fault 1: fault, clear after readback        |  |  |  |

| 1   | FT_OCP                                  | r      | 0       | Over-current protection fault flag. 0: no fault 1: fault, clear after readback |  |  |  |

| 0   | FT_OVP                                  | r      | 0       | Output voltage OVP fault flag. 0: no fault 1: fault, clear after readback      |  |  |  |

© 2017 MPS. All Rights Reserved.

### APPLICATION INFORMATION

### **Selecting the Input Capacitor**

The input capacitor reduces the surge current drawn from the input supply and the switching noise from the device. The input capacitor impedance at the switching frequency should be much less than the input source impedance to prevent the high-frequency switching current from passing through to the input. Ceramic capacitors with X5R or X7R dielectrics are recommended for their low ESR and small temperature coefficients. For most applications, a  $1 \sim 4.7 \mu F$  ceramic capacitor is sufficient.

#### Selecting the Inductor

The converter requires an inductor to supply a high output voltage while being driven by the input voltage. A larger value inductor results in less ripple current, lower peak inductor current, and less stress on the internal N-channel MOSFET. However, the larger inductor also has a larger physical size, higher series resistance, and lower saturation current.

Choose an inductor that will not saturate under the worst-case load conditions. Select the minimum inductor value to ensure that the boost converter works in continuous conduction mode (CCM) with high efficiency and good EMI performance.

Calculate the required inductance value using Equation (35) and Equation (36):

$$L \ge \frac{\eta \times V_{OUT} \times D \times (1-D)^2}{2 \times f_{SW} \times I_{LOAD}}$$

(35)

$$D = 1 - \frac{V_{IN}}{V_{OUT}} \tag{36}$$

Where  $V_{IN}$  is the input voltage,  $V_{OUT}$  is the output voltage,  $f_{SW}$  is the switching frequency,  $I_{LOAD}$  is the LED load current, and  $\eta$  is the efficiency.

The switching current is used for peak-current-mode control. To prevent hitting the current limit, the worst-case inductor peak current should be less than 80% of the current limit ( $I_{LIM}$ ). For most applications, a 4.7 ~ 10µH inductor is sufficient.

#### **Selecting the Output Capacitor**

The output capacitor keeps the output voltage ripple small and ensures feedback loop stability. The output capacitor impedance must be low at the switching frequency. Ceramic capacitors with X7R dielectrics are recommended for their low ESR characteristics. Note that the ceramic capacitance is dependent on the voltage rating. With a DC bias voltage, the capacitance can lose as much as 50% of its value at its rated voltage rating. Leave a large enough voltage rating margin when selecting the component. Too low a capacitance value causes loop instability. For most applications, a 10µF ceramic capacitor is sufficient.

### Selecting the External Schottky Diode

To optimize the efficiency, a high-speed and low reverse-recovery current Schottky diode are recommended. Make sure the diode's average and peak current ratings exceed the output average LED current and the peak inductor current. In addition, the diode's break-down voltage rating should be large than the maximum voltage across the diode. Usually, unexpected high-frequency voltage spikes can be seen across the diode when the diode turns off. Therefore, leaving some voltage rating margin is always needed to guarantee normal long-term operation when selecting a diode.

#### **PCB Layout Guidelines**

Efficient PCB layout is critical for stable operation. Proper layout of the high-frequency switching path is critical to prevent noise and electromagnetic interference problems. For best results, refer to the guidelines below.

- Minimize the loop of MP3313's internal LS-FET, Schottky diode, and output capacitor, since it is flowing with high-frequency ripple current.

- 2. Place the input and output capacitors as close to the IC as possible.

# TYPICAL APPLICATION CIRCUIT

Figure 4: Typical Application for Single-String 3\*7LEDs, 20mA/String

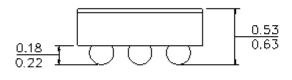

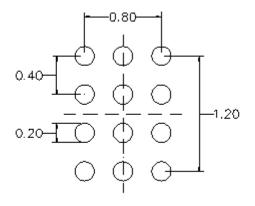

## **PACKAGE INFORMATION**

## **CSP12 (1.3mmx1.7mm)**

#### SIDE VIEW

#### NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) BALL COPLANARITY SHALL BE 0.05 MILLIMETER MAX.

- 3) JEDEC REFERENCE IS MO-211.

- 4) DRAWING IS NOT TO SCALE.

#### RECOMMENDED LAND PATTERN

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.