# 77 GHz Medium Power Amplifier

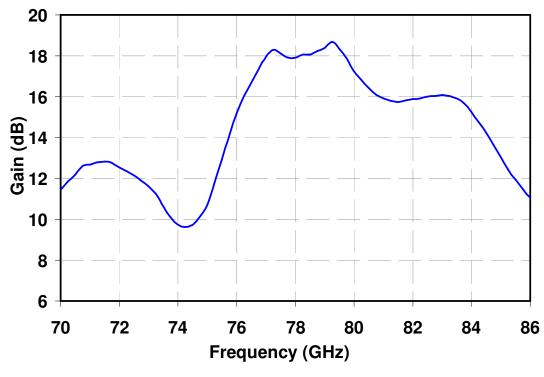

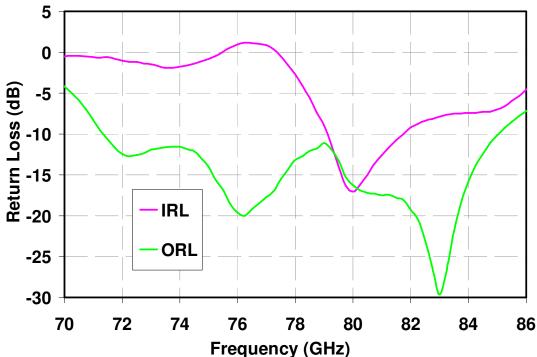

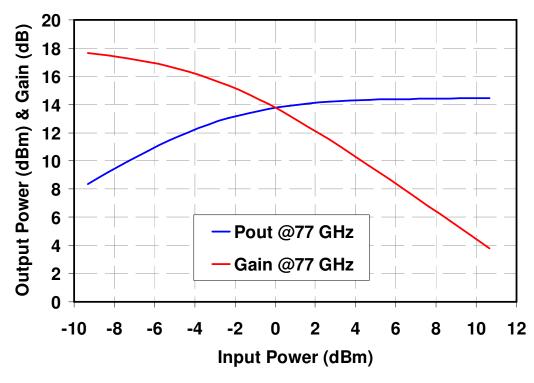

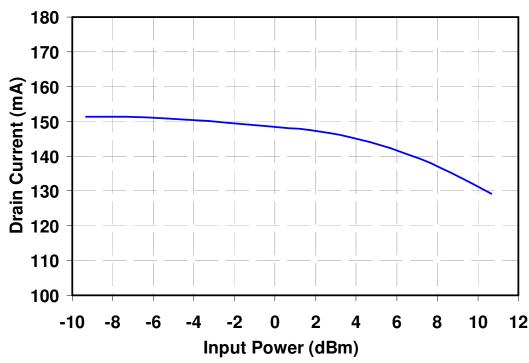

#### **Measured Performance**

#### **Key Features**

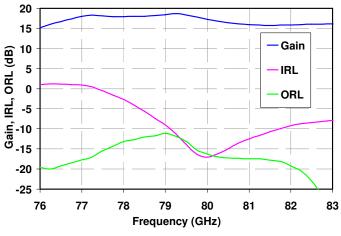

- Frequency Range: 76 83 GHz

- Psat: 14 dBm at 77 GHz

- Gain: 15 dB

- Bias: Vd = 3.5 V, Vg = +0.2 V, Idq = 125 mA

- Typical

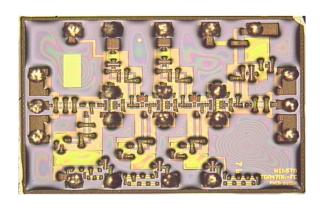

- Technology: 0.13 um pHEMT with front-side

- Cu/Sn pillars

- Chip Dimensions: 1.86 x 1.37 x 0.38 mm

### **Primary Applications**

- Automotive Radar

- E-Band Communication

### **Product Description**

The TriQuint TGA4706-FC is a flip-chip medium power amplifier designed to operate at the automotive radar frequencies band. The TGA4706-FC is designed using TriQuint's proven 0.13  $\mu m$  pHEMT process and front-side Cu / Sn pillar technology for simplified assembly and low interconnect inductance. Die reliability is enhanced by using TriQuint's BCB polymeric passivation process.

The TGA4706-FC typically provides 14 dBm saturated output power with 15 dB small signal gain at 77 GHz.

Lead-free and RoHS compliant.

Table I

Absolute Maximum Ratings 1/

| Symbol | Parameter                   | Value         | Notes |

|--------|-----------------------------|---------------|-------|

| Vd-Vg  | Drain to Gate Voltage       | 6 V           |       |

| Vd     | Drain Voltage               | 4 V           | 2/    |

| Vg     | Gate Voltage Range          | -2 to +0.45 V |       |

| ld     | Drain Current               | 240 mA        | 2/    |

| lg     | Gate Current                | 4 mA          |       |

| Pin    | Input Continuous Wave Power | 15 dBm        | 2/    |

- 1/ These ratings represent the maximum operable values for this device. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device and / or affect device lifetime. These are stress ratings only, and functional operation of the device at these conditions is not implied.

- 2/ Combinations of supply voltage, supply current, input power, and output power shall not exceed the maximum power dissipation listed in Table IV.

# Table II Recommended Operating Conditions

| Symbol | Parameter 1/              | Value  |

|--------|---------------------------|--------|

| Vd     | Drain Voltage             | 3.5 V  |

| Vg     | Gate Voltage              | +0.2 V |

| ldq    | Drain Current (Quiescent) | 125 mA |

1/ See assembly diagram for bias instructions.

# Table III RF Characterization Table

Bias conditions: Vd = 3.5 V, Vg = +0.2 V, Idq = 125 mA Typical

| SYMBOL | PARAMETER                           | TEST<br>CONDITIONS | MINIMUM | NOMINAL | UNITS |

|--------|-------------------------------------|--------------------|---------|---------|-------|

| Gain   | Small Signal Gain                   | f = 76-77 GHz      |         | 15      | dB    |

| IRL    | Input Return Loss                   | f = 76-77 GHz      |         | 4       | dB    |

| ORL    | Output Return Loss                  | f = 76-77 GHz      |         | 15      | dB    |

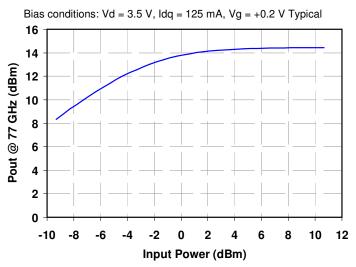

| Psat   | Saturated Output<br>Power           | f = 77 GHz         |         | 14      | dBm   |

| Pout   | Output Power (Input<br>Power=-3dBm) | f = 77 GHz         | 9       | 12      | dBm   |

# Table IV Power Dissipation and Thermal Properties

| Parameter                                 | Test Conditions                                                                 | Value                                                      | Notes |

|-------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------|-------|

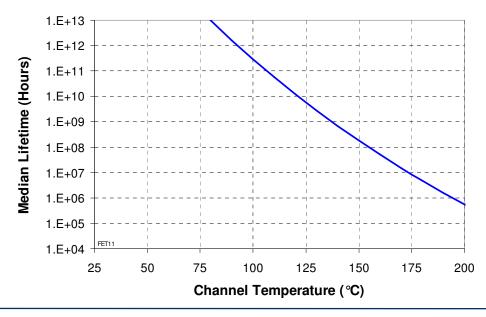

| Maximum Power Dissipation                 | Tbaseplate = 130.0 ℃                                                            | Pd = 0.6 W<br>Tchannel = 150 ℃<br>Tm = 2.4E+7 Hrs          | 1/ 2/ |

| Thermal Resistance, θjc<br>Under RF Drive | Vd = 3.5 V<br>Vg = +0.2 V<br>Idq = 125 mA<br>Pd = 0.438 W<br>Tbaseplate = 85 °C | θjc = 33.3 (°C/W)<br>Tchannel = 93.8°C<br>Tm = 3.2E+10 Hrs |       |

| Mounting Temperature                      |                                                                                 | Refer to Solder Reflow<br>Profiles (pp 10)                 |       |

| Storage Temperature                       |                                                                                 | -65 to 150℃                                                |       |

- 1/ For a median life of 2.4E+07 hours, Power Dissipation is limited to  $Pd(max) = (150 \, ^{\circ}C Tbase \, ^{\circ}C)/\theta jc.$

- 2/ Channel operating temperature will directly affect the device median time to failure (MTTF). For maximum life, it is recommended that channel temperatures be maintained at the lowest possible levels.

#### Median Lifetime (Tm) vs Channel Temperature

# Measured Data on Flipped Die on Carrier Board

Bias conditions: Vd = 3.5 V, Vg = +0.2 V, Idq = 125 mA Typical

# Measured Data on Flipped Die on Carrier Board

Bias conditions: Vd = 3.5 V, Vg = +0.2 V, Idq = 125 mA Typical

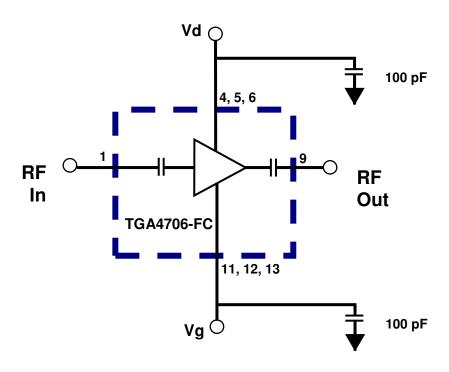

#### **Electrical Schematic**

# **Bias Procedures**

| Bias-up | <b>Procedure</b> |

|---------|------------------|

|---------|------------------|

Vg set to -0.6 V

Vd set to +3.5 V

Adjust Vg more positive until Vg is +0.2 V. Id will be  $\sim 125$  mA

Apply RF signal to input

#### **Bias-down Procedure**

Turn off RF supply

Reduce Vg to -0.6V. Ensure Id ~ 0 mA

Turn Vd to 0 V

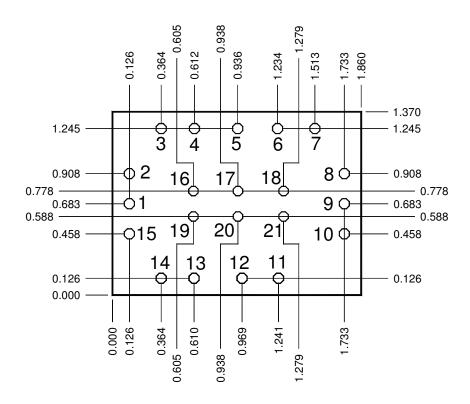

### Mechanical Drawing Drawing is for chip face-up

Units: millimeters Thickness: 0.380

Die x,y size tolerance: +/- 0.050

Chip edge to pillar dimensions are shown to center of pillar

| Pillar # 1                                   | RF IN         | 0.075 Ø |

|----------------------------------------------|---------------|---------|

| Pillar # 9                                   | RF OUT        | 0.075 Ø |

| Pillar # 4                                   | Vd1           | 0.075 Ø |

| Pillar # 5                                   | Vd2           | 0.075 Ø |

| Pillar # 6                                   | Vd3           | 0.075 Ø |

| Pillar # 11                                  | Vg3           | 0.075 Ø |

| Pillar # 12                                  | Vg2           | 0.075 Ø |

| Pillar # 13                                  | Vg1           | 0.075 Ø |

| Pillar # 2, 8, 10, 15                        | RF CPW Ground | 0.075 Ø |

| Pillar # 3, 7, 14, 16,<br>17, 18, 19, 20, 21 | DC Ground     | 0.075 Ø |

GaAs MMIC devices are susceptible to damage from Electrostatic Discharge. Proper precautions should be observed during handling, assembly and test.

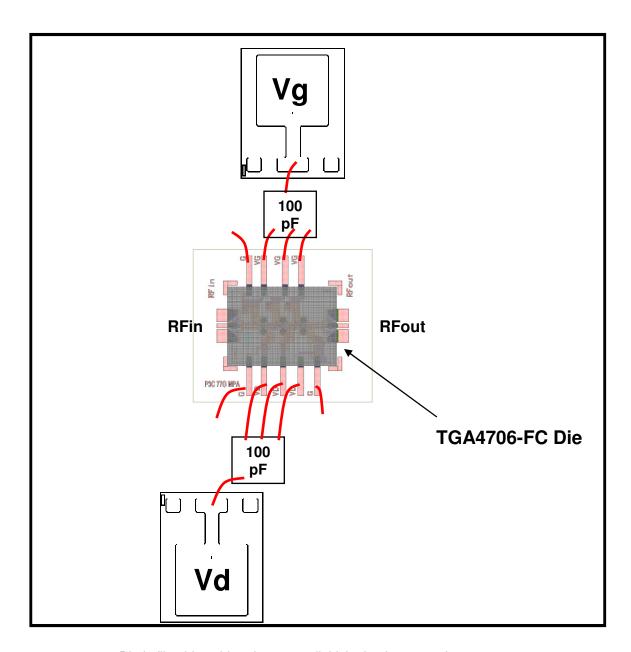

# **Recommended Assembly Diagram**

Die is flip-chip soldered to a 15 mil thick alumina test substrate

GaAs MMIC devices are susceptible to damage from Electrostatic Discharge. Proper precautions should be observed during handling, assembly and test.

## **Assembly Notes**

Component placement and die attach assembly notes:

- · Vacuum pencils and/or vacuum collets are the preferred method of pick up.

- · Air bridges must be avoided during placement.

- Cu pillars on die are 65 um tall with a 22 um tall Sn solder cap.

- Recommended board metallization is evaporated TiW followed by nickel/gold at pillar attach interface. Ni is the adhesion layer for

the solder and the gold keeps the Ni from oxidizing. The Au should be kept to a minimum to avoid embrittlement; suggested Au /

Sn mass ratio must not exceed 8%.

- Au metallization is not recommended on traces due to solder wicking and consumption concerns. If Au traces are used, a physical

solder barrier must be applied or designed into the pad area of the board. The barrier must be sufficient to keep the solder from

undercutting the barrier.

#### Reflow process assembly notes:

- Minimum alloying temperatures 245 °C.

- · Repeating reflow cycles is not recommended due to Sn consumption on the first reflow cycle.

- · An alloy station or conveyor furnace with an inert atmosphere such as N2 should be used.

- Dip copper pillars in "no-clean flip chip" flux prior to solder attach. Suggest using a high temperature flux. Avoid exposing entire die to flux.

- If screen printing flux, use small apertures and minimize volume of flux applied.

- · Coefficient of thermal expansion matching between the MMIC and the substrate/board is critical for long-term reliability.

- · Devices must be stored in a dry nitrogen atmosphere.

- · Suggested reflow will depend on board material and density.

# Typical Reflow Profiles for TriQuint Cu / Sn Pillars

| Process                              | Sn Reflow                   |

|--------------------------------------|-----------------------------|

| Ramp-up Rate                         | 3 °C/sec                    |

| Flux Activation Time and Temperature | 60 - 120 sec @ 140 - 160 °C |

| Time above Melting Point (245 °C)    | 60 – 150 sec                |

| Max Peak Temperature                 | 300 °C                      |

| Time within 5 °C of Peak Temperature | 10 – 20 sec                 |

| Ramp-down Rate                       | 4 – 6 °C/sec                |

## **Ordering Information**

| Part       | Package Style |

|------------|---------------|

| TGA4706-FC | GaAs MMIC Die |

GaAs MMIC devices are susceptible to damage from Electrostatic Discharge. Proper precautions should be observed during handling, assembly and test.