## Features

- TTL Logic Level Inputs for 3.3V Logic Interfaces

- Smart Logic for Power Up / Hot Plug State Control

- Monolithic IC Reliability

- Low Matched R<sub>ON</sub>

- · Eliminates the Need for Zero-Cross Switching

- Flexible Switch Timing to Transition from Ringing Mode to Talk Mode.

- Clean, Bounce-Free Switching

- Tertiary Protection Consisting of Integrated Current Limiting, Voltage Clamping, and Thermal Shutdown for SLIC Protection

- 5V Operation with Power Consumption < 10 mW</li>

- Intelligent Battery Monitor

- Latched Logic-Level Inputs, no External Drive Circuitry Required

- Small 16-pin SOIC Package

# **Applications**

- VoIP Gateways

- Central office (CO)

- Digital Loop Carrier (DLC)

- PBX Systems

- Digitally Added Main Line (DAML)

- Hybrid Fiber Coax (HFC)

- Fiber in the Loop (FITL)

- Pair Gain System

- Channel Banks

## Description

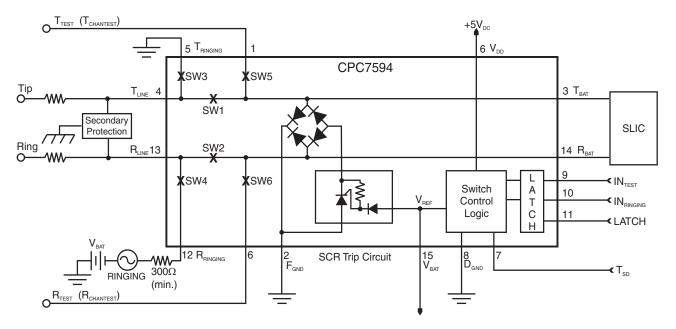

The CPC7594 is a member of IXYS Integrated Circuits Division's next generation Line Card Access Switch family. This monolithic 6-pole solid-state switch is available in a 16-pin SOIC package. It provides the necessary functions to replace two 2-Form-C electro-mechanical relays used on traditional analog and contemporary integrated voice and data (IVD) line cards found in Central Office, Access, and PBX equipment. Because this device contains solid state switches for tip and ring line break, ringing injection/return, and channel test access, it requires only a +5V supply for operation, and TTL logic-level inputs for control.

The CPC7594 is particularly designed for IVD line cards where an EMR is required for line test due to the high frequencies typical of ADSL, but solid-state switches are desired for switching and test-in functions.

# **Ordering Information**

| Part #      | Description                                 |

|-------------|---------------------------------------------|

| CPC7594BA   | 16-Pin SOIC, with Protection SCR, 50/Tube   |

| CPC7594BATR | 16-Pin SOIC, with Protection SCR, 1000/Reel |

# Figure 1. CPC7594 Block Diagram

| 1. Specifications                                                             | 2   |

|-------------------------------------------------------------------------------|-----|

| 1.1 Package Pinout                                                            |     |

| 1.1 Fackage Fillout                                                           |     |

|                                                                               |     |

| 1.3 Absolute Maximum Ratings                                                  |     |

| 1.4 ESD Rating                                                                |     |

| 1.5 General Conditions                                                        |     |

| 1.6 Switch Specifications                                                     |     |

| 1.6.1 Break Switches, SW1 and SW2                                             | . 5 |

| 1.6.2 Ringing Return Switch, SW3.                                             | . 6 |

| 1.6.3 Ringing Switch, SW4                                                     | . / |

| 1.6.4 Test Switches, SW5 and SW6<br>1.7 Digital I/O Electrical Specifications | . 8 |

| 1.8 Voltage and Power Specifications                                          |     |

|                                                                               |     |

| 1.9 Protection Circuitry Electrical Specifications                            |     |

| 1.10 Truth Tables.                                                            | 11  |

| 1.10.1 CPC7594xA and CPC7594xB Truth Table                                    | 11  |

| 1.10.2 CPC7594xC Truth Table                                                  | 11  |

| 2. Functional Description                                                     | 12  |

| 2.1 Introduction                                                              |     |

| 2.1.1 CPC7594xA and CPC7594xB Logic States                                    |     |

| 2.1.1 CPC/594XA and CPC/594XB Logic States                                    | 12  |

| 2.2 Under Voltage Switch Lock Out Circuitry.                                  | 12  |

| 2.2.1 Introduction                                                            |     |

| 2.2.2 Hot Plug and Power Up Circuit Design Considerations                     | 13  |

| 2.3 Switch Logic.                                                             | 13  |

| 2.3.1 Start-up                                                                |     |

| 2.3.2 Switch Timing                                                           | 13  |

| 2.3.3 Make-Before-Break Operation                                             | 14  |

| 2.3.4 Break-Before-Make Operation                                             | 14  |

| 2.3.5 Alternate Break-Before-Make Operation.                                  | 15  |

| 2.4 Data Latch                                                                |     |

| 2.5 T <sub>SD</sub> Pin Description                                           |     |

| 2.6 Ringing Switch Zero-Cross Current Turn Off                                |     |

| 2.7 Power Supplies                                                            |     |

| 2.8 Battery Voltage Monitor                                                   | 17  |

| 2.9 Protection.                                                               | 17  |

| 2.9.1 Diode Bridge/SCR.                                                       | 17  |

| 2.9.2 Current Limiting function                                               |     |

| 2.10 Thermal Shutdown.                                                        |     |

| 2.11 External Protection Elements.                                            | 18  |

|                                                                               |     |

| 3. Manufacturing Information                                                  |     |

| 3.1 Moisture Sensitivity                                                      | 19  |

| 3.2 ESD Sensitivity                                                           | 19  |

| 3.3 Reflow Profile.                                                           | 19  |

| 3.4 Board Wash                                                                | 19  |

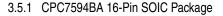

| 3.5 Mechanical Dimensions                                                     |     |

| 3.5.1 CPC7594BA 16-Pin SOIC Package                                           |     |

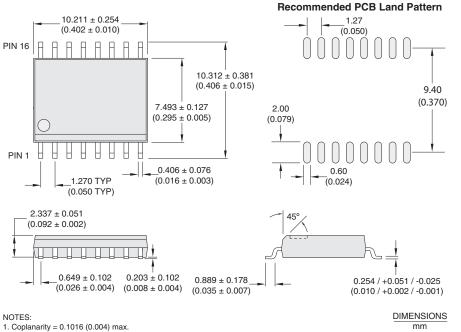

| 3.5.2 CPC7594BATR Tape & Reel                                                 |     |

|                                                                               |     |

# 1. Specifications

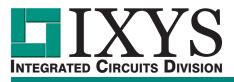

# 1.1 Package Pinout

### 1.2 Pinout

| Pin | Name                  | Description                     |

|-----|-----------------------|---------------------------------|

| 1   | T <sub>TEST</sub>     | Tip lead of the test bus        |

| 2   | F <sub>GND</sub>      | Fault ground                    |

| 3   | T <sub>BAT</sub>      | Tip lead to the SLIC            |

| 4   | T <sub>LINE</sub>     | Tip lead of the line side       |

| 5   | T <sub>RINGING</sub>  | Ringing generator return        |

| 6   | V <sub>DD</sub>       | +5 V supply                     |

| 7   | T <sub>SD</sub>       | Temperature shutdown pin        |

| 8   | D <sub>GND</sub>      | Digital ground                  |

| 9   | IN <sub>TEST</sub>    | Logic control input             |

| 10  | IN <sub>RINGING</sub> | Logic control input             |

| 11  | LATCH                 | Data latch enable control input |

| 12  | R <sub>RINGING</sub>  | Ringing generator source        |

| 13  | R <sub>LINE</sub>     | Ring lead of the line side      |

| 14  | R <sub>BAT</sub>      | Ring lead to the SLIC           |

| 15  | V <sub>BAT</sub>      | Battery supply                  |

| 16  | R <sub>TEST</sub>     | Ring lead of the test bus       |

#### **1.3 Absolute Maximum Ratings**

| Parameter                                                     | Minimum | Maximum               | Unit |

|---------------------------------------------------------------|---------|-----------------------|------|

| +5V power supply (V <sub>DD</sub> )                           | -0.3    | 7                     | V    |

| Battery Supply                                                | -       | -85                   | V    |

| D <sub>GND</sub> to F <sub>GND</sub> Separation               | -5      | +5                    | V    |

| Logic input voltage                                           | -0.3    | V <sub>DD</sub> + 0.3 | V    |

| Logic input to switch output isolation                        | -       | 320                   | V    |

| Switch open-contact<br>isolation (SW1, SW2, SW3,<br>SW5, SW6) | -       | 320                   | V    |

| Switch open-contact<br>Isolation (SW4)                        | -       | 465                   | V    |

| Operating relative humidity                                   | 5       | 95                    | %    |

| Operating temperature                                         | -40     | +110                  | °C   |

| Storage temperature                                           | -40     | +150                  | ٥C   |

Absolute maximum electrical ratings are at 25°C.

Absolute Maximum Ratings are stress ratings. Stresses in excess of these ratings can cause permanent damage to the device. Functional operation of the device at conditions beyond those indicated in the operational sections of this data sheet is not implied.

#### 1.4 ESD Rating

| ESD Rating (Human Body Model) |

|-------------------------------|

| 1000 V                        |

#### **1.5 General Conditions**

Unless otherwise specified, minimum and maximum values are guaranteed by production testing requirements.

Typical values are characteristic of the device at 25° C and are the result of engineering evaluations. They are provided for information purposes only and are not part of the testing requirements.

Specifications cover the operating temperature range  $T_A = -40^{\circ}$  C to  $+85^{\circ}$  C. Also, unless otherwise specified all testing is performed with  $V_{DD} = 5 V_{dc}$ , logic low input voltage is 0  $V_{dc}$  and logic high voltage is 5  $V_{dc}$ .

## **1.6 Switch Specifications**

1.6.1 Break Switches, SW1 and SW2

| Parameter                                                                                                                                    | Test Conditions                                                                                                            | Symbol          | Minimum | Typical                                                  | Maximum | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------|---------|----------------------------------------------------------|---------|------|

|                                                                                                                                              | $V_{SW1}$ (differential) = $T_{LINE}$ to $T_{BAT}$<br>$V_{SW2}$ (differential) = $R_{LINE}$ to $R_{BAT}$<br>All-Off state. |                 |         |                                                          |         |      |

| Off-State<br>Leakage Current<br>On Resistance<br>On Resistance<br>Matching<br>DC current limit<br>Dynamic current limit<br>(t $\leq$ 0.5 µs) | +25° C,<br>V <sub>SW</sub> (differential) = -320 V to gnd<br>V <sub>SW</sub> (differential) = +260 V to -60 V              |                 |         | 0.1                                                      |         |      |

|                                                                                                                                              | +85° C,<br>V <sub>SW</sub> (differential) = -330 V to gnd<br>V <sub>SW</sub> (differential) = +270 V to -60 V              | I <sub>SW</sub> | -       | 0.3                                                      | 1       | μΑ   |

|                                                                                                                                              | -40° C,<br>V <sub>SW</sub> (differential) = -310 V to gnd<br>V <sub>SW</sub> (differential) = +250 V to -60 V              |                 |         | 0.1                                                      |         |      |

|                                                                                                                                              | $I_{SW}(on) = \pm 10$ mA, $\pm 40$ mA, $R_{BAT}$ and $T_{BAT} = -2$ V                                                      |                 |         |                                                          |         |      |

|                                                                                                                                              | +25° C                                                                                                                     | R <sub>ON</sub> | -       | 14.7                                                     | -       |      |

|                                                                                                                                              | +85° C                                                                                                                     |                 |         | 21.1                                                     | 28      | Ω    |

|                                                                                                                                              | -40° C                                                                                                                     |                 |         | 21.1     28       10.7     -       0.15     0.8          | -       |      |

| On Resistance<br>Matching                                                                                                                    | Per SW1 & SW2 On Resistance test<br>conditions.                                                                            | $\Delta R_{ON}$ | -       | 0.15                                                     | 0.8     | Ω    |

|                                                                                                                                              | $V_{SW}$ (on) = ±10 V, +25° C                                                                                              |                 | -       | 300                                                      |         | mA   |

| DC current limit                                                                                                                             | $V_{SW}$ (on) = ±10 V, +85° C                                                                                              | I <sub>SW</sub> | 80      | 160                                                      | -       |      |

|                                                                                                                                              | $V_{SW}$ (on) = ±10 V, -40° C                                                                                              |                 | -       | 0.3<br>0.1<br>0.1<br>14.7<br>21.1<br>10.7<br>0.15<br>300 | 425     |      |

| Dynamic current limit $(t \le 0.5 \ \mu s)$                                                                                                  | Break switches on, all other switches off. Apply $\pm 1$ kV 10x1000 $\mu$ s pulse with appropriate protection in place.    | I <sub>SW</sub> | -       | 2.5                                                      | -       | A    |

|                                                                                                                                              | +25° C, Logic inputs = gnd,<br>V <sub>SW</sub> (T <sub>LINE</sub> , R <sub>LINE</sub> ) = $\pm$ 320 V                      |                 | -       | 0.1                                                      |         |      |

| Logic input to switch<br>output isolation                                                                                                    | +85° C, Logic inputs = gnd, $V_{SW}$ (T <sub>LINE</sub> , R <sub>LINE</sub> ) = ±330 V                                     | I <sub>SW</sub> | -       | 0.3                                                      | 1       | μΑ   |

|                                                                                                                                              | -40° C, Logic inputs = gnd,<br>V <sub>SW</sub> (T <sub>LINE</sub> , R <sub>LINE</sub> ) = $\pm$ 310 V                      |                 | -       | 0.1                                                      |         |      |

| dV/dt sensitivity                                                                                                                            | -                                                                                                                          | -               | -       | 500                                                      | -       | V/µs |

# 1.6.2 Ringing Return Switch, SW3

| Parameter                                                      | Test Conditions                                                                                                                          | Symbol                                                                  | Minimum | Typical | Maximum  | Unit |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------|---------|----------|------|

|                                                                | $V_{SW3}$ (differential) = $T_{LINE}$ to $T_{RINGING}$<br>All-Off state.                                                                 |                                                                         |         |         |          |      |

| _                                                              | +25° C,<br>V <sub>SW</sub> (differential) = -320 V to gnd<br>V <sub>SW</sub> (differential) = +260 V to -60 V                            |                                                                         |         | 0.1     |          |      |

| Off-State<br>Leakage Current                                   | +85° C,<br>V <sub>SW</sub> (differential) = -330 V to gnd<br>V <sub>SW</sub> (differential) = +270 V to -60 V                            | I <sub>SW</sub>                                                         | -       | 0.3     | 1        | μΑ   |

|                                                                | -40° C,<br>V <sub>SW</sub> (differential) = -310 V to gnd<br>V <sub>SW</sub> (differential) = +250 V to -60 V                            |                                                                         |         | 0.1     |          |      |

| Vs Vs   On Resistance Is   Is Vs   DC current limit Vs   Vs Vs | $I_{SW}(on) = \pm 0 \text{ mA}, \pm 10 \text{ mA}, \pm 25^{\circ} \text{ C}$                                                             | R <sub>ON</sub>                                                         | -       | 51      | -        | Ω    |

|                                                                | $I_{SW}(on) = \pm 0 \text{ mA}, \pm 10 \text{ mA}, +85^{\circ} \text{ C}$                                                                |                                                                         |         | 75      | 100<br>- |      |

|                                                                | $I_{SW}(on) = \pm 0 \text{ mA}, \pm 10 \text{ mA}, -40^{\circ} \text{ C}$                                                                |                                                                         |         | 39      |          |      |

|                                                                | $V_{SW}$ (on) = ± 10 V, +25° C                                                                                                           |                                                                         |         |         |          |      |

| DC current limit                                               | $V_{SW}$ (on) = ± 10 V, +85° C                                                                                                           | $\begin{array}{c c c c c c c c } & & & & & & & & & & & & & & & & & & &$ | 85      | -       | mA       |      |

|                                                                | $V_{SW}$ (on) = ± 10 V, -40° C                                                                                                           |                                                                         | -       | 210     |          |      |

| Dynamic current limit $(t \le 0.5 \ \mu s)$                    | Ringing switches on, all other switches off. Apply $\pm 1 \text{ kV} 10x1000 \ \mu \text{s}$ pulse with appropriate protection in place. | I <sub>SW</sub>                                                         | -       | 2.5     | -        | A    |

|                                                                | +25° C, Logic inputs = gnd,<br>$V_{SW}$ (T <sub>RINGING</sub> , T <sub>LINE</sub> ) = ±320 V                                             |                                                                         |         | 0.1     |          |      |

| Logic input to switch<br>output isolation                      | +85° C, Logic inputs = gnd,<br>V <sub>SW</sub> (T <sub>RINGING</sub> , T <sub>LINE</sub> ) = ±330 V                                      | I <sub>SW</sub>                                                         | -       | 0.3     | 1        | μA   |

|                                                                | -40° C, Logic inputs = gnd,<br>V <sub>SW</sub> (T <sub>RINGING</sub> , T <sub>LINE</sub> ) = ±310 V                                      |                                                                         |         | 0.1     |          |      |

| dV/dt sensitivity                                              | -                                                                                                                                        | -                                                                       | -       | 500     | -        | V/µs |

# 1.6.3 Ringing Switch, SW4

| Parameter                                                                                                                                                                                             | Test Conditions                                                                                                                                                                                              | Symbol               | Minimum | Typical | Maximum | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------|---------|---------|------|

|                                                                                                                                                                                                       | $V_{SW4}$ (differential) = $R_{LINE}$ to $R_{RINGING}$<br>All-Off state.                                                                                                                                     |                      |         |         |         |      |

| Off-State<br>Leakage Current<br>On Resistance<br>On Voltage<br>On-State<br>Leakage Current<br>Steady-State Current*<br>Surge Current*<br>Release Current<br>Logic input to switch<br>output isolation | +25° C<br>V <sub>SW</sub> (differential) = -255 V to +210 V<br>V <sub>SW</sub> (differential) = +255 V to -210 V                                                                                             | I <sub>SW</sub>      |         | 0.05    |         |      |

|                                                                                                                                                                                                       | +85° C<br>V <sub>SW</sub> (differential) = -270 V to +210 V<br>V <sub>SW</sub> (differential) = +270 V to -210 V                                                                                             |                      | -       | 0.1     | 1       | μΑ   |

|                                                                                                                                                                                                       | $\begin{array}{l} -40^{\circ} \mbox{ C} \\ \mbox{V}_{SW} \mbox{ (differential)} = -245 \mbox{ V to } +210 \mbox{ V} \\ \mbox{V}_{SW} \mbox{ (differential)} = +245 \mbox{ V to } -210 \mbox{ V} \end{array}$ |                      |         | 0.05    |         |      |

| On Resistance                                                                                                                                                                                         | $I_{SW}$ (on) = ±70 mA, ±80 mA                                                                                                                                                                               | R <sub>ON</sub>      | -       | 6       | 15      | Ω    |

| On Voltage                                                                                                                                                                                            | $I_{SW}$ (on) = ± 1 mA                                                                                                                                                                                       | V <sub>ON</sub>      | -       | 1.5     | 3       | V    |

|                                                                                                                                                                                                       | Inputs set for ringing -Measure ringing generator current to ground.                                                                                                                                         | I <sub>RINGING</sub> | -       | 0.1     | 0.25    | mA   |

| Steady-State Current*                                                                                                                                                                                 | Inputs set for ringing mode.                                                                                                                                                                                 | I <sub>SW</sub>      | -       | -       | 150     | mA   |

| Surge Current*                                                                                                                                                                                        | Ringing switches on, all other switches off. Apply $\pm 1 \text{ kV}$ 10x1000 $\mu$ s pulse with appropriate protection in place.                                                                            | I <sub>SW</sub>      | -       | -       | 2       | A    |

| Release Current                                                                                                                                                                                       | SW4 transition from on to off.                                                                                                                                                                               | I <sub>RINGING</sub> | -       | 420     | -       | μA   |

|                                                                                                                                                                                                       | +25° C, Logic inputs = gnd,<br>$V_{SW}$ (R <sub>RINGING</sub> , R <sub>LINE</sub> ) = ±320 V                                                                                                                 |                      |         | 0.10    |         |      |

|                                                                                                                                                                                                       | +85° C, Logic inputs = gnd,<br>V <sub>SW</sub> (R <sub>RINGING</sub> , R <sub>LINE</sub> ) = ±330 V                                                                                                          | I <sub>SW</sub>      | -       | 0.12    | 1       | μΑ   |

| ouput isolation                                                                                                                                                                                       | -40° C, Logic inputs = gnd,<br>V <sub>SW</sub> (R <sub>RINGING</sub> , R <sub>LINE</sub> ) = $\pm$ 310 V                                                                                                     |                      |         | 0.10    |         |      |

| dV/dt sensitivity                                                                                                                                                                                     | -                                                                                                                                                                                                            | -                    | -       | 500     | -       | V/µs |

| *Secondary protection and                                                                                                                                                                             | current limiting must prevent exceeding this para                                                                                                                                                            | ameter.              |         |         |         |      |

#### 1.6.4 Test Switches, SW5 and SW6

| Parameter                                   | Test Conditions                                                                                                                        | Symbol          | Minimum           | Typical                                                                                                                            | Maximum | Unit |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------|---------|------|

|                                             | $V_{SW1}$ (differential) = $T_{TEST}$ to $T_{BAT}$<br>$V_{SW2}$ (differential) = $R_{TEST}$ to $R_{BAT}$<br>All-Off state.             |                 |                   |                                                                                                                                    |         |      |

| Off-State                                   | +25° C,<br>V <sub>SW</sub> (differential) = -320 V to gnd<br>V <sub>SW</sub> (differential) = +260 V to -60 V                          |                 |                   | 0.1                                                                                                                                |         |      |

| Leakage Current                             | +85° C,<br>V <sub>SW</sub> (differential) = -330 V to gnd<br>V <sub>SW</sub> (differential) = +270 V to -60 V                          | I <sub>SW</sub> | I <sub>SW</sub> - | 0.2                                                                                                                                | 1       | μA   |

|                                             | -40° C,<br>V <sub>SW</sub> (differential) = -310 V to gnd<br>V <sub>SW</sub> (differential) = +250 V to -60 V                          |                 |                   | 0.1                                                                                                                                |         |      |

| On Resistance                               | $I_{SW}(on) = \pm 10$ mA, $\pm 40$ mA, R <sub>BAT</sub> and T <sub>BAT</sub> = -2 V                                                    |                 |                   |                                                                                                                                    |         |      |

|                                             | +25° C                                                                                                                                 |                 |                   | 38                                                                                                                                 | -       |      |

|                                             |                                                                                                                                        | 70              | Ω                 |                                                                                                                                    |         |      |

|                                             | -40° C                                                                                                                                 |                 |                   | 28                                                                                                                                 | -       |      |

|                                             | $V_{SW}$ (on) = ±10 V, +25° C                                                                                                          |                 | -                 | 125                                                                                                                                |         |      |

| DC current limit                            | $V_{SW}$ (on) = ±10 V, +85° C                                                                                                          | I <sub>SW</sub> | 80                | 95                                                                                                                                 | -       | mA   |

|                                             | $V_{SW}$ (on) = ±10 V, -40° C                                                                                                          |                 | -                 | 0.1       0.1       38       46       28       -       125       80       95       -       165       -       2.5       -       0.1 | 250     |      |

| Dynamic current limit $(t \le 0.5 \ \mu s)$ | Break switches on, all other switches off. Apply $\pm 1 \text{ kV} 10x1000 \ \mu \text{s}$ pulse with appropriate protection in place. | I <sub>SW</sub> | -                 | 2.5                                                                                                                                | -       | A    |

| Logic input to switch output isolation      | +25° C, Logic inputs = gnd, $V_{SW}$ (T <sub>LINE</sub> , R <sub>LINE</sub> ) = ±320 V                                                 |                 | -                 | 0.1                                                                                                                                |         |      |

|                                             | +85° C, Logic inputs = gnd, $V_{SW}$ (T <sub>LINE</sub> , R <sub>LINE</sub> ) = ±330 V                                                 | I <sub>SW</sub> | -                 | 0.3                                                                                                                                | 1       | μΑ   |

|                                             | -40° C, Logic inputs = gnd, $V_{SW}$ (T <sub>LINE</sub> , R <sub>LINE</sub> ) = ±310 V                                                 |                 | -                 | 0.1                                                                                                                                |         |      |

| dV/dt sensitivity                           | -                                                                                                                                      | -               | -                 | 500                                                                                                                                | -       | V/µs |

# 1.7 Digital I/O Electrical Specifications

| Parameter                                                                              | Test Conditions                                                                                                       | Symbol               | Minimum | Typical         | Maximum | Unit |

|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------|---------|-----------------|---------|------|

| Input Characteristics                                                                  | 1                                                                                                                     |                      |         |                 |         |      |

| Input voltage, Logic low                                                               | Input voltage falling                                                                                                 | V <sub>IL</sub>      | 0.8     | 1.0             | -       | V    |

| Input voltage, Logic high                                                              | Input voltage rising                                                                                                  | V <sub>IH</sub>      |         | 1.7             | 2.0     | v    |

| Input leakage current,<br>IN <sub>RINGING</sub> and IN <sub>TEST</sub> ,<br>Logic high | V <sub>DD</sub> = 5.5 V, V <sub>BAT</sub> = -75 V, V <sub>HI</sub> = 2.4 V                                            | IIH                  | -       | 0.1             | 1       | μΑ   |

| Input leakage current,<br>IN <sub>RINGING</sub> and IN <sub>TEST</sub> ,<br>Logic low  | V <sub>DD</sub> = 5.5 V, V <sub>BAT</sub> = -75 V, V <sub>IL</sub> = 0.4 V                                            | IIL                  | -       | 0.1             | 1       | μΑ   |

| Input leakage current,<br>LATCH Logic high                                             | $V_{DD} = 4.5 \text{ V}, V_{BAT} = -75 \text{ V}, V_{IH} = 2.4 \text{ V}$                                             | IIH                  | 7       | 19              | -       | μΑ   |

| LATCH Pull-up<br>Minimum Load                                                          | $V_{DD} = 4.5 \text{ V}, V_{BAT} = -75 \text{ V}, I_{IN} = -10 \mu\text{A}$<br>Latch input transitions to logic high. | Logic = High         | True    |                 |         |      |

| Input leakage current,<br>LATCH Logic low                                              | $V_{DD} = 5.5 \text{ V}, V_{BAT} = -75 \text{ V}, V_{IL} = 0.4 \text{ V}$                                             | I                    | -       | 46              | 125     | μΑ   |

| Input leakage current,<br>T <sub>SD</sub> Logic high                                   | $V_{DD} = 5.5 \text{ V}, V_{BAT} = -75 \text{ V}, V_{IH} = 2.4 \text{ V}$                                             | Ι <sub>ΙΗ</sub>      | 10      | 16              | 30      | μΑ   |

| Input leakage current,<br>T <sub>SD</sub> Logic low                                    | $V_{DD} = 5.5 \text{ V}, V_{BAT} = -75 \text{ V}, V_{IL} = 0.4 \text{ V}$                                             | I <sub>IL</sub>      | 10      | 16              | 30      | μΑ   |

| <b>Output Characteristics</b>                                                          | L                                                                                                                     |                      |         | I               |         |      |

| Output voltage,<br>T <sub>SD</sub> Logic high                                          | $V_{DD}$ = 5.5 V, $V_{BAT}$ = -75 V, $I_{TSD}$ = 10 $\mu$ A                                                           | V <sub>TSD_off</sub> | 2.4     | V <sub>DD</sub> | -       | V    |

| Output voltage,<br>T <sub>SD</sub> Logic low                                           | V <sub>DD</sub> = 5.5 V, V <sub>BAT</sub> = -75 V, I <sub>TSD</sub> = 1mA                                             | $V_{TSD_{on}}$       | -       | 0               | 0.4     | V    |

# **1.8 Voltage and Power Specifications**

| Parameter                                                                       | Test Conditions                                                            | Symbol             | Minimum                | Typical         | Maximum                | Unit              |

|---------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------|------------------------|-----------------|------------------------|-------------------|

| Voltage Requirement                                                             | S                                                                          |                    |                        |                 | 1                      |                   |

| V <sub>DD</sub>                                                                 | -                                                                          | V <sub>DD</sub>    | 4.5                    | 5.0             | 5.5                    | V                 |

| V <sub>BAT</sub> <sup>1</sup>                                                   | -                                                                          | V <sub>BAT</sub>   | -19                    | -48             | -72                    | V                 |

| <sup>1</sup> V <sub>BAT</sub> is used only for inte<br>drops below approximatel | rnal protection circuitry. If V <sub>BAT</sub> rises above-10 V<br>y -15 V | the device will er | nter the all-off state | and will remain | in the all-off state i | until the battery |

| Power Specifications                                                            |                                                                            |                    |                        |                 |                        |                   |

|                                                                                 | V <sub>DD</sub> = 5 V, V <sub>BAT</sub> = -48 V,                           |                    |                        |                 |                        |                   |

| Power concumption                                                               | Measure I <sub>DD</sub> and I <sub>BAT</sub> ,                             |                    |                        |                 |                        |                   |

| rower consumption                                                               | Talk and All-Off States                                                    | Р                  | -                      | 5.5             | 10                     | mW                |

| Power Specifications                                                            | All other states                                                           | Р                  | -                      | 6.5             | 10                     | mW                |

|                                                                                 | V <sub>DD</sub> = 5 V, V <sub>BAT</sub> = -48 V                            |                    | 1                      |                 |                        |                   |

| V <sub>DD</sub> current                                                         | Talk and All-Off states                                                    | I <sub>DD</sub>    |                        | 1.1             | 2.0                    | mA                |

|                                                                                 | Ringing and Test states                                                    | I <sub>DD</sub>    | -                      | 1.3             | 2.0                    | mA                |

| V <sub>BAT</sub> current                                                        | $V_{DD}$ = 5 V, $V_{BAT}$ = -72 V, All states                              | I <sub>BAT</sub>   | -                      | 0.1             | 10                     | μA                |

# **1.9 Protection Circuitry Electrical Specifications**

| Parameter                                                 | Conditions                                                                                               | Symbol                                    | Minimum             | Typical | Maximum             | Unit |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------|---------|---------------------|------|

| Protection Diode Bridg                                    | e                                                                                                        |                                           | !                   |         | ++                  |      |

| Forward Voltage drop,<br>continuous current<br>(50/60 Hz) | Apply ± dc current limit of break switches                                                               | V <sub>F</sub>                            | -                   | 2.1     | 3.0                 | V    |

| Forward Voltage drop, surge current                       | Apply ± dynamic current limit of break switches                                                          | V <sub>F</sub>                            | -                   | 5       | -                   |      |

| Protection SCR                                            |                                                                                                          |                                           | <u> </u>            |         | <u> </u>            |      |

| Surge current                                             | -                                                                                                        | -                                         | -                   | -       | *                   | А    |

| Trigger current:                                          | SCR activates, +25° C                                                                                    | I <sub>TRIG</sub> -                       |                     | 134     |                     | mA   |

| Current into V <sub>BAT</sub> pin.                        | SCR activates, +85° C                                                                                    |                                           | -                   | 87      |                     |      |

| Hold current: Current                                     | SCR remains active, +25° C                                                                               | I <sub>HOLD</sub>                         | -                   | 250     |                     | mA   |

| through protection SCR                                    | SCR remains active, +85° C                                                                               |                                           | 110                 | 184     |                     |      |

| Gate trigger voltage                                      | I <sub>GATE</sub> = I <sub>TRIGGER</sub> §                                                               | V <sub>TBAT</sub> or<br>V <sub>RBAT</sub> | V <sub>BAT</sub> -4 | -       | V <sub>BAT</sub> -2 | V    |

| Reverse leakage current                                   | V <sub>BAT</sub> = -48 V                                                                                 | I <sub>VBAT</sub>                         | -                   | 0.02    | 1.0                 | μA   |

|                                                           | 0.5 A, t = 0.5 μs                                                                                        | V <sub>TBAT</sub> or                      |                     | -3      |                     | M    |

| On-state voltage                                          | 2.0 A, t = 0.5 μs                                                                                        | V <sub>RBAT</sub>                         | -                   | -5      |                     | V    |

| Temperature Shutdowr                                      | Specifications                                                                                           |                                           | <u> </u>            |         | <u> </u>            |      |

| Shutdown activation temperature                           | Not production tested - limits are                                                                       | T <sub>TSD_on</sub>                       | 110                 | 125     | 150                 | °C   |

| Shutdown circuit<br>hysteresis                            | guaranteed by design and Quality<br>Control sampling audits.                                             | T <sub>TSD_off</sub>                      | 10                  | -       | 25                  | °C   |

|                                                           | ith appropriate secondary protection in place.<br>I <sub>TRIGGER</sub> for the internal SCR to activate. |                                           |                     |         | . I                 |      |

### 1.10 Truth Tables

1.10.1 CPC7594xA and CPC7594xB Truth Table

| State                              | IN <sub>ringing</sub>                  | IN <sub>TEST</sub>            | LATCH                      | T <sub>SD</sub>           | Break<br>Switches | Ringing<br>Switches | Test<br>Switches |  |  |

|------------------------------------|----------------------------------------|-------------------------------|----------------------------|---------------------------|-------------------|---------------------|------------------|--|--|

| Talk                               | 0                                      | 0                             |                            |                           | On                | Off                 | Off              |  |  |

| Test                               | 0                                      | 1                             | 0                          |                           | Off               | Off<br>On<br>Off    | On               |  |  |

| Ringing                            | 1                                      | 0                             | 0                          | Z <sup>1</sup>            | Off               |                     | Off              |  |  |

| All-Off                            | 1                                      | 1                             | -                          |                           | Off               |                     | Off              |  |  |

| Latched                            | Х                                      | Х                             | 1                          |                           | Unchanged         |                     |                  |  |  |

| All-Off                            | Х                                      | Х                             | Х                          | 0                         | Off               | Off                 | Off              |  |  |

| <sup>1</sup> Z = High Impedance. E | Because T <sub>SD</sub> has an interna | al pull up at this pin, it sh | ould be controlled with an | open-collector or open-dr | ain type device.  |                     |                  |  |  |

### 1.10.2 CPC7594xC Truth Table

| State                              | IN <sub>RINGING</sub>                 | IN <sub>TEST</sub>             | LATCH                      | T <sub>SD</sub>           | Break<br>Switches | Ringing<br>Switches | Test<br>Switches |  |  |

|------------------------------------|---------------------------------------|--------------------------------|----------------------------|---------------------------|-------------------|---------------------|------------------|--|--|

| Talk                               | 0                                     | 0                              |                            |                           | On                | Off                 | Off              |  |  |

| Test/Monitor                       | 0                                     | 1                              |                            |                           | On                | Off                 | On               |  |  |

| Ringing                            | 1                                     | 0                              | 0                          | Z <sup>1</sup>            | Off               | Off On              | Off              |  |  |

| All-Off                            | 1                                     | 1                              |                            |                           | Off               | Off                 | Off              |  |  |

| Latched                            | Х                                     | Х                              | 1                          |                           | Unchanged         |                     |                  |  |  |

| All-Off                            | Х                                     | Х                              | Х                          | 0                         | Off               | Off                 | Off              |  |  |

| <sup>1</sup> Z = High Impedance. B | Because T <sub>SD</sub> has an intern | al pull up at this pin, it she | ould be controlled with an | open-collector or open-dr | ain type device.  | L                   |                  |  |  |

# 2. Functional Description

### 2.1 Introduction

- 2.1.1 CPC7594xA and CPC7594xB Logic States

- **Talk**. Break switches SW1 and SW2 closed, ringing switches SW3 and SW4 open, and test switches SW5 and SW6 open.

- **Ringing**. Break switches SW1 and SW2 open, ringing switches SW3 and SW4 closed, and test switches SW5 and SW6 open.

- **Test**. Break switches SW1 and SW2 open, ringing switches SW3 and SW4 open, and channel test switches SW5 and SW6 closed.

- All-off. Break switches SW1 and SW2 open, ringing switches SW3 and SW4 open, and test switches SW5 and SW6 open.

### 2.1.2 CPC7594xC Logic States

The CPC7594xC replaces the Test state with the Test/Monitor state as defined below.

• **Test/Monitor**. Break switches SW1 and SW2 closed, ringing switches SW3 and SW4 open, and test switches SW5 and SW6 closed.

The CPC7594 offers break-before-make and make-before-break switching from the ringing state to the talk state with simple TTL level logic input control. Solid-state switch construction means no impulse noise is generated when switching during ring cadence or ring trip, eliminating the need for external zero-cross switching circuitry. State control is via TTL logic-level input so no additional driver circuitry is required. The linear break switches SW1 and SW2 have exceptionally low RON and excellent matching characteristics. The ringing switch, SW4, has a minimum open contact breakdown voltage of 465 V at +25°C sufficiently high with proper protection to prevent breakdown in the presence of a transient fault condition (i.e., passing the transient on to the ringing generator).

Integrated into the CPC7594 is an over-voltage clamping circuit, active current limiting, and a thermal shutdown mechanism to provide protection for the SLIC during a fault condition. Positive and negative lightning surge currents are reduced by the current limiting circuitry and hazardous potentials are diverted away from the SLIC via the protection diode bridge or the optional integrated protection SCR. Power-cross potentials are also reduced by the current limiting and thermal shutdown circuits.

To protect the CPC7594 from an over-voltage fault condition, use of a secondary protector is required. The secondary protector must limit the voltage seen at the tip and ring terminals to a level below the maximum breakdown voltage of the switches. To minimize the stress on the solid-state contacts, use of a foldback or crowbar type secondary protector is highly recommended. With proper selection of the secondary protector, a line card using the CPC7594 will meet all relevant ITU, LSSGR, TIA/EIA and IEC protection requirements.

The CPC7594 operates from a single +5 V supply. This gives the device extremely low power consumption in any state with virtually any range of battery voltage. The battery voltage used by the CPC7594 has a two fold function. It is used as a reference and as a current source for the internal integrated protection circuitry under surge conditions. Second, it is used as a reference. In the event of battery voltage loss, the CPC7594 enters the all-off state.

### 2.2 Under Voltage Switch Lock Out Circuitry

### 2.2.1 Introduction

Smart logic in the CPC7594 now provides for switch state control during both power up and power loss transitions. An internal detector is used to evaluate the  $V_{DD}$  supply to determine when to de-assert the under voltage switch lock out circuitry with a rising  $V_{DD}$  and when to assert the under voltage switch lock out circuitry with a falling  $V_{DD}$ . Any time unsatisfactory low  $V_{DD}$  conditions exist the lock out circuit overrides user switch control by blocking the information at the external input pins and conditioning internal switch commands to the all off state. Upon restoration of  $V_{DD}$  the switches will remain in the all-off state until the LATCH input is pulled low.

The rising  $V_{DD}$  lock out release threshold is internally set to ensure all internal logic is properly biased and functional before accepting external switch commands from the inputs to control the switch states. For a falling  $V_{DD}$  event, the lock out threshold is set to assure proper logic and switch behavior up to the moment the switches are forced off and external inputs are suppressed.

To facilitate hot plug insertion and power up control the LATCH pin has an integrated weak pull up resistor to the  $V_{DD}$  power rail that will hold a non-driven LATCH pin at a logic high state. This enables board designers to use the CPC7594 with FPGAs and other devices that provide high impedance outputs during power up and configuration. The weak pull up allows a fan out of up to 32 when the system's LATCH control driver has a logic low minimum sink capability of 4mA.

2.2.2 Hot Plug and Power Up Circuit Design Considerations

There are six possible start up scenarios that can occur during power up. They are:

- 1. All inputs defined at power up & LATCH = 0

- 2. All inputs defined at power up & LATCH = 1

- 3. All inputs defined at power up & LATCH = Z

- 4. All inputs not defined at power up & LATCH = 0

- 5. All inputs not defined at power up & LATCH = 1

- 6. All inputs not defined at power up & LATCH = Z

Under all of the start up situations listed above the CPC7594 will hold all of it's switches in the all-off state during power up. When  $V_{DD}$  requirements have been satisfied the LCAS will complete it's start up procedure in one of three conditions.

For start up scenario 1 the CPC7594 will transition from the all off state to the state defined by the inputs when  $V_{DD}$  is valid.

For start up scenarios 2, 3, 5, and 6 the CPC7594 will power up in the all-off state and remain there until the LATCH pin is pulled low. This allows for an indefinite all off state for boards inserted into a powered system but are not configured for service or boards that need to wait for other devices to be configured first. Start up scenario 4 will start up with all switches in the all-off state but upon the acceptance of a valid  $V_{DD}$  the LCAS will revert to one of the legitimate states listed in the truth tables and there after may randomly change states based on input pin leakage currents and loading. Because the LCAS state after power up can not be predicted with this start up condition it should never be utilized.

On designs that do not wish to individually control the LATCH pins of multi-port cards it is possible to bus many (or all) of the LATCH pins together to create a single board level input enable control.

### 2.3 Switch Logic

### 2.3.1 Start-up

The CPC7594 uses smart logic to monitor the V<sub>DD</sub> supply. Any time the V<sub>DD</sub> is below an internally set threshold, the smart logic places the control logic to the all-off state. An internal pullup at the LATCH pin locks the CPC7594 in the all-off state following start-up until the LATCH pin is pulled down to a logic low. Prior to the assertion of a logic low at the LATCH pin, the switch control inputs must be properly conditioned.

### 2.3.2 Switch Timing

The CPC7594 provides, when switching from the ringing state to the talk state, the ability to control the release timing of the ringing switches SW3 and SW4 relative to the state of the switches SW1 and SW2 using simple TTL logic-level inputs. The two available techniques are referred to as make-before-break and break-before-make operation. When the break switch contacts of SW1 and SW2 are closed (made) before the ringing switch contacts of SW3 and SW4 are opened (broken), this is referred to as make-before-break operation. Break-before-make operation occurs when the ringing contacts of SW3 and SW4 are opened (broken) before the switch contacts of SW1 and SW2 are closed (made). With the CPC7594, make-before-break and break-before-make operations can easily be accomplished by applying the proper sequence of logic-level inputs to the device.

The logic sequences for either mode of operation are provided in "Make-Before-Break Ringing to Talk Transition Logic Sequence" on page 14, "Break-Before-Make Ringing to Talk Transition Logic Sequence" on page 15, and "Alternate Break-Before-Make Ringing to Talk Transition Logic Sequence" on page 15. Logic states and input control settings are provided in "CPC7594xA and CPC7594xB Truth Table" on page 11 and "CPC7594xC Truth Table" on page 11.

#### 2.3.3 Make-Before-Break Operation

To use make-before-break operation, change the logic inputs from the ringing state directly to the talk state. Application of the talk state opens the ringing return switch, SW3, as the break switches SW1 and SW2 close. The ringing switch, SW4, remains closed until the next zero-crossing of the ringing current. While in the make-before-break state, ringing potentials in excess of the CPC7594 protection circuitry thresholds will be diverted away from the SLIC.

| State                     | IN <sub>ringing</sub> | IN <sub>test</sub> | LATCH | T <sub>SD</sub> | Timing                                                                                                                                                                                                                                                    | Break<br>Switches | Ringing<br>Return<br>Switch<br>(SW3) | Ringing<br>Switch<br>(SW4) | Test<br>Switches |

|---------------------------|-----------------------|--------------------|-------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------|----------------------------|------------------|

| Ringing                   | 1                     | 0                  |       |                 | -                                                                                                                                                                                                                                                         | Off               | On                                   | On                         | Off              |

| Make-<br>before-<br>break | 0                     | 0                  | 0     | Z               | SW4 waiting for next zero-current crossing to<br>turn off. Maximum time is one-half of the<br>ringing cycle. In this transition state current<br>limited by the dc break switch current limit<br>value will be sourced from the ring node of<br>the SLIC. | On                | Off                                  | On                         | Off              |

| Talk                      | 0                     | 0                  |       |                 | Zero-cross current has occurred                                                                                                                                                                                                                           | On                | Off                                  | Off                        | Off              |

#### Make-Before-Break Ringing to Talk Transition Logic Sequence

#### 2.3.4 Break-Before-Make Operation

Break-before-make operation of the CPC7594 can be achieved using two different techniques.

The first method uses manipulation of the  $IN_{RINGING}$ and  $IN_{TEST}$  logic inputs as shown in "Break-Before-Make Ringing to Talk Transition Logic Sequence" on page 15.

- At the end of the ringing state apply the all off state (1,1). This releases the ringing return switch (SW3) while the ringing switch (SW4) remains on, waiting for the next zero current event.

- 2. Hold the all off state for at least one-half of a ringing cycle to assure that a zero crossing event occurs and that SW4, the ringing switch, has opened.

- 3. Apply inputs for the next desired state. For the talk state, the inputs would be (0,0).

Break-before-make operation occurs when the ringing switches open before the break switches SW1 and SW2 close.

| State                     | IN <sub>ringing</sub> | IN <sub>TEST</sub> | LATCH | T <sub>SD</sub>                                                                                       | Timing                                       | Break<br>Switches | Ringing<br>Return<br>Switch<br>(SW3) | Ringing<br>Switch<br>(SW4) | Test<br>Switches |

|---------------------------|-----------------------|--------------------|-------|-------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------|--------------------------------------|----------------------------|------------------|

| Ringing                   | 1                     | 0                  |       |                                                                                                       | -                                            | Off               | On                                   | On                         | Off              |

| All-Off                   | 1                     | 1                  |       | Hold this state for at least one-half of the ringing cycle. SW4 waiting for zero current to turn off. | Off                                          | Off               | On                                   | Off                        |                  |

| Break-<br>Before-<br>Make | 1                     | 1                  | 0     | Z                                                                                                     | Zero current has occurred.<br>SW4 has opened | Off               | Off                                  | Off                        | Off              |

| Talk                      | 0                     | 0                  |       |                                                                                                       | Break switches close.                        | On                | Off                                  | Off                        | Off              |

Break-Before-Make Ringing to Talk Transition Logic Sequence

2.3.5 Alternate Break-Before-Make Operation

The alternate break-before-make technique is available for all versions of the CPC7594. As shown in "CPC7594xA and CPC7594xB Truth Table" on page 11 and "CPC7594xC Truth Table" on page 11, the bi-directional  $T_{SD}$  interface disables all of the switches when pulled to a logic low. Although logically disabled, an active ringing switch (SW4) will remain closed until the next zero crossing current event.

As shown in the table "Alternate Break-Before-Make Ringing to Talk Transition Logic Sequence" on page 15, this operation is similar to the one shown in "Alternate Break-Before-Make Operation" on page 15, except in the method used to select the all off state, and in when the IN<sub>RINGING</sub> and IN<sub>TEST</sub> inputs are reconfigured for the talk state.

Pull T<sub>SD</sub> to a logic low to end the ringing state. This opens the ringing return switch (SW3) and prevents any other switches from closing.

- Keep T<sub>SD</sub> low for at least one-half the duration of the ringing cycle period to allow sufficient time for a zero crossing current event to occur and for the circuit to enter the break-before-make state.

- 3. During the  $T_{SD}$  low period, set the IN<sub>RINGING</sub> and IN<sub>TEST</sub> inputs to the talk state (0, 0).

- 4. Release T<sub>SD</sub>, allowing the internal pull-up to activate the break switches.

When using  $T_{SD}$  as an input, the two recommended states are "0" which overrides the logic input pins and forces an all off state and "Z" which allows normal switch control via the logic input pins. This requires the use of an open-collector or open-drain type buffer.

Forcing  $T_{SD}$  to a logic high prevents the user from detecting a thermal shutdown condition and is therefore not recommended.

| State                     | IN <sub>ringing</sub> | IN <sub>test</sub> | LATCH | T <sub>SD</sub> | Timing                                                                                                | Break<br>Switches | Ringing<br>Return<br>Switch<br>(SW3) | Ringing<br>Switch<br>(SW4) | Test<br>Switches |

|---------------------------|-----------------------|--------------------|-------|-----------------|-------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------|----------------------------|------------------|

| Ringing                   | 1                     | 0                  | 0     | Z               | -                                                                                                     | Off               | On                                   | On                         | Off              |

| All-Off                   | 1                     | 0                  | x     | 0               | Hold this state for at least one-half of the ringing cycle. SW4 waiting for zero current to turn off. | Off               | Off                                  | On                         | Off              |

| Break-<br>Before-<br>Make | 0                     | 0                  | ^     | U               | SW4 has opened                                                                                        | Off               | Off                                  | Off                        | Off              |

| Talk                      | 0                     | 0                  | 0     | Z               | Close Break Switches                                                                                  | On                | Off                                  | Off                        | Off              |

### Alternate Break-Before-Make Ringing to Talk Transition Logic Sequence

### 2.4 Data Latch

The CPC7594 has an integrated transparent data latch. The latch enable operation is controlled by TTL logic input levels at the LATCH pin. Data input to the latch is via the input pins  $IN_{RINGING}$  and  $IN_{TEST}$  while the output of the data latch are internal nodes used for state control. When the LATCH enable control pin is at a logic 0 the data latch is transparent and the input control signals flow directly through the data latch to the state control circuitry. A change in input will be reflected by a change in the switch state.

Whenever the LATCH enable control pin is at logic 1, the data latch is active and data is locked. Subsequent changes to the input controls  $IN_{RINGING}$  and  $IN_{TEST}$  will not result in a change to the control logic or affect the existing switch state.

The switches will remain in the state they were in when the LATCH changes from logic 0 to logic 1 and will not respond to changes in input as long as the LATCH is at logic 1. However, neither the  $T_{SD}$  input nor the  $T_{SD}$  output control functions are affected by the latch function. Since internal thermal shutdown control and external "All-off" control is not affected by the state of the LATCH enable input,  $T_{SD}$  will override state control.

### 2.5 T<sub>SD</sub> Pin Description

The  $T_{SD}$  pin is a bi-directional I/O structure with an internal pull-up current source having a nominal value of 16  $\mu$ A biased from V<sub>DD</sub>.

As an output, this pin indicates the status of the thermal shutdown circuitry. Typically, during normal operation, this pin will be pulled up to  $V_{DD}$  but under fault conditions that create excess thermal loading the CPC7594 will enter thermal shutdown and a logic low will be output.

As an input, the  $T_{SD}$  pin is utilized to place the CPC7594 into the "All-Off" state by simply pulling the input to a logic low. For applications using low-voltage logic devices (lower than  $V_{DD}$ ), IXYS IC Division recommends the use of an open-collector or an open-drain type output to control  $T_{SD}$ . This avoids sinking the  $T_{SD}$  pull up bias current to ground during normal operation when the all-off state is not required. In general, IXYS IC Division recommends all applications use an open-collector or open-drain type device to drive this pin.

Unlike the CPC7584, driving  $T_{SD}$  to a logic 1 or tying this pin to  $V_{CC}$  will not prevent normal operation of the thermal shutdown circuitry inside the CPC7594. As a result the  $T_{SD}$  pin may be held at a logic high. However, the CPC7594  $T_{SD}$  pin has only two recommended operating states when it is used as an input control. A logic 0, which forces the device to the all-off state and a high impedance (Z) state for normal operation. This requires the use of an open-collector or open-drain type buffer.

### 2.6 Ringing Switch Zero-Cross Current Turn Off

After the application of a logic input to turn SW4 off, the ringing switch is designed to delay the change in state until the next zero-crossing. Once on, the switch requires a zero-current cross to turn off, and therefore should not be used to switch a pure DC signal. The switch will remain in the on state no matter the logic input until the next zero crossing. These switching characteristics will reduce and possibly eliminate overall system impulse noise normally associated with ringing switches. See IXYS IC Division's application note AN-144, Impulse Noise Benefits of Line Card Access Switches for more information. The attributes of ringing switch SW4 may make it possible to eliminate the need for a zero-cross switching scheme. A minimum impedance of  $300\Omega$  in series with the ringing generator is recommended.

### 2.7 Power Supplies

Both a +5V supply and battery voltage are connected to the CPC7594. Switch state control is powered exclusively by the +5V supply. As a result, the CPC7594 exhibits extremely low power consumption during active and idle states.