### Halogen-free & RoHS Recast Compliant

### **CompactFlash Series 6**

Industrial CompactFlash Card Product Specifications

June 29, 2016

Version 1.4

#### Apacer Technology Inc.

1F, No.32, Zhongcheng Rd., Tucheng Dist., New Taipei City, Taiwan, R.O.C Tel: +886-2-2267-8000 Fax: +886-2-2267-2261 www.apacer.com

### **Features:**

- CompactFlash Association Specification Revision 6.0 Standard Interface

- ATA command set compatible

- ATA transfer mode supports:

PIO Mode 6

Multiword DMA Mode 4

Ultra DMA Mode 7

PCMCIA UDMA Mode 7

- Capacity

- 512 MB

- 1, 2, 4, 8, 16, 32, 64 GB

- Performance\*

- Sustained read: Up to 110 MB/sec

- Sustained write: Up to 80 MB/sec

- Flash Management

- Wear-leveling algorithms to substantially increase longevity of flash media

- Built-in BCH ECC capable of correcting up to 72 bits in 1KB data

- Supports S.M.A.R.T commands

- NAND Flash Type: SLC

### Temperature Range

Operating:

Standard: 0°C to 70°C Extended: -40°C to 85°C

Storage: -40°C to 100°C

#### Operating Voltage for Read and Write

- 3.3 V

- 5.0 V

#### Power Consumption\*

Active mode: 310 mAStandby mode: 5 mA

#### Connector Type

50 pins female

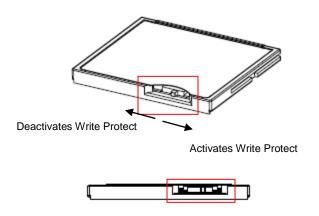

#### Write Protect by Hardware Switch

Write protect activated/deactivated by a mechanical switch

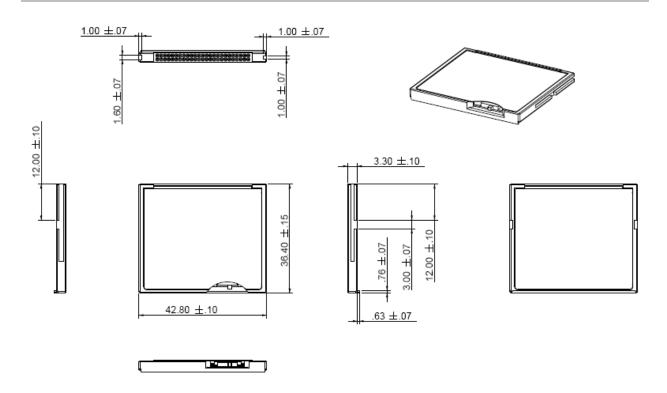

#### Physical Dimensions

- 36.4mm x 42.8mm x 3.3mm

#### Halogen Free

#### RoHS Recast Complient

Complies with 2011/65/EU

<sup>\*</sup>Varies from capacities. Performance and power consumption presented here are typical and may vary depending on capacities, flash configuration or host system settings.

### **Table of Contents**

| 1. GENERAL DESCRIPTION                                                                                                             | 3  |

|------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 Intelligent Endurance Design                                                                                                   |    |

| 2. FUNCTIONAL BLOCK                                                                                                                | 4  |

| 3. PIN ASSIGNMENTS                                                                                                                 | 5  |

| 4. PRODUCT SPECIFICATIONS                                                                                                          | 7  |

| 4.1 CAPACITY 4.2 PERFORMANCE 4.3 ENVIRONMENTAL SPECIFICATIONS 4.4 MEAN TIME BETWEEN FAILURES (MTBF) 4.5 CERTIFICATION & COMPLIANCE |    |

| 5. SOFTWARE INTERFACE                                                                                                              | 9  |

| 5.1 CF-ATA COMMAND SET                                                                                                             | 9  |

| 6. OPERATING CONDITIONS                                                                                                            | 11 |

| 6.1 AC/DC CHARACTERISTICS                                                                                                          | 11 |

| 7. MECHANICAL SPECIFICATIONS                                                                                                       | 37 |

| 7.1 DIMENSIONS                                                                                                                     |    |

| 8. PRODUCT ORDERING INFORMATION                                                                                                    | 39 |

| 8.1 PRODUCT CODE DESIGNATIONS                                                                                                      |    |

### 1. General Description

Apacer's value-added Industrial CompactFlash Card offers high performance, high reliability and power-efficient storage. Regarding standard compliance, this CompactFlash Card complies with CompactFlash specification revision 6.0, supporting transfer modes up to Programmed Input Output (PIO) Mode 6, Multiword Direct Memory Access (DMA) Mode 4, Ultra DMA Mode 7, and PCMCIA Ultra DMA Mode 7.

Apacer's value-added CFC provides complete PCMCIA – ATA functionality and compatibility. Apacer 's CompactFlash technology is designed for applications in Point of Sale (POS) terminals, telecom, IP-STB, medical instruments, surveillance systems, industrial PCs and handheld applications such as the new generation of Digital Single Lens Reflex (DSLR) cameras.

### 1.1 Intelligent Endurance Design

### 1.1.1 Error Correction Code (ECC)

The CompactFlash card is programmed with BCH Error Detection Code (EDC) and Error Correction Code (ECC) algorithms capable of correcting up to 72 random bits in 1KB bytes data.

High performance is achieved through hardware-based error detection and correction.

### 1.1.2 Wear-Leveling Algorithms

Flash memory devices differ from Hard Disk Drives (HDDs) in terms of how blocks are utilized. For HDDs, when a change is made to stored data, like erase or update, the controller mechanism on HDDs will perform overwrites on blocks. Unlike HDDs, flash blocks cannot be overwritten and each P/E cycle wears down the lifespan of blocks gradually. Repeatedly program/erase cycles performed on the same memory cells will eventually cause some blocks to age faster than others. This would bring flash storages to their end of service term sooner. Wear leveling is an important mechanism that level out the wearing of blocks so that the wearing-down of blocks can be almost evenly distributed. This will increase the lifespan of SSDs. Commonly used wear leveling types are Static and Dynamic.

#### 1.1.3 S.M.A.R.T. Technology

S.M.A.R.T. is an acronym for Self-Monitoring, Analysis and Reporting Technology, an open standard allowing disk drives to automatically monitor their own health and report potential problems. It protects the user from unscheduled downtime by monitoring and storing critical drive performance and calibration parameters. Ideally, this should allow taking proactive actions to prevent impending drive failure. Apacer SMART feature adopts the standard SMART command B0h to read data from the drive. When the Apacer SMART Utility running on the host, it analyzes and reports the disk status to the host before the device is in critical condition.

#### 1.1.4 Flash Block Management

Current production technology is unable to guarantee total reliability of NAND flash memory array. When a flash memory device leaves factory, it comes with a minimal number of initial bad blocks during production or out-of-factory as there is no currently known technology that produce flash chips free of bad blocks. In addition, bad blocks may develop during program/erase cycles. When host performs program/erase command on a block, bad block may appear in Status Register. Since bad blocks are inevitable, the solution is to keep them in control. Apacer flash devices are programmed with ECC, block mapping technique and S.M.A.R.T to reduce invalidity or error. Once bad blocks are detected, data in those blocks will be transferred to free blocks and error will be corrected by designated algorithms.

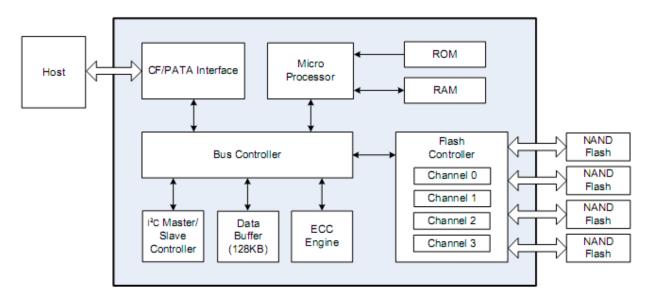

### 2. Functional Block

The CompactFlash Card (CFC) includes a controller and flash media, as well as the CompactFlash standard interface. Figure 2-1 shows the functional block diagram.

Figure 2-1: Functional Block Diagram

### 3. Pin Assignments

Table 3-1 lists the pin assignments with respective signal names for the 50-pin configuration. A "#" suffix indicates the active low signal. The pin type can be input, output or input/output.

Table 3-1: Pin Assignments (1 of 2)

| Pin No. | Memory      | card mode    | I/O ca      | rd mode      | True ID          | True IDE mode |  |  |

|---------|-------------|--------------|-------------|--------------|------------------|---------------|--|--|

|         | Signal name | Pin I/O type | Signal name | Pin I/O type | Signal name      | Pin I/O type  |  |  |

| 1       | GND         | 1            | GND         | -            | GND              | -             |  |  |

| 2       | D3          | I/O          | D3          | I/O          | D3               | I/O           |  |  |

| 3       | D4          | I/O          | D4          | I/O          | D4               | I/O           |  |  |

| 4       | D5          | I/O          | D5          | I/O          | D5               | I/O           |  |  |

| 5       | D6          | I/O          | D6          | I/O          | D6               | I/O           |  |  |

| 6       | D7          | I/O          | D7          | I/O          | D7               | I/O           |  |  |

| 7       | #CE1        |              | #CE1        | I            | #CS0             | I             |  |  |

| 8       | A10         |              | A10         | ı            | A10 <sup>1</sup> | I             |  |  |

| 9       | #OE         |              | #OE         | I            | #ATA SEL         |               |  |  |

| 10      | A9          |              | A9          | I            | A9 <sup>1</sup>  |               |  |  |

| 11      | A8          |              | A8          | I            | A8 <sup>1</sup>  |               |  |  |

| 12      | A7          |              | A7          | I            | A7 <sup>1</sup>  |               |  |  |

| 13      | VCC         | -            | VCC         | -            | VCC              | -             |  |  |

| 14      | A6          | ı            | A6          | ı            | A6 <sup>1</sup>  | I             |  |  |

| 15      | A5          |              | A5          | I            | A5 <sup>1</sup>  |               |  |  |

| 16      | A4          |              | A4          | ı            | A4 <sup>1</sup>  |               |  |  |

| 17      | A3          |              | A3          | ı            | A3 <sup>1</sup>  |               |  |  |

| 18      | A2          |              | A2          | ı            | A2               |               |  |  |

| 19      | A1          |              | A1          | ı            | A1               |               |  |  |

| 20      | A0          |              | A0          | ı            | A0               |               |  |  |

| 21      | D0          | I/O          | D0          | I/O          | D0               | I/O           |  |  |

| 22      | D1          | I/O          | D1          | I/O          | D1               | I/O           |  |  |

| 23      | D2          | I/O          | D2          | I/O          | D2               | I/O           |  |  |

| 24      | WP          | 0            | #IOIS16     | 0            | #IOCS16          | 0             |  |  |

| 25      | #CD2        | 0            | #CD2        | 0            | #CD2             | 0             |  |  |

| 26      | #CD1        | 0            | #CD1        | 0            | #CD1             | 0             |  |  |

| 27      | D11         | I/O          | D11         | I/O          | D11              | I/O           |  |  |

| 28      | D12         | I/O          | D12         | I/O          | D12              | I/O           |  |  |

| 29      | D13         | I/O          | D13         | I/O          | D13              | I/O           |  |  |

| 30      | D14         | I/O          | D14         | I/O          | D14              | I/O           |  |  |

| 31      | D15         | I/O          | D15         | I/O          | D15              | I/O           |  |  |

| 32      | #CE2        |              | #CE2        | Ī            | #CS1             | I             |  |  |

| 33      | #VS1        | 0            | #VS1        | 0            | #VS1             | 0             |  |  |

| 34      | #IORD       | Ī            | #IORD       | Ī            | #IORD            | Ī             |  |  |

| 35      | #IOWR       | I            | #IOWR       | I            | #IOWR            | I             |  |  |

| 36      | #WE         | I            | #WE         | I            | #WE              | I             |  |  |

| 37      | RDY/-BSY    | 0            | #IREQ       | Ö            | INTRQ            | Ö             |  |  |

| 38      | VCC         | -            | VCC         | -            | VCC              | -             |  |  |

| 39      | #CSEL       | I            | #CSEL       | ı            | #CSEL            | I             |  |  |

| 40      | #VS2        | 0            | #VS2        | Ö            | #VS2             | Ö             |  |  |

| 41      | RESET       | I            | RESET       | Ī            | #RESET           | Ī             |  |  |

Table 3-1: Pin Assignments (2 of 2)

| Pin No. | Memory card mode |              | I/O cai     | rd mode      | True IDE mode      |              |  |

|---------|------------------|--------------|-------------|--------------|--------------------|--------------|--|

|         | Signal name      | Pin I/O type | Signal name | Pin I/O type | Signal name        | Pin I/O type |  |

| 42      | #WAIT            | 0            | #WAIT       | 0            | IORDY              | 0            |  |

| 43      | #INPACK          | 0            | #INPACK     | 0            | DMARQ <sup>2</sup> | 0            |  |

| 44      | #REG             | I            | #REG        | I            | DMACK <sup>2</sup> | 1            |  |

| 45      | BVD2             | 0            | #SPKR       | 0            | #DASP              | I/O          |  |

| 46      | BVD1             | 0            | #STSCHG     | 0            | #PDIAG             | I/O          |  |

| 47      | D8               | I/O          | D8          | I/O          | D8                 | I/O          |  |

| 48      | D9               | I/O          | D9          | I/O          | D9                 | I/O          |  |

| 49      | D10              | I/O          | D10         | I/O          | D10                | I/O          |  |

| 50      | GND              | -            | GND         | -            | GND                | -            |  |

The signal should be grounded by the host. Connection required when UDMA is in use.

### 4. Product Specifications

### 4.1 Capacity

Capacity specifications of the Compact Flash Card series (CFC) are available as shown in Table 4-1. It lists the specific capacity and the default numbers of heads, sectors and cylinders for each product line.

Table 4-1: Capacity Specifications

| Capacity | Total bytes <sup>1</sup> | Cylinders | Heads | Sectors | Max LBA     |

|----------|--------------------------|-----------|-------|---------|-------------|

| 512 MB   | 512,483,328              | 993       | 16    | 63      | 1,000,944   |

| 1 GB     | 1,024,966,656            | 1,986     | 16    | 63      | 2,001,888   |

| 2 GB     | 2,048,901,120            | 3,970     | 16    | 63      | 4,001,760   |

| 4 GB     | 4,110,188,544            | 7,964     | 16    | 63      | 8,027,712   |

| 8 GB     | 8,195,604,480            | 15,880    | 16    | 63      | 16,007,040  |

| 16 GB    | 16,391,340,032           | 16,383    | 16    | 63      | 32,014,336  |

| 32 GB    | 32,019,316,736           | 16,383    | 16    | 63      | 62,537,728  |

| 64 GB    | 64,030,244,864           | 16,383    | 16    | 63      | 125,059,072 |

Note:

Display of total bytes varies from operating systems.

Cylinders, heads or sectors are not applicable for these capacities. Only LBA addressing applies

Notes: 1 GB = 1,000,000,000 bytes; 1 sector = 512 bytes.

LBA count addressed in the table above indicates total user storage capacity and will remain the same throughout the lifespan of the device. However, the total usable capacity of the SSD is most likely to be less than the total physical capacity because a small portion of the capacity is reserved for device maintenance usages.

### 4.2 Performance

Performance of the CF cards is listed in Table 4-2

Table 4-2: Performance Specifications

| Capacity Performance   | 512 MB | 1 GB | 2 GB | 4 GB | 8 GB | 16 GB | 32 GB | 64 GB |

|------------------------|--------|------|------|------|------|-------|-------|-------|

| Sustained read (MB/s)  | 85     | 85   | 105  | 110  | 110  | 110   | 110   | 110   |

| Sustained write (MB/s) | 20     | 40   | 70   | 70   | 75   | 75    | 80    | 80    |

Note: performance may vary depending on flash configurations or host system settings.

### 4.3 Environmental Specifications

Environmental specifications of the Compact Flash Card series (CFC) which follow the MIL-STD-810F standards is available as shown in Table 4-3.

Table 4-3: Environmental Specifications

| Environment               |           | Specifications                                   |

|---------------------------|-----------|--------------------------------------------------|

| T                         | Operating | 0°C to 70°C (Standard); -40°C to 85°C (Extended) |

| Temperature               | Storage   | -40°C to 100°C                                   |

| Humidity                  |           | 5% to 95% RH (Non-condensing)                    |

| Vibration (Non-Operating) |           | Sine wave: 10~2000Hz, 15G (X, Y, Z axes)         |

| Shock (Non-Operating)     |           | Half sine wave 1,500G (X, Y, Z; All 6 axes)      |

### 4.4 Mean Time Between Failures (MTBF)

MTBF, an acronym for Mean Time Between Failures, is a measure of a device's reliability. Its value represents the average time between a repair and the next failure. The measure is typically in units of hours. The higher the MTBF value, the higher the reliability of the device. The predicted result of this CompactFlash Card is higher than  $1.99 \times 10^6$  hours.

### 4.5 Certification & Compliance

The CompactFlash card complies with the following global standards:

- CE

- FCC

- Halogen-free

- EMC

- RoHS Recast (2011/65/EU)

### 5. Software Interface

### **5.1 CF-ATA Command Set**

Table 5-1 summarizes the CF-ATA command set with the paragraphs that follow describing the individual commands and the task file for each.

Table 5-1: CFC-ATA Command Set

| Command Set         | Command                                    | Code       | Protocol          |

|---------------------|--------------------------------------------|------------|-------------------|

| CFA Feature Set     | Request Sense                              | 03h        | Non-data          |

|                     | Write Sectors Without Erase                | 38h        | PIO data-out      |

|                     | Erase Sectors                              | C0h        | Non-data          |

|                     | Write Multiple Without Erase               | CDh        | PIO data-out      |

|                     | Translate Sector                           | 87h        | PIO data-in       |

|                     | Set Features Enable/Disable 8-bit Transfer | Efh        | Non-data          |

| General Feature Set | Execute Drive Diagnostic                   | 90h        | Device diagnostic |

|                     | Flush Cache                                | E7h        | Non-data          |

|                     | Identify Device                            | Ech        | PIO data-in       |

|                     | Read DMA                                   | C8h        | DMA               |

|                     | Read Multiple                              | C4h        | PIO data-in       |

|                     | Read Sector(s)                             | 20h or 21h | PIO data-in       |

|                     | Read Verify Sector(s)                      | 40h or 41h | Non-data          |

|                     | Set Feature                                | Efh        | Non-data          |

|                     | Set Multiple Mode                          | C6h        | Non-data          |

|                     | Write DMA                                  | Cah        | DMA               |

|                     | Write Multiple                             | C5h        | PIO data-out      |

|                     | Write Sector(s)                            | 30h or 31h | PIO data-out      |

|                     | NOP                                        | 00h        | Non-data          |

|                     | Read Buffer                                | E4h        | PIO data-in       |

|                     | Write Buffer                               | E8h        | PIO data-out      |

|                     | Set Feature                                | Efh        | Non-data          |

| Power Management    | Check Power Mode                           | E5h or 98h | Non-data          |

| Feature Set         | Idle                                       | E3h or 97h | Non-data          |

|                     | Idle Immediate                             | E1h or 95h | Non-data          |

|                     | Sleep                                      | E6h or 99h | Non-data          |

|                     | Standby                                    | E2h or 96h | Non-data          |

|                     | Standby Immediate                          | E0h or 94h | Non-data          |

| Command Set            | Command                          | Code | Protocol     |

|------------------------|----------------------------------|------|--------------|

| Security Mode Feature  | Security Set Password            | F1h  | PIO data-out |

| Set                    | Security Unlock                  | F2h  | PIO data-out |

|                        | Security Erase Prepare           | F3h  | Non-data     |

|                        | Security Erase Unit              | F4h  | PIO data-out |

|                        | Security Freeze Lock             | F5h  | Non-data     |

|                        | Security Disable Password        | F6h  | PIO data-out |

| SMART Feature Set      | SMART Disable Operations         | B0h  | Non-data     |

|                        | SMART Enable/Disable Autosave    | B0h  | Non-data     |

|                        | SMART Enable Operations          | B0h  | Non-data     |

|                        | SMART Return Status              | B0h  | Non-data     |

|                        | SMART Execute Off-line Immediate | B0h  | Non-data     |

|                        | SMART Read Data                  | B0h  | PIO data-in  |

| Host Protected Area    | Read Native Max Address          | F8h  | Non-data     |

| Feature Set            | Set Max Address                  | F9h  | Non-data     |

|                        | Set Max Set Password             | F9h  | PIO data-out |

|                        | Set Max Lock                     | F9h  | Non-data     |

|                        | Set Max Freeze Lock              | F9h  | Non-data     |

|                        | Set Max Unlock                   | F9h  | PIO data-out |

| Others                 | Format Track                     | 50h  | PIO data-out |

|                        | Initialize Drive Parameters      | 91h  | Non-data     |

|                        | Recalibrate                      | 1Xh  | Non-data     |

|                        | Seek                             | 7Xh  | Non-data     |

|                        | Wear Level                       | F5h  | Non-data     |

|                        | Write Verify                     | 3Ch  | PIO data-out |

| 48-bit Address Feature | Read Sector Ext                  | 24h  | PIO data-in  |

| Set                    | Read DMA Ext                     | 25h  | DMA          |

|                        | Read Multiple Ext                | 29h  | PIO data-in  |

|                        | Write Sector Ext                 | 34h  | PIO data-out |

|                        | Write DMA Ext                    | 35h  | DMA          |

|                        | Read Verify Sector Ext           | 42h  | Non-data     |

|                        | Write Multiple FUA Ext           | Ceh  | PIO data-out |

|                        | Flush Cache Ext                  | Eah  | Non-data     |

### **6. Operating Conditions**

Table 6-1: Operating Range

| Parameters             | Range           |

|------------------------|-----------------|

| Ambient temperature    | 0°C to 70°C     |

| Extended temperature   | -40°C to 85°C   |

| Supply voltage at 3.3V | 3.135 ~ 3.465 V |

| Supply voltage at 5V   | 4.75 ~ 5.25 V   |

**Table 6-2:** Power Consumption (typical)

| Mode Capacity | 512 MB | 1 GB | 2 GB | 4 GB | 8 GB | 16 GB | 8 GB | 16 GB |

|---------------|--------|------|------|------|------|-------|------|-------|

| Active (mA)   | 220    | 220  | 260  | 260  | 260  | 290   | 290  | 310   |

| Standby (mA)  | 5      | 5    | 5    | 5    | 5    | 5     | 5    | 5     |

Note: Power consumptions may vary depending on settings and platforms

### 6.1 AC/DC Characteristics

The following section provides general AC/DC characteristics of this CompactFlash card.

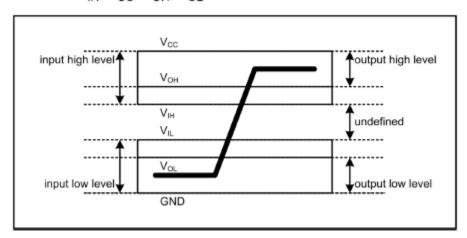

#### 6.1.1 General DC Characteristics

Definitions of VIH, VCC, VOH, VOL

DC characteristics for host interface (Vcc = 3.3V/5V)

| Parameter                 | Symbol | Minimum | Maximum | Unit | Remark              |

|---------------------------|--------|---------|---------|------|---------------------|

| Supply Voltage 5V         | Vcc    | 4.5     | 5.5     | V    |                     |

| Supply voltage 3.3V       | Vcc    | 2.97    | 3.63    | V    |                     |

| High Level Output Voltage | Voн    | 2.5     |         | V    |                     |

| Low Level Output Voltage  | Vol    |         | 0.4     | V    |                     |

| High Level Input Voltage  | VIH    | 2.4     |         | V    | Non-Schmitt trigger |

|                           |        | 2.05    |         | V    | Schmitt trigger     |

| Low Level Input Voltage   | VIL    |         | 0.6     | V    | Non-Schmitt trigger |

|                           |        |         | 1.25    | V    | Schmitt trigger     |

| Pull-up Resistance        | Rpu    | 52.7    | 141     | kOhm |                     |

| Pull-down Resistance      | Rpd    | 47.5    | 172     | kOhm |                     |

### • General DC characteristics

| Parameter                 | Symbol | Minimum | Maximum | Unit | Remark              |  |  |

|---------------------------|--------|---------|---------|------|---------------------|--|--|

| Supply Voltage            | Vcc    | 2.7     | 3.6     | V    |                     |  |  |

| High Level Output Voltage | Voн    | 2.4     |         | V    |                     |  |  |

| Low Level Output Voltage  | Vol    |         | 0.4     | V    |                     |  |  |

| High Level Input Voltage  | ViH    | 2.0     |         | V    | Non-Schmitt trigger |  |  |

|                           |        | 1.4     | 2.0     | V    | Schmitt trigger     |  |  |

| Low Level Input Voltage   | VIL    |         | 0.8     | V    | Non-Schmitt trigger |  |  |

|                           |        |         | 1.2     | V    | Schmitt trigger     |  |  |

| Pull-up Resistance        | Rpu    | 40      |         | kOhm |                     |  |  |

| Pull-down Resistance      | Rpd    | 40      |         | kOhm |                     |  |  |

### 6.1.2 General AC Characteristics

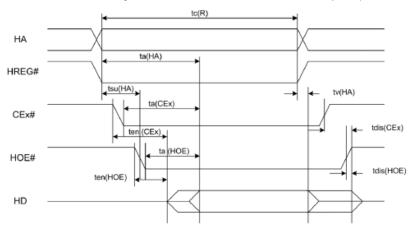

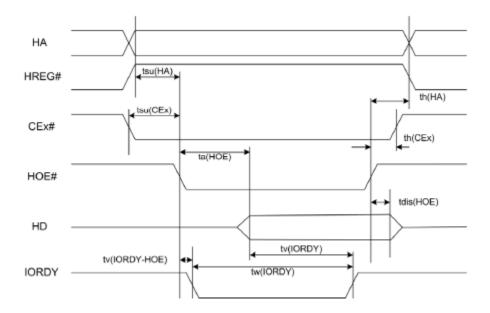

Attribute Memory Read Timing

| Item                           | Symbol     | Min. (ns) | Max. (ns) |

|--------------------------------|------------|-----------|-----------|

| Read Cycle Time                | tc (R)     | 300       |           |

| Address Access Time            | ta (HA)    |           | 300       |

| Card Enable Access Time        | ta (CEx)   |           | 300       |

| Output Enable Access Time      | ta (HOE)   |           | 150       |

| Output Disable Time from CEx#  | tdis (CEx) |           | 100       |

| Output Disable Time from HOE#  | tdis (HOE) |           | 100       |

| Address Setup Time             | tsu (HA)   | 30        |           |

| Output Enable Time from CEx#   | ten (CEx)  | 5         |           |

| Output Enable Time from HOE#   | ten (HOE)  | 5         |           |

| Data Valid from Address Change | tv (HA)    | 0         |           |

Notes: all time intervals are in nanoseconds. HD refers to the data provided by the CompactFlash card to the system. The CEx# signal or both of the HOE# and the HWE# signal are de-asserted between consecutive cycle operations.

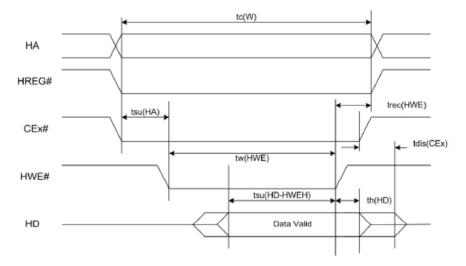

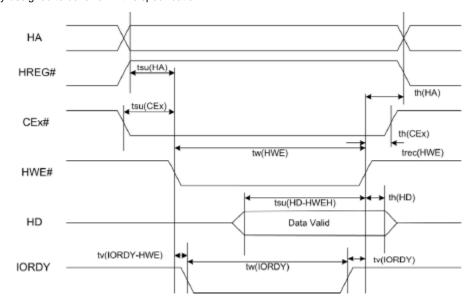

• Attribute Memory Write Timing

| ltem                     | Symbol        | Min. (ns) | Max. (ns) |

|--------------------------|---------------|-----------|-----------|

| Write Cycle Time         | tc (W)        | 250       |           |

| Write Pulse Width        | tw (HWE)      | 150       |           |

| Address setup Time       | tsu (HA)      | 30        |           |

| Write Recovery Time      | trec (HWE)    | 30        |           |

| Data Setup Time for HWE# | tsu (HD-HWEH) | 80        |           |

| Data Hold Time           | th (HD)       | 30        |           |

Notes: all time intervals are in nanoseconds. HD refers to the data provided by the CompactFlash card to the system.

• Common Memory Read Timing

| Cycle Time Mode               |                    | 250  | ns ns | 120  | ns ns | 100  | ) ns | 80   | ns   |

|-------------------------------|--------------------|------|-------|------|-------|------|------|------|------|

| Item                          | Symbol             | Min. | Max.  | Min. | Max.  | Min. | Max. | Min. | Max. |

| Output Enable Access Time     | ta (HOE)           |      | 125   |      | 60    |      | 50   |      | 45   |

| Output Disable Time from HOE# | tdis (HOE)         |      | 100   |      | 60    |      | 50   |      | 45   |

| Address Setup Time            | tsu (HA)           | 30   |       | 15   |       | 10   |      | 10   |      |

| Address Hold Time             | th (HA)            | 20   |       | 15   |       | 15   |      | 10   |      |

| CEx# Setup before HOE#        | tsu (CEx)          | 5    |       | 5    |       | 5    |      | 5    |      |

| CEx# Hold following HOE#      | th (CEx)           | 20   |       | 15   |       | 15   |      | 10   |      |

| Wait Delay falling from HOE#  | tv (IORDY-<br>HOE) |      | 35    |      | 35    |      | 35   |      | Na   |

| Data Setup for Wait Release   | tv (IORDY)         |      | 0     |      | 0     |      | 0    |      | Na   |

| Wait Width Time               | tw (IORDY)         |      | 350   |      | 350   |      | 350  |      | Na   |

Note: IORDY is not supported in this 80 ns mode. The maximum load on IORDY is 1 LSTTL with a 50 pF (40 pF below 120 nsec cycle time) total load. All time intervals are in nanoseconds. HD refers to the data provided by the CompactFlash card to the system. The IORDY signal can be ignored when the HOE# cycle-to-cycle time is greater than the Wait Width Time. The Max Wait Width Time can be determined from the Card Information Structure (CIS). Although adhering to the PCM-CIA specification, the Wait Width Time is intentionally designed to be lower in this specification.

Common Memory Write Timing

| Cycle Time Mode              |                     | 250  | ) ns | 120    | ns   | 100  | ) ns | 80   | ns   |

|------------------------------|---------------------|------|------|--------|------|------|------|------|------|

| Item                         | Symbol              | Min. | Max. | Min.   | Max. | Min. | Max. | Min. | Max. |

| Data Setup before HWE#       | tsu (HD-<br>HWEH)   | 80   |      | 50     |      | 40   |      | 30   |      |

| Data Hold following HWE#     | th (HD)             | 30   |      | 15     |      | 10   |      | 10   |      |

| HWE# Pulse Width             | tw (HWE)            | 150  |      | 70     |      | 60   |      | 55   |      |

| Address Setup Time           | tsu (HA)            | 30   |      | 15     |      | 10   |      | 10   |      |

| CEx# Setup before HWE#       | tsu (CEx)           | 5    |      | 5      |      | 5    |      | 5    |      |

| Write Recovery Time          | trec (HWE)          | 30   |      | 15     |      | 15   |      | 15   |      |

| Address Hold Time            | th (HA)             | 20   |      | 15     |      | 15   |      | 15   |      |

| CEx# Hold following HWE#     | th (CEx)            | 20   |      | 15     |      | 15   |      | 10   |      |

| Wait Delay falling from HWE# | tv (IIORDY-<br>HWE) |      | 35   |        | 35   |      | 35   |      | Na   |

| HWE# High from Wait Release  | tv (IORDY)          | 0    |      | 0      |      | 0    |      | Na   |      |

| Wait Width Time              | tw (IORDY)          |      | 350  | (: 410 | 350  | 50.5 | 350  | 100  | Na   |

Note: IORDY is not supported in this 80 ns mode. The maximum load on IORDY is 1 LSTTL with a 50 pF (40 pF below 120 nsec cycle time) total load. All time intervals are in nanoseconds. HD refers to the data provided by the CompactFlash card to the system. The IORDY signal can be ignored when the HWE# cycle-to-cycle time is greater than the Wait Width Time. The Max Wait Width Time can be determined from the Card Information Structure (CIS). Although adhering to the PCM-CIA specification, the Wait Width Time is intentionally designed to be lower in this specification.

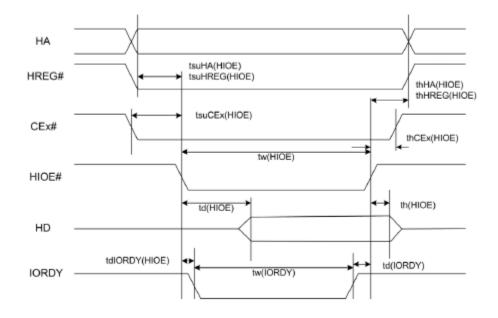

I/O Read Timing

| Cycle Time Mode               |                   | 250  | ns ns | 120  | ns ns | 100  | ) ns | 80   | ns   |

|-------------------------------|-------------------|------|-------|------|-------|------|------|------|------|

| ltem                          | Symbol            | Min. | Max.  | Min. | Max.  | Min. | Max. | Min. | Max. |

| Data Delay after HIOE#        | td (HIOE)         |      | 100   |      | 50    |      | 50   |      | 45   |

| Data Hold following HIOE#     | th (HIOE)         | 0    |       | 5    |       | 5    |      | 5    |      |

| HIOE# Width Time              | tw (HIOE)         | 165  |       | 70   |       | 65   |      | 55   |      |

| Address Setup before HIOE#    | tsuHA<br>(HIOE)   | 70   |       | 25   |       | 25   |      | 15   |      |

| Address Hold following HIOE#  | thHA (HIOE)       | 20   |       | 10   |       | 10   |      | 10   |      |

| CEx# Setup before HIOE#       | tsuCEx<br>(HIOE)  | 5    |       | 5    |       | 5    |      | 5    |      |

| CEx# Hold following HIOE#     | thCEx<br>(HIOE)   | 20   |       | 10   |       | 10   |      | 10   |      |

| HREG# Setup before HIOE#      | tsuHREG<br>(HIOE) | 5    |       | 5    |       | 5    |      | 5    |      |

| HREG# Hold following HIOE#    | thHREG<br>(HIOE)  | 0    |       | 0    |       | 0    |      | 0    |      |

| Wait Delay falling from HIOE# | tdIORDY<br>(HIOE) |      | 35    |      | 35    |      | 35   |      | Na   |

| Data Delay from Wait Rising   | td (IORDY)        |      | 0     |      | 0     |      | 0    |      | na   |

| Wait Width Time               | tw (IORDY)        |      | 350   |      | 350   |      | 350  |      | Na   |

Note: IORDY is not supported in this 80 ns mode. Maximum load on IORDY is 1 LSTTL with a 50 pF (40 pF below 120 nsec cycle time) total load. All time intervals are in nanoseconds. Although minimum time from IORDY high to HIOE# high is 0 nsec, the minimum HIOE# width is still met. HD refers to data provided by the CompactFlash Card to the system. Although following PCMCIA specification, the Wait Width Time is intentionally lower in this specification.

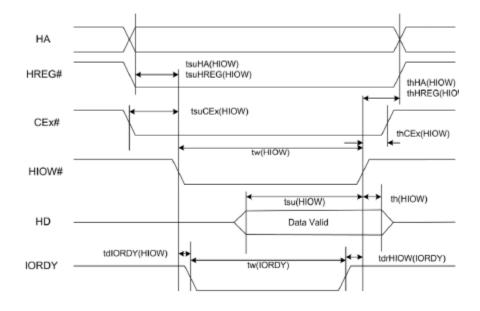

I/O Write Timing

| Cycle Time Mode               | _                 | 250  | ) ns | 120  | ns   | 100  | ) ns | 80   | ns   |

|-------------------------------|-------------------|------|------|------|------|------|------|------|------|

| Item                          | Symbol            | Min. | Max. | Min. | Max. | Min. | Max. | Min. | Max. |

| Data Setup before HIOW#       | tsu (HIOW)        | 60   |      | 20   |      | 20   |      | 15   |      |

| Data Hold following HIOW#     | th (HIOW)         | 30   |      | 10   |      | 5    |      | 5    |      |

| HIOW# Width Time              | tw (HIOW)         | 165  |      | 70   |      | 65   |      | 65   |      |

| Address Setup before HIOW#    | tsuHA<br>(HIOW)   | 70   |      | 25   |      | 25   |      | 15   |      |

| Address Hold following HIOW#  | thHA (HIOW)       | 20   |      | 20   |      | 10   |      | 10   |      |

| CEx# Setup before HIOW#       | tsuCEx<br>(HIOW)  | 5    |      | 5    |      | 5    |      | 5    |      |

| CEx# Hold following HIOW#     | thCEx<br>(HIOW)   | 20   |      | 20   |      | 10   |      | 10   |      |

| HREG# Setup before HIOW#      | tsuHREG<br>(HIOW) | 5    |      | 5    |      | 5    |      | 5    |      |

| HREG# Hold following HIOW#    | thHREG<br>(HIOW)  | 0    |      | 0    |      | 0    |      | 0    |      |

| Wait Delay falling from HIOW# | tdIORDY<br>(HIOW) |      | 35   |      | 35   |      | 35   |      | na   |

| HIOW# high from Wait High     | tdHIOW<br>(IORDY) | 0    |      | 0    |      | 0    |      | na   |      |

| Wait Width Time               | tw (IORDY)        |      | 350  |      | 350  |      | 350  |      | na   |

Note: IORDY is not supported in this 80 ns mode. The maximum load on IORDY is 1 LSTTL with a 50 pF (40 pF below 120 nsec cycle time) total load. All time intervals are in nanoseconds. Although minimum time from IORDY high to HIOW# high is 0 nsec, the minimum HIOW# width is still met. HD refers to data provided by the CompactFlash Card to the system.

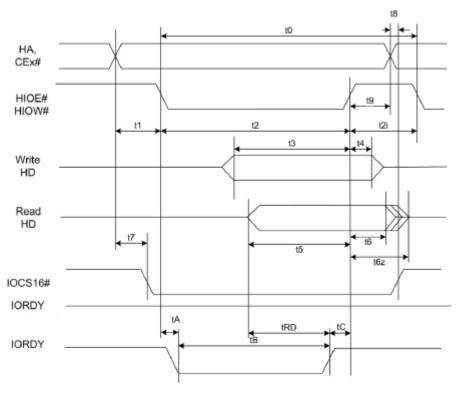

True IDE PIO Mode Read/Write Timing

| • True IDE PIO Wiode Rea                                                | ad/ VVIIIC I | g      |        |        |        |        |        |        |

|-------------------------------------------------------------------------|--------------|--------|--------|--------|--------|--------|--------|--------|

| Item                                                                    | Symbol       | Mode 0 | Mode 1 | Mode 2 | Mode 3 | Mode 4 | Mode 5 | Mode 6 |

| Cycle Time (Min.)                                                       | t0           | 600    | 383    | 240    | 180    | 120    | 100    | 80     |

| Address Valid to HIOE# / HIOW#<br>Setup (Min.)                          | t1           | 70     | 50     | 30     | 30     | 25     | 15     | 10     |

| HIOE# / HIOW# (Min.)                                                    | t2           | 165    | 125    | 100    | 80     | 70     | 65     | 55     |

| HIOE# / HIOW# (Min.) Register<br>(8-bit)                                | t2           | 290    | 290    | 290    | 80     | 70     | 65     | 55     |

| HIOE# / HIOW# Recovery Time<br>(Min.)                                   | t2i          | -      | -      | -      | 70     | 25     | 25     | 20     |

| HIOW# Data Setup (Min.)                                                 | t3           | 60     | 45     | 30     | 30     | 20     | 20     | 15     |

| HIOW# Data Hold (Min.)                                                  | t4           | 30     | 20     | 15     | 10     | 10     | 5      | 5      |

| HIOE# Data Setup (Min.)                                                 | t5           | 50     | 35     | 20     | 20     | 20     | 15     | 10     |

| HIOE# Data Hold (Min.)                                                  | t6           | 5      | 5      | 5      | 5      | 5      | 5      | 5      |

| HIOE# Data Tristate (Max.)                                              | t6Z          | 30     | 30     | 30     | 30     | 30     | 20     | 20     |

| Address Valid to IOCS16#<br>Assertion (Max.)                            | t7           | 90     | 50     | 40     | n/a    | n/a    | n/a    | n/a    |

| Address Valid to IOCS16# released (Max.)                                | t8           | 60     | 45     | 30     | n/a    | n/a    | n/a    | n/a    |

| HIOE# / HIOW# to Address Valid<br>Hold                                  | t9           | 20     | 15     | 10     | 10     | 10     | 10     | 10     |

| Read Data Valid to IORDY Active (Min.), if IORDY initially low after tA | tRD          | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| IORDY Setup Time                                                        | tA           | 35     | 35     | 35     | 35     | 35     | Na     | Na     |

| IORDY Pulse Width (Max.)                                                | tB           | 1250   | 1250   | 1250   | 1250   | 1250   | Na     | Na     |

| IORDY Assertion to Release (Max.)                                       | tC           | 5      | 5      | 5      | 5      | 5      | Na     | Na     |

<sup>\*</sup>All timing intervals are measured in nanoseconds. The maximum load on IOCS16# is 1 LSTTL with a 50 pF (40 pF below 120 nsec cycle time) total load. All time intervals are in nanoseconds. Although minimum time from IORDY high to HIOE# high is 0 nsec, the minimum HIOE# width is still met.

Where t0 denotes the minimum total cycle time; t2 represents the minimum command active time; t2i is the minimum command recovery time or command inactive time. Actual cycle time equals to the sum of actual command active time and actual command inactive time. The three timing requirements for t0, t2, and t2i are met. The minimum total cycle time requirement is greater than the sum of t2 and t2i, implying that a host implementation can extend either or both t2 or t2i to ensure that t0 is equal to or greater than the value reported in the device identity data. A CompactFlash card implementation supports any legal host implementation. The delay originates from HIOW# or HIOW# activation until the state of IORDY is first sampled. If IORDY is inactive, the host waits until IORDY is active before the PIO cycle is completed. When the CompactFlash Card is not driving IORDY, which is negated at tA after HIOE# or HIOW# activation, then t5 is met and tRD is inapplicable. When the CompactFlash Card is driving IORDY, which is negated at the time tA after HIOE# or HIOW# activation, then tRD is met and t5 is inapplicable.

Both t7 and t8 apply to modes 0, 1, and 2 only. For other modes, the signal is invalid.

Device address comprises CE1#, CE2#, and HA[2:0] Data comprises HD[15:0] (16-bit) or HD[7:0] (8-bit)

IOCS16# is shown for PIO modes 0, 1, and 2. For other modes, the signal is ignored.

The negation of IORDY by the device is used to lengthen the PIO cycle. Whether the cycle is to be extended is determined by the host after tA from the assertion of HIOE# or HIOW#. The assertion and negation of IORDY is described in the following cases. First, the device never negates IORDY, so no wait is generated. Secondly, device drives IORDY low before tA. Thus, wait is generated. The cycle is completed after IORDY is re-asserted. For cycles in which a wait is generated and HIOE# is asserted, the device places read data on D15-D00 for tRD before IORDY is asserted.

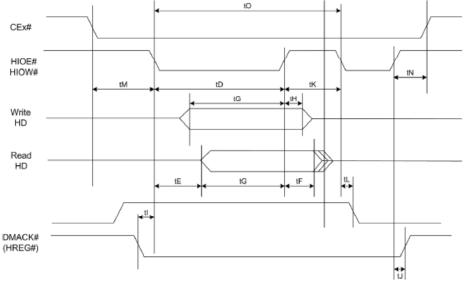

True IDE Multiword DMA Mode Read/Write Timing

| Item                                | Symbol | Mode 0 | Mode 1 | Mode 2 | Mode 3 | Mode 4 |

|-------------------------------------|--------|--------|--------|--------|--------|--------|

| Cycle Time (Min.)                   | tO     | 480    | 150    | 120    | 100    | 80     |

| HIOE#/HIOW# asserted width (Min.)   | tD     | 215    | 80     | 70     | 65     | 65     |

| HIOE# data access (Max.)            | tE     | 150    | 60     | 50     | 50     | 45     |

| HIOE# data hold (Min.)              | tF     | 5      | 5      | 5      | 5      | 5      |

| HIOE# / HIOW# data setup (Min.)     | tG     | 100    | 30     | 20     | 15     | 10     |

| HIOW# data hold (Min.)              | tH     | 20     | 15     | 10     | 5      | 5      |

| HREG# to HIOE#/HIOW# setup (Min.)   | tl     | 0      | 0      | 0      | 0      | 0      |

| HIOE#/HIOW# to HREG# hold<br>(Min.) | tJ     | 20     | 5      | 5      | 5      | 5      |

| HIOE# negated width (Min.)          | tKR    | 50     | 50     | 25     | 25     | 20     |

| HIOW# negated width (Min.)          | tKW    | 215    | 50     | 25     | 25     | 20     |

| HIOE# to DMARQ delay (Max.)         | tLR    | 120    | 40     | 35     | 35     | 35     |

| HIOW# to DMARQ delay (Max.)         | tLW    | 40     | 40     | 35     | 35     | 35     |

| CEx# valid to HIOE#/HIOW#           | tM     | 50     | 30     | 25     | 10     | 5      |

| CEx# hold                           | tN     | 15     | 10     | 10     | 10     | 10     |

Note: Where t0 is the minimum total cycle time and tD is minimum command active time, whereas tKR and tKW are minimum command recovery time or command inactive time for input and output cycles, respectively. Actual cycle time equals to the sum of actual command active time and actual command inactive time. The three timing requirements of t0, for instance, tD, tKR, and tKW, must be met. The minimum total cycle time requirement exceeds the sum of tD and tKR or tKW for input and output cycles respectively, implying that a host implementation can extend either or both tD and tKR or tKW as deemed necessary to ensure that t0 equals or exceeds the value reported in the device identify data. A CompactFlash card implementation supports any legal host, appropriate host implementation.

If a card cannot sustain continuous, minimum cycle time DMA transfers, it may negate DMARQ during the time from the start of a DMA transfer cycle (to suspend DMA transfers in progress) and re-assertion of the signal at a relatively later time to continue DMA transfer operations. The host may negate this signal to suspend the DMA transfer in progress.

Ultra DMA Signal Usage in Each Interface Mode

| Signal   | Туре   | Non-UDMA<br>Memory<br>Mode | PC Card Memory<br>Mode UDMA | PC Card IO Mode<br>UDMA     | True IDE Mode<br>UDMA       |

|----------|--------|----------------------------|-----------------------------|-----------------------------|-----------------------------|

| DMARQ    | Output | (INPACK#)                  | DMARQ#                      | DMARQ#                      | DMARQ                       |

| HREG#    | Input  | (REG#)                     | DMACK#                      | DMACK                       | DMACK#                      |

| HIOW#    | Input  | (IOWR#)                    | STOP <sup>1</sup>           | STOP <sup>1</sup>           | STOP <sup>1</sup>           |

| HIOE#    | Input  | (IORD#)                    | HDMARDY#(R) <sup>1,2</sup>  | HDMARDY#(R) <sup>1,2</sup>  | HDMARDY#(R) <sup>1,2</sup>  |

|          |        |                            | HSTROBE(W) <sup>1,3,4</sup> | HSTROBE(W) <sup>1,3,4</sup> | HSTROBE(W) <sup>1,3,4</sup> |

| IORDY    | Output | (WAIT#)                    | DDMARDY#(W) <sup>1,3</sup>  | DDMARDY#(W) <sup>1,3</sup>  | DDMARDY#(W) <sup>1,3</sup>  |

|          |        |                            | DSTROBE(R) <sup>1,2,4</sup> | DSTROBE(R) <sup>1,2,4</sup> | DSTROBE(R) <sup>1,2,4</sup> |

| HD[15:0] | Bidir  | (D[15:00])                 | D[15:00]                    | D[15:00]                    | D[15:00]                    |

| HA[10:0] | Input  | (A[10:00])                 | A[10:00]                    | A[10:00]                    | A[02:00] <sup>5</sup>       |

| CSEL#    | Input  | (CESL#)                    | CSEL#                       | CSEL#                       | CSEL#                       |

| HIRQ     | Output | (READY)                    | READY                       | INTRQ#                      | INTRQ                       |

| CE1#     | Input  | (CE1#)                     | CE1#                        | CE1#                        | CS0#                        |

| CE2#     |        | (CE2#)                     | CE2#                        | CE2#                        | CS1#                        |

- 1. UDMA interpretation of this signal is valid only during an Ultra DMA data burst.

- UDMA interpretation of this signal is valid only during an Ultra DMA data burst during a DMA Read command.

UDMA interpretation of this signal is valid only during an Ultra DMA data burst during a DMA Write command.

- 4. HSTROBE and DSTROBE signals are active on both rising and falling edges.5. Address lines 03-10 are not used in the True IDE mode.

**Ultra DMA Data Burst Timing Requirements**

| Parameter            | UDMA<br>Mode 0 | UDMA<br>Mode 1 | UDMA<br>Mode 2 | UDMA<br>Mode 3 | UDMA<br>Mode 4 | UDMA<br>Mode 5 | Measure<br>Location |

|----------------------|----------------|----------------|----------------|----------------|----------------|----------------|---------------------|

| t <sub>2CYCTYP</sub> | 240            | 160            | 120            | 90             | 60             | 40             | Sender              |

| t <sub>CYC</sub>     | 112            | 73             | 54             | 39             | 25             | 16.8           | See note            |

| t <sub>2CYC</sub>    | 230            | 153            | 115            | 86             | 57             | 38             | Sender              |

| t <sub>DS</sub>      | 15.0           | 10.0           | 7.0            | 7.0            | 5.0            | 4.0            | Recipient           |

| t <sub>DH</sub>      | 5.0            | 5.0            | 5.0            | 5.0            | 5.0            | 4.6            | Recipient           |

| t <sub>DVS</sub>     | 70.0           | 48.0           | 31.0           | 20.0           | 6.7            | 4.8            | Sender              |

| t <sub>DVH</sub>     | 6.2            | 6.2            | 6.2            | 6.2            | 6.2            | 4.8            | Sender              |

| t <sub>CS</sub>      | 15.0           | 10.0           | 7.0            | 7.0            | 5.0            | 5.0            | Device              |

| t <sub>CH</sub>      | 5.0            | 5.0            | 5.0            | 5.0            | 5.0            | 5.0            | Device              |

| t <sub>CVS</sub>     | 70.0           | 48.0           | 31.0           | 20.0           | 6.7            | 10.0           | Host                |

| t <sub>CVH</sub>     | 6.2            | 6.2            | 6.2            | 6.2            | 6.2            | 10.0           | Host                |

| t <sub>ZFS</sub>     | 0              | 0              | 0              | 0              | 0              | 35             | Device              |

| t <sub>DZFS</sub>    | 70.0           | 48.0           | 31.0           | 20.0           | 6.7            | 25             | Sender              |

| Parameter           | UDMA<br>Mode 0 | UDMA<br>Mode 1 | UDMA<br>Mode 2 | UDMA<br>Mode 3 | UDMA<br>Mode 4 | UDMA<br>Mode 5 | Measure<br>Location |

|---------------------|----------------|----------------|----------------|----------------|----------------|----------------|---------------------|

| t <sub>FS</sub>     | 230            | 200            | 170            | 130            | 120            | 90             | Device              |

| t <sub>LI</sub>     | 0 - 150        | 0 - 150        | 0 - 150        | 0 - 100        | 0 - 100        | 0 - 75         | See note            |

| t <sub>MLI</sub>    | 20             | 20             | 20             | 20             | 20             | 20             | Host                |

| t <sub>UI</sub>     | 0              | 0              | 0              | 0              | 0              | 0              | Host                |

| t <sub>AZ</sub>     | 10             | 10             | 10             | 10             | 10             | 10             | See note            |

| t <sub>ZAH</sub>    | 20             | 20             | 20             | 20             | 20             | 20             | Host                |

| t <sub>ZAD</sub>    | 0              | 0              | 0              | 0              | 0              | 0              | Device              |

| t <sub>ENV</sub>    | 20 - 70        | 20 - 70        | 20 – 70        | 20 - 55        | 20 - 55        | 20 - 50        | Host                |

| t <sub>RFS</sub>    | 75             | 70             | 60             | 60             | 60             | 50             | Sender              |

| t <sub>RP</sub>     | 160            | 125            | 100            | 100            | 100            | 85             | Recipient           |

| t <sub>IORDYZ</sub> | 20             | 20             | 20             | 20             | 20             | 20             | Device              |

| t <sub>ZIORDY</sub> | 0              | 0              | 0              | 0              | 0              | 0              | Device              |

| t <sub>ACK</sub>    | 20             | 20             | 20             | 20             | 20             | 20             | Host                |

| t <sub>SS</sub>     | 50             | 50             | 50             | 50             | 50             | 50             | Sender              |

#### Notes:

All timing are in nanoseconds and all timing measurement switching points (low to high and high to low) are taken at 1.5V. All signal transitions for a timing parameter are determined at the connector specified in the measurement location column. Parameter  $t_{CYC}$  is determined at the connector of the recipient farthest from the sender, while parameter  $t_{LI}$  is determined at the connector of a sender or recipient responding to an incoming transition from the recipient or sender, respectively. Both incoming signal and outgoing response are determined at the same connector. Parameter  $t_{AZ}$  is determined at the connector of a sender or recipient driving the bus, and must release the bus to allow for a bus turnaround.

Ultra DMA Data Burst Timing Descriptions

| Parameter            | Description & Comment                                                                                                                   | Note |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|

| t <sub>2CYCTYP</sub> | Typical sustained average two cycle time                                                                                                |      |

| t <sub>CYC</sub>     | Cycle time allowing for asymmetry and clock variations (from STROBE edge to STROBE edge)                                                |      |

| t <sub>2CYC</sub>    | Two cycle time allowing for clock variations (from rising edge to next rising edge or from falling edge to next falling edge of STROBE) |      |

| t <sub>DS</sub>      | Data setup time at recipient (from data valid until STROBE edge)                                                                        | 2, 5 |

| t <sub>DH</sub>      | Data hold time at recipient (from STROBE edge until data may become invalid)                                                            | 2,5  |

| t <sub>DVS</sub>     | Data valid setup at sender (from data valid until STROBE edge)                                                                          | 3    |

| $t_{DVH}$            | Data valid hold time at sender (from STROBE edge until data may become invalid)                                                         | 3    |

| t <sub>CS</sub>      | CRC word setup time at device                                                                                                           | 2    |

| t <sub>CH</sub>      | CRC word hold time at device                                                                                                            | 2    |

| $t_{\text{CVS}}$     | CRC word valid setup time at host (from CRC valid until DMACK(#) negation)                                                              | 3    |

| t <sub>CVH</sub>     | CRC word valid hold time at sender (from DMACK(#) negation until CRC may become invalid)                                                | 3    |

| Parameter           | Description & Comment                                                                                                                         | Note |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|

| $t_{ZFS}$           | Time from STROBE output released-to-driving until the first transition of critical timing                                                     |      |

| t <sub>DZFS</sub>   | Time from data output released-to-driving until the first transition of critical timing)                                                      |      |

| t <sub>FS</sub>     | First STROBE time (for device to first negate DSTROBE from STOP during a data in burst)                                                       |      |

| $t_{LI}$            | Limited interlock time                                                                                                                        | 1    |

| t <sub>MLI</sub>    | Interlock time with minimum                                                                                                                   | 1    |

| t <sub>UI</sub>     | Unlimited interlock time                                                                                                                      | 1    |

| $t_{AZ}$            | Maximum time allowed for output drives to release (from asserted or negated)                                                                  |      |

| $t_{ZAH}$           | Minimum delay time required for output                                                                                                        |      |

| $t_{ZAD}$           | Drivers to assert or negate (from released)                                                                                                   |      |

| $t_{ENV}$           | Envelope time (from DMACK(#)) to STOP and HDMARDY# during data in burst initiation and from DMACK(#) to STOP during data out burst initiation |      |

| t <sub>RFS</sub>    | Ready-to-final-STROBE time (no STROBE edges shall be sent this long after negation of DMARDY#)                                                |      |

| t <sub>RP</sub>     | Ready-to-pause time (that recipient shall wait to pause after negating DMARDY#)                                                               |      |

| t <sub>IORDYZ</sub> | Maximum time before releasing IORDY                                                                                                           | 6    |

| t <sub>ZIORDY</sub> | Minimum time before driving IORDY                                                                                                             | 4, 6 |

| t <sub>ACK</sub>    | Setup and hold times for DMACK(#) (before assertion or negation                                                                               |      |

| t <sub>SS</sub>     | Time from STROBE edge to negation of DMARQ(#) or assertion of STOP (when sender terminates a burst)                                           |      |

#### Notes

- 1. Parameters tUI, tMLI and tLI represent sender-to-recipient or recipient-to-sender interlocks, for instance, one agent (sender or recipient) is waiting for the other agent to respond with a signal before proceeding. Parameter tUI denotes an unlimited interlock that has no maximum time value; tMLI represents a limited time-out that has defined minimum; tLI is a limited time-out that has a defined maximum.

- 2. The 80-conductor cabling is required to meet setup (tDS, tCS) and hold (tDH, tCH) times in modes exceeding 2.

- 3. Timing for tDVS, tDVH, tCVS, and tCVH must be met for lumped capacitive loads of 15 and 40 pF at the connector where the data and STROBE signals have the same capacitive load value.

- 4. Fall all timing modes, parameter tZIORDY may be greater than tENV since the host has a pull up on IORDY giving it a known state when released.

- 5. Parameters tDS and tDH for mode 5 are defined for a recipient at the end of a cable only in a configuration that has a single device located at the cable end. This configuration can result in tDS, and tDH for mode 5 at the middle connector having minimum values of 3.0 and 3.9 nanoseconds respectively.

- 6. The parameters are only applied to True IDE mode operation.

Ultra DMA Sender & Recipient IC Timing Requirements

| Item               | UD                                                                  | MA                                                                              | UD   | MA     | UD   | MA     | UD   | MA     | UD   | MA     | UD   | MA     |

|--------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------|------|--------|------|--------|------|--------|------|--------|------|--------|

|                    | Mode                                                                | 0 (ns)                                                                          | Mode | 1 (ns) | Mode | 2 (ns) | Mode | 3 (ns) | Mode | 4 (ns) | Mode | 5 (ns) |

|                    | Min.                                                                | Max.                                                                            | Min. | Max.   | Min. | Min.   | Max. | Max.   | Min. | Max.   | Min. | Max.   |

| t <sub>DSIC</sub>  | 14.7                                                                |                                                                                 | 9.7  |        | 6.8  |        | 6.8  |        | 4.8  |        | 2.3  |        |

| t <sub>DHIC</sub>  | 4.8                                                                 |                                                                                 | 4.8  |        | 4.8  |        | 4.8  |        | 4.8  |        | 2.8  |        |

| t <sub>DVSIC</sub> | 72.9                                                                |                                                                                 | 50.9 |        | 33.9 |        | 22.6 |        | 9.5  |        | 6.0  |        |

| t <sub>DVHIC</sub> | 9.0                                                                 |                                                                                 | 9.0  |        | 9.0  |        | 9.0  |        | 9.0  |        | 6.0  |        |

| t <sub>DSIC</sub>  |                                                                     | Recipient IC data setup time (from data valid until STROBE edge)                |      |        |      |        |      |        |      |        |      |        |

| t <sub>DHIC</sub>  |                                                                     | Recipient IC data hold time (from STROBE edge until data may become invalid)    |      |        |      |        |      |        |      |        |      |        |

| t <sub>DVSIC</sub> | Sender IC data valid setup time (from data valid until STROBE edge) |                                                                                 |      |        |      |        |      |        |      |        |      |        |

| t <sub>DVHIC</sub> |                                                                     | Sender IC data valid hold time (from STROBE edge until data may become invalid) |      |        |      |        |      |        |      |        |      |        |

Note: all timing switching point measurements are taken at 1.5V. The correct data value is captured by the recipient given input data with a slew rate of 0.4 V/ns rising and falling and the input STROBE with a slew rate of 0.4 V/ns rising and falling at tDSIC and tDHIC timing (measured at 1.5V). Parameters tDVSIC and tDVHIC must be met for lumped capacitive loads of 15 and 40 pF at the IC where all signals have the same capacitive load value. Noise that can couple onto the output signals from external sources is not included in these values.

Ultra DMA AC Signal Requirements

| Item                                  | Symbol            | Min.   | Max.   |

|---------------------------------------|-------------------|--------|--------|

|                                       |                   | (V/ns) | (V/ns) |

| Rising Edge Slew Rate for any signal  | S <sub>RISE</sub> |        | 1.25   |

| Falling Edge Slew Rate for any signal | S <sub>FALL</sub> |        | 1.25   |

#### Notes:

- 1. The sender is tested while driving an 18-inch, 80-conductor cable with PVC insulation. The signal being tested must be cut at a test point such that it has no trace, cable, or recipient loading after the test point. All other signals must remain connected through to the recipient. The test point should be located between a sender's series termination resistor and within 0.5 inch or less from where the conductor exits the connector. If the test point is on a cable conductor rather than on the PCB, an adjacent ground conductor must also be cut within 0.5 inch or the connector.

- 2. The test load and test points should be soldered directly to the exposed source side connectors. The test loads consist of a 15 pF or a 40 pF, 5%, 0.08 inch by 0.05 inch surface mount or relatively smaller capacitor connected between the test point and ground. Slew rates are met for both capacitor values.

- 3. Measurements must be taken at the test point using a <1 pF, >100 Kohm, 1GHz probe and a 500 MHz oscilloscope. The average rate is measured from 20% ~ 80% of the settled VOH level with data transitions at least 120 nanoseconds apart. The settled VOH level must be measured as the average high output level under the defined test conditions from 100 nanoseconds after 80% of a rising edge until 20% of the subsequent falling edge.

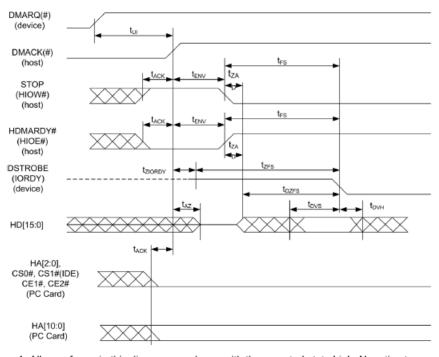

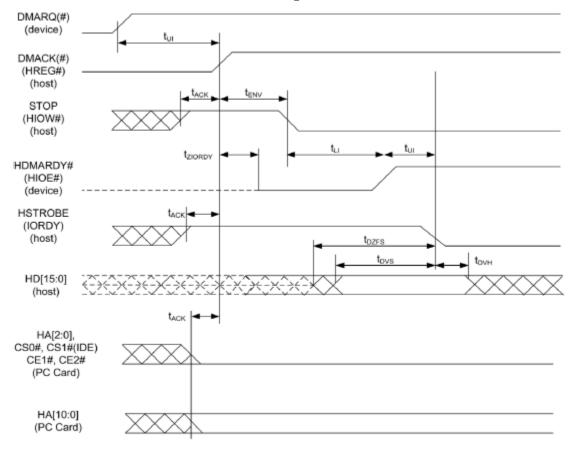

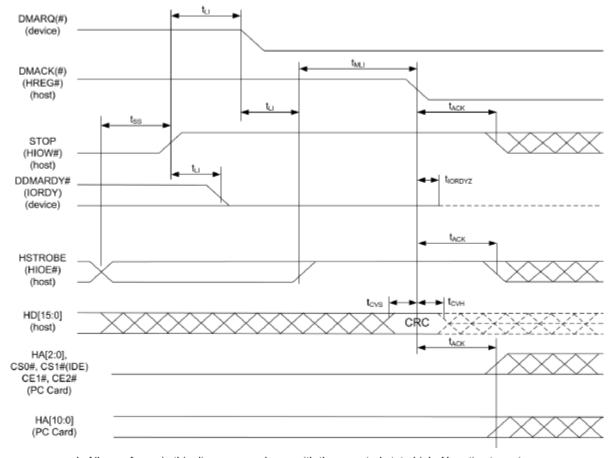

### Ultra DMA Data-in Burst Initiation Timing

- All waveforms in this diagram are shown with the asserted state high. Negative true signals are inverted on the bus relative to the diagram.

- 2. The definitions for the IORDY:DDMARDY#:DSTROBE, HIOE#: HDMARDY#: HSTROBE and HIOW#: STOP signal lines are not in effect until DMARQ(#) and DMACK(#) are asserted. Notably, HA[2:0], CS0# and CS1# are True IDE mode signal definitions, and HA[10:0], CE1# and CE2# are PC Card mode signals. The Bus polarity of DMACK(#) and DMARQ(#) is based on the active interface mode.

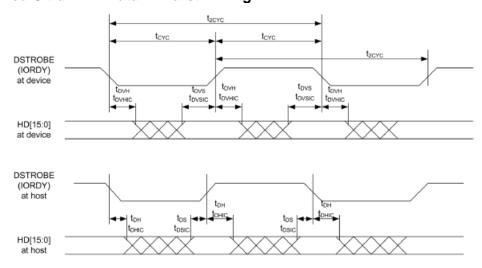

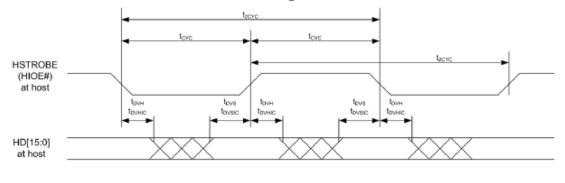

#### Sustained Ultra DMA Data-in Burst Timing

HD[15:0] and IORDY signals are shown at both the host and device to emphasize that neither cable settling time nor cable propagation delay allow data signals to be considered stable at the host until after they are driven by the device.

#### • Ultra DMA Data-in Burst Host Pause Timing

- All waveforms in this diagram are shown with the asserted state high. Negative true signals are inverted on the bus relative to the diagram.

- 2. The host can implement STOP to request termination of the Ultra DMA data burst at a time no sooner than when tRP after HDMARDY# is negated.

- 3. After negating HDMARDY#, the host may receive zero, 1, 2, or 3 additional data words from the device.

- 4. Bus polarities of the DMARQ(#) and DMACK(#) signals are dependent on the active interface mode.

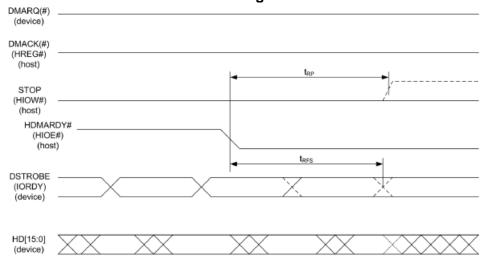

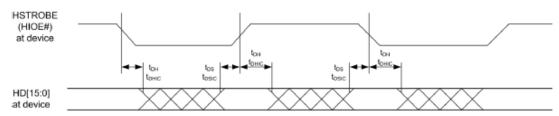

### • Ultra DMA Data-in Burst Device Termination Timing

- All waveforms in this diagram are shown with the asserted state high. Negative true signals are inverted on the bus relative to the diagram.

- 2. Definitions for STOP, HDMARDY#, and DSTROBE signal lines are no longer in effect once DMARQ(#) and DMACK(#) are negated. The HA[2:0], CS0# and CS1# are True IDE mode signal definitions. HA[10:0], CE1# and CE2# are PC Card mode signals. Bus polarities of DMARQ(#) and DMACK(#) are dependent on the active interface mode.

### Ultra DMA Data-in Burst Host Termination Timing

- 1. All waveforms in this diagram are shown with the asserted state high. Negative true signals are inverted on the bus relative to the diagram.

- 2. Definitions for STOP, HDMARDY#, and DSTROBE signal lines are no longer in effect once DMARQ(#) and DMACK(#) are negated. The HA[2:0], CS0# and CS1# are True IDE mode signal definitions. The HA[10:0], CE1# and CE2# are PC Card mode signal definitions. Bus polarities of DMARQ(#) and DMACK(#) are dependent on the active interface mode.

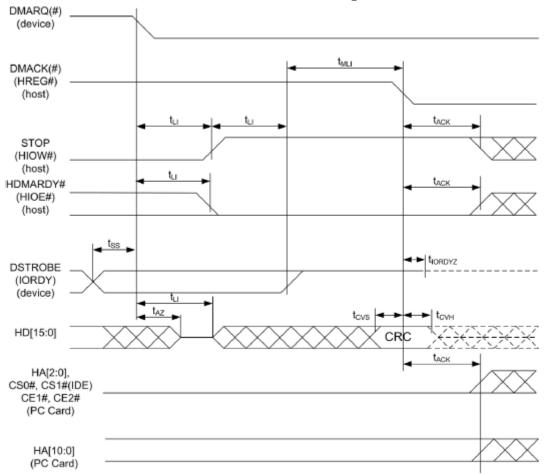

### • Ultra DMA Data-out Burst Initiation Timing

- 1. All waveforms in this diagram are shown with the asserted state high. Negative true signals are inverted on the bus relative to the diagram.

- 2. Definitions for STOP, DDMARDY#, and HSTROBE signal lines are not in effect until DMARQ(#) and DMACK(#) are asserted. The HA[2:0], CS0# and CS1# are True IDE mode signal definitions. The HA[10:0], CE1# and CE2# are PC Card mode signal definitions. Bus polarities of DMARQ(#) and DMACK(#) are dependent on the active interface mode.

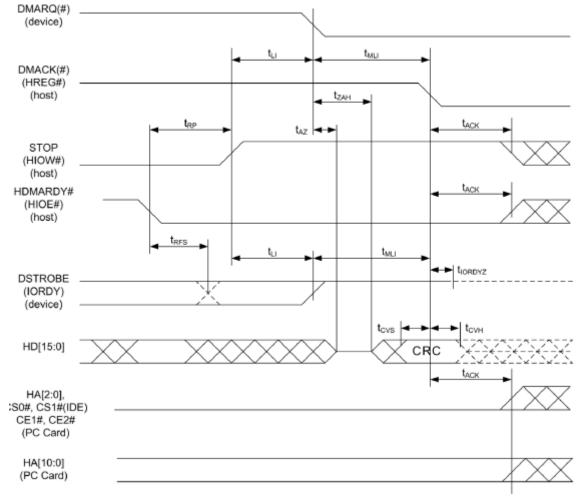

### Sustained Ultra DMA Data-out Burst Timing

Data (HD[15:0]) and HSTROBE signals are shown at both the device and host to emphasize that neither cable settling time nor cable propagation delay allow for data signals to be considered stable at the device until after they are driven by a host.

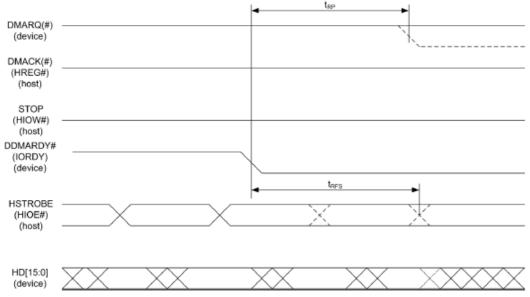

#### Ultra DMA Data-out Burst Device Pause Timing

- All waveforms in this diagram are shown with the asserted state high. Negative true signals are inverted on the bus relative to the diagram.

- The device can negate DMARQ(#) when requesting termination of the Ultra DMA data burst no sooner than tRP after DDMARDY# is negated.

- After negating DDMARDY#, the device may receive zero, 1, 2, or 3 additional data words from the host.

- 4. The bus polarities of DMARQ(#) and DMACK(#) are dependent on the active interface mode.

- 1. All waveforms in this diagram are shown with the asserted state high. Negative true signals are inverted on the bus relative to the diagram.

- 2. Definitions for the STOP, DDMARDY#, and HSTROBE signal lines are no longer in effect [after OR once] DMARQ(#) and DMACK(#) are negated. The HA[2:0], CS0# and CS1# are True IDE mode signal definitions. The HA[10:0], CE1# and CE2# are PC Card mode signals. Bus polarities of DMARQ(#) and DMACK(#) are dependent on the active interface mode.

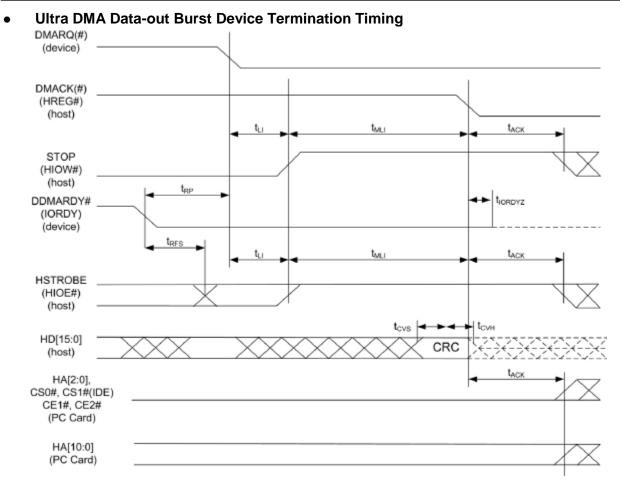

### • Ultra DMA Data-out Burst Host Termination Timing

- 1. All waveforms in this diagram are shown with the asserted state high. Negative true signals are inverted on the bus relative to the diagram.

- 2. Definitions for the STOP, DDMARDY#, and HSTROBE signal lines are no longer in effect once DMARQ(#) and DMACK(#) are negated. The HA[2:0], CS0# and CS1# are True IDE mode signal definitions. The HA[10:0], CE1# and CE2# are PC Card mode signal definitions. Bus polarities of DMARQ(#) and DMACK(#) are dependent on the active interface mode.

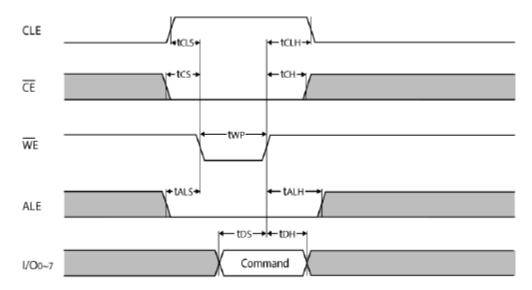

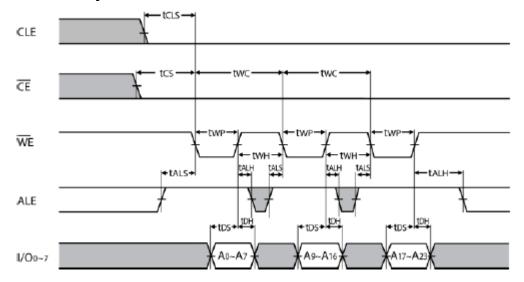

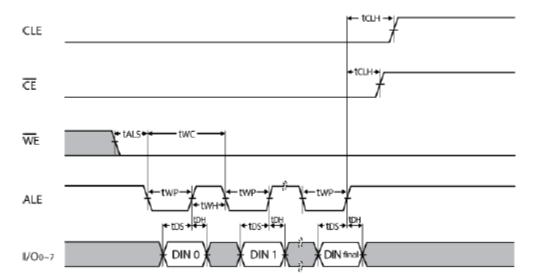

### • Flash Interface AC Characteristics

| Parameter         | Symbol | Timing                   |                         |     |

|-------------------|--------|--------------------------|-------------------------|-----|

|                   |        | Disable Flash CMD Extend | Enable Flash CMD Extend |     |

| CLE Setup time    | tCLS   | 2                        | 4                       | tCK |

| CLE hold time     | tCLH   | 1                        | 2                       | tCK |

| ALE setup time    | tALS   | 2                        | 4                       | tCK |

| ALE hold time     | tALH   | 1                        | 2                       | tCK |

| WE pulse width    | tWP    | 1                        | 2                       | tCK |

| Data setup time   | tDS    | 1                        | 3                       | tCK |

| Data hold time    | tDH    | 1                        | 1                       | tCK |

| Write cycle time  | tWC    | 2                        | 4                       | tCK |

| WE high hold time | tWH    | 1                        | 2                       | tCK |

| WE Low hold time  | tWP    | 1                        | 2                       | tCK |

| Parameter            | Symbol | Timing | Unit |

|----------------------|--------|--------|------|

|                      |        |        |      |

| WE Pulse Width       | tWP    | 0.5    | tCK  |

| Data setup time      | tDS    | 0.75   | tCK  |

| Data hold time       | tDH    | 0.25   | tCK  |

| Write cycle time     | tWC    | 1      | tCK  |

| WE high hold time    | tWH    | 0.5    | tCK  |

| WE pulse width       | tWP    | 0.5    | tCK  |

| Read cycle time      | tRC    | 1      | tCK  |

| RE Pulse Width       | tRP    | 0.5    | tCK  |

| RE High Hold<br>Time | tREH   | 0.5    | tCK  |

### • Command Latch Cycle

### Address Latch Cycle

### Input Data Latch Cycle

### 7. Mechanical Specifications

### 7.1 Dimensions

Figure 7-1: Physical Dimensions

### 7.2 Write Protect by Hardware Switch

This industrial CompactFlash comes with write protect function enabled by a hardware mechanical switch. Users can activate/deactivate the write protection with it. Please refer to the illustration below for locating the switch.

#### Description of Apacer Write Protect:

Apacer implements the Virtual Write scheme that allows write commands to go through the flash controller and data temporarily stored. The OS can then function normally and no data has been actually written into the flash. Since the Virtual Write scheme runs at device level, it requires no software or driver installation and is independent from the host OS.

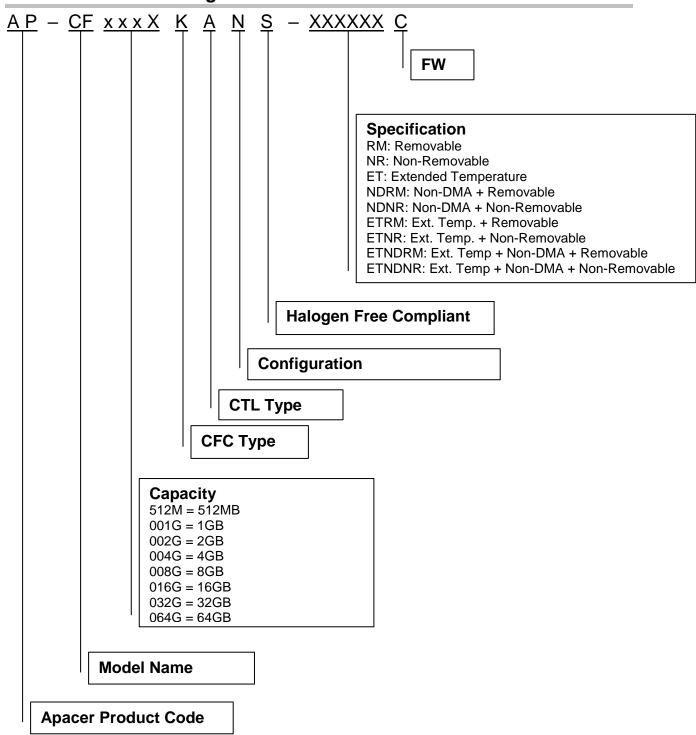

### 8. Product Ordering Information

### **8.1 Product Code Designations**

### **8.2 Valid Combinations**

### 8.2.1 Standard Temperature (0°C ~ 70°C)

### 8.2.1.1 Non-Removable

| Capacity | AP/N              |

|----------|-------------------|

| 512MB    | AP-CF512MKANS-NRC |

| 1GB      | AP-CF001GKANS-NRC |

| 2GB      | AP-CF002GKANS-NRC |

| 4GB      | AP-CF004GKANS-NRC |

| 8GB      | AP-CF008GKANS-NRC |

| 16GB     | AP-CF016GKANS-NRC |

| 32GB     | AP-CF032GKANS-NRC |

| 64GB     | AP-CF064GKANS-NRC |

### 8.2.1.2 Removable

| Capacity | AP/N              |

|----------|-------------------|

| 512MB    | AP-CF512MKANS-RMC |

| 1GB      | AP-CF001GKANS-RMC |

| 2GB      | AP-CF002GKANS-RMC |

| 4GB      | AP-CF004GKANS-RMC |

| 8GB      | AP-CF008GKANS-RMC |

| 16GB     | AP-CF016GKANS-RMC |

| 32GB     | AP-CF032GKANS-RMC |

| 64GB     | AP-CF064GKANS-RMC |

#### 8.2.1.3 Non-DMA + Removable

| Capacity | AP/N                |

|----------|---------------------|

| 512MB    | AP-CF512MKANS-NDRMC |

| 1GB      | AP-CF001GKANS-NDRMC |

| 2GB      | AP-CF002GKANS-NDRMC |

| 4GB      | AP-CF004GKANS-NDRMC |

| 8GB      | AP-CF008GKANS-NDRMC |

| 16GB     | AP-CF016GKANS-NDRMC |

| 32GB     | AP-CF032GKANS-NDRMC |

| 64GB     | AP-CF064GKANS-NDRMC |

### 8.2.1.4 Non-DMA + Non-Removable

| Capacity | AP/N                |

|----------|---------------------|

| 512MB    | AP-CF512MKANS-NDNRC |

| 1GB      | AP-CF001GKANS-NDNRC |

| 2GB      | AP-CF002GKANS-NDNRC |

| 4GB      | AP-CF004GKANS-NDNRC |

| 8GB      | AP-CF008GKANS-NDNRC |

| 16GB     | AP-CF016GKANS-NDNRC |

| 32GB     | AP-CF032GKANS-NDNRC |

| 64GB     | AP-CF064GKANS-NDNRC |

### 8.2.2 Extended Temperature (-40°C ~ 85°C)

### 8.2.2.1 Extended Temp. + Non-Removable

| Capacity | AP/N                |

|----------|---------------------|

| 512MB    | AP-CF512MKANS-ETNRC |

| 1GB      | AP-CF001GKANS-ETNRC |

| 2GB      | AP-CF002GKANS-ETNRC |

| 4GB      | AP-CF004GKANS-ETNRC |

| 8GB      | AP-CF008GKANS-ETNRC |

| 16GB     | AP-CF016GKANS-ETNRC |

| 32GB     | AP-CF032GKANS-ETNRC |

| 64GB     | AP-CF064GKANS-ETNRC |

### 8.2.2.2 Extended Temp. + Removable

| Capacity | AP/N                |

|----------|---------------------|

| 512MB    | AP-CF512MKANS-ETRMC |

| 1GB      | AP-CF001GKANS-ETRMC |

| 2GB      | AP-CF002GKANS-ETRMC |

| 4GB      | AP-CF004GKANS-ETRMC |

| 8GB      | AP-CF008GKANS-ETRMC |

| 16GB     | AP-CF016GKANS-ETRMC |

| 32GB     | AP-CF032GKANS-ETRMC |

| 64GB     | AP-CF064GKANS-ETRMC |

### 8.2.2.3 Extended Temp. + Non-DMA + Removable

| Capacity | AP/N                  |

|----------|-----------------------|

| 512MB    | AP-CF512MKANS-ETNDRMC |

| 1GB      | AP-CF001GKANS-ETNDRMC |

| 2GB      | AP-CF002GKANS-ETNDRMC |

| 4GB      | AP-CF004GKANS-ETNDRMC |

| 8GB      | AP-CF008GKANS-ETNDRMC |

| 16GB     | AP-CF016GKANS-ETNDRMC |

| 32GB     | AP-CF032GKANS-ETNDRMC |

| 64GB     | AP-CF064GKANS-ETNDRMC |

### 8.2.2.4 Extended Temp. +Non-DMA + Non-Removable

| Capacity | AP/N                  |  |

|----------|-----------------------|--|

| 512MB    | AP-CF512MKANS-ETNDNRC |  |

| 1GB      | AP-CF001GKANS-ETNDNRC |  |

| 2GB      | AP-CF002GKANS-ETNDNRC |  |

| 4GB      | AP-CF004GKANS-ETNDNRC |  |