## High Power Negative Voltage Hot Swap Controller with Energy Monitor **DESCRIPTION**

## FEATURES

ANALOG

- Drives Two Gates for High Power Applications

- Configurable Parallel, Staged Start or Single Modes

POWER BY

- Protects MOSFET with SOA Timer

- Programmable 15mV to 30mV Current Limit Sense Voltage with 2% Accuracy and Adjustable Foldback

- 8-Bit to 16-Bit Gear-Shift ADC with 0.5% Accuracy

- Monitors Voltages, Currents, Power and Energy

- Nonvolatile Configuration and Fault Recording

- Floating Topology for Rugged High Voltage Operation

- Selectable Inrush Control: dV/dt or Current Limit

- I<sup>2</sup>C/SMBus or Single-Wire Broadcast Interfaces

- Min/Max ADC Measurement Logging with Alerts

- Reboots on I<sup>2</sup>C Command with Programmable Delay

-52V/2500W Hot Swap Controller with Telemetry

- Adjustable Input UV/OV Thresholds and Hysteresis

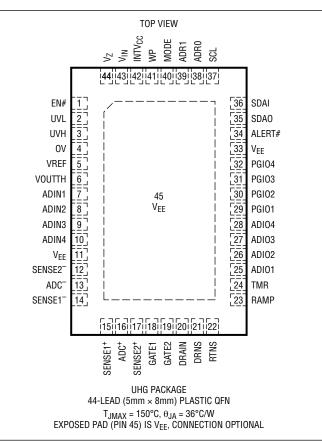

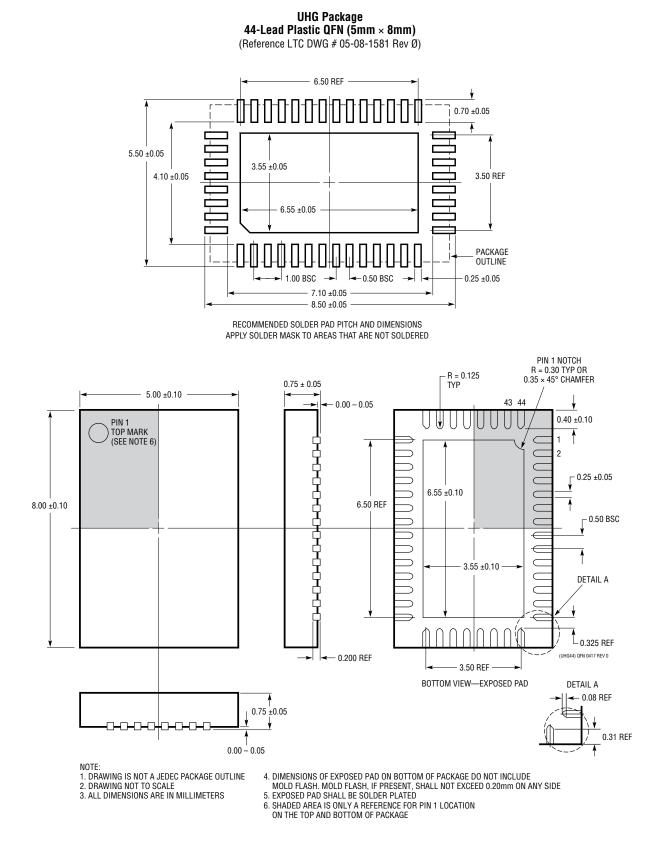

- 44-Pin 5mm × 8mm QFN Package

## **APPLICATIONS**

- Telecom Infrastructure

- –48V Distributed Power Systems

- Servers and Data Centers

- Power Monitors

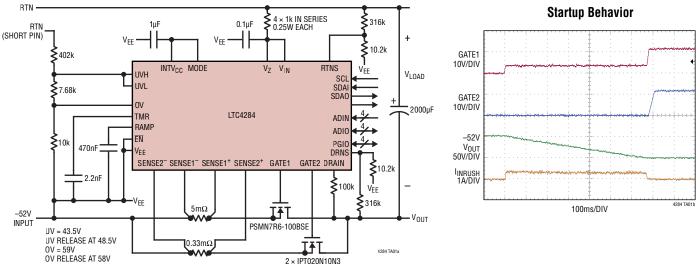

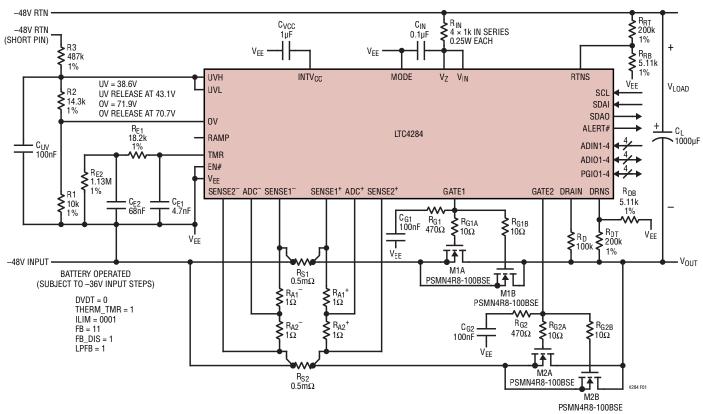

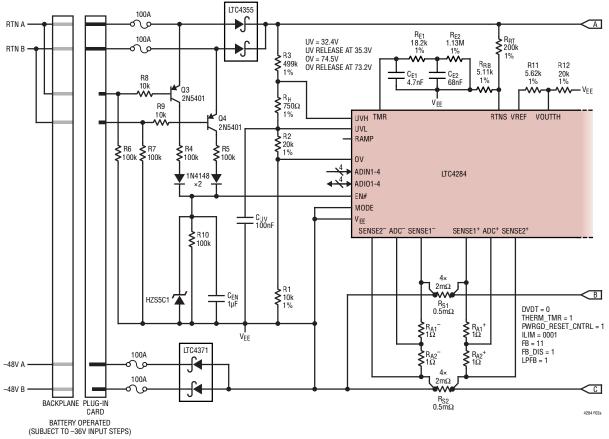

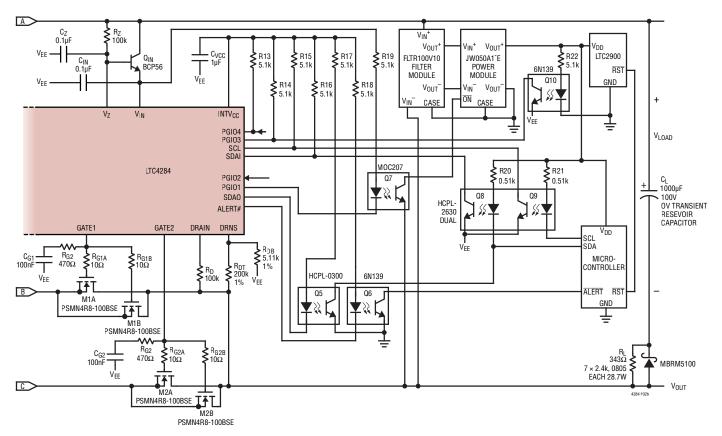

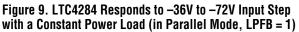

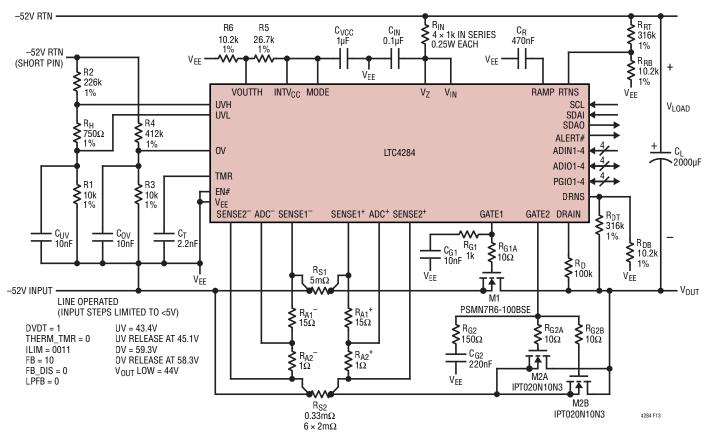

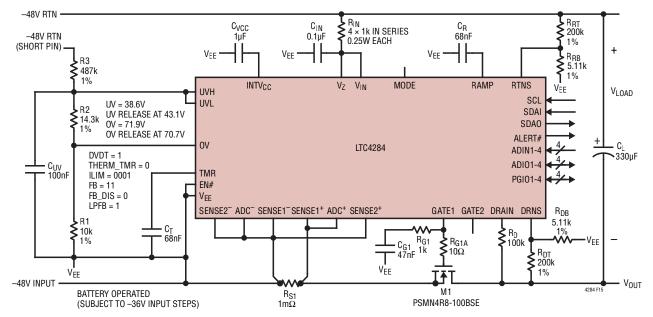

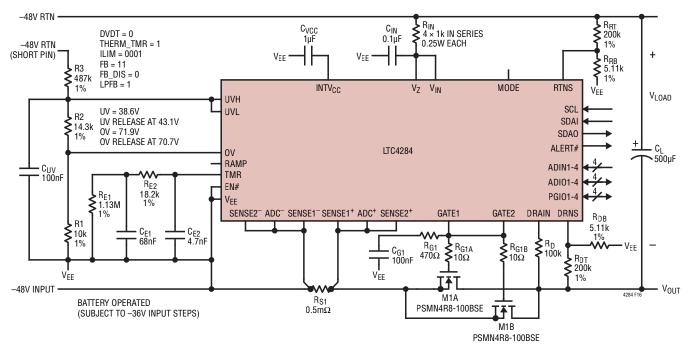

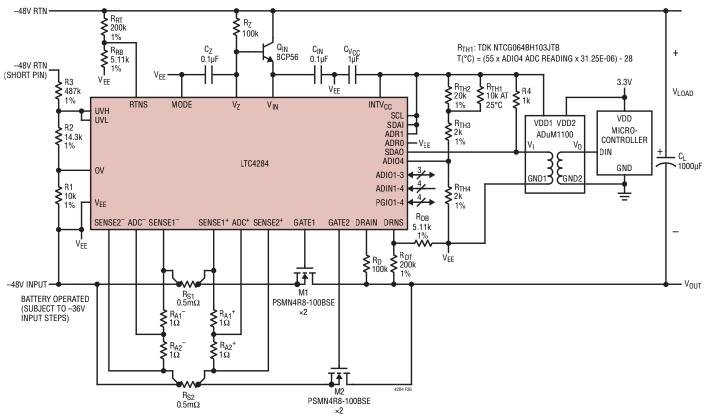

## TYPICAL APPLICATION

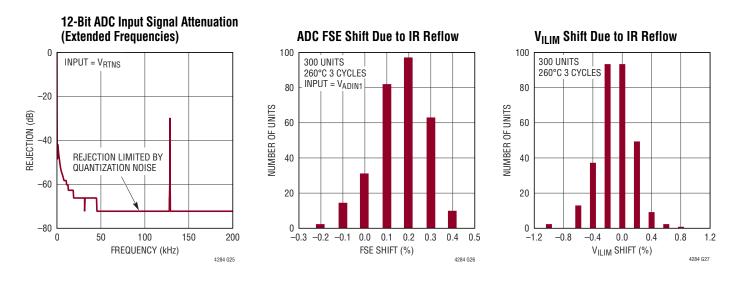

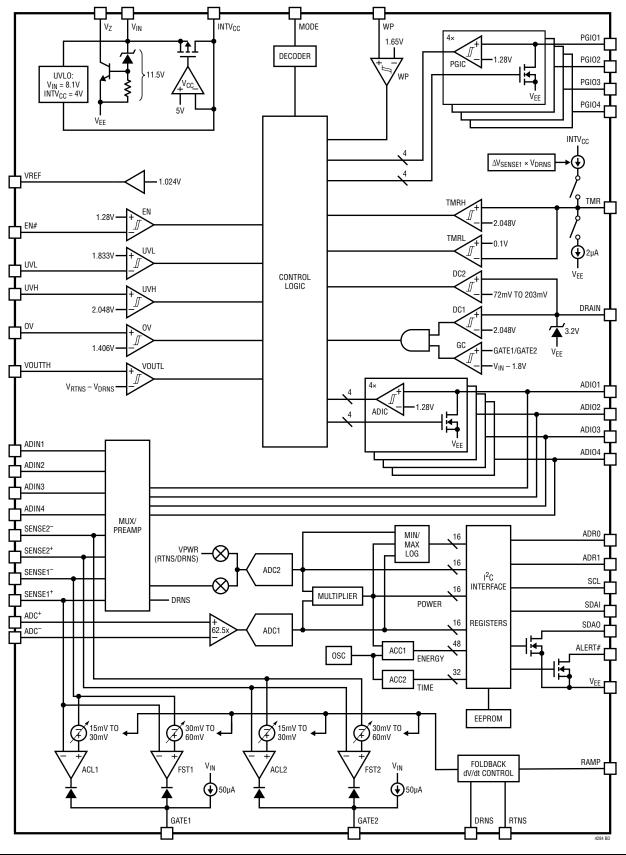

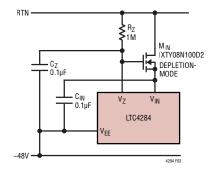

#### The LTC<sup>®</sup>4284 negative voltage hot swap controller drives external N-channel MOSFETs to allow a board to be safely inserted and removed from a live backplane. The dualgate, multi-mode drivers optimize the MOSFET safe operating area (SOA) for a variety of power levels. The SOA timer limits MOSFET temperature rise for reliable protection against overstresses.

An I<sup>2</sup>C interface and onboard gear-shift ADC allow monitoring of board current, voltage, power, energy, and fault status. An available single-wire broadcast mode simplifies the interface by eliminating two isolators. The included EEPROM provides black-box capturing and nonvolatile configuration of fault behavior.

Additional features respond to input UV/OV, interrupt the host when a fault has occurred, notify when output power is good, detect insertion of a board, turn off the MOSFETs if an external supply monitor fails to indicate power good within a timeout period, and auto-reboot after a programmable delay following a host commanded turn-off.

All registered trademarks and trademarks are the property of their respective owners. Protected by U.S. patents, including 8230151, 7382167, 9634480, 9634481, 10263414.

For more information www.analog.com

# TABLE OF CONTENTS

| Features                               | 1  |

|----------------------------------------|----|

| Applications                           |    |

| Typical Application                    | 1  |

| Description                            |    |

| Absolute Maximum Ratings               | 3  |

| Order Information                      |    |

| Pin Configuration                      | 3  |

| Electrical Characteristics             | 4  |

| I <sup>2</sup> C Timing Diagram        | 9  |

| Typical Performance Characteristics    | 9  |

| Pin Functions                          | 12 |

| Block Diagram                          | 16 |

| Operation                              | 17 |

| Applications Information               | 18 |

| Input Power Supply                     | 18 |

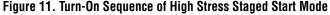

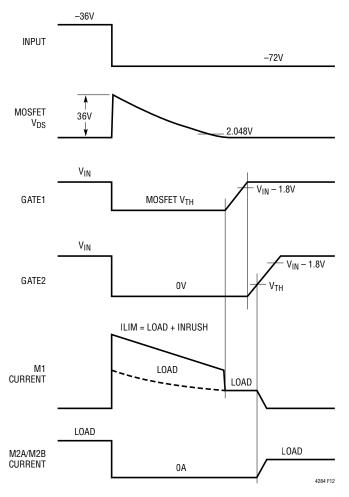

| Turn-On Sequence                       | 20 |

| Inrush Control                         | 22 |

| Power Good Monitors and PGI Fault      | 23 |

| Turn-Off Sequence                      | 24 |

| Overcurrent Protection                 | 24 |

| SOA Timer                              |    |

| Overcurrent Fault and Auto-Retry       | 27 |

| Current Limit Adjustment               |    |

| Current Limit Foldback                 | 27 |

| FET Bad Fault and Auto-Retry           |    |

| Input Step and Optimum Output Ramp     |    |

| Dual-Gate Operation Modes              |    |

| Parallel Mode (Mode 2)                 |    |

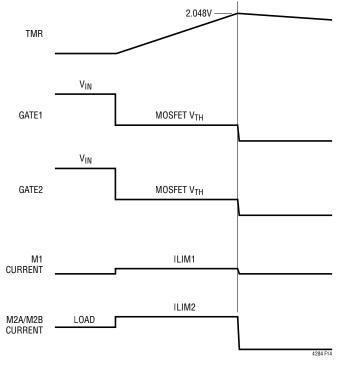

| High Stress Staged Start Mode (Mode 3) |    |

| Low Stress Staged Start (Mode 4)       |    |

| Single Driver Mode (Mode 1)            |    |

| Overvoltage Fault and Auto-Retry       |    |

| Undervoltage Fault and Auto-Retry      |    |

| FET Short Fault                        |    |

| Power Failed Fault                     |    |

| External Fault and Auto-Retry          |    |

| Cooling Delay                          | 38 |

|    | Resetting Faults                                                 |    |

|----|------------------------------------------------------------------|----|

|    | Alarms                                                           |    |

|    | EN# Pin                                                          |    |

|    | ON Bit                                                           |    |

|    | Turning the LTC4284 On and Off                                   |    |

|    | Configuring PGIO and ADIO Pins<br>Design Examples                |    |

|    | Example 1: Design Procedure of Parallel Mode with                |    |

|    | SOA Timer and Current Limit Startup                              |    |

|    | Example 2: Design Procedure of Low Stress Stage                  |    |

|    | Start Mode with Single Capacitor on TMR Pin and                  |    |

|    | dV/dt Startup                                                    | 45 |

|    | Layout Considerations                                            |    |

|    | Reboot on I <sup>2</sup> C Command                               | 49 |

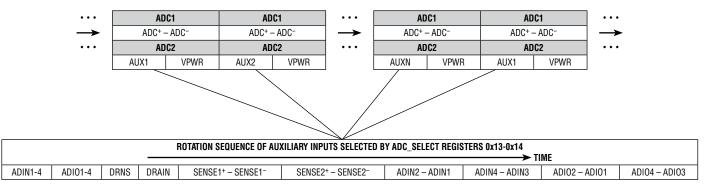

|    | Data Converters                                                  |    |

|    | EEPROM                                                           |    |

|    | Fault Log                                                        |    |

|    | Digital Interface                                                |    |

|    | Bus Compatibility                                                | 55 |

|    | START, REPEATED START and STOP Conditions                        | 56 |

|    | ACK/NACK                                                         |    |

|    | I <sup>2</sup> C Device Addressing                               |    |

|    | Transfer Protocol Types<br>Command Codes and Register Addressing |    |

|    | Write Protocols                                                  |    |

|    | Read Protocols                                                   |    |

|    | Read Page and Write Page Protocols                               |    |

|    | Byte Ordering                                                    |    |

|    | ALERT# and Alert Response Protocol                               |    |

|    | Stuck Bus Reset                                                  |    |

|    | Data Synchronization and Arbitration                             |    |

|    | Single-Wire Broadcast                                            | 60 |

|    | Register Tables                                                  | 62 |

| Ра | ckage Description                                                | 80 |

|    | vision History                                                   |    |

|    | pical Application                                                |    |

| Re | lated Parts                                                      | 82 |

## **ABSOLUTE MAXIMUM RATINGS**

#### (Notes 1 and 2)

Supply Voltage:

| V <sub>IN</sub> –0.3V to 12.5V                                    | l |

|-------------------------------------------------------------------|---|

| INTV <sub>CC</sub> 0.3V to 5.5V                                   |   |

| Input Voltages                                                    |   |

| V <sub>Z</sub> (Note 3)–0.3V to 16V                               | l |

| DRAIN (Note 4)0.3V to 3.2V                                        |   |

| EN# (Note 5)0.3V to 6V                                            |   |

| MODE0.3V to V <sub>IN</sub> + 0.3V                                |   |

| UVL, UVH –0.3V to 16V                                             |   |

| ADC <sup>+</sup> , ADC <sup>-</sup> , ADIN1-4, ADR0, ADR1,        |   |

| DRNS, OV, RTNS, SCL, SDAI, SENSE1 <sup>+</sup> ,                  |   |

| SENSE1 <sup>-</sup> , SENSE2 <sup>+</sup> , SENSE2 <sup>-</sup> , |   |

| VOUTTH, WP–0.3V to INTV <sub>CC</sub> + 0.3V                      | 1 |

| Output Voltages                                                   |   |

| GATE1, GATE2, PGI01-40.3V to V <sub>IN</sub> + 0.3V               | I |

| VREF0.3V to 4.5V                                                  |   |

| ADI01-4, RAMP, TMR0.3V to INTV <sub>CC</sub> + 0.3V               |   |

| ALERT#, SDA00.3V to 5.5V                                          |   |

| Input Currents:                                                   |   |

|                                                                   |   |

| DRAIN                                                             |   |

| EN#5mA                                                            |   |

| Operating Ambient Temperature Range                               |   |

| LTC4284C 0°C to 70°C                                              | , |

| LTC4284I–40°C to 85°C                                             | , |

| LTC4284H40°C to 125°C                                             |   |

| Storage Temperature Range65°C to 150°C                            |   |

|                                                                   |   |

## PIN CONFIGURATION

## **ORDER INFORMATION**

| TUBE            | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|-----------------|-------------------|---------------|---------------------------------|-------------------|

| LTC4284CUHG#PBF | LTC4284CUHG#TRPBF | 4284          | 44-Lead (5mm × 8mm) Plastic QFN | 0°C to 70°C       |

| LTC4284IUHG#PBF | LTC4284IUHG#TRPBF | 4284          | 44-Lead (5mm × 8mm) Plastic QFN | -40°C to 85°C     |

| LTC4284HUHG#PBF | LTC4284HUHG#TRPBF | 4284          | 44-Lead (5mm × 8mm) Plastic QFN | -40°C to 125°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

| SYMBOL                  | PARAMETER                                                                       | CONDITIONS                                                                                             |   | MIN                   | ТҮР                   | MAX                   | UNITS |

|-------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---|-----------------------|-----------------------|-----------------------|-------|

| Power Supply            | /                                                                               | •                                                                                                      | · |                       |                       |                       | ·     |

| V <sub>IN</sub>         | Shunt Regulated Voltage at V <sub>IN</sub>                                      | $I_{IN} + I_{VZ} = 4mA$                                                                                | • | 10.8                  | 11.5                  | 12                    | V     |

| $\Delta V_{IN}$         | Load Regulation at V <sub>IN</sub>                                              | $I_{IN} + I_{VZ} = 4$ mA to 35mA                                                                       | • |                       | 250                   | 500                   | mV    |

| I <sub>IN</sub>         | V <sub>IN</sub> Supply Current                                                  | V <sub>IN</sub> = 10.5V                                                                                | • |                       | 2.5                   | 4                     | mA    |

| V <sub>IN(UVLO)</sub>   | V <sub>IN</sub> Undervoltage Lockout Threshold                                  | V <sub>IN</sub> Rising                                                                                 | • | 7.5                   | 8.1                   | 8.6                   | V     |

| $\Delta V_{IN(UVLO)}$   | V <sub>IN</sub> Undervoltage Lockout Hysteresis                                 |                                                                                                        | • | 0.4                   | 0.5                   | 0.6                   | V     |

| I <sub>VZ</sub>         | V <sub>Z</sub> Input Current                                                    | V <sub>IN</sub> = 10.5V, V <sub>Z</sub> = 15V                                                          | • |                       |                       | 20                    | μA    |

| INTV <sub>CC</sub>      | Internal 5V LDO Voltage                                                         | $I_{LOAD}$ = 1mA to 30mA, $I_{IN}$ + $I_{VZ}$ = 35mA                                                   | • | 4.75                  | 5.05                  | 5.35                  | V     |

| V <sub>CC(UVLO)</sub>   | INTV <sub>CC</sub> Undervoltage Lockout Threshold                               | INTV <sub>CC</sub> Rising                                                                              | • | 3.65                  | 4                     | 4.3                   | V     |

| $\Delta V_{CC(UVLO)}$   | INTV <sub>CC</sub> Undervoltage Lockout Hysteresis                              |                                                                                                        | • | 0.12                  | 0.2                   | 0.3                   | V     |

| Gate Drive              |                                                                                 |                                                                                                        |   |                       |                       |                       |       |

| V <sub>GATE</sub>       | Gate Drive Voltage for GATE1,2                                                  |                                                                                                        | • | V <sub>IN</sub> – 0.3 | VIN                   | V <sub>IN</sub> + 0.3 | V     |

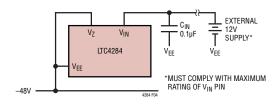

| V <sub>GATE(TH)</sub>   | Gate High Threshold for Asserting Power Good                                    | GATE1,2 Rising                                                                                         | • | V <sub>IN</sub> – 2.1 | V <sub>IN</sub> – 1.8 | V <sub>IN</sub> – 1.5 | V     |

| V <sub>GATE(HYST)</sub> | Gate High Hysteresis                                                            |                                                                                                        | • | 0.3                   | 0.7                   | 1.1                   | V     |

| I <sub>GATE(UP)</sub>   | GATE1,2 Pull-Up Current                                                         | V <sub>GATE</sub> = 4V                                                                                 | • | -40                   | -50                   | -75                   | μA    |

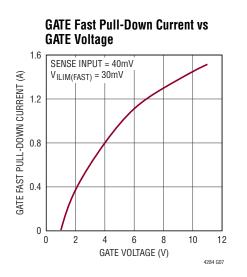

| IGATE(DN)               | GATE1,2 Fast Pull-Down Current                                                  | $\Delta V_{\text{SENSE1,2}} = V_{\text{ILIM}(\text{FAST})} + 10\text{mV}, V_{\text{GATE}} = 7\text{V}$ | • | 0.5                   | 1.2                   | 2                     | A     |

|                         | GATE1,2 Current Limit Pull-Down Current                                         | $\Delta V_{\text{SENSE1,2}} = V_{\text{ILIM}} + 5 \text{mV}, V_{\text{GATE}} = 7 \text{V}$             | • | 12.5                  | 25                    | 50                    | mA    |

|                         | GATE1,2 Turn Off Pull-Down Current                                              | TMR, OV, EN# = High, UVL = Low, V <sub>GATE</sub> =<br>7V                                              | • | 4                     | 9                     | 20                    | mA    |

| On/Off Timin            | ]                                                                               |                                                                                                        |   |                       |                       |                       |       |

| t <sub>PHL(SENSE)</sub> | ΔV <sub>SENSE1,2</sub> High to GATE1,2 Low<br>Propagation Delay                 | ILIM = 0000b, $\Delta V_{SENSE1,2}$ Steps from 0mV to 100mV, $V_{GATE}$ < 3V, GATE1,2 Open             | • |                       | 60                    | 150                   | ns    |

| t <sub>PHL(GATE)</sub>  | GATE1,2 Turn Off Propagation Delay                                              | TMR, OV, EN# = High, UVL = Low, V <sub>GATE</sub> < 3V,<br>GATE1,2 Open                                | • |                       | 0.5                   | 1                     | μs    |

| t <sub>DL(DB)</sub>     | Debounce Delay, Auto-Retry Delay<br>Following Undervoltage or PGI Fault         |                                                                                                        | • | 115                   | 128                   | 141                   | ms    |

| t <sub>DL(PG)</sub>     | Power Good Delay                                                                |                                                                                                        | • | 230                   | 256                   | 282                   | ms    |

| t <sub>DL(PGIWD)</sub>  | Power Good Input Watchdog Timer                                                 |                                                                                                        | • | 461                   | 512                   | 563                   | ms    |

| t <sub>DL(RTRY)</sub>   | Auto-Retry Delay Following Overcurrent,<br>FET Bad or External Fault (Table 11) | COOLING_DL = 000b - 111b                                                                               | • |                       |                       | ±10                   | %     |

| t <sub>DL(RTCRST)</sub> | Auto-Retry Counter Reset Delay                                                  | OC_RETRY, FET_BAD_RETRY = 01b, 10b                                                                     | • | 14.8                  | 16.4                  | 18                    | S     |

| t <sub>DL(FETBAD)</sub> | FET Bad Fault Timer Delay (Table 11)                                            | FTBD_DL = 00b - 11b                                                                                    | • |                       |                       | ±10                   | %     |

| t <sub>DL(RBT)</sub>    | Auto-Reboot Delay (Table 23)                                                    | After RBT_EN Bit is Set Via I <sup>2</sup> C Interface,<br>RBT_DL = 000b – 111b                        | • |                       |                       | ±10                   | %     |

| dV/dt Control           | •                                                                               | ·                                                                                                      |   |                       |                       |                       |       |

| I <sub>RAMP</sub>       | RAMP Output Current                                                             | Startup Only, dV/dt Control Enabled                                                                    |   | -2.25                 | -2.5                  | -2.75                 | μA    |

| IRAMP(DN)               | RAMP Discharge Current                                                          | V <sub>RAMP</sub> = 1.2V                                                                               |   | 1                     | 4                     | 10                    | mA    |

| SYMBOL                   | PARAMETER                                                                     | CONDITIONS                                                                             |                      |     | MIN          | ТҮР        | MAX          | UNITS    |

|--------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------|-----|--------------|------------|--------------|----------|

| Drain Monito             | r                                                                             | 1                                                                                      |                      |     |              |            |              |          |

| V <sub>D,PG(TH)</sub>    | DRAIN Input Threshold for Power Good                                          | DRAIN Falling                                                                          |                      |     | 2            | 2.05       | 2.1          | V        |

| $\Delta V_{D,PG(HYST)}$  | DRAIN Input Hysteresis for Power Good                                         |                                                                                        |                      |     |              | 20         |              | mV       |

| V <sub>D,FET(TH)</sub>   | DRAIN Input Threshold for FET Bad Timer<br>and TMR Pull-Up Current (Table 11) | DRAIN Rising, $V_{DTH} = 00b - 1^{-1}$                                                 | 1b                   | •   |              |            | ±10          | %        |

| $\Delta V_{D,FET(HYST)}$ | DRAIN Input Hysteresis with $V_{D,FET(TH)}$                                   |                                                                                        |                      |     |              | 10         |              | mV       |

| I <sub>DRAIN</sub>       | DRAIN Input Current                                                           | V <sub>DRAIN</sub> = 200mV                                                             |                      |     |              | 0          | ±0.1         | μA       |

|                          |                                                                               | V <sub>DRAIN</sub> = 2 V                                                               |                      |     |              | 0          | ±1           | μA       |

| Current Limit            |                                                                               | 1                                                                                      |                      | -,, |              |            |              |          |

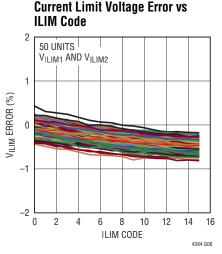

| VILIM                    | Current Limit Voltage DAC Zero-Scale                                          | ILIM = 0000b, C-Grade (Note 6<br>ILIM = 0000b, I-, H-Grade                             | 5)                   | •   | 14.7<br>14.5 | 15<br>15   | 15.3<br>15.5 | mV<br>mV |

|                          | Current Limit Voltage DAC Full-Scale                                          | ILIM = 1111b, C-Grade (Note 6<br>ILIM = 1111b, I-, H-Grade                             | 5)                   | •   | 29.4<br>29   | 30<br>30   | 30.6<br>31   | mV<br>mV |

|                          | Current Limit Voltage DAC INL                                                 |                                                                                        |                      |     |              | 0          | ±50          | μV       |

| $\Delta V_{ILIM}$        | Current Limit Voltage Mismatch between<br>Channel 1 and Channel 2             |                                                                                        |                      | •   |              | 0          | ±350         | μV       |

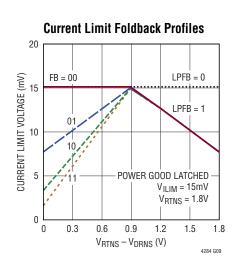

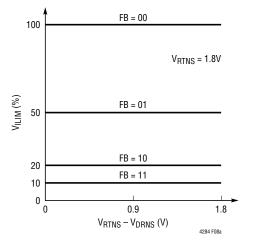

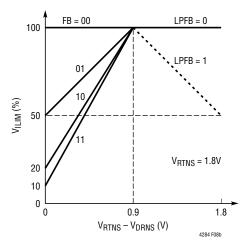

| αstartup                 | Current Limit Foldback Factor at Startup                                      | RTNS = 1.8V, DRNS = 0, 1.8V                                                            | FB = 01b             |     | 45           | 50         | 55           | %        |

|                          |                                                                               |                                                                                        | FB = 10b             |     | 16           | 20         | 24           | %        |

|                          |                                                                               |                                                                                        | FB = 11b             |     | 7            | 10         | 13           | %        |

| $\alpha_{\text{NORMAL}}$ | Current Limit Foldback Factor in Normal Operation                             | RTNS = DRNS = 1.8V                                                                     | FB = 01b             |     | 45           | 50         | 55           | %        |

|                          |                                                                               |                                                                                        | FB = 10b             |     | 15           | 20         | 26           | %        |

|                          |                                                                               |                                                                                        | FB = 11b             |     | 6            | 10         | 16           | %        |

| V <sub>ILIM(FAST)</sub>  | Fast Pull-Down Sense Threshold Voltage                                        | ILIM = 0000b                                                                           | -                    |     | 20           | 30         | 40           | mV       |

|                          |                                                                               | ILIM = 1111b                                                                           |                      | •   | 47           | 60         | 70           | mV       |

| I <sub>SENSE</sub> +     | SENSE1,2 <sup>+</sup> Input Current                                           | SENSE1,2+ = 33mV                                                                       |                      |     |              | 0          | ±1           | μΑ       |

| I <sub>SENSE</sub>       | SENSE1,2 <sup>-</sup> Input Current                                           | $SENSE1,2^{-} = SENSE1,2^{+} = 0$                                                      |                      |     | -4           | -10.5      | -15          | μA       |

| TMR Pin Fund             |                                                                               | [                                                                                      |                      |     |              |            |              |          |

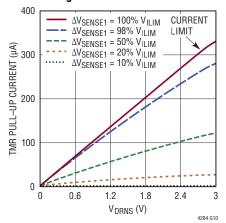

| I <sub>TMR(UP)</sub>     | TMR Pull-Up Current in Current Limit                                          |                                                                                        |                      |     |              |            |              |          |

|                          | Onset                                                                         | DRNS = 0V, TMR = 1V                                                                    |                      | •   | -1.5         | -2         | -2.5         | μΑ       |

|                          | Startup in Foldback                                                           | dV/dt Control Disabled,<br>DRNS = 1.8V, TMR = 1V                                       | FB = 00b             |     | -192         | -202       | -212         | μΑ       |

|                          |                                                                               |                                                                                        | FB = 01b<br>FB = 10b |     | -96          | -102       | -108         | μΑ       |

|                          |                                                                               |                                                                                        | FB = 100<br>FB = 11b |     | -39<br>-20   | -42<br>-22 | 45<br>24     | μΑ       |

|                          | Startup in dV/dt                                                              | dV/dt Control Enabled, DRNS =                                                          |                      |     | -192         | -22        | -24          | μΑ<br>μΑ |

|                          |                                                                               | TMR = 1V                                                                               | = 1.0V,              |     |              |            |              | ļ        |

|                          | Hard Short in Normal Operation                                                | DRNS = 1.8V, TMR = 1V                                                                  |                      | •   | -192         | -202       | -212         | μΑ       |

| I <sub>TMR(DN)</sub>     | TMR Pull-Down Current                                                         | DRAIN < V <sub>D,FET(TH)</sub> or Start into dV/dt<br>Control, THERM_TMR = 0, TMR = 1V |                      | •   | 1.6          | 2          | 2.3          | μA       |

| I <sub>TMR(RST)</sub>    | TMR Reset Current                                                             | EN# = High, TMR = 1V                                                                   |                      | •   | 3            | 5          | 8            | mA       |

| V <sub>TMRH(TH)</sub>    | TMR Fault Threshold                                                           | TMR Rising                                                                             |                      |     | 2.028        | 2.048      | 2.068        | V        |

| V <sub>TMRH(HYST)</sub>  | TMR Fault Hysteresis                                                          |                                                                                        |                      |     |              | 20         |              | mV       |

| V <sub>TMRL(TH)</sub>    | TMR Low Status Threshold                                                      | TMR Falling                                                                            |                      | •   | 80           | 100        | 120          | mV       |

| V <sub>TMRL(HYST)</sub>  | TMR Low Hysteresis                                                            |                                                                                        |                      |     |              | 20         |              | mV       |

| SYMBOL                   | PARAMETER                                                  | CONDITIONS                                        |                   |   | MIN                          | ТҮР                          | MAX                          | UNITS                                        |

|--------------------------|------------------------------------------------------------|---------------------------------------------------|-------------------|---|------------------------------|------------------------------|------------------------------|----------------------------------------------|

| Input Pins               |                                                            | _!                                                |                   | 1 |                              |                              |                              | J                                            |

| V <sub>MODE(TH)</sub>    | MODE Input Thresholds                                      | Threshold 1                                       |                   | • | 0.4                          | 0.7                          | 1                            | V                                            |

|                          |                                                            | Threshold 2 •<br>Threshold 3 •                    |                   | • | INTV <sub>CC</sub><br>- 0.85 | INTV <sub>CC</sub><br>- 0.55 | INTV <sub>CC</sub><br>- 0.25 | V                                            |

|                          |                                                            |                                                   |                   | • | INTV <sub>CC</sub> +<br>0.5  | INTV <sub>CC</sub> +<br>1.5  | INTV <sub>CC</sub> +<br>2.5  | V                                            |

| MODE(IN)                 | Allowable Leakage in Open State                            | Mode 1                                            |                   | • |                              |                              | ±10                          | μA                                           |

| V <sub>UVH(TH)</sub>     | UVH Input Threshold                                        | UVH Rising                                        |                   |   | 2.028                        | 2.048                        | 2.068                        | V                                            |

| V <sub>UVL(TH)</sub>     | UVL Input Threshold                                        | UVL Falling                                       |                   |   | 1.815                        | 1.833                        | 1.851                        | V                                            |

| $\Delta V_{UV(HYST)}$    | Built-In UV Hysteresis                                     | UVH and UVL Tied Together                         |                   |   | 204                          | 215                          | 226                          | mV                                           |

| δV <sub>UV(HYST)</sub>   | UVH, UVL Minimum Hysteresis                                |                                                   |                   |   |                              | 11                           |                              | mV                                           |

| V <sub>UVLR(TH)</sub>    | UVL Reset Threshold                                        | UVL Falling                                       |                   | ٠ | 1                            | 1.024                        | 1.05                         | V                                            |

| $\Delta V_{UVLR(HYST)}$  | UVL Reset Hysteresis                                       |                                                   |                   |   |                              | 21                           |                              | mV                                           |

| V <sub>OV(TH)</sub>      | OV Input Threshold                                         | OV Rising                                         |                   | • | 1.392                        | 1.406                        | 1.42                         | V                                            |

| $\Delta V_{OV(HYST)}$    | OV Input Hysteresis                                        |                                                   |                   | • | 10                           | 24                           | 38                           | mV                                           |

| V <sub>OUTL(TH)</sub>    | V <sub>OUT</sub> Low Threshold                             | RTNS – DRNS Falling, VOUTT                        | H = 0.8V          | • | VOUTTH<br>- 0.06             | VOUTTH                       | VOUTTH +<br>0.06             | V                                            |

| $\Delta V_{OUTL(HYST)}$  | V <sub>OUT</sub> Low Hysteresis                            |                                                   |                   |   |                              | 40                           |                              | mV                                           |

| V <sub>EN#(TH)</sub>     | EN# Input Threshold                                        | EN# Falling                                       |                   | ٠ | 1.248                        | 1.28                         | 1.312                        | V                                            |

| ΔV <sub>EN#(HYST)</sub>  | EN# Input Hysteresis                                       |                                                   |                   |   |                              | 18                           |                              | mV                                           |

| V <sub>WP(TH)</sub>      | WP Input Threshold                                         | WP Rising                                         |                   |   | 1.2                          | 1.65                         | 2.1                          | V                                            |

| ΔV <sub>WP(HYST)</sub>   | WP Input Hysteresis                                        |                                                   |                   |   |                              | 100                          |                              | mV                                           |

| V <sub>INPUT(TH)</sub>   | ADIO1-4, PGIO1-4 Input Threshold                           | ADI01-4, PGI01-4 Rising                           |                   | • | 1.248                        | 1.28                         | 1.312                        | V                                            |

| $\Delta V_{INPUT(HYST)}$ | ADIO1-4, PGIO1-4 Input Hysteresis                          |                                                   |                   |   |                              | 18                           |                              | mV                                           |

| I <sub>INPUT</sub>       | DRNS, EN#, OV, RTNS, UVL, UVH,<br>VOUTTH, WP Input Current | DRNS, EN#, OV, RTNS, UVL, UWP = 3V                | JVH, VOUTTH,      | • |                              | 0                            | ±1                           | μA                                           |

| Output Pins              |                                                            |                                                   |                   |   |                              |                              |                              |                                              |

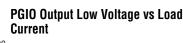

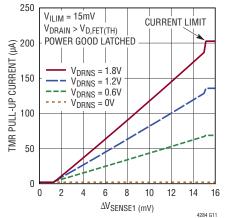

| V <sub>OL</sub>          | ADI01-4, PGI01-4 Output Low Voltage                        | l = 5mA                                           |                   |   |                              | 0.15                         | 0.4                          | V                                            |

| I <sub>LEAK</sub>        | ADIO1-4, PGIO1-4 Leakage Current                           | ADI01-4 = INTV <sub>CC</sub> , PGI01-4 =          | = V <sub>IN</sub> | • |                              | 0                            | ±1                           | μA                                           |

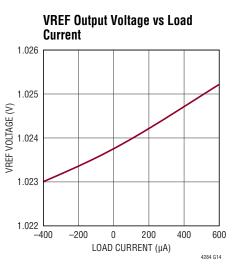

| V <sub>REF</sub>         | VREF Output Voltage                                        | I <sub>VREF</sub> = -200μA, 0, 400μA              |                   | • | 1.01                         | 1.024                        | 1.038                        | V                                            |

| r <sub>REF</sub>         | V <sub>REF</sub> to ADC V <sub>FS</sub> Ratio              | I <sub>VREF</sub> = -200μA, 0, 400μA              |                   |   | 0.495                        | 0.5                          | 0.505                        |                                              |

| ADC                      | -                                                          |                                                   |                   |   |                              |                              |                              | <u>.                                    </u> |

|                          | Resolution (No Missing Codes) (Note 6)                     | RTNS, ADIN1-4, ADIO1-4,                           | ADC = 000b        |   | 8                            |                              | -                            | Bits                                         |

|                          |                                                            | DRNS, DRAIN, (ADC <sup>+</sup> –                  | ADC = 010b        | • | 10                           |                              |                              | Bits                                         |

|                          |                                                            | ADC <sup>-</sup> ), Power                         | ADC = 100b        | • | 12                           |                              |                              | Bits                                         |

|                          |                                                            |                                                   | ADC = 110b        | • | 14                           |                              |                              | Bits                                         |

|                          |                                                            |                                                   | ADC = xx1b        | • | 14                           | 16                           |                              | Bits                                         |

|                          |                                                            | (SENSE1,2 <sup>+</sup> – SENSE1,2 <sup>-</sup> ), | ADC = 000b        | • | 7                            |                              |                              | Bits                                         |

|                          |                                                            | (ADIN2 – ADIN1),                                  | ADC = 010b        | • | 9                            |                              | -                            | Bits                                         |

|                          |                                                            | (ADIN4 – ADIN3),<br>(ADIO2 – ADIO1),              | ADC = 100b        | • | 11                           |                              |                              | Bits                                         |

|                          |                                                            | (ADIO4 – ADIO3)                                   | ADC = 110b        | • | 13                           |                              | -                            | Bits                                         |

|                          |                                                            |                                                   | ADC = xx1b        | • | 13                           | 15                           |                              | Bits                                         |

|                          | 1                                                          |                                                   | 1                 | 1 | -                            | -                            |                              | -                                            |

| SYMBOL                        | PARAMETER                                                      | CONDITIONS                                                                                                       |                                                                     |   | MIN | ТҮР     | MAX          | UNITS             |

|-------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---|-----|---------|--------------|-------------------|

| V <sub>FS</sub>               | Full-Scale Voltage                                             | Single-Ended Inputs                                                                                              |                                                                     |   |     | 2.048   |              | V                 |

|                               |                                                                | Differential Inputs                                                                                              |                                                                     |   |     | 32.768  |              | mV                |

| LSB                           | LSB Step Voltage                                               | RTNS, ADIN1-4, ADIO1-4,                                                                                          | ADC = 000b                                                          |   |     | 8       |              | mV                |

|                               |                                                                | DRNS, DRAIN                                                                                                      | ADC = 010b                                                          |   |     | 2       |              | mV                |

|                               |                                                                |                                                                                                                  | ADC = 100b                                                          |   |     | 0.5     |              | mV                |

|                               |                                                                |                                                                                                                  | ADC = 110b                                                          |   |     | 0.125   |              | mV                |

|                               |                                                                |                                                                                                                  | ADC = xx1b                                                          |   |     | 0.03125 |              | mV                |

|                               |                                                                | ADC <sup>+</sup> – ADC <sup>-</sup>                                                                              | ADC = 000b                                                          |   |     | 128     |              | μV                |

|                               |                                                                |                                                                                                                  | ADC = 010b                                                          |   |     | 32      |              | μV                |

|                               |                                                                |                                                                                                                  | ADC = 100b                                                          |   |     | 8       |              | μV                |

|                               |                                                                |                                                                                                                  | ADC = 110b                                                          |   |     | 2       |              | μV                |

|                               |                                                                |                                                                                                                  | ADC = xx1b                                                          |   |     | 0.5     |              | μV                |

|                               |                                                                | SENSE1,2 <sup>+</sup> – SENSE1,2 <sup>-</sup> ,                                                                  | ADC = 000b                                                          |   |     | 256     |              | μV                |

|                               |                                                                | ADIN2 – ADIN1,<br>ADIN4 – ADIN3,                                                                                 | ADC = 010b                                                          |   |     | 64      |              | μV                |

|                               |                                                                | ADI02 - ADI01,                                                                                                   | ADC = 100b                                                          |   |     | 16      |              | μV                |

|                               |                                                                | ADIO4 – ADIO3                                                                                                    | ADC = 110b                                                          |   |     | 4       |              | μV                |

|                               |                                                                |                                                                                                                  | ADC = xx1b                                                          |   |     | 1       |              | μV                |

| V <sub>OS</sub>               | Offset Error (Note 7)                                          | Single-Ended Inputs                                                                                              | Single-Ended Inputs                                                 |   |     | 0       | ±0.125       | % V <sub>FS</sub> |

|                               |                                                                | Differential Inputs                                                                                              |                                                                     |   |     | 0       | ±0.25        | % V <sub>FS</sub> |

| INL                           | Integral Nonlinearity (Note 7)                                 | ADIN1-4, ADIO1-4, RTNS, DRNS, DRAIN,<br>ADC <sup>+</sup> – ADC <sup>-</sup>                                      |                                                                     |   |     | ±0.01   | ±0.06        | % V <sub>FS</sub> |

|                               |                                                                | SENSE1,2 <sup>+</sup> – SENSE1,2 <sup>-</sup> , ADIN2 – ADIN1,<br>ADIN4 – ADIN3, ADIO2 – ADIO1,<br>ADIO4 – ADIO3 |                                                                     |   |     | ±0.02   | ±0.12        | % V <sub>FS</sub> |

| FSE                           | Full-Scale Error (Note 7)                                      | Single-Ended Inputs, C-Grade (Note 6)<br>Single-Ended Inputs, I-, H-Grade                                        |                                                                     | • |     |         | ±0.5<br>±0.7 | %                 |

|                               |                                                                | Differential Inputs, C-Grade (Note 6)<br>Differential Inputs, I-, H-Grade                                        |                                                                     | • |     |         | ±1<br>±1.2   | %                 |

|                               |                                                                | Power, C-Grade (Note 6)<br>Power, I-, H-Grade                                                                    |                                                                     | • |     |         | ±1<br>±1.2   | %                 |

|                               |                                                                | Energy                                                                                                           |                                                                     |   |     |         | ±5           | %                 |

| f <sub>CONV</sub>             | Refresh Rate in Continuous Mode<br>(Table 12)                  |                                                                                                                  |                                                                     |   |     |         | ±5           | %                 |

| I <sub>ADC</sub> +            | ADC <sup>+</sup> Input Current                                 | ADC <sup>+</sup> = 33mV                                                                                          |                                                                     |   |     | 0       | ±1           | μA                |

| I <sub>ADC</sub> <sup>-</sup> | ADC <sup>+</sup> Input Current                                 | $ADC^{-} = ADC^{+} = 0$                                                                                          |                                                                     |   |     | -3      | -7           | μA                |

| R <sub>ADIN(SE)</sub>         | ADIN1-4, ADIO1-4 Input Impedance,<br>Single-Ended              | V = 3V                                                                                                           |                                                                     |   | 3   |         |              | MΩ                |

| I <sub>ADIN(SE)</sub>         | ADIN1-4, ADIO1-4 Input Current,<br>Single-Ended                | V = 3V                                                                                                           |                                                                     | • |     | 0       | ±1           | μA                |

| I <sub>ADIN(DIFF)</sub>       | ADIN1, ADIN3, ADIO1, ADIO3 Input<br>Current, Differential Mode | ADIN1, ADIN3, ADIO1, ADIO<br>ADIN4, ADIO2, ADIO4 = 0                                                             | 3 = 0, ADIN2,                                                       | • |     | -3      | -7           | μA                |

|                               | ADIN2, ADIN4, ADIO2, ADIO4 Input<br>Current, Differential Mode | ADIN2, ADIN4, ADIO2, ADIO                                                                                        | ADIN2, ADIN4, ADIO2, ADIO4 = 0<br>ADIN2, ADIN4, ADIO2, ADIO4 = 33mV |   |     | 0       | ±1           | μA                |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C, I<sub>IN</sub> + I<sub>VZ</sub> = 4mA with V<sub>IN</sub> Connected to V<sub>Z</sub>. (Note 2)

| SYMBOL                     | PARAMETER                                              | CONDITIONS                        |   | MIN                          | ТҮР                          | MAX                          | UNITS  |

|----------------------------|--------------------------------------------------------|-----------------------------------|---|------------------------------|------------------------------|------------------------------|--------|

| I <sup>2</sup> C Interface | 1                                                      | I                                 |   |                              |                              |                              |        |

| V <sub>ADR(H)</sub>        | ADR0, ADR1 Input High Threshold                        |                                   | • | INTV <sub>CC</sub><br>- 0.85 | INTV <sub>CC</sub><br>- 0.55 | INTV <sub>CC</sub><br>- 0.25 | V      |

| V <sub>ADR(L)</sub>        | ADR0, ADR1 Input Low Threshold                         |                                   |   | 0.4                          | 0.7                          | 1                            | V      |

| I <sub>ADR(IN)</sub>       | Allowable Leakage Current                              |                                   | • |                              |                              | ±10                          | μA     |

| V <sub>ALERT#(OL)</sub>    | ALERT# Output Low Voltage                              | I = 5mA                           | • |                              | 0.15                         | 0.4                          | V      |

| V <sub>SDAO(OL)</sub>      | SDAO Output Low Voltage                                | I = 20mA                          | • |                              | 0.25                         | 0.6                          | V      |

| I <sub>SDAO,ALERT#</sub>   | SDAO, ALERT# Input Current                             | SDAO, ALERT# = INTV <sub>CC</sub> | • |                              | 0                            | ±1                           | μA     |

| V <sub>SDAI,SCL(TH)</sub>  | SDAI, SCL Input Threshold                              |                                   | • | 1.5                          | 1.75                         | 2                            | V      |

| I <sub>SDAI,SCL</sub>      | SDAI, SCL Input Current                                | SDAI, SCL = INTV <sub>CC</sub>    | • |                              | 0                            | ±1                           | μA     |

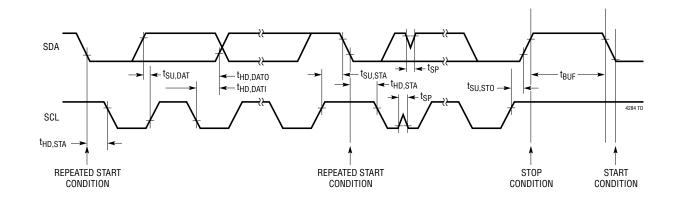

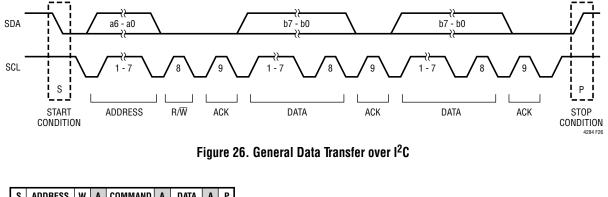

| I <sup>2</sup> C Interface | Timing (Note 7)                                        |                                   |   |                              |                              |                              |        |

| f <sub>SCL(MAX)</sub>      | Maximum SCL Clock Frequency                            |                                   |   | 400                          |                              |                              | kHz    |

| t <sub>LOW</sub>           | Minimum SCL Low Period                                 |                                   |   |                              | 0.65                         | 1.3                          | μs     |

| t <sub>HIGH</sub>          | Minimum SCL High Period                                |                                   |   |                              | 50                           | 600                          | ns     |

| t <sub>BUF(MIN)</sub>      | Minimum Bus Free Time Between Stop/<br>Start Condition |                                   |   |                              | 0.12                         | 1.3                          | μs     |

| t <sub>hd,sta(min)</sub>   | Minimum Hold Time After (Repeated)<br>Start Condition  |                                   |   |                              | 140                          | 600                          | ns     |

| t <sub>su,sta(MIN)</sub>   | Minimum Repeated Start Condition<br>Set-Up Time        |                                   |   |                              | 30                           | 600                          | ns     |

| t <sub>SU,STO(MIN)</sub>   | Minimum Stop Condition Set-Up Time                     |                                   |   |                              | 30                           | 600                          | ns     |

| t <sub>HD,DATI(MIN)</sub>  | Minimum Data Hold Time Input                           |                                   |   |                              | -100                         | 0                            | ns     |

| t <sub>HD,DATO(MIN)</sub>  | Minimum Data Hold Time Output                          |                                   |   | 300                          | 600                          | 900                          | ns     |

| t <sub>SU,DAT(MIN)</sub>   | Minimum Data Set-Up Time Input                         |                                   |   |                              | 30                           | 100                          | ns     |

| t <sub>SP(MAX)</sub>       | Maximum Suppressed Spike Pulse Width                   |                                   |   | 50                           | 110                          | 250                          | ns     |

| t <sub>RST</sub>           | Stuck-Bus Reset Time                                   | SCL or SDAO Held Low              |   | 26                           | 30                           | 34                           | ms     |

| C <sub>X</sub>             | SCL, SDA Input Capacitance                             | SDAI Tied to SDAO                 |   |                              | 5                            | 10                           | pF     |

| Single-Wire E              | Broadcast Timing                                       |                                   |   |                              |                              |                              |        |

| f <sub>BC</sub>            | Broadcast Data Rate (Table 11)                         |                                   | • |                              |                              | ±10                          | %      |

| EEPROM                     | ·                                                      | ·                                 |   |                              |                              |                              |        |

|                            | Endurance                                              | 1 Cycle = 1 Write (Notes 8, 9)    | • | 10,000                       |                              |                              | Cycles |

|                            | Data Retention                                         | (Notes 8, 9)                      | • | 20                           |                              |                              | Years  |

| t <sub>WRITE</sub>         | EEPROM Write Time per Byte                             |                                   | • | 1.2                          | 2.2                          | 3                            | ms     |

|                            |                                                        |                                   |   |                              |                              |                              |        |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: All Currents into device pins are positive and all currents out of device pins are negative. All voltages are referenced to  $\mathsf{V}_{\mathsf{EE}}$  unless otherwise specified.

**Note 3:** When V<sub>7</sub> is connected to V<sub>IN</sub>, an internal shunt regulator limits the voltage to a minimum of 11V. Driving the pins above 11V may damage the part. These pins can be safely biased by a higher voltage using a resistor or current source that limits the current below 50mA.

**Note 4:** An internal clamp limits DRAIN to a minimum of 3.2V. Driving this pin to voltages above the clamp may damage the part. The pin can be safely tied to higher voltages through a resistor that limits the current below 1.5mA.

Note 5: An internal clamp limits EN# to a minimum of 6V. Driving this pin to voltages above the clamp may damage the part. The pin can be safely tied to higher voltages through a resistor that limits the current below 5mA.

Note 6: Guaranteed by design and characterization. Not tested in production.

Note 7: Tested at 12-bit resolution and guaranteed for other resolutions by design and characterization.

Note 8: EEPROM endurance and retention are guaranteed by design, characterization and correlation with statistical process controls.

Note 9: EEPROM endurance and retention will be degraded when  $T_{J} > 85^{\circ}C$ . Rev. A

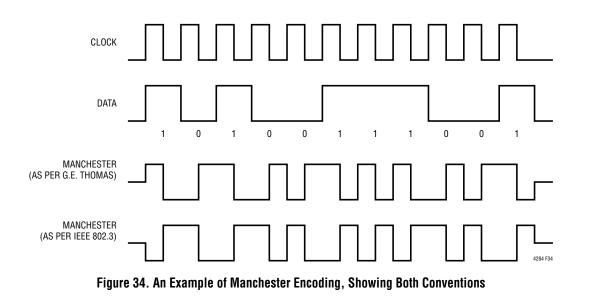

# I<sup>2</sup>C TIMING DIAGRAM

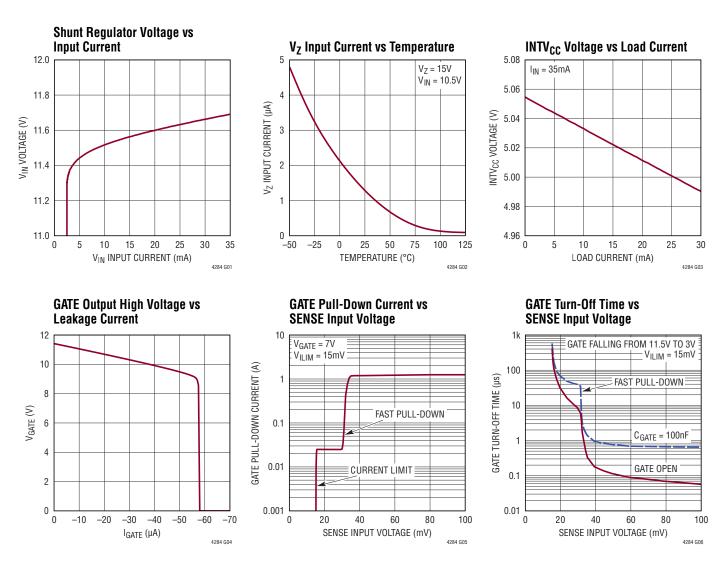

## **TYPICAL PERFORMANCE CHARACTERISTICS**

Rev. A

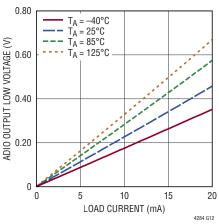

# **TYPICAL PERFORMANCE CHARACTERISTICS**

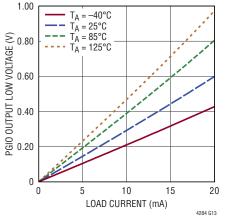

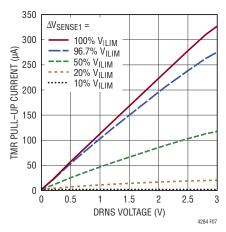

TMR Pull-Up Current vs DRNS Voltage

TMR Pull-Up Current vs SENSE Input Voltage

ADIO Output Low Voltage vs Load Current

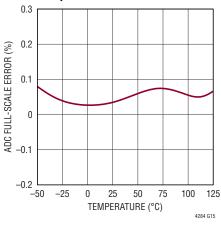

ADC Full-Scale Error vs Temperature

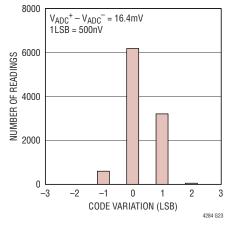

## **TYPICAL PERFORMANCE CHARACTERISTICS**

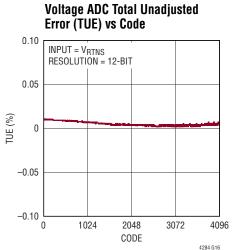

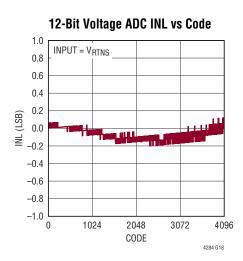

12-Bit Voltage ADC DNL vs Code

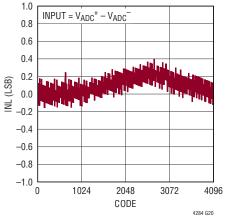

12-Bit Current ADC INL vs Code

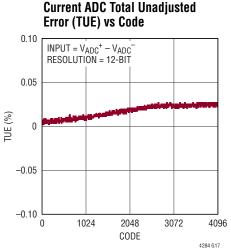

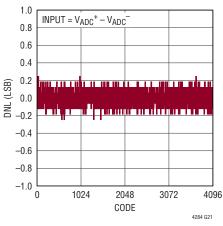

**12-Bit Current ADC DNL vs Code**

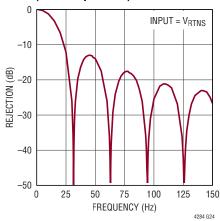

12-Bit ADC Input Signal Attenuation (Low Frequencies)

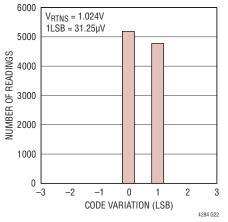

16-Bit Voltage ADC Noise Histogram

#### 16-Bit Current ADC Noise Histogram

Rev. A

# TYPICAL PERFORMANCE CHARACTERISTICS

## PIN FUNCTIONS

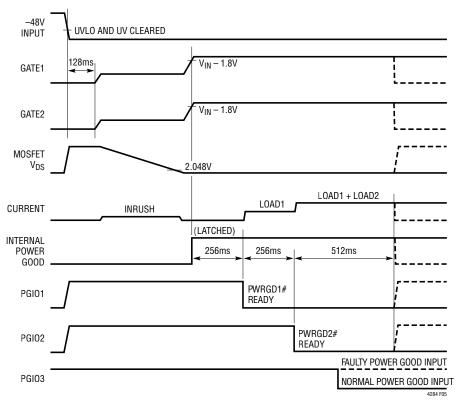

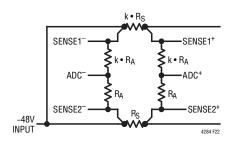

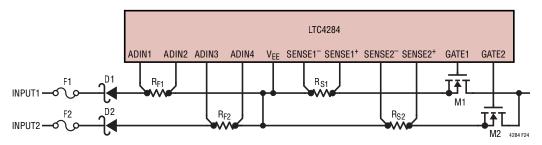

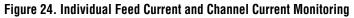

**ADC<sup>+</sup>** (Pin 16): Positive Current Sense Kelvin Input to ADC. Connect to the tap of an external resistive divider between SENSE1<sup>+</sup> and SENSE2<sup>+</sup> to measure the average between those two pins. Connect to SENSE1<sup>+</sup> when using a single sense resistor. Connect to  $V_{EE}$  if unused.

**ADC<sup>-</sup>** (Pin 13): Negative Current Sense Kelvin Input to ADC. Connect to the tap of an external resistive divider between SENSE1<sup>-</sup> and SENSE2<sup>-</sup> to measure the average between those two pins. Connect to SENSE1<sup>-</sup> when using a single sense resistor. Connect to  $V_{EE}$  if unused.

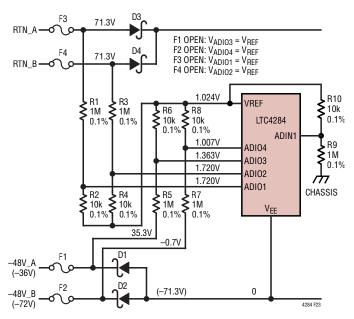

**ADIN1–ADIN4 (Pins 7–10):** ADC Inputs. A single-ended voltage between OV and 2.048V applied to each ADIN is measured by the on-chip ADC. Two differential voltages ADIN2 – ADIN1 and ADIN4 – ADIN3, if enabled, are also measured by the ADC with a full scale of 32.768mV. Connect to  $V_{EE}$  if unused.

**ADIO1–ADIO4 (Pins 25–28):** General Purpose Inputs/ Outputs and ADC Inputs. Configurable to logic inputs and general purpose outputs (open-drain). See Table 13 for details. The single-ended voltages at ADIOs are measured by the ADC with a full scale of 2.048V. The differential voltages ADIO2 – ADIO1 and ADIO4 – ADIO3, if enabled, are also measured by the ADC with a full scale of 32.768mV. Connect to  $V_{\text{EE}}$  if unused.

**ADR0, ADR1 (Pin 38, Pin 39):** Serial Bus Address Inputs. Connecting to  $V_{EE}$ , OPEN or INTV<sub>CC</sub> configures one of nine possible addresses, with one dedicated to the single-wire broadcast mode. Do not bias with an external supply. See Table 2 in Applications Information for address decoding.

**ALERT# (Pin 34):** Fault Alert Output. Open-drain logic output that pulls to  $V_{EE}$  when a fault occurs to alert the host controller. A fault alert is enabled by the FAULT\_ALERT and ADC\_ALERT registers. See Tables 15 and 16 in Applications Information for details. Connect to  $V_{EE}$  if unused.

**DRAIN (Pin 20):** Drain Sense Input. Connect an external 100k resistor between this pin and the drain terminal of the N-channel MOSFET. A DRAIN voltage below 2.048V is one of the conditions to assert power good outputs and turn on GATE2 in the high stress staged start (Mode 3) or low stress staged start mode (Mode 4). When DRAIN voltage is above a voltage configurable between 72mV and 203mV, the FET Bad fault timer is started and the TMR output current is enabled when not in current limit. DRAIN is internally clamped to a minimum of 3.2V.

## PIN FUNCTIONS

**DRNS (Pin 21):** Attenuated Drain Sense Input. Connect to the tap of an external resistive divider between the drain terminal of the N-channel MOSFET and  $V_{EE}$  to monitor the drain voltage. DRNS coupled with RTNS monitors the output voltage for the load, which controls dV/dt inrush current and current limit foldback. DRNS operates from 0 to 2.8V. Connect to  $V_{EE}$  if unused.

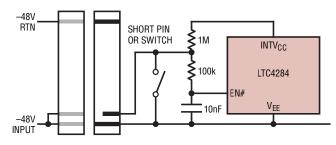

**EN# (Pin 1):** Device Enable Input. Pull low to enable the GATE outputs to turn-on after a startup debounce delay. When pulled high, both GATE1 and GATE2 are turned off. A high-to-low transition clears faults. Transitions are recorded. Requires external pull-up. Debouncing with an external capacitor is recommended when used to monitor board present. Connect to V<sub>EE</sub> if unused.

**Exposed Pad (Pin 45):** Exposed Pad may be left open or connected to device ground (V<sub>EE</sub>).

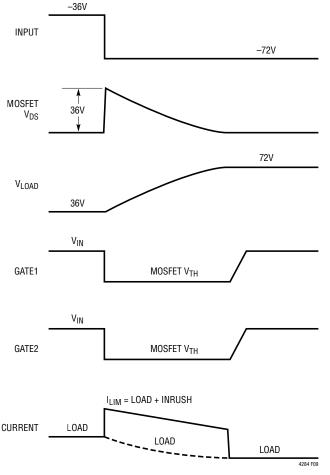

**GATE1, GATE2 (Pin 18, Pin 19):** N-Channel MOSFET Gate Drive Outputs. The GATEs can be configured into single driver, parallel, high stress staged start, and low stress staged start modes. See Table 1 in Application Information for details. The GATEs are pulled high by internal current sources (>40µA) when  $V_{IN}$  and  $INTV_{CC}$  cross the UVLO thresholds, UV and OV conditions are satisfied, no other faults are present and the debounce delay expires. The GATE1 and GATE2 voltages higher than  $V_{IN} - 1.8V$  satisfy one of the conditions to assert power good outputs. Upon a low impedance output short, a 1.2A fast pull-down current is immediately activated.

**INTV<sub>CC</sub> (Pin 42):** 5V Internal Supply Output. The output of the internal linear regulator sources up to 30mA with an UVLO threshold of 4V. The supply powers the data converters, logic control circuitry, I<sup>2</sup>C interface and EEPROM. Bypass with 1 $\mu$ F capacitor to V<sub>EE</sub>. INTV<sub>CC</sub> is not current limited. When driving INTV<sub>CC</sub> with an external supply, V<sub>IN</sub> and V<sub>Z</sub> must be left open or connected to INTV<sub>CC</sub>.

**MODE (Pin 40):** GATE Drive Mode Configuration Input. Its voltage decodes four operation modes of GATE1 and GATE2. Leaving MODE open enables the single driver mode (Mode 1): GATE1 and GATE2 drive a single channel of MOSFETs. Connecting MODE to  $V_{EE}$  enables the

parallel mode (Mode 2): GATE1 and GATE2 drive two parallel channels of MOSFETs that turn on simultaneously to share the load current and turn off simultaneously upon overload. Connecting MODE to V<sub>IN</sub> enables the high stress staged start mode (Mode 3): GATE1 drives a high SOA MOSFET that turns on first for startup and withstands the stress under overload conditions, while GATE2 drives a low R<sub>DS(ON)</sub> MOSFET as a bypass switch that turns on after GATE1 is fully enhanced and turns off whenever overload occurs. Connecting MODE to INTV<sub>CC</sub> enables the low stress staged start mode (Mode 4): the turn-on behavior of GATE1 and GATE2 is the same as Mode 3. but GATE1 drives a low SOA trickle MOSFET and the low R<sub>DS(ON)</sub> bypass MOSFET driven by GATE2 stays on under overload to share the stress. See Applications Information for more details.

**OV (Pin 4):** Overvoltage Detection Input. Connect to an external resistive divider from  $V_{EE}$ . When OV is above its threshold of 1.406V, the GATE outputs pull low to turn off the MOSFETs and an overvoltage fault is recorded. The overvoltage fault does not affect the status of the power good outputs. Connect to  $V_{EE}$  if unused.

**PGI01, PGI02 (Pin 29, Pin 30):** General Purpose Inputs/Outputs. Configurable to sequenced, inverted and non-inverted power good outputs, general purpose logic inputs and open-drain outputs. See Table 12 in Application Information for details. If the PGI02\_ACLB bit in CONTROL\_1 register 0x0A is set, PGI02 is configured as inverted current limit engagement indicator after startup. Connect to V<sub>EE</sub> if unused.

**PGIO3 (Pin 31):** General Purpose Input/Output. Configurable to inverted and non-inverted power good watchdog input (PGI# and PGI), general purpose logic input and open-drain output. See Table 12 in Application Information for details. Connect to V<sub>EE</sub> if unused.

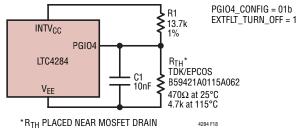

**PGIO4 (Pin 32):** General Purpose Input/Output. Configurable to inverted and non-inverted external fault input (EXT\_FAULTIN# and EXT\_FAULTIN), general purpose logic input and open-drain output. See Table 12 in Application Information for details. Connect to INTV<sub>CC</sub> if unused.

## PIN FUNCTIONS

**RAMP (Pin 23):** Ramp Control. Connect a capacitor between RAMP and  $V_{EE}$  to set inrush current in dV/dt startup mode. During the dV/dt control, RAMP acts as an attenuated output and feeds a fixed 2.5µA current through the RAMP capacitor to set the slew rate of the output voltage. The dV/dt inrush control is disabled after startup when power good signals are asserted. Leave open if unused.

**RTNS (Pin 22):** RTN Sense Input. Connect to the tap of an external resistive divider between RTN and  $V_{EE}$  to monitor the board input voltage. When selected, the RTNS voltage is measured by the ADC and used to calculate the input power. Monitors the output voltage for the load when coupled with DRNS, which controls dV/dt inrush current and current limit foldback. Operates from 0V to 2.8V. Connect to INTV<sub>CC</sub> if unused.

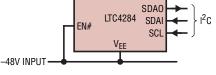

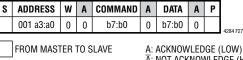

**SCL (Pin 37):** Serial Bus Clock Input. Data at SDAI is shifted in and data at SDAO is shifted out on rising edges of SCL. This is a high impedance input that is generally connected to the output of the incoming isolator driven by the SCL port of the master controller. An external pull-up resistor or current source is required. Pull up to  $INTV_{CC}$  if unused.

**SDAI (Pin 36):** Serial Bus Data Input. This is a high impedance input used for shifting in command bits, data bits, and SDAO acknowledge bits. An external pull-up resistor or current source is required. Normally connected to the output of the incoming isolator that is driven by the SDA port of the master controller. Pull up to INTV<sub>CC</sub> if unused.

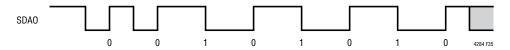

**SDAO (Pin 35):** Serial Bus Data Output. Open-drain output used for sending data back to the master controller or acknowledging a write operation. An external pull-up resistor or current source is required. Normally connected to the input of the outgoing isolator that outputs to the SDA port of the master controller. In the single-wire broadcast mode, SDAO sends out selected data that is Manchester encoded with an internal clock. The broadcast bit rate is configurable between 2Mbit/s and 32kbit/s.

**SENSE1+, SENSE2+ (Pin 15, Pin 17):** Positive Current Sense Kelvin Inputs. Connect to the high side of the current sense resistors. The active current limit amplifiers control GATE1 and GATE2 independently to limit the sense voltages SENSE1+ – SENSE1<sup>-</sup> and SENSE2+ – SENSE2<sup>-</sup> from 15mV to 30mV, configurable in 1mV steps. When enabled, SENSE1+ – SENSE1<sup>-</sup> and SENSE2+ – SENSE2<sup>-</sup> are also measured by the ADC with a full scale of 32.768mV. Connect together when using a single sense resistor. Connect SENSE2+ to V<sub>EE</sub> in the high stress staged start mode (Mode 3). Connect both to V<sub>EE</sub> if unused.

**SENSE1<sup>-</sup>, SENSE2<sup>-</sup> (Pin 14, Pin 12):** Negative Current Sense Kelvin Inputs. Connect to the low side of the current sense resistors.

TMR (Pin 24): Timer Current Output. The current sourced out of TMR is proportional to the power dissipation in the MOSFET driven by GATE1. If an RC network that represents the thermal behavior of the MOSFET is connected between TMR and V<sub>EE</sub>, the voltage at TMR represents the real-time temperature rise of the MOSFET. When the TMR voltage reaches its threshold of 2.048V that corresponds to T<sub>J(MAX)</sub> of the MOSFET, both GATE1 and GATE2 pull low to turn off the MOSFETs and an overcurrent fault is logged. If a single capacitor is connected between TMR and V<sub>FF</sub>, TMR sets the delay for MOSFET turn-off based on the power dissipation in the MOSFET. In this mode the 2µA pull-down current must be enabled to discharge the capacitor when the MOSFET power drops to near zero. When EN# is low, TMR is discharged by a 5mA current. Connect to V<sub>FF</sub> if unused.

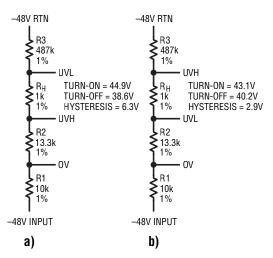

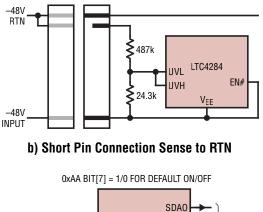

**UVH (Pin 3):** Undervoltage High Level Input. Connect to an external resistive divider from  $V_{EE}$ . If UVH rises above 2.048V and UVL is above 1.833V, the GATE outputs pull high to turn on the MOSFETs. A capacitor of at least 10nF between UVH and  $V_{EE}$  prevents transients and switching noise from affecting the UV threshold. Connect to INTV<sub>CC</sub> if unused.

## PIN FUNCTIONS

**UVL (Pin 2):** Undervoltage Low Level Input. Connect to an external resistive divider from  $V_{EE}$ . If UVL drops below 1.833V and UVH is below 2.048V, the MOSFETs are turned off. Pulling below 1.024V resets faults and allows the MOSFET to turn back on when undervoltage is cleared. Connect to INTV<sub>CC</sub> if unused.

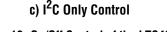

$V_{EE}$  (Pin 11 and Pin 33): Negative Supply Voltage Input and Device Ground. Connect to the negative side of the power supply. The connection between any component and device ground must be made to a dedicated plane that connects directly to V<sub>EE</sub>, not to the main current-carrying trace of -48V on the board.

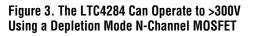

$V_{IN}$  (Pin 43): Positive Supply Input to the Device. Connect to  $V_Z$  directly or through an external buffer transistor driven by  $V_Z$ . The voltage at  $V_{IN}$  is internally regulated at 11.5V. An undervoltage lockout (UVLO) circuit holds the GATE1 and GATE2 outputs low until  $V_{IN}$  is above 8.1V. Bypass with at least 0.1µF capacitor to  $V_{EE}$ . If it is desired to log fault information into EEPROM upon brown-out, bypass  $V_{IN}$  with at least 68µF capacitor to  $V_{EE}$  (See Applications Information for details).

**VOUTTH (Pin 6):** Output Low Threshold Input. Connect to an external reference voltage for output voltage low threshold. RTNS – DRNS below VOUTTH sets the  $V_{OUT}$  low status bit. RTNS – DRNS above VOUTTH satisfies one of the conditions to assert power good outputs. Connect to  $V_{EE}$  if unused.

**VREF (Pin 5):** Reference Voltage Output. Regulated at 1.024V or half of the ADC full-scale. Sources up to  $200\mu$ A and sinks up to  $400\mu$ A. It can drive a capacitive load of up to 10nF. Leave open if unused.