### Overvoltage protection device

Datasheet - production data

#### **Features**

- Input overvoltage protection up to 28 V

- Integrated high voltage N-channel MOSFET switch - low R<sub>DS(on)</sub> of 165 mΩ

- Integrated charge pump

- Maximum continuous current of 2 A

- Thermal shutdown

- Soft-start feature to control the inrush current

- Enable input (EN)

- Fault indication output (FLT)

- IN input ESD protection: ±15 kV air discharge, ±8 kV contact discharge (with 1 µF input capacitor), ±2 kV HBM (standalone device)

- Certain overvoltage options compliant with the China Communications Standard YD/T 1591-2006 (overvoltage protection only)

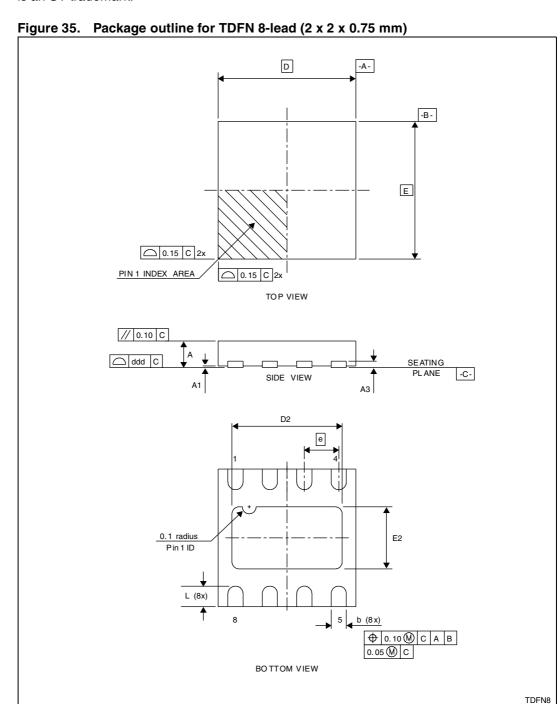

- Small, RoHS compliant 2 x 2 x 0.75 mm TDFN 8-lead package with thermal pad.

### **Applications**

- Smart phones

- Digital cameras

- PDA and palmtop devices

- MP3 players

- Low power handheld devices.

Contents STBP112

## **Contents**

| 1    | Description |                                           |         |  |

|------|-------------|-------------------------------------------|---------|--|

| 2    | Pin (       | description                               | 7       |  |

|      | 2.1         | Input (IN)                                | 7       |  |

|      | 2.2         | Output (OUT)                              | 7       |  |

|      | 2.3         | Fault indication output (FLT)             | 7       |  |

|      | 2.4         | Enable input $(\overline{\overline{EN}})$ | 7       |  |

|      | 2.5         | No connect (NC)                           | 8       |  |

|      | 2.6         | Ground (GND)                              | 8       |  |

| 3    | Ope         | ration                                    | 10      |  |

|      | 3.1         | Power-up                                  | 10      |  |

|      | 3.2         | Normal operation                          | 10      |  |

|      | 3.3         | Undervoltage lockout (UVLO)               | 10      |  |

|      | 3.4         | Overvoltage lockout (OVLO)                | 10      |  |

|      | 3.5         | Thermal shutdown                          | 11      |  |

| 4    | Timi        | ing diagrams                              | 12      |  |

| 5    | Турі        | cal operating characteristics             | 14      |  |

|      | Typic       | cal operating characteristics (STBP112CV) | 15      |  |

| 6    | Max         | imum rating                               | 25      |  |

| 7    | DC a        | and AC parameters                         | 26      |  |

| 8    | Арр         | lication information                      | 28      |  |

|      | 8.1         | Calculating the power dissipation         | 28      |  |

|      | 8.2         | Calculating the junction temperature      | 28      |  |

|      | 8.3         | PCB layout recommendations                | 29      |  |

| 9    | Pack        | kage information                          | 30      |  |

| 10   | Таре        | e and reel information                    | 32      |  |

| 2/38 |             | Doc ID 023357 Rev 3                       | <b></b> |  |

| STBP112 |                             | Contents |

|---------|-----------------------------|----------|

| 11      | Part numbering              | 35       |

| 12      | Package marking information | 36       |

| 13      | Revision history            | 37       |

List of tables STBP112

## List of tables

| Table 1.  | Pin description and signal names                                | 8  |

|-----------|-----------------------------------------------------------------|----|

| Table 2.  | Absolute maximum ratings                                        |    |

| Table 3.  | Thermal data                                                    | 25 |

| Table 4.  | Operating and AC measurement conditions                         | 26 |

| Table 5.  | DC and AC characteristics                                       |    |

| Table 6.  | Package mechanical dimensions for TDFN 8-lead (2 x 2 x 0.75 mm) |    |

| Table 7.  | Carrier tape dimensions                                         |    |

| Table 8.  | Further tape and reel information                               |    |

| Table 9.  | Reel dimensions                                                 |    |

| Table 10. | Ordering information scheme                                     | 35 |

| Table 11. | Marking description                                             |    |

| Table 12  | · ·                                                             |    |

STBP112 List of figures

# **List of figures**

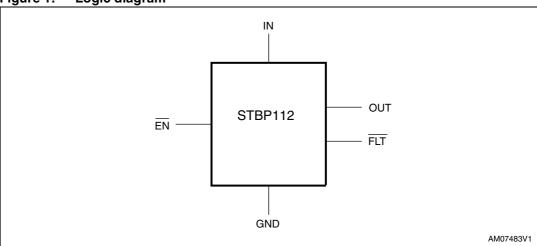

| Figure 1.  | Logic diagram                                                                                                    |

|------------|------------------------------------------------------------------------------------------------------------------|

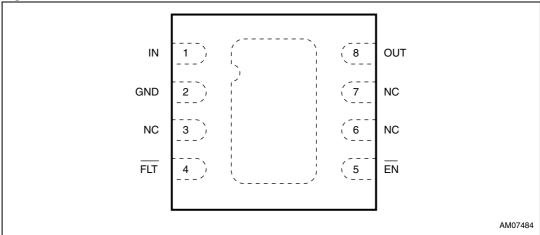

| Figure 2.  | Pinout                                                                                                           |

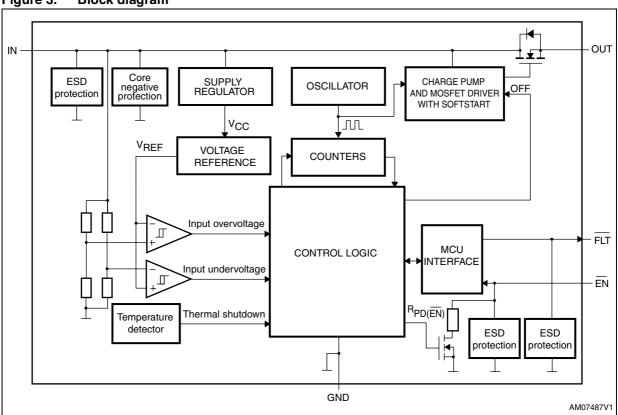

| Figure 3.  | Block diagram                                                                                                    |

| Figure 4.  | Typical application circuit                                                                                      |

| Figure 5.  | Power-up                                                                                                         |

| Figure 6.  | Overvoltage protection                                                                                           |

| Figure 7.  | Disable (EN = high)                                                                                              |

| Figure 8.  | Recovery from OVP                                                                                                |

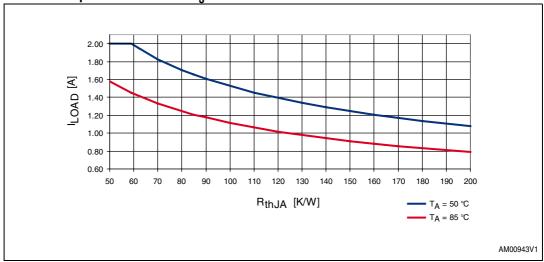

| Figure 9.  | Maximum load current at T <sub>A</sub> = 50 °C and 85 °C for various PCB thermal performance                     |

| J          | and T <sub>J</sub> ≤125 °C                                                                                       |

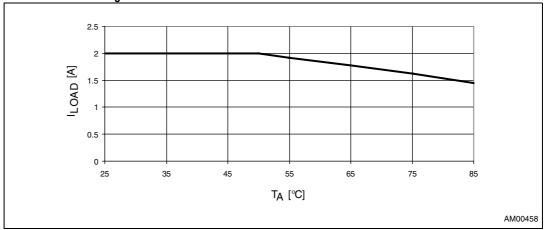

| Figure 10. | Maximum load current vs. ambient temperature for R <sub>thJA</sub> = 59 K/W                                      |

|            | and T <sub>J</sub> ≤125 °C                                                                                       |

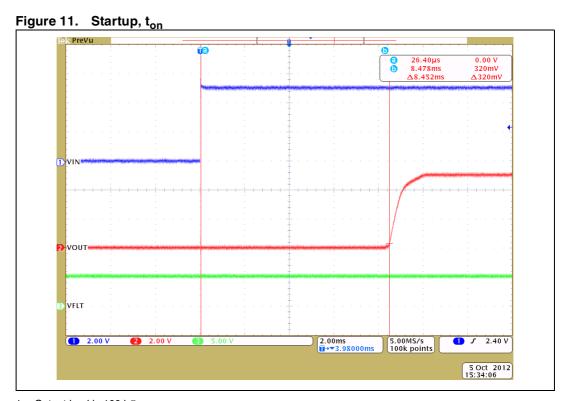

| Figure 11. | Startup, t <sub>on</sub>                                                                                         |

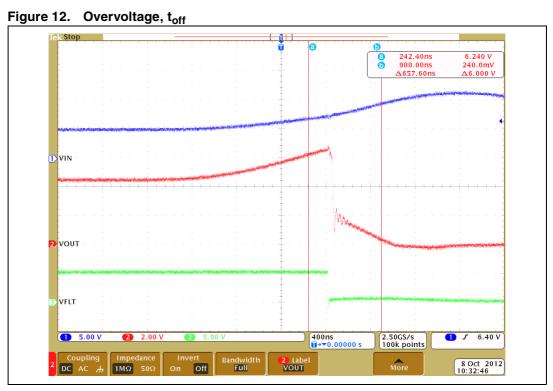

| Figure 12. | Overvoltage, t <sub>off</sub>                                                                                    |

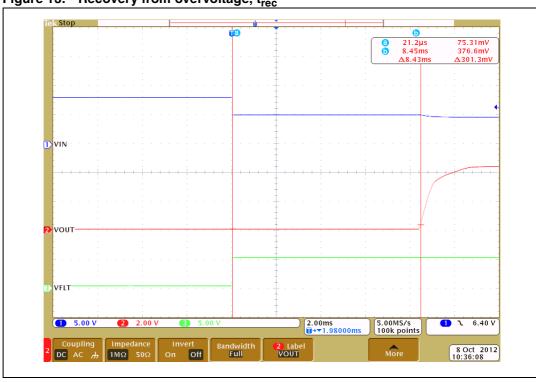

| Figure 13. | Recovery from overvoltage, t <sub>rec</sub>                                                                      |

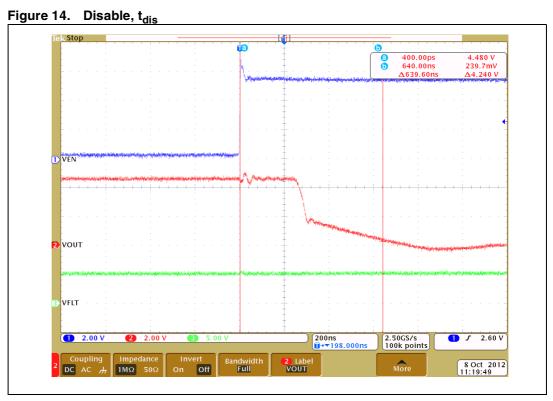

| Figure 14. | Disable, t <sub>dis</sub>                                                                                        |

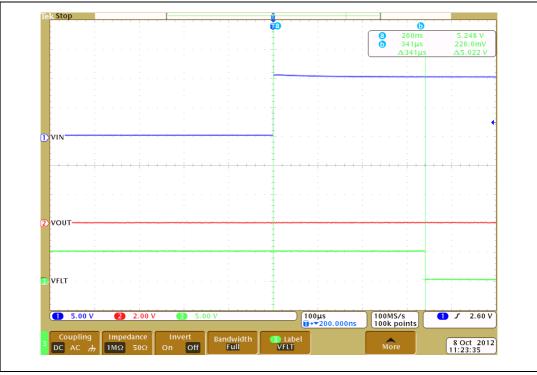

| Figure 15. | Startup to overvoltage                                                                                           |

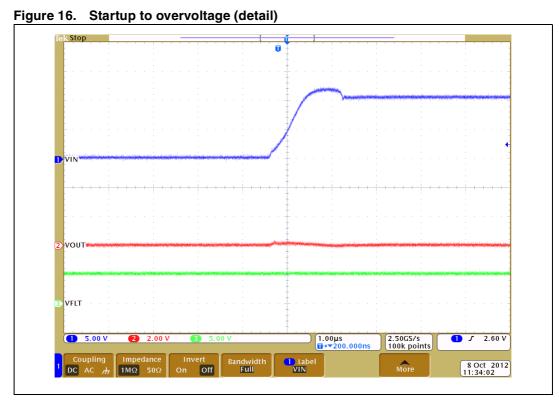

| Figure 16. | Startup to overvoltage (detail)                                                                                  |

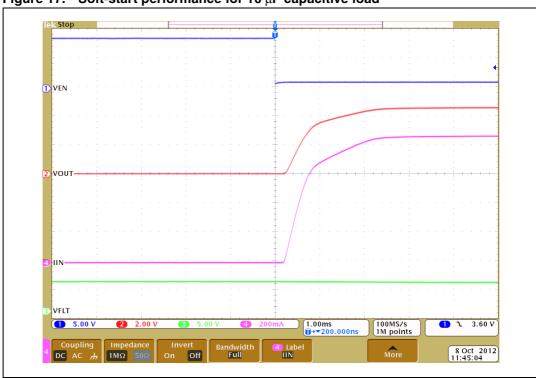

| Figure 17. | Soft-start performance for 10 µF capacitive load                                                                 |

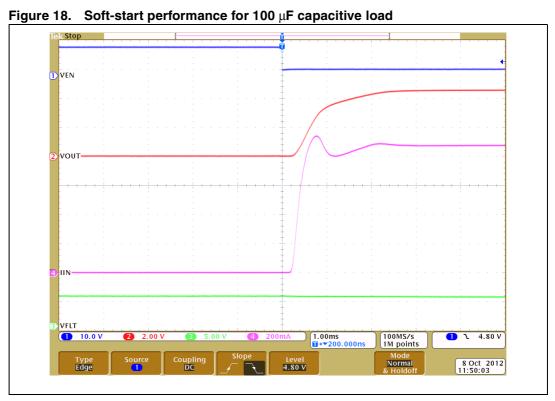

| Figure 18. | Soft-start performance for 100 µF capacitive load                                                                |

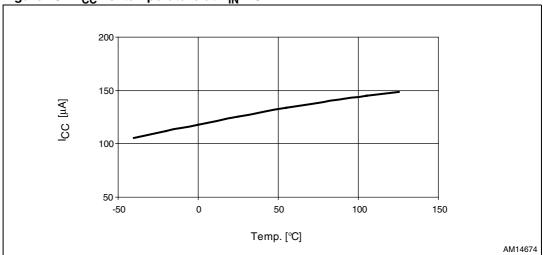

| Figure 19. | I <sub>CC</sub> vs. temperature at V <sub>IN</sub> = 5 V                                                         |

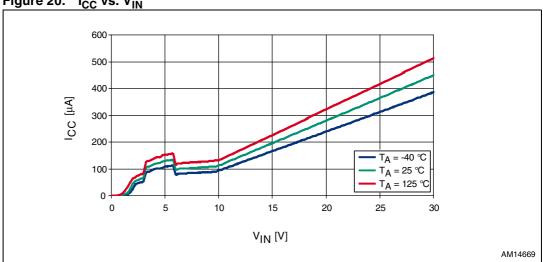

| Figure 20. | I <sub>CC</sub> vs. V <sub>IN</sub>                                                                              |

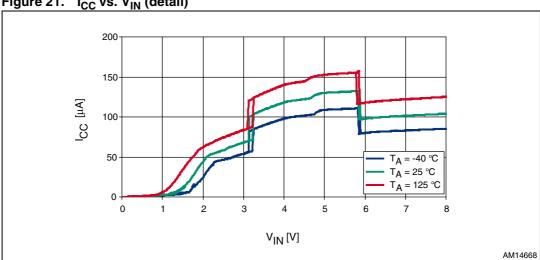

| Figure 21. | I <sub>CC</sub> vs. V <sub>IN</sub> (detail)                                                                     |

| Figure 22. | I <sub>CC(STDBY)</sub> vs. temperature at V <sub>IN</sub> = 5 V                                                  |

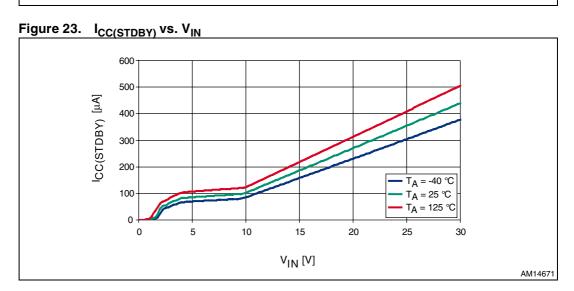

| Figure 23. | I <sub>CC(STDBY)</sub> vs. V <sub>IN</sub>                                                                       |

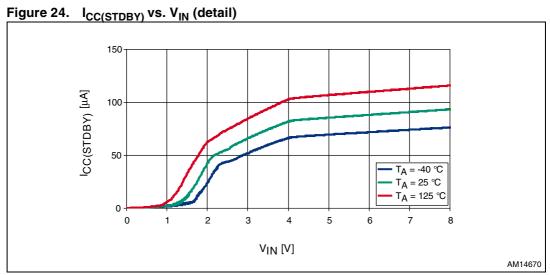

| Figure 24. | I <sub>CC(STDBY)</sub> vs. V <sub>IN</sub> (detail)                                                              |

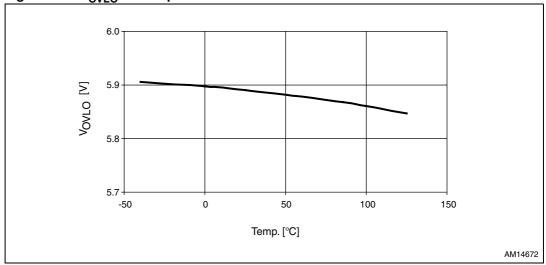

| Figure 25. | V <sub>OVLO</sub> vs. temperature                                                                                |

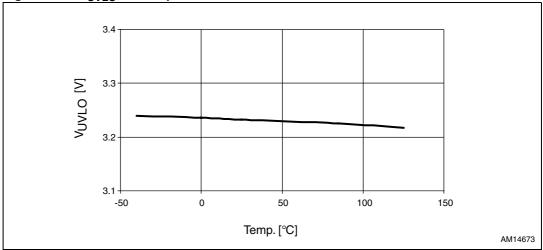

| Figure 26. | V <sub>UVLO</sub> vs. temperature                                                                                |

| Figure 27. | $V_{OL}(\overline{FLT})$ vs. temperature at $I_{SINK}(\overline{FLT}) = 5$ mA, $V_{IN} = 5$ V                    |

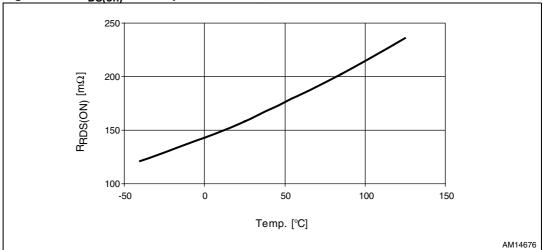

| Figure 28. | R <sub>DS(on)</sub> vs. temperature at 5 V, 1 Å                                                                  |

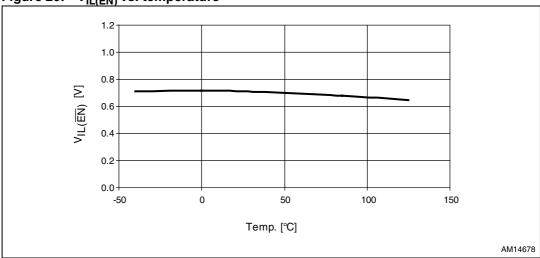

| Figure 29. | $V_{IL}(\overline{EN})$ vs. temperature                                                                          |

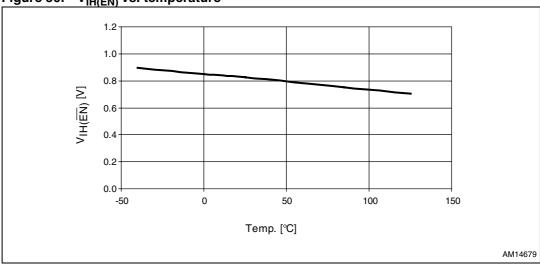

| Figure 30. | $V_{IH}(\overline{EN})$ vs. temperature                                                                          |

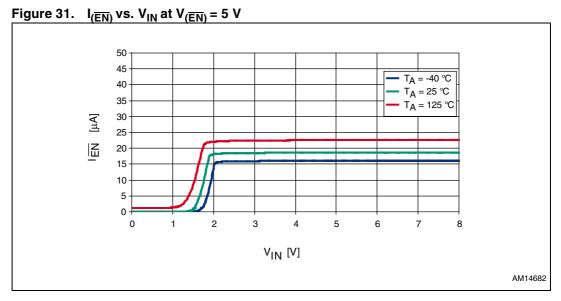

| Figure 31. | $I_{(\overline{EN})}$ vs. $V_{IN}$ at $V_{(\overline{EN})} = 5$ V                                                |

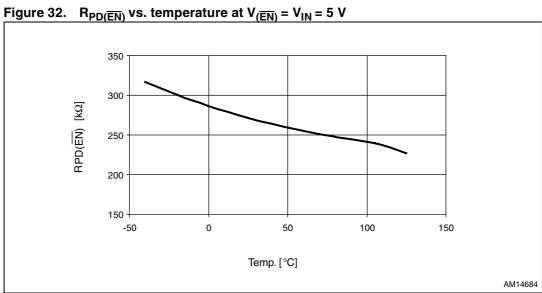

| Figure 32. | $\dot{R}_{PD}(\overline{EN}_{1})$ vs. temperature at $V_{1}(\overline{EN}_{1}) = V_{1}(\overline{EN}_{1}) = 5$ V |

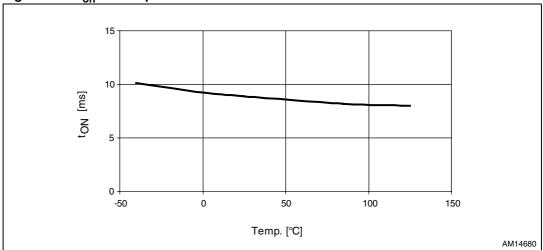

| Figure 33. | t <sub>on</sub> vs. temperature                                                                                  |

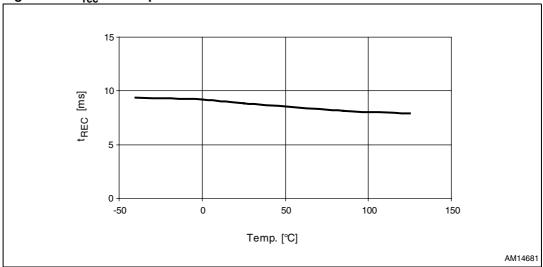

| Figure 34. | t <sub>rec</sub> vs. temperature24                                                                               |

| Figure 35. | Package outline for TDFN 8-lead (2 x 2 x 0.75 mm)                                                                |

| Figure 36. | Tape and reel                                                                                                    |

| Figure 37. | Reel dimensions                                                                                                  |

| Figure 38. | Tape trailer/leader                                                                                              |

| Figure 39. | Pin 1 orientation                                                                                                |

Description STBP112

### 1 Description

The STBP112 device provides overvoltage protection for input voltage up to +28 V. Its low  $R_{DS(on)}$  N-channel MOSFET switch protects the systems connected to the OUT pin against failures of the DC power supplies in accordance with the China MII Communications Standard YD/T 1591-2006.

In the event of an input overvoltage condition, the device immediately disconnects the DC power supply by turning off an internal low  $R_{DS(on)}$  N-channel MOSFET to prevent damage to protected components.

In addition, the device also monitors its own junction temperature and switches off the internal MOSFET if the junction temperature exceeds the specified limit.

The device can be controlled by the microcontroller and can also provide status information about fault conditions.

The STBP112 is offered in a small, RoHS-compliant 8-lead TDFN (2 mm x 2 mm) package.

Figure 2. Pinout

1. Exposed thermal pad may be tied to GND.

STBP112 Pin description

### 2 Pin description

### 2.1 Input (IN)

Input voltage (IN) pin. The IN pin is connected to the DC power supply. An external low ESR ceramic capacitor of minimum value 1  $\mu$ F must be connected between IN and GND. This capacitor is needed for decoupling and also protects the IC against fast voltage spikes and ESD events. This capacitor should be located as close to the IN pin as possible.

### 2.2 Output (OUT)

Output voltage (OUT) pin. The OUT pin is connected to the input through a low  $R_{DS(on)}$  N-channel MOSFET switch.

If no fault is detected and the STBP112 is enabled by the  $\overline{\text{EN}}$  input, this switch is turned on and the output voltage follows the input voltage.

The output is disconnected from the input when the input voltage is under the UVLO threshold or above the OVLO threshold, when the junction temperature is above the thermal shutdown threshold or when the device is disabled by the  $\overline{\text{EN}}$  input.

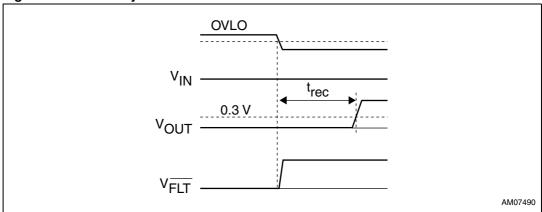

After the input voltage or junction temperature returns to the specified range, there is a recovery delay, t<sub>rec</sub>, and the power output is then connected to the input (see *Figure 8 on page 13*).

The switch turn-on time is intentionally prolonged to limit the inrush current and voltage drop caused, for example, by charging output capacitors (soft-start feature).

### 2.3 Fault indication output (FLT)

The active low, open-drain fault indication output provides information on the STBP112 state to the application controller. The  $\overline{\text{FLT}}$  is asserted (i.e. driven low), if the STBP112 is in the overvoltage condition or thermal shutdown mode is active.

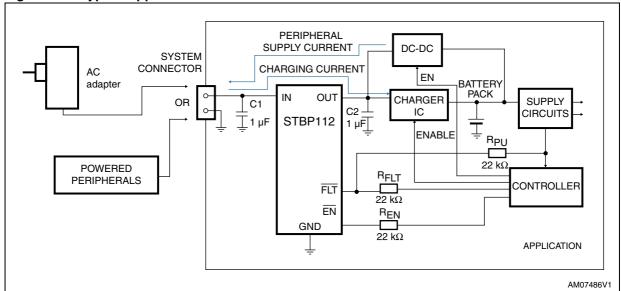

As the  $\overline{\text{FLT}}$  output is of the open-drain type, it may be pulled up by an external resistor R<sub>PU</sub> to the controller supply voltage (see *Figure 4*). If there is no need to use this output, it may be left disconnected. The suitable R<sub>PU</sub> resistor value is in the range of 10 k $\Omega$  to 1 M $\Omega$ .

To improve safety and to prevent damage to application circuits in the event of extreme voltage or current conditions, an optional protective resistor  $R_{FLT}$  can be connected between the  $\overline{FLT}$  output and the controller input (see *Figure 4*). The suitable  $R_{FLT}$  resistor value is in the range of 10 k $\Omega$  to 100 k $\Omega$ .

The FLT output is in Hi-Z (high impedance) state when the device is disabled by EN input or when the input voltage is lower than the UVLO threshold.

### 2.4 Enable input (EN)

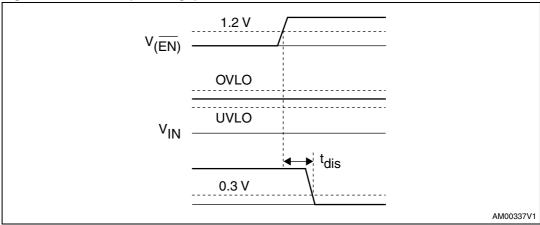

This active low logical input can be used to enable or disable the device. When the  $\overline{EN}$  input is driven high, the STBP112 is in shutdown mode and the power output is disconnected from the input (see *Figure 8 on page 13*). When the  $\overline{EN}$  input is driven low and all operating conditions are within specified limits, the power output is connected to the input.

Pin description STBP112

The  $\overline{\text{EN}}$  input is equipped with an internal pull-down resistor of 250 k $\Omega$  (typical value). If there is no need to use this input, it may be left floating or, preferably, connected to GND.

For  $V_{IN}$  lower than 2.5 V (max.), the pull-down resistor is internally disconnected to lower the  $\overline{EN}$  pin input current in case the external AC adapter is not connected, the application is running from an internal battery and the STBP112 device is disabled.

To improve safety and to prevent damage to application circuits in the event of extreme voltage or current conditions, an optional protective resistor  $R_{EN}$  can be connected between the  $\overline{EN}$  input and the controller output (see *Figure 4*). The protective resistor forms a voltage divider with the internal pull-down resistor, which limits the maximum possible  $R_{EN}$  value with respect to the  $V_{IH(\overline{EN})}$  threshold of  $\overline{EN}$  input and the controller's output voltage for logic high,  $V_{OH}$ . For the worst case, the highest protective resistor value is

$R_{ENmax} = R_{PD(\overline{EN})min} \times (V_{OH} / V_{IH(\overline{EN})} - 1),$

where  $R_{PD(\overline{EN})min}$  is 100 k $\Omega$  and  $V_{IH(\overline{EN})}$  is 1.2 V.

For most cases, an R<sub>EN</sub> value of 10 k $\Omega$  to 100 k $\Omega$  is adequate.

The FLT output is in Hi-Z state when the device is disabled by EN input.

### 2.5 No connect (NC)

Pin 3, 6, and 7 are no connect (NC). They may be left floating or connected to GND.

### 2.6 Ground (GND)

Ground terminal. All voltages are referenced to GND. The exposed thermal pad is internally connected to GND.

| Table 1. | ible 1. I in description and signal names |              |                                          |  |  |  |  |

|----------|-------------------------------------------|--------------|------------------------------------------|--|--|--|--|

| Pin Name |                                           | Туре         | Function                                 |  |  |  |  |

| 1        | IN                                        | Input/supply | Input voltage                            |  |  |  |  |

| 2        | GND                                       | Supply       | Ground                                   |  |  |  |  |

| 3, 6, 7  | NC                                        | -            | Not connected                            |  |  |  |  |

| 4        | FLT                                       | Output       | Fault indication output (open-drain)     |  |  |  |  |

| 5        | ĒN                                        | Input        | Enable input (pull-down resistor to GND) |  |  |  |  |

| 8        | OUT                                       | Output       | Output voltage                           |  |  |  |  |

Table 1. Pin description and signal names

STBP112 Pin description

Figure 3. Block diagram

Figure 4. Typical application circuit

- Optional resistors R<sub>EN</sub> and R<sub>FLT</sub> prevent damage to the controller under extreme voltage or current conditions and are not required. Low ESR ceramic capacitor C1 is necessary to ensure proper function of the STBP112. Capacitor C2 is not necessary for STBP112 but may be required by the charger IC.

- 2. The STBP112 MOSFET switch topology allows the current to flow also in a reverse direction, i.e. from OUT to IN, which can be useful for powering external peripherals from the system connector. If the reverse current (supply current) is undesirable, it may be prevented by connecting an external Schottky diode in series with the OUT pin. The voltage drop between IN and the charger is then increased by the voltage drop across the diode.

Operation STBP112

### 3 Operation

The STBP112 provides overvoltage protection for positive input voltage up to 28 V using a built-in low  $R_{DS(on)}$  N-channel MOSFET switch.

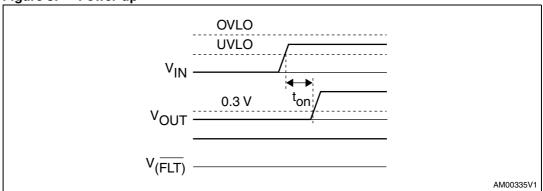

#### 3.1 Power-up

At power-up, with  $\overline{EN}$  = low, the MOSFET switch is turned on after the startup delay,  $t_{on}$ , after the input voltage exceeds the UVLO threshold to ensure the input voltage is stabilized (see *Figure 5*).

### 3.2 Normal operation

The device continuously monitors the input voltage and its own internal temperature so the output voltage is kept within the specified range. The internal MOSFET switch is turned on and the  $\overline{\text{FLT}}$  output is deasserted.

The STBP112 enters normal operation state if the input voltage returns to the interval between  $V_{UVLO}$  and  $V_{OVLO}$  -  $V_{HYS(OVLO)}$  and the junction temperature falls below  $T_{off}$  -  $T_{HYS(off)}$ . The internal MOSFET is turned on after the  $t_{rec}$  delay to ensure that the conditions have stabilized and the  $\overline{FLT}$  output is deasserted.

Note:

The STBP112 MOSFET switch topology allows the current to flow also in a reverse direction, i.e. from OUT to IN, which can be useful for powering external peripherals from the system connector (see the supply current in Figure 4). At first, the current flows through the MOSFET body diode. If the voltage that appears on the IN terminal is above the UVLO threshold, the MOSFET is (after the startup delay) turned on so the voltage drop across STBP112 is significantly reduced.

If the reverse current is undesirable, it may be prevented by connecting an external, properly rated low drop Schottky diode in series with the OUT pin. The voltage drop between IN and charger is increased by the voltage drop across the diode.

### 3.3 Undervoltage lockout (UVLO)

To ensure proper operation under any condition, the STBP112 has an undervoltage lockout (UVLO) threshold. When the input voltage is rising, the output remains disconnected from input until the  $V_{\text{IN}}$  voltage exceeds the  $V_{\text{UVLO}}$  threshold. This circuit is equipped with hysteresis,  $V_{\text{HYS}(\text{UVLO})}$ , to improve noise immunity under transient conditions.

### 3.4 Overvoltage lockout (OVLO)

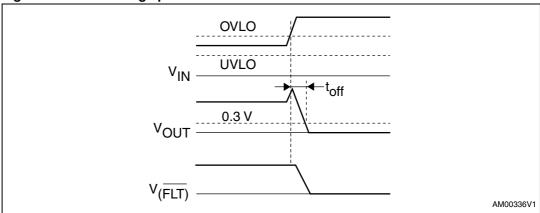

If the input voltage  $V_{IN}$  rises above the threshold level  $V_{OVLO}$ , the MOSFET switch is immediately turned off. At the same time, the fault indication output  $\overline{FLT}$  is activated (i.e. driven low), see *Figure 6*. This device is equipped with hysteresis,  $V_{HYS(OVLO)}$ , to improve noise immunity under transient conditions.

STBP112 Operation

### 3.5 Thermal shutdown

If the STBP112 internal junction temperature exceeds the  $T_{\underline{off}}$  threshold, the internal MOSFET switch is turned off and the fault indication output  $\overline{FLT}$  is driven low.

To improve thermal robustness, this circuit has a 20 °C hysteresis, T<sub>HYS(off)</sub>.

Due to the internal reverse diode, the thermal shutdown is not functional for the reverse current.

Timing diagrams STBP112

## 4 Timing diagrams

Figure 5. Power-up

1.  $\overline{\text{EN}}$  input is low.

Figure 6. Overvoltage protection

1. EN input is low.

Figure 7. Disable ( $\overline{EN} = high$ )

1.  $\overline{\text{FLT}}$  output is in Hi-Z state when  $\overline{\text{EN}}$  driven high.

STBP112 Timing diagrams

Figure 8. Recovery from OVP

1. EN input is low.

## 5 Typical operating characteristics

Figure 9. Maximum load current at T<sub>A</sub> = 50 °C and 85 °C for various PCB thermal performance and T<sub>J</sub>  $\leq$  125 °C

Figure 10. Maximum load current vs. ambient temperature for  $R_{thJA}$  = 59 K/W and  $T_{J} \leq$  125  $^{\circ}C$

14/38 Doc ID 023357 Rev 3

## Typical operating characteristics (STBP112CV)

1. Output load is 100  $k\Omega.$

1. Output load is 5  $\Omega$ .

Figure 13. Recovery from overvoltage,  $t_{rec}$

1. Output load is 5  $\Omega$ .

1. Output load is 5  $\Omega$ .

Figure 15. Startup to overvoltage

1. Output load is 5  $\Omega$ .

1. Output load is 5  $\Omega$ . Almost no glitch on the output.

Figure 17. Soft-start performance for 10  $\mu\text{F}$  capacitive load

1. Output load is 10  $\mu\text{F}$  in parallel with 5  $\Omega.$

1. Output load is 100  $\mu F$  in parallel with 5  $\Omega.$

Figure 20.  $I_{CC}$  vs.  $V_{IN}$

Figure 21.  $I_{CC}$  vs.  $V_{IN}$  (detail)

AM14675

ICC(STDBY) [µA] 80 60 40 100 150 Temp. [°C]

Figure 25.  $V_{OVLO}$  vs. temperature

Figure 26. V<sub>UVLO</sub> vs. temperature

Figure 27. V<sub>OL(FLT)</sub> vs. temperature at I<sub>SINK(FLT)</sub> = 5 mA, V<sub>IN</sub> = 5 V

AM14677

Figure 28. R<sub>DS(on)</sub> vs. temperature at 5 V, 1 A

Figure 29.  $V_{IL(\overline{EN})}$  vs. temperature

Figure 30.  $V_{IH(\overline{EN})}$  vs. temperature

Figure 33.  $t_{on}$  vs. temperature

Figure 34. t<sub>rec</sub> vs. temperature

STBP112 Maximum rating

### 6 Maximum rating

Stressing the device above the rating listed in *Table 2* may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in *Section 3 on page 10* of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics<sup>TM</sup> SURE program and other relevant documentation.

Table 2. Absolute maximum ratings

| Symbol                          | Paramet                                      | er                                           | Value      | Unit |

|---------------------------------|----------------------------------------------|----------------------------------------------|------------|------|

| T <sub>STG</sub>                | Storage temperature (V <sub>IN</sub> off)    |                                              | -55 to 150 | °C   |

| T <sub>SLD</sub> <sup>(1)</sup> | Lead solder temperature for 10 sec           | onds                                         | 260        | °C   |

| TJ                              | Operating junction temperature ran           | ge (internally limited to T <sub>off</sub> ) | -40 to 150 | °C   |

| V <sub>IN</sub>                 | IN pin input voltage                         |                                              | -0.3 to 30 | V    |

| V <sub>OUT</sub>                | OUT pin input/output voltage                 | -0.3 to 12                                   | V          |      |

| V <sub>IO</sub>                 | Input/output voltage (other pins)            | -0.3 to 7                                    | V          |      |

| _                               | Load ourrent (IN to OLIT)                    | T <sub>A</sub> ≤ 50 °C                       | 2000       | mA   |

| I <sub>LOAD</sub>               | Load current (IN to OUT)                     | T <sub>A</sub> = 85 °C                       | 1500       | mA   |

| I <sub>REVERSE</sub>            | Reverse diode current (OUT to IN)            |                                              | 500        | mA   |

| I <sub>SINK(FLT)</sub>          | FLT pin sink current                         |                                              | 15         | mA   |

|                                 | ESD withstand voltage (IEC 61000-            | ±15 (air),<br>±8 (contact)                   | kV         |      |

| V <sub>ESD</sub>                | Human body model (HBM), model :              | 2000                                         | V          |      |

|                                 | Machine model (MM), model = B <sup>(4)</sup> |                                              | 200        | V    |

- 1. Reflow at peak temperature of 260 °C. The time above 255 °C must not exceed 30 seconds.

- 2. System-level value (see typical application circuit, C1  $\geq$  1  $\mu F$  low ESR ceramic capacitor).

- Human body model, 100 pF discharged through a 1.5 kΩ resistor according to the JESD22/A114 specification.

- 4. Machine model, 200 pF discharged through all pins according to the JESD22/A115 specification.

Table 3. Thermal data

| Symbol            | Parameter                                | Value             | Unit |

|-------------------|------------------------------------------|-------------------|------|

| R <sub>thJA</sub> | Thermal resistance (junction-to-ambient) | 59 <sup>(1)</sup> | °C/W |

| R <sub>thJC</sub> | Thermal resistance (junction-to-case)    | 5.9               | °C/W |

The package was mounted on a 4-layer JEDEC test board with 2 thermal vias connecting from the thermal land to the first buried plane. The 4-layer PCB (2S2P) was constructed based on JESD 51-7 specifications and vias based on JESD 51-5.

### 7 DC and AC parameters

This section summarizes the operating measurement conditions, and the DC and AC characteristics of the device. The parameters in *Table 5* are derived from tests performed under the measurement conditions summarized in *Table 4*. Designers should check that the operating conditions in their circuit match the operating conditions when relying on the quoted parameters.

Table 4. Operating and AC measurement conditions

| Parameter                                        | Value      | Unit |

|--------------------------------------------------|------------|------|

| Input voltage (V <sub>IN</sub> )                 | 5          | V    |

| Ambient operating temperature (T <sub>A</sub> )  | -40 to 85  | °C   |

| Junction operating temperature (T <sub>J</sub> ) | -40 to 125 | °C   |

| Logical input rise and fall times                | 5          | ns   |

Table 5. DC and AC characteristics

| Symbol                 | Description                                                   | Test condition <sup>(1)</sup>                                                       | Min.              | Тур.               | Max.              | Unit |  |

|------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------|--------------------|-------------------|------|--|

| V <sub>IN</sub>        | Input voltage range                                           |                                                                                     | $V_{UVLO}$        |                    | 28                | ٧    |  |

| V <sub>UVLO</sub>      | Input undervoltage lockout threshold (V <sub>IN</sub> rising) | Option T<br>Option U<br>Option V                                                    | 2.5<br>2.8<br>3.1 | 2.7<br>3.0<br>3.25 | 2.9<br>3.2<br>3.4 | V    |  |

| V <sub>HYS(UVLO)</sub> | Undervoltage lockout<br>hysteresis <sup>(2)</sup>             |                                                                                     |                   | 100                |                   | mV   |  |

|                        |                                                               | V <sub>IN</sub> raises OVLO threshold, option A                                     | 5.25              | 5.375              | 5.50              |      |  |

|                        |                                                               | V <sub>IN</sub> raises OVLO threshold, option B                                     | 5.30              | 5.50               | 5.70              | V    |  |

|                        | Overvoltage lockout threshold                                 | V <sub>IN</sub> raises OVLO threshold, option C                                     | 5.71              | 5.90               | 6.10              |      |  |

| V <sub>OVLO</sub>      |                                                               | V <sub>IN</sub> raises OVLO threshold, option D                                     | 5.70              | 6.02               | 6.40              |      |  |

|                        |                                                               | V <sub>IN</sub> raises OVLO threshold, option E                                     | 6.20              | 6.40               | 6.60              |      |  |

|                        |                                                               | V <sub>IN</sub> raises OVLO threshold, option F                                     | 6.60              | 6.80               | 7.00              | -    |  |

|                        |                                                               | V <sub>IN</sub> raises OVLO threshold, option G                                     | 7.00              | 7.20               | 7.40              |      |  |

| V <sub>HYS(OVLO)</sub> | Input overvoltage hysteresis                                  |                                                                                     | 30                | 60                 | 90                | mV   |  |

| R <sub>DS(on)</sub>    | IN to OUT resistance                                          | $V_{(\overline{EN})} = 0 \text{ V}, V_{IN} = 5 \text{ V}, I_{LOAD} = 0.5 \text{ A}$ |                   | 165                | 280               | mΩ   |  |

| Icc                    | Operating current                                             | $V_{(\overline{EN})} = 0 \text{ V}, I_{LOAD} = 0 \text{ A}$                         |                   | 140                | 210               |      |  |

| I <sub>CC(STDBY)</sub> | Standby current                                               | $V_{(\overline{EN})} = 5 \text{ V}, I_{LOAD} = 0 \text{ A}$                         |                   | 80                 | 120               | μΑ   |  |

| V <sub>OL(FLT)</sub>   | FLT output low level voltage                                  | $V_{IN} > V_{OVLO}, I_{SINK(\overline{FLT})} = 5 \text{ mA}$                        |                   | 350                | 800               | mV   |  |

| I <sub>L(FLT)</sub>    | FLT output leakage current                                    | $V_{\overline{FLT}} = 5 V$                                                          |                   | 0.1                | 2                 | μΑ   |  |

| V <sub>IL(ĒN)</sub>    | EN low level input voltage                                    |                                                                                     |                   |                    | 0.4               | ٧    |  |

Table 5. DC and AC characteristics (continued)

| Symbol                          | Description                                                           | Test condition <sup>(1)</sup>                                                                                                                                                                              | Min. | Тур. | Max. | Unit |

|---------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>IH(EN)</sub>             | EN high level input voltage                                           |                                                                                                                                                                                                            | 1.2  |      |      | V    |

| R <sub>PD(EN)</sub>             | EN internal pull-down resistor <sup>(3)</sup>                         | $V_{IN} > 2.5 \text{ V}, V_{(\overline{EN})} = 5 \text{ V}$                                                                                                                                                | 100  | 250  | 400  | kΩ   |

|                                 | Timing parameters                                                     |                                                                                                                                                                                                            |      |      |      |      |

| t <sub>on</sub>                 | Startup delay <sup>(4)</sup>                                          | Time measured from $V_{IN} > V_{UVLO}$ to $V_{OUT} = 0.3 \text{ V}$ (no load on the output).                                                                                                               |      | 8    |      | ms   |

| t <sub>off</sub> <sup>(5)</sup> | Output turn-off time                                                  | Time measured from V <sub>IN</sub> > V <sub>OVLO</sub> to V <sub>OUT</sub> $\leq$ 0.3 V. V <sub>IN</sub> increasing from 5.0 V to 8.0 V at 3.0 V/µs, R <sub>LOAD</sub> = 5 $\Omega$ C <sub>LOAD</sub> = 0. |      |      | 1    | μs   |

| t <sub>dis</sub> (5)            | Disable time                                                          | Time measured from $V_{(\overline{EN})} \ge 1.2 \text{ V to}$ $V_{OUT} < 0.3 \text{ V}, R_{LOAD} = 5 \Omega, C_{LOAD} = 0.$                                                                                |      | 1    | 5    |      |

| t <sub>rec</sub>                | Recovery delay from UVLO,<br>OVLO, or thermal shutdown <sup>(4)</sup> | Time measured to V <sub>OUT</sub> = 0.3 V (no load on the output)                                                                                                                                          |      | 8    |      | ms   |

|                                 | Thermal shutdown                                                      |                                                                                                                                                                                                            |      |      |      |      |

| T <sub>off</sub>                | Thermal shutdown threshold temperature                                |                                                                                                                                                                                                            |      | 140  | 150  | °C   |

| T <sub>HYS(off)</sub>           | Thermal shutdown hysteresis                                           |                                                                                                                                                                                                            |      | 20   |      | °C   |

<sup>1.</sup> Test conditions described in *Table 4* (except where noted).

<sup>2.</sup> Hysteresis of 60 mV typ. available upon request.

<sup>3.</sup> Version without pull-down resistor or with permanently connected pull-down resistor available upon request.

<sup>4.</sup> Delays of 16, 32, and 64 ms available upon request.

<sup>5.</sup> Guaranteed by design. Not tested in production.

### 8 Application information

### 8.1 Calculating the power dissipation

The worst case power dissipation of the STBP112 internal power MOSFET can be calculated using the following formula:

#### **Equation 1**

$$P_D = I_{LOAD}^2 \times R_{DS(on)(max)}$$

where  $I_{LOAD}$  is the load current and  $R_{DS(on)(max)}$  is the maximum value of MOSFET resistance.

#### **Example 1**

$$V_{IN} = 5 \text{ V}, R_{LOAD} = 5 \Omega R_{DS(on)(max)} = 280 \text{ m}\Omega$$

$$I_{LOAD} = V_{IN} / (R_{DS(on)(max)} + R_{LOAD}) = 5 / (5 + 0.280) = 0.95 \text{ A}$$

$$P_D = 0.95^2 \times 0.28 = 0.25 \text{ W}$$

The power dissipation of the reverse diode in powering accessories mode can be estimated as  $P_D = (V_{OUT} - V_{IN}) \times I_{REVERSE} \approx 0.7 \times I_{REVERSE}$ .

### 8.2 Calculating the junction temperature

The maximum junction temperature for given power dissipation, ambient temperature, and thermal resistance junction-to-ambient can be calculated as:

#### **Equation 2**

$$T_J = T_A + 1.15 \text{ x P}_D \text{ x R}_{thJA} = T_A + 1.15 \text{ x I}_{LOAD}^2 \text{ x R}_{DS(on)(max)} \text{ x R}_{thJA}$$

where  $T_J$  is junction temperature,  $T_A$  is given ambient temperature, 1.15 is a derating factor, and  $R_{thJA}$  is a junction-to-ambient thermal resistance, depending on PCB design. The junction temperature may not exceed 125 °C (see *Table 4*) to stay within the specified range.

Maximum allowed MOSFET current for ambient temperature  $T_A$  = 85 °C and various  $R_{thJA}$  values are listed in *Figure 9 on page 14*.

#### Example 2

For conditions listed in the previous example, with a well designed PCB (ensuring  $R_{thJA}$  = 59 °C/W) and  $T_A$  = 85 °C, the maximum junction temperature is:

#### **Equation 3**

$$T_{.1} = 85 + 1.15 \times 0.25 \times 59 = 102 \,^{\circ}C,$$

which is a safe value (below 125 °C).

### 8.3 PCB layout recommendations

- Input capacitor C1 should be located as close as possible to the STBP112 device.

It should be a low-ESR ceramic capacitor. Also the protective resistors R<sub>FLT</sub> and R<sub>EN</sub> (if used) should be located close to the STBP112 (see *Figure 4 on page 9*).

- For good thermal performance, it is preferred to couple the STBP112 exposed thermal pads with the PCB ground plane. In most designs, this requires thermal vias between the copper pads on the PCB and the ground plane.

Package information STBP112

## 9 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: <a href="www.st.com">www.st.com</a>. ECOPACK is an ST trademark.

Table 6. Package mechanical dimensions for TDFN 8-lead (2 x 2 x 0.75 mm)<sup>(1)</sup>

|                    |      |      | Dimer | nsions |       | ,     |

|--------------------|------|------|-------|--------|-------|-------|

| Symbol             | mm   |      |       |        |       |       |

|                    | Тур. | Min. | Max.  | Тур.   | Min.  | Max.  |

| Α                  | 0.75 | 0.70 | 0.80  | 0.030  | 0.028 | 0.031 |

| A1                 | 0.02 | 0.00 | 0.05  | 0.001  | 0.000 | 0.002 |

| A3<br>REF          | 0.20 | _    | _     | 0.008  | _     | _     |

| b                  | 0.25 | 0.20 | 0.30  | 0.010  | 0.008 | 0.012 |

| D<br>BSC           | 2.00 |      | _     | 0.079  | _     |       |

| D2                 | 1.60 | 1.45 | 1.70  | 0.063  | 0.057 | 1.067 |

| E<br>BSC           | 2.00 | _    | _     | 0.079  | _     | _     |

| E2                 | 0.90 | 0.75 | 1.00  | 0.035  | 0.030 | 0.039 |

| е                  | 0.50 | _    | _     | 0.020  | _     | _     |

| L                  | 0.30 | 0.25 | 0.35  | 0.012  | 0.010 | 0.014 |

| ddd <sup>(2)</sup> | _    | _    | 0.08  | _      | _     | 0.003 |

| N <sup>(3)</sup>   |      | 8    |       |        | 8     |       |

<sup>1.</sup> Controlling dimension: millimeters.

<sup>2.</sup> Lead coplanarity should not exceed 0.08 mm.

<sup>3.</sup> N is the total number of terminals.

# 10 Tape and reel information

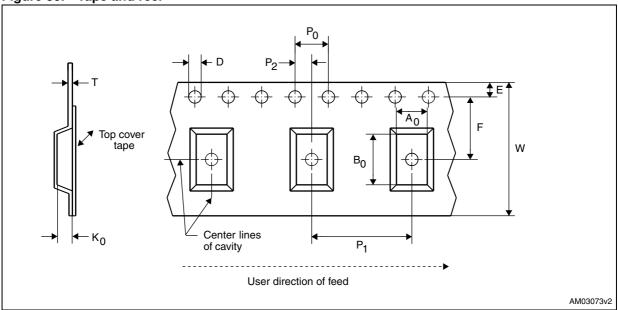

Figure 36. Tape and reel

Table 7. Carrier tape dimensions

| Tape size | W                  | D                 | E          | P0          | P2          | F               |

|-----------|--------------------|-------------------|------------|-------------|-------------|-----------------|

| 8         | 8.00 +0.30 / -0.10 | 1.50 +0.10 / -0.0 | 1.75 ± 0.1 | 4.00 ± 0.10 | 2.00 ± 0.10 | $3.50 \pm 0.05$ |

Table 8. Further tape and reel information

| Package code         | w | Α0          | В0              | K0          | P1          | Т                | Bulk<br>qty. | Reel<br>diameter |

|----------------------|---|-------------|-----------------|-------------|-------------|------------------|--------------|------------------|

| 2 x 2 mm TDFN 8-lead | 8 | 2.30 ± 0.05 | $2.30 \pm 0.05$ | 1.00 ± 0.05 | 4.00 ± 0.10 | $0.250 \pm 0.05$ | 3000         | 7                |

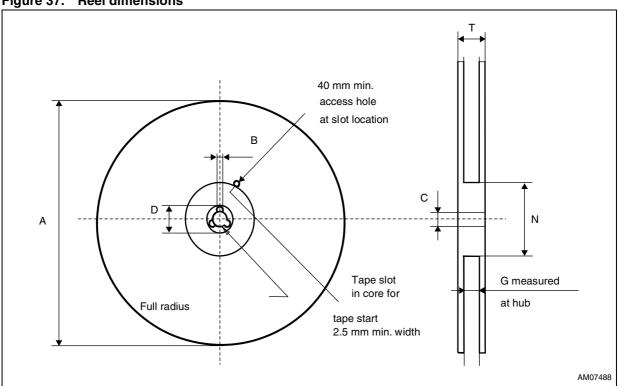

Figure 37. Reel dimensions

Table 9. Reel dimensions

| Tape size | A max.       | B min. | С        | D min. | N min. | G           | T max. |

|-----------|--------------|--------|----------|--------|--------|-------------|--------|

| 8 mm      | 180 (7 inch) | 1.5    | 13 ± 0.2 | 20.2   | 60     | 8.4 +2 / -0 | 14.4   |

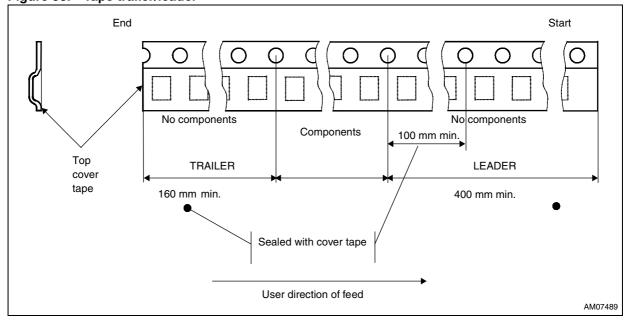

Figure 38. Tape trailer/leader

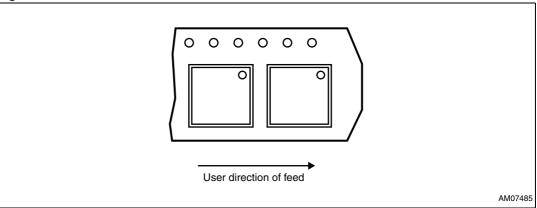

Figure 39. Pin 1 orientation

Note: Drawings are not to scale.

All dimensions are in mm, unless otherwise noted.

STBP112 Part numbering

## 11 Part numbering

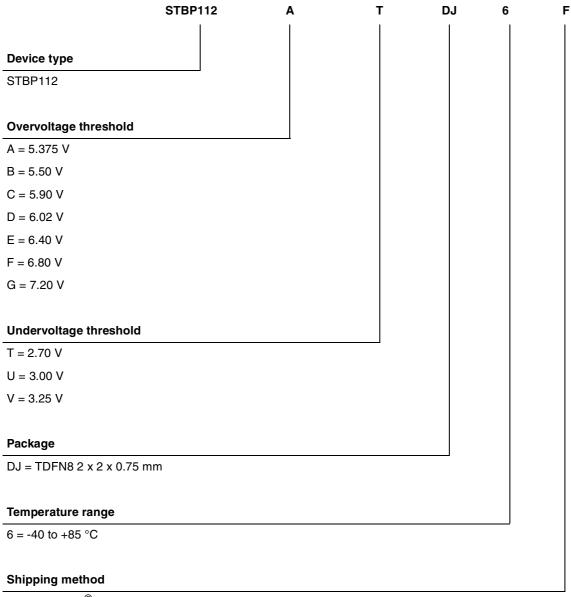

Table 10. Ordering information scheme

F = ECOPACK® package, tape and reel

Note: Please check device version availability on www.st.com. Please contact local ST sales office for new device version request.

# 12 Package marking information

Table 11. Marking description

| Part number <sup>(1)</sup> , <sup>(2)</sup> | Overvoltage threshold (V) | Undervoltage threshold (V) | Topside marking |  |

|---------------------------------------------|---------------------------|----------------------------|-----------------|--|

| STBP112ATxxxx                               | 5.375                     | 2.70                       | 12A             |  |

| STBP112BTxxxx                               | 5.50                      | 2.70                       | 12B             |  |

| STBP112CTxxxx                               | 5.90                      | 2.70                       | 12C             |  |

| STBP112DTxxxx                               | 6.02                      | 2.70                       | 12D             |  |

| STBP112ETxxxx                               | 6.40                      | 2.70                       | 12E             |  |

| STBP112FTxxxx                               | 6.80                      | 2.70                       | 12F             |  |

| STBP112GTxxxx                               | 7.20                      | 2.70                       | 12H             |  |

| STBP112AUxxxx                               | 5.375                     | 3.00                       | 12K             |  |

| STBP112BUxxxx                               | 5.50                      | 3.00                       | 12L             |  |

| STBP112CUxxxx                               | 5.90                      | 3.00                       | 12M             |  |

| STBP112DUxxxx                               | 6.02                      | 3.00                       | 12N             |  |

| STBP112EUxxxx                               | 6.40                      | 3.00                       | 12P             |  |

| STBP112FUxxxx                               | 6.80                      | 3.00                       | 12Q             |  |

| STBP112GUxxxx                               | 7.20                      | 3.00                       | 12R             |  |

| STBP112AVxxxx                               | 5.375                     | 3.25                       | 12T             |  |

| STBP112BVxxxx                               | 5.50                      | 3.25                       | 12U             |  |

| STBP112CVxxxx                               | 5.90                      | 3.25                       | 12V             |  |

| STBP112DVxxxx                               | 6.02                      | 3.25                       | 12W             |  |

| STBP112EVxxxx                               | 6.40                      | 3.25                       | 12X             |  |

| STBP112FVxxxx                               | 6.80                      | 3.25                       | 12Y             |  |

| STBP112GVxxxx                               | 7.20                      | 3.25                       | 12Z             |  |

Please check device version availability on www.st.com. Please contact local ST sales office for new device version request.

<sup>2.</sup> Currently available part numbers are marked bold in *Table 11*. For other options, or for more information on any aspect of this device, please contact the nearest ST sales office.

STBP112 Revision history

# 13 Revision history

Table 12. Document revision history

| Date          | Revision | Changes                                                                                                                                                                                                                                                                     |

|---------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22-Jun-2012   | 1        | Initial release.                                                                                                                                                                                                                                                            |

| 17-Oct-2012   | 2        | Updated <i>Features</i> (modified R <sub>DS(on)</sub> ). Added <i>Section : Typical operating characteristics (STBP112CV)</i> ( <i>Figure 11</i> to <i>Figure 34</i> ). Updated <i>Table 5</i> (modified typ. R <sub>DS(on)</sub> ). Minor corrections throughout document. |

| 07-Dec-2012 3 |          | Updated <i>Table 11</i> (STBP112CVxxxx par number marked bold, reformatted Note <i>1.</i> , added Note <i>2.</i> )                                                                                                                                                          |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY TWO AUTHORIZED ST REPRESENTATIVES, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2012 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

38/38 Doc ID 023357 Rev 3