# Precision Analog Microcontroller with Chemical Sensor Interface

### **Data Sheet**

# ADuCM355

#### **FEATURES**

Analog input/output 16-bit, 400 kSPS ADC Voltage, current, and impedance measurement capability Internal and external current and voltage channels Ultralow leakage switch matrix and input mux Input buffers, PGA Voltage DACs Two dual output voltage DACs Output range: 0.2 V to 2.4 V (±2.2 V voltage potential to sensor) for 12-bit outputs Two bias potentiostat and TIA amplifiers Ultralow power, 1 µA per amplifier One high speed 12-bit voltage DAC Output range to sensor: -607 mV to +607 mV High speed TIA for impedance measurements Programmable gain amplifier on output Amplifiers, accelerators, and references Two low power, low noise amplifiers Suitable for potentiostat bias in electrochemical sensing Two low power, low noise TIAs Suitable for measuring sensor current output in the ±0.00005 µA to ±3000 µA range Programmable load and gain resistors Analog hardware accelerators Digital waveform generator (refer to the ADuCM355 Hardware Reference Manual) **DFT and digital filters** 2.5 V and 1.82 V on-chip, precision voltage references Internal temperature sensor, ±2°C accurate Impedance measurement range of <1  $\Omega$  to 10 M $\Omega$ , 0.016 Hz to 200,000 Hz Voltammetry scan rate up to 2000 steps per second Microcontroller

26 MHz Arm Cortex-M3 processor

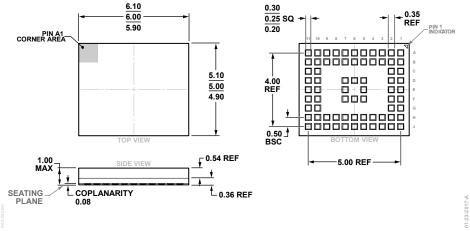

Serial wire port supports code download and debugging 128 kB flash/64 kB of SRAM Security and safety Hardware cyclic redundancy check (CRC) with programmable polynomial generator (refer to the ADuCM355 Hardware Reference Manual) Read and write protection of user flash **On-chip peripherals** UART, I<sup>2</sup>C, and SPI serial input/output Up to 17 GPIO pins **External interrupt option** General-purpose, wake-up, and watchdog timers Power 2.8 V to 3.6 V supply and active measurement range Power supply monitor Active current consumption: 30 µA/MHz for digital section Hibernate with bias to external sensor: 8.5 µA Shutdown mode with no SRAM retention: 2 µA Package and temperature range 6 mm × 5 mm, 72-lead LGA package Fully specified for -40°C to +85°C ambient operation **APPLICATIONS Gas detection Food quality**

Gas detection Food quality Environmental sensing (air, water, and soil) Blood glucose meters Life sciences and biosensing analysis Bioimpedance measurements General amperometry, voltammetry, and impedance spectroscopy functions

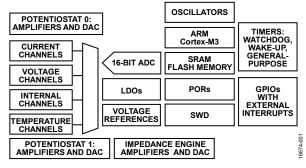

#### SIMPLIFIED FUNCTIONAL BLOCK DIAGRAM

Figure 1.

#### Rev. C

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2019–2020 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

### **TABLE OF CONTENTS**

| Features                                   |

|--------------------------------------------|

| Applications 1                             |

| Simplified Functional Block Diagram 1      |

| Revision History                           |

| Functional Block Diagram                   |

| General Description                        |

| Specifications                             |

| Microcontroller Electrical Specifications5 |

| RMS Noise Resolution of ADC15              |

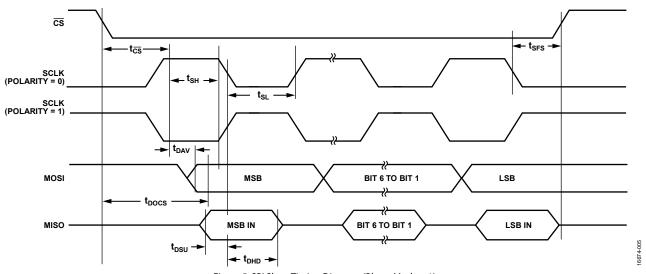

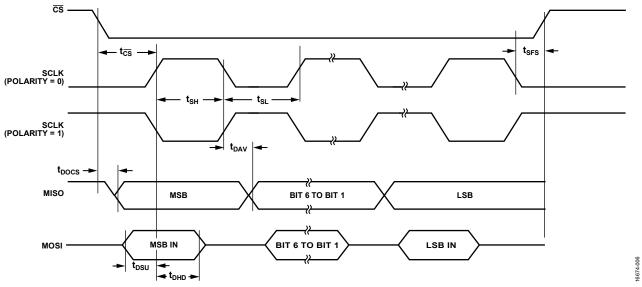

| Timing Specifications16                    |

#### **REVISION HISTORY**

| 4/2020—Rev. B to Rev. C |   |

|-------------------------|---|

| Change to Figure 19     |   |

|                         |   |

| 6/2019—Rev. A to Rev. B |   |

| Changes to Figure 2     | 3 |

| Changes to Figure 2                            | 3  |

|------------------------------------------------|----|

| Changes to Table 1                             | 9  |

| Changes to RMS Noise Resolution of ADC Section |    |

| and Table 3                                    | 15 |

|                                                |    |

| Absolute Maximum Ratings                    |

|---------------------------------------------|

| Thermal Resistance 19                       |

| ESD Caution 19                              |

| Pin Configuration and Function Descriptions |

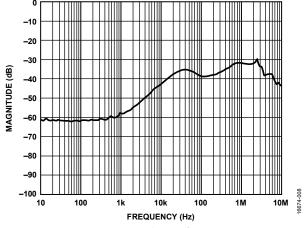

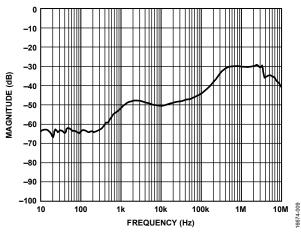

| Typical Performance Characteristics         |

| Applications Information                    |

| Recommended Circuit and Component Values    |

| Outline Dimensions                          |

| Ordering Guide 28                           |

| Changes to Figure 7                                   | 20 |

|-------------------------------------------------------|----|

| Change to Table 8                                     |    |

| Added Figure16 and Figure 17; Renumbered Sequentially |    |

| Changes to Figure 19                                  | 27 |

|                                                       |    |

| 4/2019—Rev. 0 to Rev. A                               |    |

| Changes to Table 8                                    | 21 |

3/2019—Revision 0: Initial Version

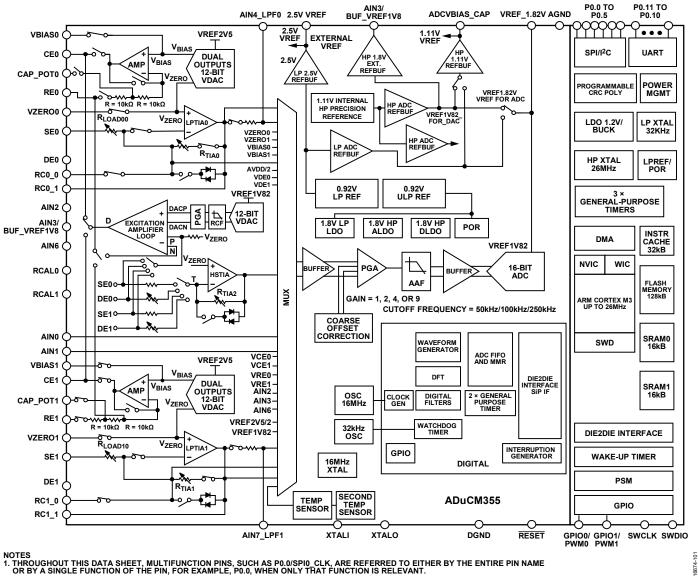

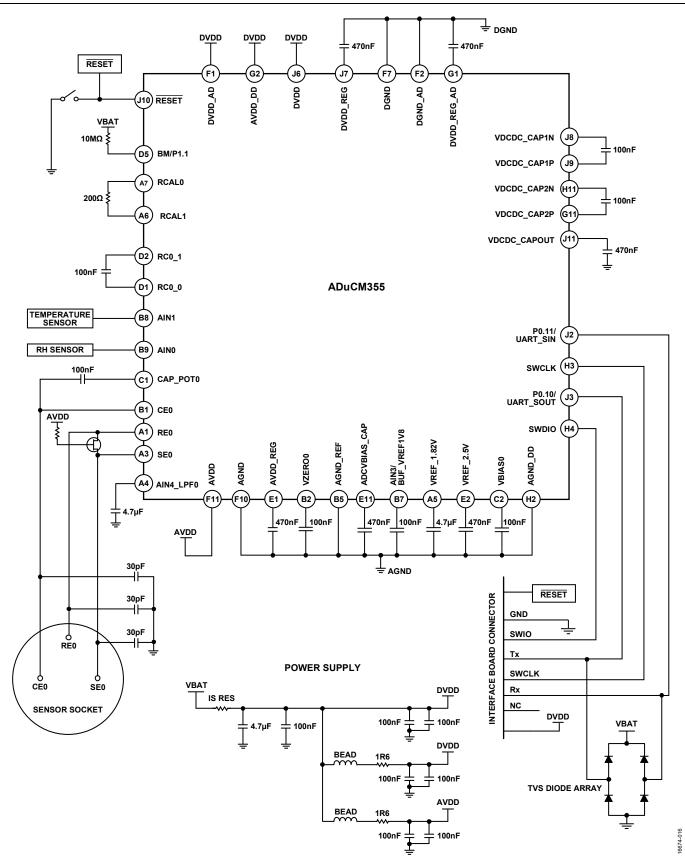

### FUNCTIONAL BLOCK DIAGRAM

Figure 2.

### **GENERAL DESCRIPTION**

The ADuCM355 is an on-chip system that controls and measures electrochemical sensors and biosensors. The ADuCM355 is an ultralow power, mixed-signal microcontroller based on the Arm<sup>®</sup> Cortex<sup>™</sup>-M3 processor. The device features current, voltage, and impedance measurement capability.

The ADuCM355 features a 16-bit, 400 kSPS, multichannel successive approximation register (SAR) analog-to-digital converter (ADC) with input buffers, built-in antialias filter (AAF), and programmable gain amplifier (PGA). The current inputs include three transimpedance amplifiers (TIA) with programmable gain and load resistors for measuring different sensor types. The analog front end (AFE) also contains two low power amplifiers designed specifically for potentiostat capability to maintain a constant bias voltage to an external electrochemical sensor. The noninverting inputs of these two amplifiers are controlled by on-chip, dual output digital-to-analog converters (DACs). The analog outputs include a high speed DAC and output amplifier designed to generate an ac signal.

The ADC operates at conversion rates up to 400 kSPS with an input range of -0.9 V to +0.9 V. An input mux before the ADC allows the user to select an input channel for measurement. These input channels include three external current inputs, multiple external voltage inputs, and internal channels. The internal channels allow diagnostic measurements of the internal supply voltages, die temperature, and reference voltages.

Two of the three voltage DACs are dual output, 12-bit string DACs. One output per DAC controls the noninverting input of a potentiostat amplifier, and the other controls the noninverting input of the TIA.

The third DAC (sometimes referred to as the high speed DAC) is designed for the high power TIA for impedance measurements. The output frequency range of this DAC is up to 200 kHz.

A precision 1.82 V and 2.5 V on-chip reference source is available. The internal ADC and voltage DAC circuits use this on-chip reference source to ensure low drift performance for all peripherals.

The ADuCM355 integrates a 26 MHz Arm Cortex-M3 processor, which is a 32-bit reduced instruction set computer (RISC)

machine. The Arm Cortex-M3 processor also has a flexible multichannel direct memory access controller (DMA) supporting two independent serial peripheral interface (SPI) ports, universal asynchronous receiver/transmitter (UART), and I<sup>2</sup>C communication peripherals. The ADuCM355 has 128 kB of nonvolatile flash/EE memory and 64 kB of single random access memory (SRAM) integrated on-chip.

The digital processor subsystem is clocked from a 26 MHz on-chip oscillator. The oscillator is the source of the main digital die system clock. Optionally, a 26 MHz phase-locked loop (PLL) can be used as the digital system clock. This clock can be internally subdivided so that the processor operates at a lower frequency and saves power. A low power, internal 32 kHz oscillator is available and can clock the timers. The ADuCM355 includes three general-purpose timers, a wake-up timer (which can be used as a general-purpose timer), and a system watchdog timer.

The analog subsystem has a separate 16 MHz oscillator used to clock the ADC, DACs, and other digital logic on the analog die. The analog die also contains a separate 32 kHz, low power oscillator to clock a watchdog timer on the analog die. Both the 32 kHz oscillator and this watchdog are independent from the digital die oscillators and system watchdog timer.

A range of communication peripherals can be configured as required in a specific application. These peripherals include UART, I<sup>2</sup>C, two SPI ports, and general-purpose input/output (GPIO) ports. The GPIOs, combined with the general-purpose timers, can be combined to generate a pulse-width modulation (PWM) type output.

Nonintrusive emulation and program download are supported via the serial wire debug port (SW-DP) interface.

The ADuCM355 operates from a 2.8 V to 3.6 V supply and is specified over a temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C. The chip is packaged in a 72-lead, 6 mm × 5 mm land grid array (LGA) package.

Note that, throughout this data sheet, multifunction pins, such as P0.0/SPI0\_CLK, are referred to either by the entire pin name or by a single function of the pin, for example, P0.0, when only that function is relevant.

### **SPECIFICATIONS**

#### **MICROCONTROLLER ELECTRICAL SPECIFICATIONS**

AVDD = DVDD = 2.8 V to 3.6 V, maximum difference between supplies = 0.3 V, ADC reference and excitation DAC and amplifier = 1.82 V internal reference, low power VBIASx and VZEROX DAC reference = 2.5 V internal reference, central processing unit (CPU) speed ( $f_{CORE}$ ) = 26 MHz,  $T_A = -40^{\circ}$ C to +85°C, buck convertor on digital die disabled, unless otherwise noted.

#### Table 1.

| Parameter                                                 | Symbol                     | Min   | Тур  | Max   | Unit               | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------|----------------------------|-------|------|-------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC SPECIFICATIONS                                        |                            |       |      |       |                    | Pseudo differential mode measured<br>relative to ADCVBIAS_CAP pin voltage<br>(1.82 V) unless otherwise stated,<br>specifications based on high speed mode<br>unless otherwise stated, ADC voltage<br>channel calibrated in production with PG/<br>gain = 1.5, AFE die analog clock (ACLK) =<br>32 MHz or 16 MHz unless otherwise stated |

| Data Rate <sup>1</sup>                                    | <b>f</b> sample            |       |      | 400   | kSPS               | High speed mode, decimation factor of 4                                                                                                                                                                                                                                                                                                 |

|                                                           | <b>f</b> <sub>SAMPLE</sub> |       |      | 200   | kSPS               | Normal mode, decimation factor of 4                                                                                                                                                                                                                                                                                                     |

| Resolution <sup>1</sup>                                   |                            | 16    |      |       | Bits               | Number of data bits                                                                                                                                                                                                                                                                                                                     |

| Integral Nonlinearity <sup>1</sup>                        | INL                        | -4    | ±2.0 | +4.0  | LSB                | PGA Gain = 1.5, 1.82 V internal reference,<br>1 LSB <sup>2</sup> = $(1.82 V/2^{15})/PGA$ gain                                                                                                                                                                                                                                           |

|                                                           |                            | -5.6  | ±2.0 | +4.7  | LSB                | PGA gain = 9, 1.82 V internal reference                                                                                                                                                                                                                                                                                                 |

|                                                           |                            |       | ±2.0 |       | LSB                | 1.82 V external reference, 1 LSB <sup>2</sup> = (1.82 V/2 <sup>15</sup> )/PGA gain                                                                                                                                                                                                                                                      |

| Differential Nonlinearity (No Missing Codes) <sup>1</sup> | DNL                        | -0.99 | ±0.9 | +2.5  | LSB                | 1.82 V internal reference, 1 LSB <sup>2</sup> = (1.82 V/2 <sup>15</sup> )/PGA gain                                                                                                                                                                                                                                                      |

| DC Code Distribution <sup>3</sup>                         |                            |       | ±6   |       | LSB                | Minimum and maximum range from mea<br>ADC codes for 1000 ADC samples, PGA<br>gain = 1.5, low power mode, ADC input<br>0.9 V, ADC output data rate = 200 kSPS,<br>1 LSB <sup>2</sup> = (1.82 V/2 <sup>15</sup> )/PGA gain                                                                                                                |

|                                                           |                            |       | ±6   |       | LSB                | Input channel is low power TIA $0 = 1 \mu A$ , TIA<br>resistor (R <sub>TIA</sub> ) = 512 k $\Omega$ , load resistor (R <sub>LOAD</sub> ) =<br>10 $\Omega$ , ADC output data rate = 200 kSPS                                                                                                                                             |

|                                                           |                            |       | ±6   |       | LSB                | Input channel is high power TIA (HPTIA) = 1 $\mu$ A, R <sub>TIA</sub> = 10 k $\Omega$ , R <sub>LOAD</sub> = 100 $\Omega$ , ADC output data rate = 200 kSPS                                                                                                                                                                              |

| ADC ENDPOINT ERRORS                                       |                            |       |      |       |                    | For AIN0 to AIN7_LPF1 inputs, 200 kSPS AD update rate, sinc3 filter enabled                                                                                                                                                                                                                                                             |

| Offset Error                                              |                            | -600  | ±200 | +600  | μV                 | PGA gain = 1.5, low power mode, all<br>channels except AIN3                                                                                                                                                                                                                                                                             |

|                                                           |                            | -620  | ±200 | +880  | μV                 | PGA gain = 1.5, low power mode, AIN3 only                                                                                                                                                                                                                                                                                               |

| High Power Mode⁴                                          |                            | -1.1  | ±0.5 | +1.4  | mV                 | PGA gain = 1.5, high power mode                                                                                                                                                                                                                                                                                                         |

| Drift <sup>1</sup>                                        |                            |       | ±3   |       | μV/°C              | Using 1.82 V internal reference                                                                                                                                                                                                                                                                                                         |

| Offset Matching                                           |                            |       | ±2   |       | LSB                | Matching compared to AIN3                                                                                                                                                                                                                                                                                                               |

| Full-Scale Error                                          |                            | -750  | ±400 | +940  | μV                 | Excluding internal channels, both negative<br>and positive full scale, error at both<br>endpoints, PGA gain = 1.5, low power mod                                                                                                                                                                                                        |

| High Power Mode <sup>4</sup>                              |                            | -1.6  | ±0.8 | +1.82 | mV                 | PGA gain = 1.5, high power mode                                                                                                                                                                                                                                                                                                         |

| Internal Channels <sup>1</sup>                            |                            |       | 0.2  | 0.75  | % of full<br>scale | AVDD/2, DVDD/2, ADCVBIAS_CAP,<br>VREF_2.5V, VREF_1.8V, AVDD_REG                                                                                                                                                                                                                                                                         |

| Gain Drift <sup>1</sup>                                   |                            | -3    | ±1   | +3    | μV/°C              | Full-scale error drift minus offset error dri                                                                                                                                                                                                                                                                                           |

| Gain Error Matching                                       |                            |       | ±3   |       | LSB                | Mismatch from channel to channel                                                                                                                                                                                                                                                                                                        |

| Parameter                                    | Symbol | Min      | Тур  | Max    | Unit     | Test Conditions/Comments                                                                                                                 |

|----------------------------------------------|--------|----------|------|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| PGA Mismatch Error <sup>1</sup>              |        |          |      |        |          |                                                                                                                                          |

| PGA Gain Mismatch Drift                      |        |          | 1.5  |        | μV/°C    | Drift after calibration                                                                                                                  |

| Uncalibrated PGA Gain Mismatch               |        |          | 4    |        | %        | Production devices only calibrated for PG, gain = 1.5                                                                                    |

| Uncalibrated PGA Gain Mismatch<br>Drift      |        |          | 10   |        | μV/°C    | Uncalibrated drift                                                                                                                       |

| ADC DYNAMIC PERFORMANCE                      |        |          |      |        |          | Input signal frequency ( $f_{IN}$ ) = 20 kHz sine<br>wave, $f_{SAMPLE}$ = 200 kSPS, using AINx voltage<br>input channels, PGA gain = 1.5 |

| Signal-to-Noise Ratio                        | SNR    |          |      |        |          | Includes distortion and noise components                                                                                                 |

|                                              |        |          | 80   |        | dB       | PGA gain = 1, 1.5, and 2                                                                                                                 |

|                                              |        |          | 76   |        | dB       | PGA gain = 4                                                                                                                             |

|                                              |        |          | 70   |        | dB       | PGA gain = 9                                                                                                                             |

| Total Harmonic Distortion <sup>1</sup>       | THD    |          | -84  |        | dB       |                                                                                                                                          |

| Peak Harmonic or Spurious Noise <sup>1</sup> |        |          | -86  |        | dB       |                                                                                                                                          |

| Channel to Channel Crosstalk <sup>1</sup>    |        |          | -86  |        | dB       | Measured on adjacent channels                                                                                                            |

| Noise (RMS) <sup>1,5</sup>                   |        | See      |      |        |          | 0.1 Hz to 10 Hz                                                                                                                          |

|                                              |        | Table 2  |      |        |          |                                                                                                                                          |

|                                              |        |          | 800  |        | nV/√Hz   | Chop off                                                                                                                                 |

|                                              |        |          | 400  |        | nV/√Hz   | Chop on                                                                                                                                  |

| ADC INPUT                                    |        |          |      |        |          | Input to ADC mux                                                                                                                         |

| Input Voltage Ranges <sup>1</sup>            |        | 0.2      |      | 2.1    | V        | Voltage applied to any input pin                                                                                                         |

| Pseudo Differential Voltage                  |        |          |      |        |          | Between ADCVBIAS_CAP pin voltage<br>(1.82 V) and analog input from mux                                                                   |

|                                              |        | -0.9     |      | +0.9   | V        | Gain = 1                                                                                                                                 |

|                                              |        | -0.9     |      | +0.9   | V        | Gain = 1.5                                                                                                                               |

|                                              |        | -0.6     |      | +0.6   | V        | Gain = 2                                                                                                                                 |

|                                              |        | -0.3     |      | +0.3   | V        | Gain = 4                                                                                                                                 |

|                                              |        | -0.133   |      | +0.133 | V        | Gain = 9                                                                                                                                 |

| Input Range <sup>1</sup>                     |        | ±0.00005 |      | ±3000  | μΑ       | Low power TIA 0, low power TIA 1, and HPTIA current input channel ranges                                                                 |

| Common-Mode Range <sup>1</sup>               |        | 0.2      | 1.1  | 2.1    | V        |                                                                                                                                          |

| Leakage Current                              |        | -1.5     | ±0.5 | +1.5   | nA       | AIN0 to AIN7_LPF1, SE0, and SE1 pins<br>(exclusive of DE0 and DE1 pins)                                                                  |

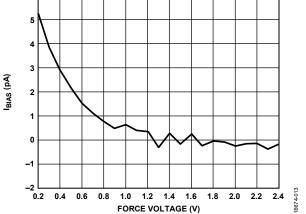

|                                              |        |          | ±2   |        | nA       | DE0 and DE1 pins only, see Figure 14                                                                                                     |

| Input Current <sup>1</sup>                   |        | -8       | ±2   | +8     | nA       | AIN0 to AIN7_LPF1, SE0, SE1, and DE0 pins                                                                                                |

| Input Capacitance                            |        |          | 40   |        | pF       | During ADC acquisition                                                                                                                   |

| AAF, 3 dB Frequency Range                    |        |          |      |        |          | 3 programmable settings                                                                                                                  |

| Mode 0                                       |        |          | 50   |        | kHz      |                                                                                                                                          |

| Mode 1                                       |        |          | 100  |        | kHz      |                                                                                                                                          |

| Mode 2                                       |        |          | 250  |        | kHz      |                                                                                                                                          |

| ADC Channel Switch Settling Time             |        |          | 250  |        | Ki iz    | Time delay required after switching ADC input channel, excludes sinc3 settling time                                                      |

| AAF, 3 dB Cutoff Frequency <sup>1</sup>      |        |          |      |        |          |                                                                                                                                          |

| 250 kHz                                      |        | 25       |      |        | μs       |                                                                                                                                          |

| 100 kHz                                      |        | 40       |      |        | μs<br>μs |                                                                                                                                          |

| 50 kHz                                       |        | 40<br>60 |      |        | -        |                                                                                                                                          |

| <b>Ου ΚΠΖ</b>                                | 1      | 00       |      |        | μs       |                                                                                                                                          |

| Parameter                                                         | Symbol     | Min   | Тур  | Max           | Unit    | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------|------------|-------|------|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

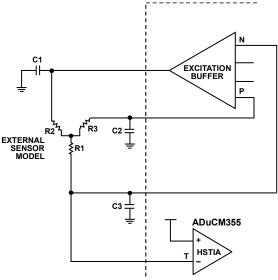

| DISCRETE FOURIER TRANSFORM (DFT)-<br>BASED IMPEDANCE MEASUREMENTS |            |       |      |               |         | For impedance (Z) of 1 k $\Omega$ (0.02% tolerant<br>resistor), excitation frequency = 0.1 Hz to<br>200 kHz, sine amplitude = 10 mV rms,<br>R <sub>TIA</sub> = 5 k $\Omega$ , RCALx = 200 $\Omega$ , 1% accurate<br>temperature coefficient 5 ppm/°C, single<br>DFT measurement, DFT using 8192 ADC<br>samples, Hanning on, HSDACCON, Bits[8:1] =<br>0x1B for low power mode and impedance<br>measurements ≤80 kHz, HSDACCON,<br>Bits[8:1] = 0x7 for high power mode and<br>impedance measurements > 80 Hz |

| Magnitude                                                         |            | -1.25 | ±0.2 | +1.25         | %       | 20 kHz to 200 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| -                                                                 |            |       | ±0.2 |               | %       | 10 Hz to 20 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                   |            |       | ±1   |               | %       | 1 Hz to <10 Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Phase                                                             |            | -0.3  | ±0.1 | +0.3          | Degrees |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Three Resistor Star Cell                                          |            |       |      |               |         | $Z = 2.2 \Omega$ connected, see Figure 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Accuracy                                                          |            |       |      |               |         | 0.1 Hz to 200 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Magnitude                                                         |            |       | ±0.5 |               | %       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Phase                                                             |            |       | ±0.5 |               | Degrees |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Accuracy                                                          |            |       |      |               |         | Z = 100 $\Omega$ connected, 0.1 Hz to 200 kHz, see Figure 18                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Magnitude                                                         |            |       | ±0.2 |               | %       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Phase                                                             |            |       | ±0.2 |               | Degrees |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| High Speed Loop                                                   |            |       |      |               |         | See Figure 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Allowed External Load                                             |            |       |      | 100           | pF      | R2 + R3 $\leq$ 200 $\Omega$ , R1 $\leq$ 100 $\Omega$ , for excitation                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Capacitance <sup>1</sup>                                          |            |       |      | 50            | pF      | frequencies $\ge 1$ kHz<br>R2 + R3 $\le 1$ k $\Omega$ , R1 $\le 500 \Omega$ , for excitation<br>frequencies $\ge 1$ kHz                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                   |            |       |      | 40            | pF      | R2 + R3 ≤ 1.6 kΩ, R1 ≤ 800 Ω, for excitation frequencies ≥ 1 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Excitation Amplifier Bandwidth                                    |            |       | 3    |               | MHz     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Impedance Frequency Range <sup>1</sup>                            |            | 0.016 | 5    | 200,000       | Hz      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Impedance Measurement Range <sup>1</sup>                          |            | 0.4   |      | 10,000        | Ω       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| LOW POWER TIA AND POTENTIOSTAT<br>AMPLIFIERS                      |            |       |      |               |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Input Bias Current                                                |            |       | 80   | 300           | pА      | TIA, SEx pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                   |            |       | 20   | 150           | pА      | Potentiostat amplifiers, REx pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Offset Voltage                                                    |            |       | 50   | 150           | μV      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Offset Voltage Drift vs. Temperature                              |            |       | 1    |               | μV/°C   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Noise                                                             |            |       |      |               |         | Unity-gain mode, rms voltage in 0.1 Hz to<br>10 Hz range                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                   |            |       | 1.6  |               | μV rms  | Normal mode (LPTIACONx Bit 2 = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                   |            |       | 2    |               | μV rms  | Half power mode (LPTIACONx Bit $2 = 1$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Potentiostat Source and Sink<br>Current <sup>1</sup>              |            | -750  |      | +750          | μΑ      | Normal mode (LPTIACONx, Bits[4:3] = 00), from CEx pins                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                   |            | -3    |      | +3            | mA      | High current mode (LPTIACONx, Bits[4:3] = 01 or 11), from CEx pins                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DC Power Supply Rejection Ratio                                   | DC<br>PSRR |       | 70   |               | dB      | At REx pin, $R_{TIA} = 256 \text{ k}\Omega$ , $R_{LOAD} = 10 \Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Input Common-Mode Voltage Range <sup>1</sup>                      |            | 300   |      | AVDD –<br>600 | mV      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Output Voltage Range <sup>1</sup>                                 |            | 300   |      | AVDD -        | mV      | Normal mode (LPTIACONx, Bits[4:3] = 00),                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                   |            | 300   |      | 400<br>AVDD – | mV      | sink and source 750 μA<br>High current mode (LPTIACONx, Bits[4:3] =                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Parameter                                                              | Symbol | Min   | Тур          | Max  | Unit             | Test Conditions/Comments                                                                                                                                                         |

|------------------------------------------------------------------------|--------|-------|--------------|------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overcurrent Limit Protection                                           |        |       | 20           |      | mA               | Amplifiers try to limit source and sink current to this value via internal clamp                                                                                                 |

| Allowed Duration of Overcurrent<br>Limit <sup>1</sup>                  |        |       |              | 5    | sec              | User must limit duration of overcurrent condition to less than this value or risk damaging amplifier                                                                             |

| Allowed Frequency of Overcurrent<br>Conditions                         |        |       |              | 1    | Per<br>hour      |                                                                                                                                                                                  |

| Short-Circuit Current                                                  |        |       | 12           |      | mA               | When amplifier output is shorted to ground                                                                                                                                       |

| PROGRAMMABLE RESISTORS                                                 |        |       |              |      |                  |                                                                                                                                                                                  |

| Low Power TIA R <sub>LOAD</sub> on SE0, SE1<br>Inputs <sup>1</sup>     |        |       |              |      |                  |                                                                                                                                                                                  |

| Drift over Temperature                                                 |        |       | ±200<br>±400 |      | ppm/°C<br>ppm/°C | 10 Ω, 30 Ω, 100 Ω, 1500 Ω, 3000 Ω, 3500 Ω<br>50 Ω                                                                                                                                |

| 0 Ω RLOAD Accuracy                                                     |        | 0.01  | 0.08         | 0.15 | Ω                |                                                                                                                                                                                  |

| 10 Ω RLOAD Accuracy                                                    |        | 9.8   | 11.7         | 13.5 | Ω                |                                                                                                                                                                                  |

| 30 Ω R <sub>LOAD</sub> Accuracy                                        |        | 28    | 33.8         | 39   | Ω                |                                                                                                                                                                                  |

| 50 Ω R <sub>LOAD</sub> Accuracy                                        |        | 48    | 55           | 63   | Ω                |                                                                                                                                                                                  |

| 100 $\Omega$ RLOAD Accuracy                                            |        | 88    | 110          | 130  | Ω                |                                                                                                                                                                                  |

| Low Power TIA R <sub>TIA</sub> Gain on SE0, SE1<br>Inputs <sup>1</sup> |        |       |              |      |                  |                                                                                                                                                                                  |

| Accuracy                                                               |        | -5    |              | +15  | %                | User programmable, includes 1 kΩ, 2 kΩ, 3 kΩ,<br>4 kΩ, 6 kΩ, 8 kΩ, 10 kΩ, 16 kΩ, 20 kΩ, 22 kΩ,<br>30 kΩ, 40 kΩ, 64 kΩ, 100 kΩ, 128 kΩ, 160 kΩ,<br>192 kΩ, 256 kΩ, 512 kΩ         |

|                                                                        |        | 115   | 120          | 130  | Ω                | 200 $\Omega$ setting with R <sub>LOAD</sub> = 100 $\Omega$                                                                                                                       |

| Drift over Temperature                                                 |        |       | ±100         |      | ppm/°C           |                                                                                                                                                                                  |

| Low Power TIA R <sub>TIA</sub> Mismatch Error <sup>1</sup>             |        |       |              |      |                  | Error when moving up or down one R <sub>TIA</sub> value                                                                                                                          |

|                                                                        |        | -0.6  | +0.2         | +0.6 | %                | 512 kΩ to 2 kΩ range excluding 40 kΩ                                                                                                                                             |

|                                                                        |        | -3.5  | +0.5         | +3.5 | %                | 40 k $\Omega$ (up to 48 k $\Omega$ , down to 32 k $\Omega$ )                                                                                                                     |

|                                                                        |        |       | ±20          |      | %                | 200 Ω                                                                                                                                                                            |

| HPTIA RLOAD on SE0, SE1 Inputs <sup>1</sup>                            |        |       |              |      |                  |                                                                                                                                                                                  |

| Accuracy                                                               |        | 102   | 110          | 116  | Ω                | Fixed 100 $\Omega$ target setting                                                                                                                                                |

| Drift                                                                  |        |       | ±160         |      | ppm/°C           | · ····································                                                                                                                                           |

| HPTIA RTIA Gain on SEO, SE1 Inputs <sup>1</sup>                        |        |       |              |      | PP               | RTIA02 and RTIA04                                                                                                                                                                |

| Accuracy                                                               |        |       | ±20          |      | %                | User programmable, includes 0.2 k $\Omega$ , 1 k $\Omega$ ,<br>5 k $\Omega$ , 10 k $\Omega$ , 20 k $\Omega$ , 40 k $\Omega$ , 80 k $\Omega$ , 160 k $\Omega$                     |

| Drift                                                                  |        |       | ±200         |      | ppm/°C           |                                                                                                                                                                                  |

| HPTIA RLOAD on DE0, DE1 Inputs <sup>1</sup>                            |        |       |              |      |                  | RLOAD03 and RLOAD05                                                                                                                                                              |

| Accuracy                                                               |        | 0.001 |              | 0.15 | Ω                | 0 Ω setting                                                                                                                                                                      |

| ,                                                                      |        | 5     |              | 10.7 | Ω                | 10 Ω setting                                                                                                                                                                     |

|                                                                        |        | 26.5  | 32.6         | 37.6 | Ω                | $30 \Omega$ setting                                                                                                                                                              |

|                                                                        |        |       | ±20          |      | %                | $30 \Omega$ , $50 \Omega$ , and $100 \Omega$ settings                                                                                                                            |

| Drift over Temperature                                                 |        |       | ±0.2         |      | %/°C             | $10 \Omega$ setting                                                                                                                                                              |

| Dintover remperature                                                   |        |       | ±200         |      | ppm/°C           | Excludes $R_{LOAD} = 0 \Omega$ and $10 \Omega$                                                                                                                                   |

| HPTIA R <sub>TIA</sub> Gain on DE0, DE1 Inputs <sup>1</sup>            |        |       | ±200         |      | ppin/ C          | User programmable, includes 0.1 k $\Omega$ ,<br>0.2 k $\Omega$ , 1 k $\Omega$ , 5 k $\Omega$ , 10 k $\Omega$ , 20 k $\Omega$ , 40 k $\Omega$ ,<br>80 k $\Omega$ , 160 k $\Omega$ |

| Accuracy                                                               |        | 120   | 135          | 150  | Ω                | 100 Ω setting                                                                                                                                                                    |

|                                                                        |        | 230   | 250          | 290  | Ω                | 200 Ω setting                                                                                                                                                                    |

|                                                                        |        |       | ±20          |      | %                | 1 kΩ, 5 kΩ, 10 kΩ, 20 kΩ, 40 kΩ, 80 kΩ,<br>160 kΩ                                                                                                                                |

| Drift over Temperature                                                 |        |       | ±350         |      | ppm/°C           | 100 Ω, 200 Ω settings                                                                                                                                                            |

|                                                                        |        |       | ±200         |      | ppm/°C           | 1 kΩ, 5 kΩ, 10 kΩ, 20 kΩ, 40 kΩ, 80 kΩ,<br>160 kΩ                                                                                                                                |

| Parameter                                                          | Symbol  | Min  | Тур  | Max           | Unit            | Test Conditions/Comments                                                                                                                      |

|--------------------------------------------------------------------|---------|------|------|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| HPTIA $R_{TIA}$ Mismatch Error SE0, SE1, DE0, and DE1 <sup>1</sup> |         |      |      |               |                 | Error introduced when moving up or down one RTIA value                                                                                        |

|                                                                    |         | -3.5 | +1   | +3.5          | %               | 160 kΩ to 5 kΩ range                                                                                                                          |

|                                                                    |         | -2.5 | ±2   | +5            | %               | 1 kΩ, 200 Ω, and 100 Ω                                                                                                                        |

| HPTIA AMPLIFIER                                                    |         |      |      |               |                 |                                                                                                                                               |

| Bias Current                                                       |         |      | 1    |               | nA              |                                                                                                                                               |

| Maximum Current Sink and Source <sup>1</sup>                       |         | -3   |      | +3            | mA              | Ensure $R_{TIA}$ selection generates output voltage of less than $\pm 900$ mV with PGA gain = 1                                               |

| Input Common-Mode Voltage Range <sup>1</sup>                       |         | 300  |      | AVDD –<br>700 | mV              |                                                                                                                                               |

| Output Voltage Range <sup>1</sup>                                  |         | 200  |      | AVDD –<br>400 | mV              |                                                                                                                                               |

| Overcurrent Limit Protection <sup>1</sup>                          |         |      | 17   |               | mA              | Amplifier tries to limit source and sink current to this value via internal clamp, tested with $R_{LOAD} = 0 \Omega$ , $R_{TIA} = 100 \Omega$ |

| Allowed Duration of Overcurrent<br>Limit <sup>1</sup>              |         |      |      | 5             | sec             |                                                                                                                                               |

| Allowed Frequency of Overcurrent                                   |         |      |      | 1             | Per             |                                                                                                                                               |

| Conditions <sup>1</sup>                                            |         |      |      |               | hour            |                                                                                                                                               |

| Short-Circuit Current                                              |         |      | 30   |               | mA              | When amplifier output is shorted to ground                                                                                                    |

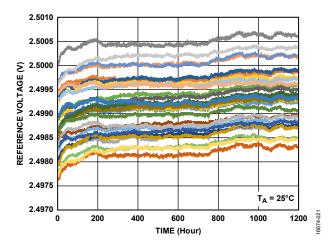

| LOW POWER ON-CHIP VOLTAGE<br>REFERENCE                             |         |      | 2.5  |               | V               | 0.47 μF from VREF_2.5V to AGND,<br>reference is measured with all low power<br>voltage DACs and output amplifiers enabled                     |

| Accuracy                                                           |         |      |      | ±5            | mV              | $T_A = 25^{\circ}C$                                                                                                                           |

| Noise <sup>1</sup>                                                 |         |      | 60   |               | µV р-р          | Peak-to-peak voltage in 0.1 Hz to 10 Hz<br>range                                                                                              |

| Reference Temperature Coefficient <sup>1,6</sup>                   |         | -25  | ±10  | +25           | ppm/°C          |                                                                                                                                               |

| DC Power Supply Rejection Ratio                                    | DC PSRR |      | 70   |               | dB              | DC variation due to AVDD supply changes                                                                                                       |

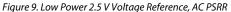

| AC Power Supply Rejection Ratio <sup>7</sup>                       | AC PSRR |      | 48   |               | dB              | AC 1 kHz, 50 mV peak-to-peak ripple applied to AVDD supply                                                                                    |

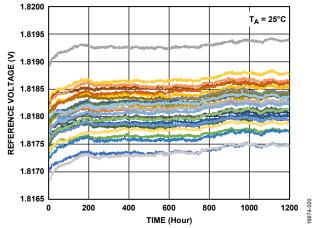

| Long-Term Stability <sup>8</sup>                                   |         |      | 100  |               | ppm/<br>1000 hr |                                                                                                                                               |

| HIGH POWER REFERENCES                                              |         |      |      |               |                 |                                                                                                                                               |

| High Power On-Chip Voltage<br>Reference                            |         |      | 1.82 |               | V               | 4.7 $\mu\text{F}$ from VREF_1.82V to AGND, reference is measured with ADC enabled                                                             |

| Accuracy                                                           |         |      |      | ±5            | mV              | $T_A = 25^{\circ}C$                                                                                                                           |

| Reference Temperature Coefficient <sup>1,2</sup>                   |         | -20  | ±5   | +20           | ppm/°C          |                                                                                                                                               |

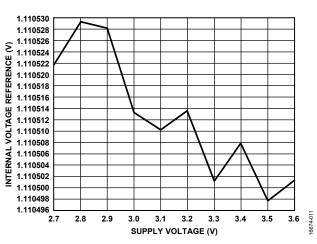

| DC Power Supply Rejection Ratio                                    | DC PSRR |      | 85   |               | dB              | DC variation due to AVDD supply changes                                                                                                       |

| AC Power Supply Rejection Ratio <sup>9</sup>                       | AC PSRR |      | 60   |               | dB              | AC 1 kHz, 50 mV peak-to-peak ripple applied to AVDD supply                                                                                    |

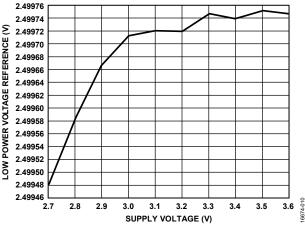

| ADC Common Mode Reference<br>Source                                |         |      | 1.11 |               | V               | 470 nF from ADCVBIAS_CAP to AGND, reference is measured with ADC enabled                                                                      |

| Accuracy                                                           |         |      |      | ±5            | mV              | $T_A = 25^{\circ}C$                                                                                                                           |

| Reference Temperature Coefficient <sup>1</sup>                     |         | -20  | ±5   | +20           | ppm/°C          |                                                                                                                                               |

| DC Power Supply Rejection Ratio                                    | DC PSRR |      | 80   |               | dB              | DC variation due to AVDD supply changes                                                                                                       |

| AC Power Supply Rejection Ratio                                    | AC PSRR |      | 60   |               | dB              | AC 1 kHz, 50 mV peak-to-peak ripple applied to AVDD supply                                                                                    |

| Long-Term Stability                                                |         |      | 100  |               | ppm/<br>1000 hr |                                                                                                                                               |

| Parameter                                                      | Symbol | Min   | Тур  | Мах   | Unit   | Test Conditions/Comments                                                                                                                                                                                                                                      |

|----------------------------------------------------------------|--------|-------|------|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUFFERED REFERENCE VOLTAGE<br>OUTPUT                           |        |       | 1.82 |       | V      |                                                                                                                                                                                                                                                               |

| Accuracy                                                       |        |       |      | ±5    | mV     | $T_A = 25^{\circ}$ C, capacitive load to ground 100 pF                                                                                                                                                                                                        |

| Reference Temperature Coefficient <sup>1,5</sup>               |        | -20   |      | +20   | ppm/°C |                                                                                                                                                                                                                                                               |

| Output Impedance                                               |        |       | 0.5  | 1     | Ω      |                                                                                                                                                                                                                                                               |

| Load Current <sup>1</sup>                                      |        |       |      | 200   | μA     |                                                                                                                                                                                                                                                               |

| LOW POWER DAC SPECIFICATIONS<br>(VBIASx/VZEROx)                |        |       |      |       |        | VBIASx specifications derived from<br>measurements taken with potentiostat<br>amplifier in unity-gain mode and<br>measured at CE0 and CE1 pins, VZEROx<br>specifications derived from measurement<br>at VZERO0 and VZERO1 pins, dual output<br>low power DACs |

| Resolution <sup>1</sup>                                        |        | 12    |      |       | Bits   | 12-bit mode                                                                                                                                                                                                                                                   |