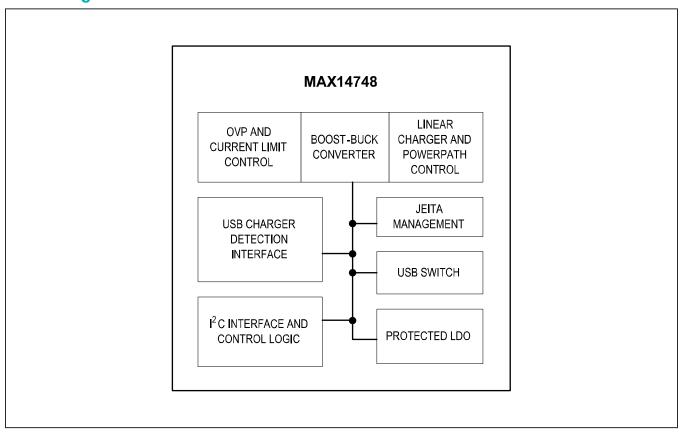

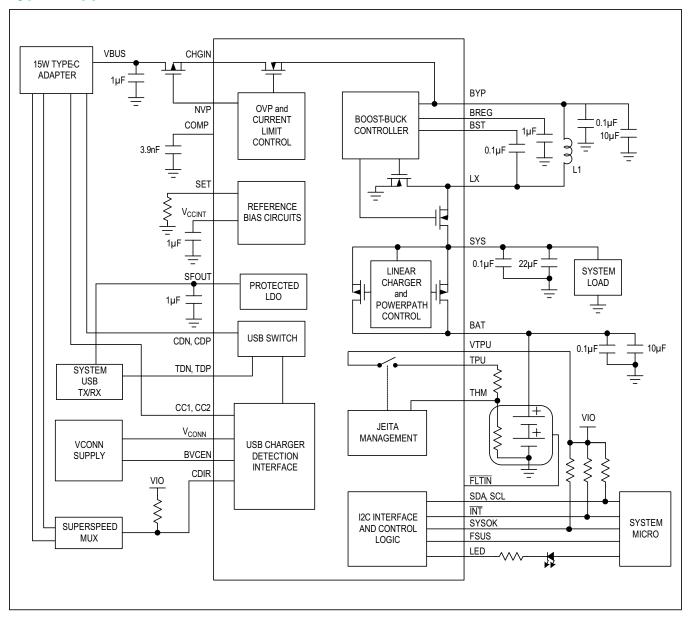

## **General Description**

The MAX14748 USB battery charger integrates a charger detector, boost/buck converter, and Li+ battery charger with smart power selector to provide fast and safe charging of 2s Li+ battery packs.

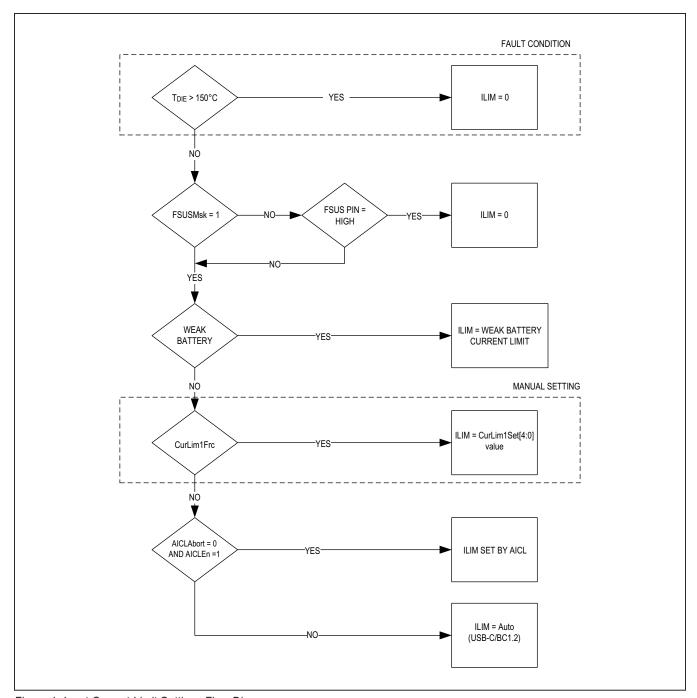

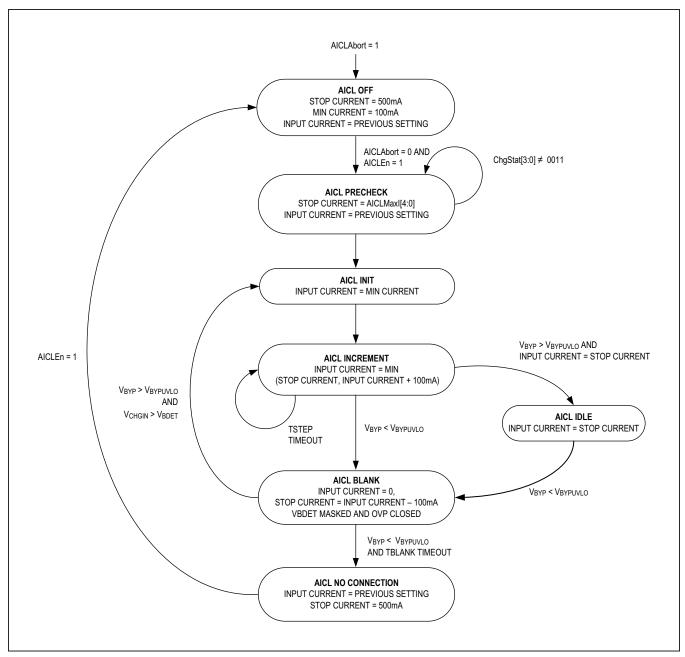

The MAX14748 provides support for devices functioning as a UFP/DRP per the USB Type-C 1.1 standard, while also providing detection of legacy USB Battery Charging Specification, Revision 1.2 (BC1.2) compliant chargers in addition to other nonstandard chargers. The programmable Automatic Input Current Limiting (AICL) feature ensures that maximum safe current is drawn from the charging adapter.

The Li+ charger includes an automatic Smart Power Selector™ to simultaneously charge the battery and provide power to the system load. The Smart Power Selector function will supplement the system power with the battery if power from the charging adapter is insufficient. The Li+ charger features JEITA thermal monitoring and charger voltage/current reduction or charger disable.

The MAX14748 is available in a 54-bump, 0.4mm pitch, 3.97mm x 2.77mm x 0.64mm wafer-level package (WLP) and operates over the -40°C to +85°C extended temperature range.

## **Applications**

- Digital Imaging (DSC, DVC)

- Wireless Speakers

- Handheld Barcode Readers

Ordering Information appears at end of data sheet.

## **Benefits and Features**

- Minimize Power Management Footprint Through High Integration

- 13mΩ (typ) Integrated Battery To System Switch

- · Thermal Current Limiting

- · DC-DC Converter with Boost and Reverse Buck

- · High Efficiency

- 92% in Boost Mode at 1A Output Current and 7.4V Battery Voltage

- 94% in Reverse Buck Mode at 500mA Output

- Internal USB Switch for USB D+/D- Data Lines

- Easy-to-Implement Li+ Battery Charging

- Charges 2s Li-lon Batteries from Legacy 5V USB Adapters

- 15W Input Power with 3A Type-C Adapter

- 7.5W Input Power with DCP Adapter

- 1A System/Charge Current From DCP Adapter

- 2A System/Charge Current From 3A Type-C Adapter

- DRP Mode USB Type-C Specification, Rev 1.1 Compliant

- UFP Mode USB Type-C Specification, Rev 1.1 Support

- V<sub>CONN</sub> and Super-Speed Multiplexer Logic Controls

- · Non-Standard DCP Detection

- · USB Battery Charging Specification, Rev 1.2 Compliant

- Automatic Input Current Limit (AICL) Power Management

- Support Weak/Dead Batteries Detection

- · Smart Power Selector

- Thermistor Monitor

- Various Protection Features

- · 28V Integrated Overvoltage Protection

- JEITA Charge Protection

- ±15kV ESD Protection on USB Adapter Pins

Smart Power Selector is a trademark of Maxim Integrated Products, Inc.

# **Absolute Maximum Ratings**

| Voltages Referenced to GND                                   |

|--------------------------------------------------------------|

| CHGIN0.3V to +30V                                            |

| BST0.3V to +16V                                              |

| SYS to BAT0.3V to +12V                                       |

| BAT, SYS0.3V to +12V                                         |

| BYP to CHGIN30V to +0.3V                                     |

| BYP, THM, INT, SYSOK, FLTIN, FSUS,                           |

| LED, SDA, SCL0.3V to 6V                                      |

| COMP, SET0.3V to V <sub>CCINT</sub> + 0.3V                   |

| CC1, CC2, TDN, TDP, CDN, CDP, V <sub>CONN</sub> 0.3V to +6V  |

| CC1, CC2, in fault mode through a 10k resistor0.3V to +20V   |

| CDIR0.3V to +6V                                              |

| VTPU (VTPU-TPU switch open)0.3V to V <sub>CCINT</sub> + 0.3V |

| TPU (VTPU-TPU switch open)0.3V to 6 or VTPU + 0.3V           |

| VTPU, TPU Maximum Current                                    |

| (VTPU-TPU switch closed)100mA to +100mA                      |

| BVCEN0.3V to V <sub>CCINT</sub> + 0.3V                       |

| SFOUT, V <sub>CCINT</sub> , BREG0.3V to min ((V <sub>CHGIN</sub> + 0<br>LX0.3V to V <sub>SYS</sub><br>NVP0.3V | s + 0.3V |

|---------------------------------------------------------------------------------------------------------------|----------|

| AGND, DGND, PGND, GND0.3V t                                                                                   | to +0.3V |

| Continuous Current into                                                                                       |          |

| CHGIN, SYS                                                                                                    | +6.4A    |

| BAT                                                                                                           | +4.8A    |

| Any Other Terminal                                                                                            |          |

| Continuous Power Dissipation                                                                                  |          |

| (multilayer board at +70°C): 9 x 6 Array 54-Bump,                                                             |          |

| 3.97mm x 2.77mm 0.4mm Pitch WLP                                                                               |          |

| (derate 24.46mW/°C)                                                                                           | 1.957W   |

| Operating Temperature Range40°C to                                                                            |          |

| Junction Temperature                                                                                          |          |

| Storage Temperature Range65°C to                                                                              |          |

| Lead Temperature (soldering, 10s)                                                                             | +300°C   |

| Soldering Temperature (reflow)                                                                                |          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

| PACKAGE TYPE: 54 WLP                   |                                |  |  |  |

|----------------------------------------|--------------------------------|--|--|--|

| Package Code                           | W151G2+1                       |  |  |  |

| Outline Number                         | 21-100122                      |  |  |  |

| Land Pattern Number                    | Refer to Application Note 1891 |  |  |  |

| THERMAL RESISTANC, FOUR-LAYER BOARD    |                                |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 40.88°C/W                      |  |  |  |

For the latest package outline information and land patterns (footprints), go to www.maximintegrated.com/packages. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

## **Electrical Characteristics**

$(V_{BAT} = 8.3V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ all registers in their default state, unless otherwise noted.}$  Typical values are at  $V_{CHGIN} = 5.0V, V_{BAT} = 7.4V, T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                                | SYMBOL                  | CONDITIONS                                                                                                                       | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| SUPPLY CURRENT                           |                         |                                                                                                                                  |      |      |      |       |

| BAT Supply Current                       | I <sub>BAT</sub>        | V <sub>CHGIN</sub> = 0V or Floating, Type-C detection active                                                                     |      | 140  |      | μА    |

| ,                                        | B/(I                    | Low Power mode                                                                                                                   |      | 25   |      | μA    |

|                                          |                         | V <sub>CHGIN</sub> = +5V, T <sub>A</sub> +25°C, ChgEn = 0                                                                        |      | 5.3  |      | mA    |

| CHGIN Supply Current                     | ICHG                    | V <sub>CHGIN</sub> = +5V, T <sub>A</sub> +25°C,<br>Suspend Mode (FSUS = High)                                                    |      | 0.98 |      | mA    |

| CHGIN TO BYP PATH                        |                         |                                                                                                                                  |      |      |      |       |

| Allowed CHGIN Input<br>Voltage Range     | V <sub>CHGIN_RNG</sub>  |                                                                                                                                  | 0    |      | 28   | V     |

| CHGIN Detect                             | V <sub>BDET</sub>       | Rising                                                                                                                           | 3.8  | 3.9  | 4.0  | V     |

| Threshold                                | V <sub>BDET_F</sub>     | Falling                                                                                                                          | 3.6  | 3.7  | 3.8  | ] v   |

|                                          | $V_{OVP}$               | Rising                                                                                                                           | 5.59 | 5.66 | 5.72 | V     |

| CHGIN Overvoltage Threshold              | V <sub>OVP_F</sub>      | Falling                                                                                                                          | 5.56 |      |      | V     |

| Timoonoid                                | V <sub>OVP_H</sub>      | Hysteresis                                                                                                                       |      | 28   |      | mV    |

| CHGIN-BYP Resistance                     | R <sub>CHGIN_BYP</sub>  | V <sub>CHGIN</sub> = 5V                                                                                                          |      | 45   |      | mΩ    |

| CHGIN-BYP Soft-Start<br>Timeout          | t <sub>BYP_SFTTO</sub>  | If V <sub>BYP</sub> has not reached within 50mV of V <sub>CHGIN</sub> at timeout, a fault is flagged by SysFlt of register 0x02. |      | 100  |      | ms    |

| CHGIN-BYP Soft-Start<br>Current          | I <sub>BYP_SFT</sub>    |                                                                                                                                  |      | 60   |      | mA    |

| CHGIN-BYP Soft-Start<br>End Comparator   | V <sub>BYP_SFTEND</sub> |                                                                                                                                  | 15   | 50   | 80   | mV    |

| CHGIN-BYP Overload<br>Comparator         | V <sub>BYP_OVL</sub>    |                                                                                                                                  | 290  | 360  | 420  | mV    |

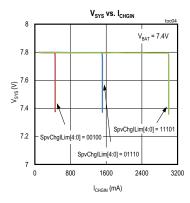

|                                          |                         | SpvChglLim[4:0] = 00100                                                                                                          |      | 0.4  |      |       |

| Input Current Limit                      | $I_{LIM}$               | SpvChglLim[4:0] = 01110                                                                                                          |      | 1.5  |      | Α     |

|                                          |                         | SpvChglLim[4:0] = 11101                                                                                                          |      | 3    |      |       |

| Input Current Limit<br>Programming Range | I <sub>LIM_RNG</sub>    |                                                                                                                                  | 0.1  |      | 3    | А     |

| Input Current Limit<br>Programming Step  | I <sub>LIM_STEP</sub>   |                                                                                                                                  |      | 100  |      | mA    |

| INTERNAL SUPPLIES                        |                         |                                                                                                                                  |      |      |      |       |

| Internal V <sub>CCINT</sub><br>Regulator | V <sub>CCINT</sub>      | V <sub>CHGIN</sub> = 5V, boost off                                                                                               | 4.0  | 4.3  | 4.6  | V     |

| Boost Regulator BREG                     | $V_{BREG}$              |                                                                                                                                  |      | 4.3  |      | V     |

| V <sub>CCINT</sub> UVLO                  |                         | V <sub>CCINT</sub> rising                                                                                                        | 3.1  | 3.4  | 3.7  |       |

| Threshold                                | V <sub>UVLO</sub>       | V <sub>CCINT</sub> falling                                                                                                       | 3.0  | 3.3  | 3.6  | V     |

$(V_{BAT} = 8.3V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ all registers in their default state, unless otherwise noted. Typical values are at <math>V_{CHGIN} = 5.0V, V_{BAT} = 7.4V, T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                                       | SYMBOL                  | CONDITIONS                                                          | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------------|-------------------------|---------------------------------------------------------------------|------|------|------|-------|

| V <sub>CCINT</sub> UVLO<br>Threshold Hysteresis | Vuvlo_HYS               | Hysteresis                                                          |      | 100  |      | mV    |

|                                                 |                         | SfOutLvI = 1, V <sub>CHGIN</sub> = 6V,<br>I <sub>SFOUT</sub> = 0    | 3.15 | 3.3  | 3.45 |       |

| SECULT L DO Voltago                             | W                       | SfOutLvI = 1, V <sub>CHGIN</sub> = 6V,<br>I <sub>SFOUT</sub> = 15mA |      | 2.95 |      | V     |

| SFOUT LDO Voltage                               | VsFout                  | SfOutLvI = 0, V <sub>CHGIN</sub> = 6V,<br>I <sub>SFOUT</sub> = 0    | 5.0  | 5.25 | 5.5  | V     |

|                                                 |                         | SfOutLvI = 0, VCHGIN = 6V,<br>I <sub>SFOUT</sub> = 15mA             |      | 4.9  |      |       |

| SFOUT Maximum<br>Current                        | I <sub>SFOUT_MAX</sub>  |                                                                     | 15   |      |      | mA    |

| Current Reduce<br>Temperature                   | T <sub>CHG_LIM</sub>    |                                                                     |      | 120  |      | °C    |

| Thermal Shutdown Temperature                    | T <sub>SHUTDOWN</sub>   |                                                                     |      | 150  |      | °C    |

| Thermal Shutdown<br>Hysteresis                  | T <sub>SHUTDOWN_H</sub> |                                                                     |      | 20   |      | °C    |

|                                                 |                         | BYPUVLO[2:0] = 000, V <sub>BYP</sub> falling                        |      | 3.8  |      |       |

|                                                 |                         | BYPUVLO[2:0] = 001, V <sub>BYP</sub> falling                        |      | 3.9  |      |       |

|                                                 | V <sub>BYPUVLO</sub>    | BYPUVLO[2:0] = 010, V <sub>BYP</sub> falling                        |      | 4.0  |      | - V   |

| BYP UVLO Threshold                              |                         | BYPUVLO[2:0] = 011, V <sub>BYP</sub> falling                        |      | 4.1  |      |       |

| BTT GVEG TIMEGRICIA                             |                         | BYPUVLO[2:0] = 100, V <sub>BYP</sub> falling                        |      | 4.2  |      |       |

|                                                 |                         | BYPUVLO[2:0] = 101, V <sub>BYP</sub> falling                        |      | 4.3  |      |       |

|                                                 |                         | BYPUVLO[2:0] = 110, V <sub>BYP</sub> falling                        |      | 4.4  |      |       |

|                                                 |                         | BYPUVLO[2:0] = 111, V <sub>BYP</sub> falling                        |      | 4.5  |      |       |

| BYP UVLO Threshold<br>Hysteresis                | V <sub>BYPUVLO_</sub> H |                                                                     |      | 25   |      | mV    |

|                                                 |                         | VPChg[2:0] = 000, V <sub>SYS</sub> rising                           |      | 5.9  |      |       |

|                                                 |                         | VPChg[2:0] = 001, V <sub>SYS</sub> rising                           |      | 6.0  |      |       |

|                                                 |                         | VPChg[2:0] = 010, V <sub>SYS</sub> rising                           |      | 6.1  |      |       |

| SYS UVLO (SYSOK)                                | V                       | VPChg[2:0] = 011, V <sub>SYS</sub> rising                           |      | 6.2  |      | V     |

| Threshold                                       | Vsysuvlo                | VPChg[2:0] = 100, V <sub>SYS</sub> rising                           |      | 6.3  |      | ) v   |

|                                                 |                         | VPChg[2:0] = 101, V <sub>SYS</sub> rising                           |      | 6.4  |      | -     |

|                                                 |                         | VPChg[2:0] = 110, V <sub>SYS</sub> rising                           |      | 6.5  |      |       |

|                                                 |                         | VPChg[2:0] = 111, V <sub>SYS</sub> rising                           |      | 6.6  |      |       |

| SYS UVLO Threshold<br>Hysteresis                | V <sub>SYSUVLO_</sub> H |                                                                     |      | 500  |      | mV    |

$(V_{BAT} = 8.3V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ all registers in their default state, unless otherwise noted.}$  Typical values are at  $V_{CHGIN} = 5.0V, V_{BAT} = 7.4V, T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                | SYMBOL                  | CONDIT                                                         | IONS                                 | MIN   | TYP  | MAX  | UNITS |

|--------------------------|-------------------------|----------------------------------------------------------------|--------------------------------------|-------|------|------|-------|

| BYP-SYS BOOST PATH       |                         | -                                                              |                                      | ,     |      |      | ,     |

| Switching Frequency      | f <sub>BST_SW</sub>     |                                                                |                                      |       | 0.8  |      | MHz   |

| Maximum Input Current    | I <sub>BST_MAX</sub>    | L = 2.2µH                                                      |                                      | 3     |      |      | Α     |

| Input Peak Current Limit | I <sub>BST_LIM_PK</sub> |                                                                |                                      |       | 4.5  |      | Α     |

|                          |                         |                                                                | 00000                                |       | 100  |      |       |

|                          |                         |                                                                | 00001                                |       | 200  |      |       |

|                          |                         |                                                                | 00010                                |       | 300  |      |       |

|                          |                         |                                                                | 00011                                |       | 400  |      |       |

|                          |                         |                                                                | 00100                                | 405   | 450  | 495  |       |

|                          |                         |                                                                | 00101                                |       | 600  |      |       |

|                          |                         |                                                                | 00110                                |       | 700  |      |       |

|                          |                         |                                                                | 00111                                |       | 800  |      |       |

|                          |                         |                                                                | 01000                                |       | 900  |      |       |

|                          |                         |                                                                | 01001                                |       | 1000 |      |       |

|                          |                         |                                                                | 01010                                |       | 1100 |      |       |

|                          |                         |                                                                | 01011                                |       | 1200 |      |       |

|                          | IILIM_F                 | CurLim1Frc = 1,                                                | 01100                                |       | 1300 |      |       |

|                          |                         |                                                                | 01101                                |       | 1400 |      |       |

|                          |                         |                                                                | 01110                                |       | 1500 |      |       |

| Forced Input Current     |                         |                                                                | 01111                                |       | 1600 |      | mA    |

| Limit                    |                         | IILIM_F                                                        | CurLim1Set[4:0] =                    | 10000 |      | 1700 |       |

|                          |                         |                                                                | 10001                                |       | 1800 |      |       |

|                          |                         |                                                                | 10010                                |       | 1900 |      |       |

|                          |                         |                                                                | 10011                                |       | 2000 |      |       |

|                          |                         |                                                                | 10100                                |       | 2100 |      |       |

|                          |                         |                                                                | 10101                                |       | 2200 |      |       |

|                          |                         |                                                                | 10110                                |       | 2300 |      |       |

|                          |                         |                                                                | 10111                                |       | 2400 |      |       |

|                          |                         |                                                                | 11000                                |       | 2500 |      |       |

|                          |                         |                                                                | 11001                                |       | 2600 |      |       |

|                          |                         |                                                                | 11010                                |       | 2700 |      |       |

|                          |                         |                                                                | 11011                                |       | 2800 |      |       |

|                          |                         |                                                                | 11100                                |       | 2900 |      |       |

|                          |                         |                                                                | 11101                                |       | 3000 |      |       |

|                          |                         |                                                                | 11110                                |       | 3100 |      |       |

|                          |                         |                                                                | 11111                                |       | 3200 |      |       |

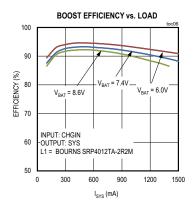

| Efficiency               | EFF <sub>BST</sub>      | I <sub>SYS</sub> = 1000mA, V <sub>E</sub><br>L1 = Bourns SRP40 | <sub>BAT</sub> = 7.4V,<br>012TA-2R2M |       | 91.6 |      | %     |

$(V_{BAT} = 8.3V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ all registers in their default state, unless otherwise noted.}$  Typical values are at  $V_{CHGIN} = 5.0V, V_{BAT} = 7.4V, T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                                   | SYMBOL                   | CONDITIONS                                                                          | MIN  | TYP                        | MAX  | UNITS  |

|---------------------------------------------|--------------------------|-------------------------------------------------------------------------------------|------|----------------------------|------|--------|

| CVC D                                       | \/                       | Charger disabled                                                                    |      | V <sub>BAT</sub> + 0.4     |      | V      |

| SYS Regulation Voltage                      | V <sub>SYS_REG</sub>     | Charger in precharge, V <sub>BAT</sub> = 5V                                         | V    | / <sub>PCHG</sub> + 0.4    |      | V      |

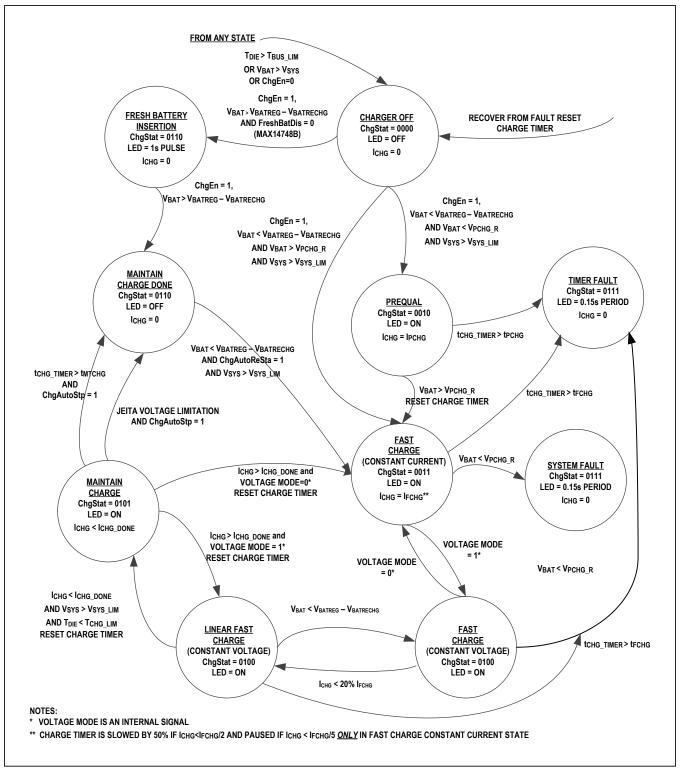

| SYS Regulation Voltage<br>Limit             | V <sub>SYS_LIM</sub>     | See Battery Charger State Diagram                                                   |      | V <sub>SYS_REG</sub> - 0.2 |      | V      |

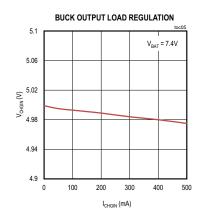

| BYP-SYS BUCK PATH                           |                          |                                                                                     | '    |                            |      | ,      |

| Switching Frequency                         | f <sub>BK_SW</sub>       |                                                                                     |      | 0.8                        |      | MHz    |

| Maximum Output<br>Current                   | I <sub>BK_MAX</sub>      | L = 2.2µH                                                                           | 500  |                            |      | mA     |

| Short-Circuit Peak<br>Current Limit         | I <sub>BK_LIM</sub>      |                                                                                     |      | 1.3                        |      | А      |

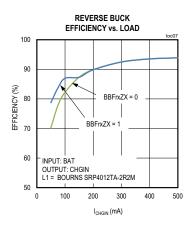

| Efficiency                                  | EFF <sub>BK</sub>        | I <sub>CHGIN</sub> = 500mA , V <sub>BAT</sub> = 7.4V,<br>L1 = Bourns SRP4012TA-2R2M |      | 94                         |      | %      |

| Output Voltage Range                        | V <sub>BK_OUT_RNG</sub>  |                                                                                     | 4    |                            | 5.5  | V      |

| Output Accuracy                             | V <sub>BK_OUT_ACC</sub>  |                                                                                     | -1.5 |                            | +1.5 | %      |

| SYS-BAT CHARGER/SWI                         | TCH CONTROLLER           |                                                                                     |      |                            |      |        |

| BAT-to-SYS Regulation                       | V <sub>BAT-SYS_ON</sub>  | MAX14748                                                                            |      | -20                        |      | mV     |

| Voltage                                     | *BAI-512_ON              | MAX14748B                                                                           |      | -40                        |      | 1111   |

| BAT-to-SYS Switch Fast<br>Turn-On Threshold | V <sub>BAT-SYS_OFF</sub> | V <sub>SYS</sub> falling                                                            |      | -100                       |      | mV     |

| BAT-to-SYS Switch<br>On-Resistance          | R <sub>BAT_SYS</sub>     | I <sub>BAT</sub> = 1A                                                               |      | 13                         |      | mΩ     |

| Charger Current<br>Soft-Start Time          | <sup>t</sup> CHG_SOFT    |                                                                                     |      | 1                          |      | ms     |

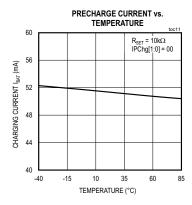

| PRECHARGE                                   |                          |                                                                                     |      |                            |      |        |

|                                             |                          | IPChg[1:0] = 00                                                                     |      | 5                          |      |        |

| Dracharge Current                           | I                        | IPChg[1:0] = 01                                                                     |      | 10                         |      | 0/1    |

| Precharge Current                           | I <sub>PCHG</sub>        | IPChg[1:0] = 10                                                                     |      | 20                         |      | %lFCHG |

|                                             |                          | IPChg[1:0] = 11, $R_{SET}$ = 20kΩ                                                   | 27   | 30                         | 33   |        |

|                                             |                          | VPChg[2:0] = 000                                                                    |      | 5.7                        |      |        |

|                                             |                          | VPChg[2:0] = 001                                                                    |      | 5.8                        |      |        |

|                                             |                          | VPChg[2:0] = 010                                                                    |      | 5.9                        |      |        |

| Prequalification                            | V                        | VPChg[2:0] = 011                                                                    |      | 6.0                        |      | V      |

| Threshold                                   | V <sub>PCHG</sub>        | VPChg[2:0] = 100                                                                    | 6.1  |                            |      | ] V    |

|                                             |                          | VPChg[2:0] = 101                                                                    |      | 6.2                        |      | ]      |

|                                             |                          | VPChg[2:0] = 110                                                                    |      | 6.3                        |      |        |

|                                             |                          | VPChg[2:0] = 111                                                                    |      | 6.4                        |      |        |

| Prequalification<br>Threshold Hysteresis    | V <sub>PCHG_H</sub>      |                                                                                     |      | 100                        |      | mV     |

$(V_{BAT} = 8.3V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ all registers in their default state, unless otherwise noted.}$  Typical values are at  $V_{CHGIN} = 5.0V, V_{BAT} = 7.4V, T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                                       | SYMBOL                | CONDITIONS                                           | MIN   | TYP   | MAX   | UNITS              |

|-------------------------------------------------|-----------------------|------------------------------------------------------|-------|-------|-------|--------------------|

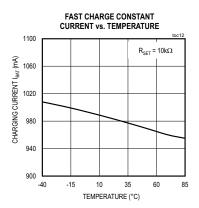

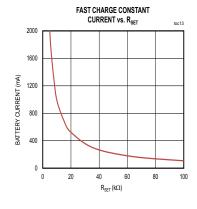

| FAST CHARGE                                     |                       | ,                                                    | '     |       |       | '                  |

| SET Current Gain Factor                         | K <sub>SET</sub>      |                                                      |       | 10000 |       | A/A                |

| SET Regulation Voltage                          | V <sub>SET</sub>      |                                                      |       | 1     |       | V                  |

|                                                 |                       | R <sub>SET</sub> = 20kΩ                              | 0.43  | 0.5   | 0.57  |                    |

| F. 101 0 1                                      |                       | R <sub>SET</sub> = 20kΩ, T = 25°C                    | 0.475 | 0.5   | 0.525 | 1                  |

| Fast-Charge Current                             | I <sub>FCHG</sub>     | R <sub>SET</sub> = 10kΩ                              |       | 1     |       | - A                |

|                                                 |                       | $R_{SET} = 4k\Omega$                                 |       | 2.5   |       |                    |

|                                                 |                       | T_T_IFChg[2:0] = 000                                 |       | 20    |       |                    |

|                                                 |                       | T_T_IFChg[2:0] = 001                                 |       | 30    |       |                    |

|                                                 |                       | T_T_IFChg[2:0] = 002                                 |       | 40    |       |                    |

| Fast-Charge Current                             | 1                     | T_T_IFChg[2:0] = 003                                 |       | 50    |       | 0/1                |

| Scaling                                         | <sup>I</sup> FCHG_T   | T_T_IFChg[2:0] = 004                                 |       | 60    |       | %I <sub>FCHG</sub> |

|                                                 |                       | T_T_IFChg[2:0] = 005                                 |       | 70    |       |                    |

|                                                 |                       | T_T_IFChg[2:0] = 006                                 |       | 80    |       |                    |

|                                                 |                       | T_T_IFChg[2:0] = 007                                 |       | 100   |       |                    |

| 1/2 Fast-Charge Current<br>Comparator Threshold | I <sub>FC_HALF</sub>  |                                                      |       | 50    |       | %I <sub>FCHG</sub> |

| 1/5 Fast-Charge Current<br>Comparator Threshold | I <sub>FC_FIFTH</sub> |                                                      |       | 20    |       | %I <sub>FCHG</sub> |

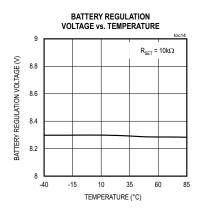

| MAINTAIN CHARGE                                 |                       |                                                      |       |       |       |                    |

|                                                 |                       | ChgDone[1:0] = 00                                    |       | 5     |       |                    |

| Charge Done Qualification                       | I <sub>CHG_DONE</sub> | ChgDone[1:0] = 01                                    |       | 10    |       | %I <sub>FCHG</sub> |

|                                                 |                       | ChgDone[1:0] = 10, $R_{SET}$ = 20k $\Omega$          | 18    | 20    | 22    |                    |

|                                                 |                       | BatReg[1:0] = 00, T <sub>A</sub> = +25°C             | 8.258 | 8.3   | 8.342 |                    |

|                                                 |                       | BatReg[1:0] = 00,<br>T <sub>A</sub> = -40°C to +85°C | 8.217 | 8.3   | 8.383 |                    |

| BAT Regulation Voltage                          | $V_{BATREG}$          | BatReg[1:0] = 01                                     |       | 8.4   |       | V                  |

|                                                 |                       | BatReg[1:0] = 10                                     |       | 8.5   |       |                    |

|                                                 |                       | BatReg[1:0] = 11                                     |       | 8.6   |       |                    |

|                                                 |                       | BatReChg[1:0] = 00                                   |       | 200   |       |                    |

| BAT Recharge                                    | V                     | BatReChg[1:0] = 01                                   |       | 300   |       | w-\/               |

| Threshold                                       | VBATRECHG             | BatReChg[1:0] = 10                                   |       | 400   |       | mV                 |

|                                                 |                       | BatReChg[1:0] = 11                                   |       | 500   |       |                    |

|                                                 |                       |                                                      |       |       |       |                    |

$(V_{BAT} = 8.3V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ all registers in their default state, unless otherwise noted.}$  Typical values are at  $V_{CHGIN} = 5.0V, V_{BAT} = 7.4V, T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                      | SYMBOL                  | CONDITIONS                                                                                                                                                         | MIN  | TYP  | MAX  | UNITS             |

|--------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------------------|

| CHARGE TIMER                   |                         |                                                                                                                                                                    |      |      |      |                   |

|                                |                         | PChgTmr[1:0] =00                                                                                                                                                   |      | 30   |      |                   |

| Maximum                        |                         | PChgTmr[1:0] = 01                                                                                                                                                  |      | 60   |      | 1 .               |

| Prequalification Time          | <sup>t</sup> PCHG       | PChgTmr[1:0] = 10                                                                                                                                                  |      | 120  |      | - min             |

|                                |                         | PChgTmr[1:0] = 11                                                                                                                                                  |      | 240  |      | 1                 |

|                                |                         | FChgTmr[1:0] = 00                                                                                                                                                  |      | 75   |      |                   |

| Maximum Fast-Charge            |                         | FChgTmr[1:0] = 01                                                                                                                                                  |      | 150  |      | 1                 |

| Time                           | <sup>t</sup> FCHG       | FChgTmr[1:0] = 10                                                                                                                                                  |      | 300  |      | Min               |

|                                |                         | FChgTmr[1:0] = 11                                                                                                                                                  |      | 600  |      | 1                 |

|                                |                         | MtChgTmr[1:0] = 00                                                                                                                                                 |      | 0    |      |                   |

|                                |                         | MtChgTmr[1:0] = 01                                                                                                                                                 |      | 15   |      | 1                 |

| Maintain Charge Time           | <sup>t</sup> TOCHG      | MtChgTmr[1:0] = 10                                                                                                                                                 |      | 30   |      | - Min             |

|                                |                         | MtChgTmr[1:0] = 11                                                                                                                                                 |      | 60   |      |                   |

| Timer Accuracy                 | t <sub>ACC</sub>        |                                                                                                                                                                    | -10  |      | +10  | %                 |

| Timer Extend Threshold         | P <sub>TIMERX</sub>     | If charge current is reduced due to I <sub>LIM</sub> or T <sub>DIE</sub> , this is the percentage of charge current below which timer clock operates at half speed |      | 50   |      | %                 |

| Timer Suspend<br>Threshold     | PTIMERSUS               | If charge current is reduced due to I <sub>LIM</sub> or T <sub>DIE</sub> , this is the percentage of charge current below which timer clock pauses                 |      | 20   |      | %                 |

| THERMISTOR MONITOR             | AND NTC DETECTION       | DN                                                                                                                                                                 |      |      |      |                   |

| THM Hot Threshold              | T4                      | V <sub>THM</sub> falling, WarmCoolSel = 0                                                                                                                          | 21.3 | 23.3 | 25.3 | %V <sub>TPU</sub> |

| Trim riot ringenera            |                         | V <sub>THM</sub> falling, WarmCoolSel = 1                                                                                                                          | 30.9 | 32.9 | 34.9 | 701110            |

| THM Warm Threshold             | Т3                      | V <sub>THM</sub> falling, WarmCoolSel = 0                                                                                                                          | 30.9 | 32.9 | 34.9 | %V <sub>TPU</sub> |

| Triwi vvaim miconola           |                         | V <sub>THM</sub> falling, WarmCoolSel = 1                                                                                                                          | 46.5 | 50   | 53.5 | 70 1 1 1 0        |

| THM Cool Threshold             | T2                      | V <sub>THM</sub> rising, WarmCoolSel = 0 or 1                                                                                                                      | 62.5 | 64.5 | 66.5 | %V <sub>TPU</sub> |

| THM Cold Threshold             | T1                      | V <sub>THM</sub> rising, WarmCoolSel = 0 or 1                                                                                                                      | 71.9 | 73.9 | 75.9 | %V <sub>TPU</sub> |

| THM Disable Threshold          | V <sub>THM_DIS</sub>    | V <sub>THM</sub> rising                                                                                                                                            | 91.0 | 93.0 | 95.0 | %V <sub>TPU</sub> |

| THM Threshold Hysteresis       | V <sub>THM_DIS_H</sub>  |                                                                                                                                                                    |      | 60   |      | mV                |

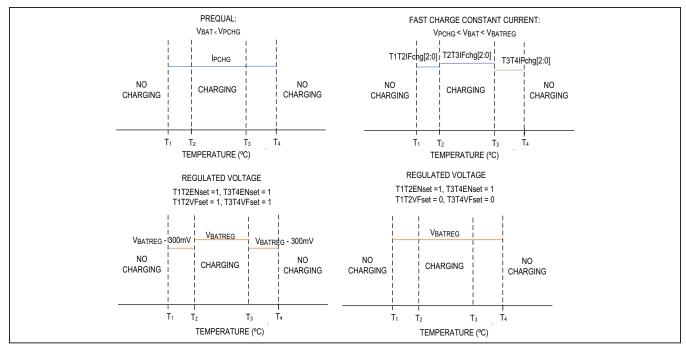

| JEITA BAT Voltage<br>Reduction | V <sub>BAT</sub> _JEITA |                                                                                                                                                                    |      | 300  |      | mV                |

| THM Input Leakage              | ITHM_LK                 |                                                                                                                                                                    | -1   |      | +1   | μA                |

| THM Detection Time             | t <sub>THM_DET</sub>    |                                                                                                                                                                    |      | 0.4  |      | ms                |

$(V_{BAT} = 8.3V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ all registers in their default state, unless otherwise noted.}$  Typical values are at  $V_{CHGIN} = 5.0V, V_{BAT} = 7.4V, T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                                              | SYMBOL                                     | CONDITIONS                                 | MIN  | TYP  | MAX | UNITS |

|--------------------------------------------------------|--------------------------------------------|--------------------------------------------|------|------|-----|-------|

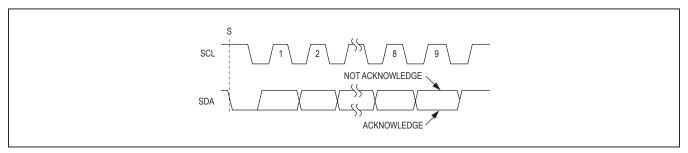

| DIGITAL I/O (SDA, SCL,                                 | FLTIN, INT, SYSOK, F                       | SUS, LED, CDIR)                            |      |      |     |       |

| Leakage Current                                        | I <sub>IO_LK</sub>                         |                                            | -1   |      | +1  | μA    |

| Logic Input High-Voltage                               | V <sub>IO_IH</sub>                         |                                            | 1.4  |      |     | V     |

| Logic Input Low-Voltage                                | V <sub>IO_IL</sub>                         |                                            |      |      | 0.5 | V     |

| Logic Output Low-Voltage                               | V <sub>IO_OL</sub>                         | I <sub>OL</sub> = 4mA                      |      |      | 0.4 | V     |

| FSUS Input Pulldown<br>Resistance                      | R <sub>FSUS_PD</sub>                       |                                            |      | 470  |     | kΩ    |

| SDA, SCL Bus<br>Low-Detection Current                  | I <sub>PD</sub>                            | V <sub>SDA</sub> = V <sub>SCL</sub> = 0.4V |      | 0.2  | 0.4 | μA    |

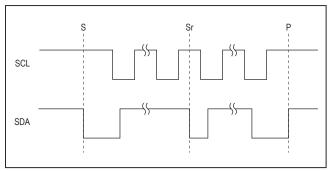

| SCL Clock Frequency                                    | fscL                                       | Note 2                                     | 0    |      | 400 | kHz   |

| Bus Free Time Between<br>a STOP and START<br>Condition | <sup>t</sup> BUF                           |                                            | 1.3  |      |     | μs    |

| START Condition<br>(Repeated) Hold Time                | t <sub>HD_SDA</sub>                        | Note 2                                     | 0.6  |      |     | μs    |

| Low Period of SCL<br>Clock                             | t <sub>LOW</sub>                           |                                            | 1.3  |      |     | μs    |

| High Period of SCL<br>Clock                            | <sup>t</sup> HIGH                          |                                            | 0.6  |      |     | μs    |

| Setup Time for a<br>Repeated START<br>Condition        | <sup>t</sup> su_sta                        |                                            | 0.6  |      |     | μs    |

| Data Hold Time                                         | t <sub>HD_DAT</sub>                        | Note 3                                     | 0    |      | 0.9 | μs    |

| Data Setup Time                                        | t <sub>SU_DAT</sub>                        | Note 3                                     | 100  |      |     | ns    |

| Setup Time for STOP<br>Condition                       | tsu_sto                                    |                                            | 0.6  |      |     | μs    |

| Spike Pulse Widths<br>Suppressed by Input<br>Filter    | tsp                                        | Note 4                                     |      | 50   |     | ns    |

| BC1.2 DETECTION                                        |                                            |                                            |      |      |     |       |

| V <sub>DP_SRC</sub> Voltage                            | V <sub>DP_SRC</sub> /V <sub>SRC06</sub>    | I <sub>LOAD</sub> = 0 to 200μA             | 0.5  | 0.6  | 0.7 | V     |

| V <sub>DM_SRC</sub> Voltage                            | V <sub>DM_SRC</sub> /V <sub>SRC06</sub>    | I <sub>LOAD</sub> = 0 to 200μA             | 0.5  | 0.6  | 0.7 | V     |

| V <sub>D33</sub> Voltage                               | V <sub>SRC33</sub>                         | I <sub>LOAD</sub> = 0 to 365μA             | 2.6  |      | 3.4 | V     |

| V <sub>DAT_REF</sub> Voltage                           | V <sub>DAT_REF</sub>                       |                                            | 0.25 | 0.32 | 0.4 | V     |

| V <sub>LGC</sub> Voltage                               | $V_{LGC}$                                  |                                            | 1.5  | 1.7  | 1.9 | V     |

| I <sub>DM_SINK</sub> Current                           | I <sub>DM_SINK</sub> /I <sub>DATSINK</sub> | 0.15V to 3.6V                              | 55   | 80   | 105 | μΑ    |

| I <sub>DP SRC</sub> Current                            | I <sub>DP_SRC</sub> /I <sub>DCD</sub>      | 0V to 2.5V                                 | 7    | 10   | 13  | μA    |

$(V_{BAT} = 8.3V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ all registers in their default state, unless otherwise noted. Typical values are at <math>V_{CHGIN} = 5.0V, V_{BAT} = 7.4V, T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                                    | SYMBOL                                  | CONDITIONS                                                                                    | MIN   | TYP | MAX   | UNITS |

|----------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------|-------|-----|-------|-------|

| R <sub>DM_DWN</sub> Resistor                 | R <sub>DM_DWN</sub> /R <sub>DWN15</sub> |                                                                                               | 12    | 20  | 24    | kΩ    |

| I <sub>WEAK</sub> Current                    | I <sub>WEAK</sub>                       |                                                                                               | 0.01  | 0.1 | 0.5   | μΑ    |

| V <sub>BUS31</sub> Threshold                 | V <sub>BUS31</sub>                      | DP and DN pins. Threshold in percent of V <sub>BUS</sub> voltage 4V < V <sub>BUS</sub> < 5.5V | 26    | 31  | 36    | %     |

| V <sub>BUS47</sub> Threshold                 | V <sub>BUS47</sub>                      | DP and DN pins. Threshold in percent of V <sub>BUS</sub> voltage 4V < V <sub>BUS</sub> < 5.5V | 43.3  | 47  | 51.7  | %     |

| V <sub>BUS64</sub> Threshold                 | V <sub>BUS64</sub>                      | DP and DN pins. Threshold in percent of V <sub>BUS</sub> voltage 4V < V <sub>BUS</sub> < 5.5V | 57    | 64  | 71    | %     |

| Charger Detection<br>Debounce                | tCDDEB                                  |                                                                                               | 45    | 50  | 55    | ms    |

| Primary-to-Secondary<br>Timer                | <sup>t</sup> PDSDWAIT                   |                                                                                               | 27    | 35  | 39    | ms    |

| Proprietary Charger<br>Debounce              | t <sub>PRDEB</sub>                      |                                                                                               | 5     | 7.5 | 10    | ms    |

| Data Contact Detect                          |                                         | DCD2s = 0                                                                                     | 700   | 800 | 900   |       |

| Timeout                                      | <sup>t</sup> DCDTMO                     | DCD2s = 1                                                                                     | 1.8   | 2.0 | 2.2   | ms    |

| DP/DN Overvoltage<br>Debounce                | t <sub>OVDXDEB</sub>                    |                                                                                               | 90    | 100 | 110   | μs    |

| OVDX Comparator                              | OVDY                                    | Rising                                                                                        | 0     |     | 0.15  | V     |

| OVDA Comparator                              | OVDX <sub>THRESHOLD</sub>               | Falling                                                                                       | -0.04 |     | +0.08 | V     |

| CDP/CDN Pulldown<br>Resistor                 | R <sub>CDP/CDN_PD</sub>                 |                                                                                               | 3     | 6   | 12    | mΩ    |

| TYPE-C DETECTION                             |                                         |                                                                                               |       |     |       |       |

| V <sub>CONN</sub> Switch Voltage<br>Drop     | V <sub>CONN_REQ</sub>                   | V <sub>CONN</sub> = 5.5V, I <sub>CC_LOAD</sub> = 20mA                                         | 5.5   |     | 5.6   | V     |

| V <sub>CONN</sub> Bulk Capacitance           | C <sub>VCONN</sub>                      |                                                                                               | 10    |     | 220   | μF    |

| CC Pin Operational<br>Voltage Range          | V <sub>CONN_RNG</sub>                   |                                                                                               |       |     | 5.5   | V     |

| CC Pin Voltage in DFP 3.0A Mode              | V <sub>CC_PIN30</sub>                   |                                                                                               | 3.1   |     |       | V     |

| CC Pin Voltage in DFP<br>1.5A Mode           | V <sub>CC_PIN15</sub>                   |                                                                                               | 1.85  |     |       | V     |

| CC Pin Low-Power Mode<br>Pulldown Resistance | R <sub>LPPD_CC</sub> _                  |                                                                                               |       | 170 |       | kΩ    |

$(V_{BAT} = 8.3V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ all registers in their default state, unless otherwise noted.}$  Typical values are at  $V_{CHGIN} = 5.0V, V_{BAT} = 7.4V, T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                                  | SYMBOL                    | CONDITIONS                                                                                | MIN   | TYP   | MAX   | UNITS |

|--------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| CC Pin Low-Power Mode<br>Voltage Threshold | V <sub>LP_CC</sub> _      | Rising                                                                                    |       | 0.7   |       | V     |

| CC Pin Clamp<br>Requirements               | VCC_PIN_CLAMP             | 60μA ≤ I <sub>CC</sub> _≤ 600μA                                                           |       | 1.1   | 1.32  | V     |

| CC UFP Pulldown<br>Resistance              | R <sub>DUFP_CC_</sub>     |                                                                                           | 4.59  | 5.1   | 5.61  | kΩ    |

| CC DFP 0.5A Current<br>Source              | I <sub>DFP0.5</sub> _CC_  |                                                                                           | 72    | 80    | 88    | μA    |

| CC DFP 1.5A Current<br>Source              | I <sub>DFP1.5_CC_</sub>   |                                                                                           | 165.6 | 180   | 194.4 | μA    |

| CC DFP 3.0A Current<br>Source              | I <sub>DFP3.0_CC</sub> _  |                                                                                           | 303.6 | 330   | 356.4 | μA    |

| CC R <sub>A</sub> and R <sub>D</sub>       | V                         | Rising                                                                                    | 0.16  | 0.2   | 0.25  | V     |

| Threshold                                  | V <sub>RA_RD0.5</sub>     | Falling                                                                                   | 0.15  |       |       |       |

| CC UFP 0.5A R <sub>D</sub>                 | V                         | Rising                                                                                    | 0.62  | 0.66  | 0.7   | V     |

| Threshold                                  | V <sub>UFP_RD0.5</sub>    | Falling                                                                                   | 0.61  |       |       |       |

| CC UFP 1.5A R <sub>D</sub>                 |                           | Rising                                                                                    | 1.17  | 1.23  | 1.31  | 1 V   |

| Threshold                                  | V <sub>UFP_RD1.5</sub>    | Falling                                                                                   | 1.16  |       |       |       |

| CC V <sub>CONN</sub> Detect                | .,                        | Rising                                                                                    | 2.11  | 2.25  | 2.4   | V     |

| Threshold                                  | VVCONN_DET                | Falling                                                                                   | 2.1   |       |       |       |

| CC DFP V <sub>OPEN</sub> Detect            | \/                        | Rising                                                                                    | 1.51  | 1.575 | 1.65  | V     |

| Threshold                                  | V <sub>DFP_</sub> VOPEN   | Falling                                                                                   | 1.5   |       |       | ]     |

| CC DFP V <sub>OPEN</sub> with              | V                         | Rising                                                                                    | 2.46  | 2.6   | 2.75  | V     |

| 3.0A Detect Threshold                      | V <sub>DFP_</sub> VOPEN3A | Falling                                                                                   | 2.45  |       |       | V     |

| V <sub>BUS</sub> Valid                     | $V_{BDET}$                | Rising                                                                                    | 3.8   | 4.12  | 4.4   | V     |

| V <sub>BUS</sub> Valid Hysteresis          | V <sub>BDET_H</sub>       | Falling hysteresis                                                                        |       | 0.7   |       | V     |

| V <sub>BUS</sub> Discharge Value           | V <sub>SAFE0V</sub>       | Falling. Voltage level where a connected UFP will find V <sub>BUS</sub> removed.          | 0.6   | 0.7   | 0.84  | V     |

|                                            |                           | Rising hysteresis                                                                         |       | 100   |       | mV    |

| CC Pin Power-Up Time                       | <sup>t</sup> CLAMPSWAP    | The maximum time allowed from removal of voltage clamp to attachment of the 5.1k resistor |       |       | 15    | ms    |

| Type-C CC Pin<br>Detection Debounce        | tCCDEB                    |                                                                                           | 100   |       | 200   | ms    |

| Type-C Debounce                            | t <sub>PDDEB</sub>        |                                                                                           | 10    |       | 20    | ms    |

$(V_{BAT} = 8.3V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ all registers in their default state, unless otherwise noted. Typical values are at <math>V_{CHGIN} = 5.0V, T_{CHGIN} = 5.0V$  $V_{BAT} = 7.4V, T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                      | SYMBOL                     | CONDITIONS                                                                                           | MIN             | TYP | MAX | UNITS |

|--------------------------------|----------------------------|------------------------------------------------------------------------------------------------------|-----------------|-----|-----|-------|

| Type-C Quick Debounce          | t <sub>QDEB</sub>          |                                                                                                      | 0.9             | 1   | 1.9 | ms    |

| V <sub>BUS</sub> Debounce      | t <sub>VBDEB</sub>         |                                                                                                      | 9               | 10  | 11  | ms    |

| V <sub>SAFE0V</sub> Debounce   | t <sub>VSAFE0VDEB</sub>    |                                                                                                      | 9               | 10  | 11  | ms    |

| Type-C Error Recovery<br>Delay | <sup>t</sup> ERRORRECOVERY |                                                                                                      | 25              |     |     | ms    |

| Type-C DRP Toggle<br>Time      | t <sub>DRP</sub>           |                                                                                                      | 50              |     | 100 | ms    |

| Duty Cycle of DRP<br>Swap      | D <sub>DRP</sub>           | Duty cycle of UFP to DFP role swap                                                                   | 30              |     | 70  | %     |

| DRP Transition Time            | <sup>t</sup> DRPTRAN       | Time a role swap from DFP to UFP or reverse is completed                                             |                 |     | 1   | ms    |

| DRP Lock Time                  | <sup>t</sup> DRPLOCK       | DRP Lock wait time before transition to unattached state                                             | 100             |     | 150 | ms    |

| V <sub>CONN</sub> Enable Time  | <sup>t</sup> /CONNON       | Time from when V <sub>BUS</sub> is supplied in DFP mode in state Attach.DFP. DRPWait                 |                 |     | 10  | ms    |

| V <sub>CONN</sub> Disable Time | <sup>t</sup> /CONNOFF      | Time from UFP detached or as directed by I <sup>2</sup> C command until V <sub>CONN</sub> is removed |                 |     | 35  | ms    |

| CC Pin Current Change<br>Time  | <sup>†</sup> SINKADJ       | Time from CC pin changes state in UFP mode until current drawn from DFP reaches new value            |                 |     | 60  | ms    |

| V <sub>BUS</sub> On-Time       | <sup>t</sup> VBUSON        | Time from UFP is attached until V <sub>BUS</sub> On                                                  |                 |     | 275 | ms    |

| V <sub>BUS</sub> Off-Time      | <sup>t</sup> VBUSOFF       | Time from UFP is detached until V <sub>BUS</sub> reaches V <sub>SAFE0V</sub>                         |                 |     | 650 | ms    |

| BVCEN Output<br>Low-Voltage    | V <sub>BVCEN_OL</sub>      | I <sub>SINK</sub> = 1mA                                                                              |                 |     | 0.4 | V     |

| BVCEN Output<br>High-Voltage   | V <sub>BVCEN_</sub> OH     | I <sub>SOURCE</sub> = 1mA                                                                            | VCCINT<br>- 0.4 |     |     | V     |

- Note 1: All devices are 100% production tested at  $T_A = +25$ °C. Limits over the operating temperature range are guaranteed by design and characterization.

- Note 2:  $f_{SCL}$  must meet the minimum clock low time plus the rise/fall times.

- Note 3: The maximum  $t_{\text{HD:DAT}}$  has to be met only if the device does not stretch the low period ( $t_{\text{LOW}}$ ) of the SCL signal. Note 4: Filters on SDA and SCL suppress noise spikes at the input buffers and delay the sampling instant.

Maxim Integrated | 12 www.maximintegrated.com

## MAX14748

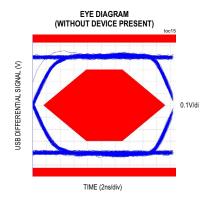

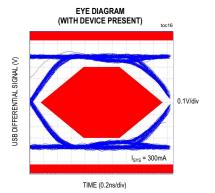

# **Typical Operating Characteristics**

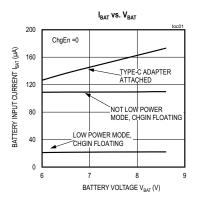

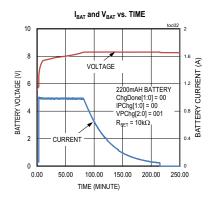

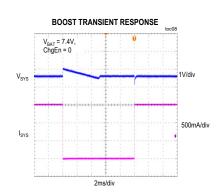

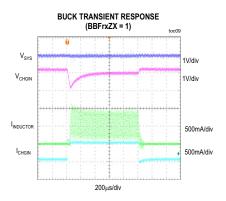

$(V_{BAT} = 8.5V, T_A = -20^{\circ}C \text{ to } +70^{\circ}C, \text{ all registers in their default state, unless otherwise noted. Typical values are at <math>V_{CHGIN} = 5.0V, V_{BAT} = 7.4V, T_A = +25^{\circ}C.)$

# **Typical Operating Characteristics (continued)**

$(V_{BAT} = 8.5V, T_A = -20^{\circ}C \text{ to } +70^{\circ}C, \text{ all registers in their default state, unless otherwise noted. Typical values are at <math>V_{CHGIN} = 5.0V, V_{BAT} = 7.4V, T_A = +25^{\circ}C.)$

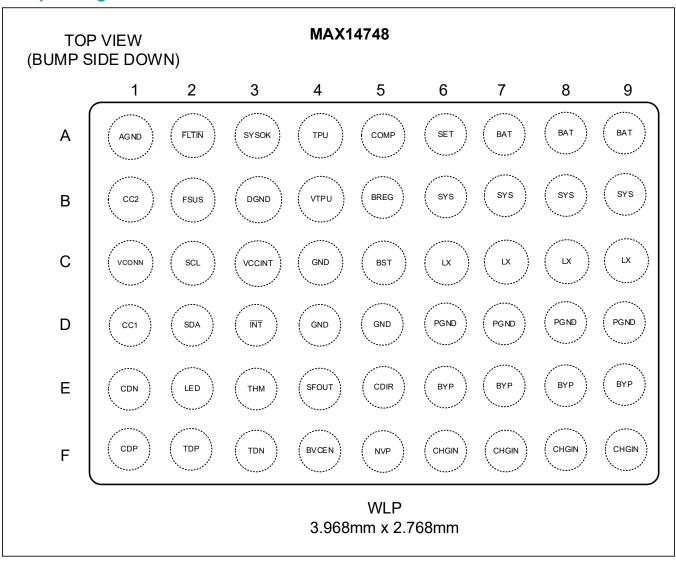

# **Bump Configuration**

# **Bump Descriptions**

| BUMP              | NAME               | FUNCTION                                                                                                                                                                                                                                                                                                                                 |

|-------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1                | AGND               | Analog Ground.                                                                                                                                                                                                                                                                                                                           |

| A2                | FLTIN              | Charger Fault Input. Logic-low on this pin forces the charger into a fault state and generates an interrupt. See Register 0x35 description for more information. Connect to digital I/O supply if not used.                                                                                                                              |

| А3                | SYSOK              | Open-Drain Status Output of SYS Regulation. When $V_{SYS}$ is above the SYS UVLO threshold and Boost is active, this output is high-impedance. When $V_{SYS}$ is below the SYS UVLO threshold, this output is low. Leave unconnected if not used.                                                                                        |

| A4                | TPU                | High-Side of Internal Resistor for THM Detection. Connect a 10k resistor between this pin and THM.                                                                                                                                                                                                                                       |

| A5                | COMP               | Buck/Boost Converter Compensation Connection. Connect a 3.9nF capacitor for internal Buck/Boost compensation                                                                                                                                                                                                                             |

| A6                | SET                | External Resistor Connection for Fast Charge Current Setting. Connect a resistor to this pin to set the fast charge current. Other charge currents are set as a proportion of fast charge current based on I <sup>2</sup> C register settings.                                                                                           |

| A7–A9             | BAT                | Battery Connection. Connect a 2s Li-ion+ battery from BAT to GND. Bypass to PGND with a parallel combination of a 0.1μF capacitor and an effective 10μF - 30μF capacitor. Keep the capacitors as close to BAT as possible and keep the stray inductance and resistance of the trace from BAT to the battery terminal as low as possible. |

| B1                | CC2                | USB Type-C CC2. Connect to CC2 on USB Type-C connector.                                                                                                                                                                                                                                                                                  |

| B2                | FSUS               | Force Suspend Input. Logic-high on this pin causes the input limiter to open and input current from CHGIN is reduced to zero. This pin is internally pulled to GND through a $470 k\Omega$ (typ) resistor and has no effect if FSUSMsk = 1.                                                                                              |

| В3                | DGND               | Digital Ground.                                                                                                                                                                                                                                                                                                                          |

| B4                | V <sub>TPU</sub>   | External Voltage Input for TPU connection. Connect to external supply or V <sub>CCINT</sub> .                                                                                                                                                                                                                                            |

| B5                | BREG               | Bypass for Internal Switching Converter Supply. Bypass with 1µF capacitor to AGND.                                                                                                                                                                                                                                                       |

| B6-B9             | SYS                | System Load Connection. Connect SYS to the system load. Bypass to PGND with a parallel combination of a 0.1µF capacitor and an effective 22µF capacitor. (Note: there is a diode between SYS and BAT)                                                                                                                                    |

| C1                | V <sub>CONN</sub>  | External V <sub>CONN</sub> Supply Input. Leave unconnected if not used.                                                                                                                                                                                                                                                                  |

| C2                | SCL                | I <sup>2</sup> C Serial Clock Input. Connect an external pull-up resistor.                                                                                                                                                                                                                                                               |

| C3                | V <sub>CCINT</sub> | Bypass For Internal Analog Supply. Bypass with 1µF capacitor to GND.                                                                                                                                                                                                                                                                     |

| C4, D4,<br>D5     | GND                | Ground.                                                                                                                                                                                                                                                                                                                                  |

| C5                | BST                | Charge Pump Connection. Connect a 0.1µF capacitor between BST and LX.                                                                                                                                                                                                                                                                    |

| C6, C7,<br>C8, C9 | LX                 | Switching Node of Boost Converter. Connect a 1.5µH or 2.2µH inductor between LX and BYP. See <i>Applications Information</i> section for more details.                                                                                                                                                                                   |

| D1                | CC1                | USB Type-C CC1. Connect to CC1 on USB Type-C connector.                                                                                                                                                                                                                                                                                  |