#### PB039 (v1.0) October 5, 2016

#### 50G IEEE 802.3 Reed-Solomon FEC v1.0

LogiCORE IP Product Brief

# Introduction

The Xilinx® LogiCORE<sup>™</sup> 50G IEEE 802.3 Reed-Solomon Forward Error Correction IP core implements the Reed-Solomon Forward Error Correction (RS-FEC) sublayer as described in the 25/50G Ethernet Consortium Schedule 3 (v1.6) section 3.2.3 [Ref 1].

# **Additional Documentation**

A product guide is available for this core. Access to this material can be requested by clicking on this registration link: www.xilinx.com/member/50g\_rs\_fec.html

# Features

- Low latency design

- Configuration and status bus

- Selectable AXI4-Lite interface for status output

- Example reference design demonstrating the use of the core with the GTY transceivers

- ECC RAM option

| Logi | CORE | IP | Facts | Table |

|------|------|----|-------|-------|

| Core Specifics                                    |                                                                                |  |  |  |

|---------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|

| Supported<br>Device Family <sup>(1)</sup>         | UltraScale+™<br>Virtex® UltraScale™                                            |  |  |  |

| Supported User<br>Interfaces                      | AXI4-Lite, Configuration and Status bus                                        |  |  |  |

| Provided with Core                                |                                                                                |  |  |  |

| Design Files                                      | Encrypted RTL                                                                  |  |  |  |

| Example Design                                    | Verilog                                                                        |  |  |  |

| Test Bench                                        | Not Provided                                                                   |  |  |  |

| Constraints File                                  | Xilinx Constraints File                                                        |  |  |  |

| Simulation<br>Model                               | Encrypted Verilog                                                              |  |  |  |

| Supported<br>S/W Driver                           | N/A                                                                            |  |  |  |

| Tested Design Flows <sup>(2)</sup>                |                                                                                |  |  |  |

| Design Entry                                      | Vivado® Design Suite                                                           |  |  |  |

| Simulation                                        | For supported simulators, see the<br>Xilinx Design Tools: Release Notes Guide. |  |  |  |

| Synthesis                                         | Vivado® Design Suite                                                           |  |  |  |

| Support                                           |                                                                                |  |  |  |

| Provided by Xilinx at the Xilinx Support web page |                                                                                |  |  |  |

#### Notes:

- 1. For a complete listing of supported devices, see the Vivado IP catalog.

- 2. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

www.xilinx.com

<sup>©</sup> Copyright 2016 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. AMBA, AMBA Designer, ARM, ARM1176JZ-S, CoreSight, Cortex, and PrimeCell are trademarks of ARM in the EU and other countries. All other trademarks are the property of their respective owners.

# Overview

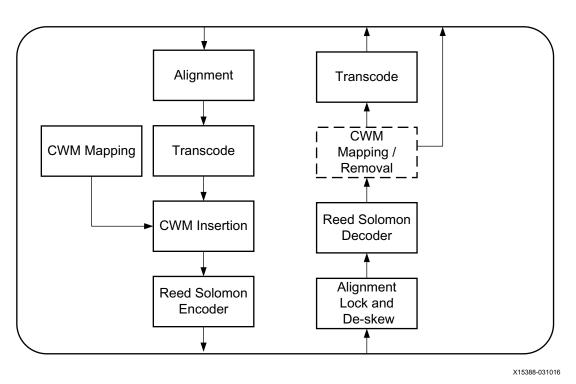

The RS-FEC layers of the 25/50G Ethernet Consortium Schedule 3 [Ref 1] define more than just the RS encoder/decoder. They define several stages of synchronization, alignment and transcoding which are necessary for the layer to communicate with preceding and subsequent layers. The functional block diagram of the core is shown in Figure 1.

# **Technical Support**

Xilinx provides technical support at the Xilinx Support web page for this LogiCORE<sup>™</sup> IP product when used as described in the product documentation. Xilinx cannot guarantee timing, functionality, or support if you do any of the following:

- Implement the solution in devices that are not defined in the documentation.

- Customize the solution beyond that allowed in the product documentation.

- Change any section of the design labeled DO NOT MODIFY.

To contact Xilinx Technical Support, navigate to the Xilinx Support web page.

## **Licensing and Ordering Information**

This Xilinx® LogiCORE<sup>™</sup> IP module is provided under the terms of the <u>Xilinx Core License</u> <u>Agreement</u>. The module is shipped as part of the Vivado Design Suite. For full access to all core functionalities in simulation and in hardware, you must purchase a license for the core. Contact your <u>local Xilinx sales representative</u> for information about pricing and availability.

For more information, visit the 50G Ethernet Subsystem product web page.

Information about other Xilinx LogiCORE IP modules is available at the <u>Xilinx Intellectual Property</u> page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your <u>local Xilinx sales representative</u>.

#### **Evaluation**

A full system hardware evaluation license is available for this core. The evaluation version of the core operates in the same way as the full version for several hours, dependent on clock frequency (approximately 10 hours at 391 MHz). Operation is then disabled and the data output does not change. If you notice this behavior in hardware, it probably means you are using an evaluation version of the core. The Xilinx tools warn that an evaluation license is being used during netlist implementation. If a full license is installed for the core to run on hardware, delete the old files and recreate the core from new.

### References

This document provides supplemental material useful with this product brief:

1. 25/50G Ethernet Consortium Schedule 3 specification, (http://25gethernet.org/)

### **Revision History**

The following table shows the revision history for this document:

| Date       | Version | Revision                                             |

|------------|---------|------------------------------------------------------|

| 10/05/2016 | 1.0     | Updated to align with Product Guide (PG234) updates. |

| 04/06/2016 | 1.0     | Initial Xilinx release.                              |

### **Please Read: Important Legal Notices**

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials without prior written consent. Certain products are subject to the terms and conditions of Xilinx's limited warranty, please refer to Xilinx's Terms of Sale which can be viewed at <a href="http://www.xilinx.com/legal.htm#tos">http://www.xilinx.com/legal.htm#tos</a>. IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are of Xilinx products in such critical applications, please refer to Xilinx's Terms of Sale which can be viewed at <a href="http://www.xilinx.com/legal.htm#tos">http://www.xilinx.com/legal.htm#tos</a>.

#### AUTOMOTIVE APPLICATIONS DISCLAIMER

AUTOMOTIVE PRODUCTS (IDENTIFIED AS "XA" IN THE PART NUMBER) ARE NOT WARRANTED FOR USE IN THE DEPLOYMENT OF AIRBAGS OR FOR USE IN APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE ("SAFETY APPLICATION") UNLESS THERE IS A SAFETY CONCEPT OR REDUNDANCY FEATURE CONSISTENT WITH THE ISO 26262 AUTOMOTIVE SAFETY STANDARD ("SAFETY DESIGN"). CUSTOMER SHALL, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE PRODUCTS, THOROUGHLY TEST SUCH SYSTEMS FOR SAFETY PURPOSES. USE OF PRODUCTS IN A SAFETY APPLICATION WITHOUT A SAFETY DESIGN IS FULLY AT THE RISK OF CUSTOMER, SUBJECT ONLY TO APPLICABLE LAWS AND REGULATIONS GOVERNING LIMITATIONS ON PRODUCT LIABILITY.