## **Features**

- High-performance

- System Speeds > 100 MHz

- Flip-flop Toggle Rates > 250 MHz

- 1.2 ns/1.5 ns Input Delay

- 3.0 ns/6.0 ns Output Delay

- Up to 204 User I/Os

- . Thousands of Registers

- Cache Logic<sup>®</sup> Design

- Complete/Partial In-System Reconfiguration

- No Loss of Data or Machine State

- Adaptive Hardware

- Low Voltage and Standard Voltage Operation

- $-5.0 (V_{CC} = 4.75V \text{ to } 5.25V)$

- $-3.3 (V_{CC} = 3.0V \text{ to } 3.6V)$

- Automatic Component Generators

- Reusable Custom Hard Macro Functions

- Very Low-power Consumption

- Standby Current of 500 μA/ 200 μA

- Typical Operating Current of 15 to 170 mA

- Programmable Clock Options

- Independently Controlled Column Clocks

- Independently Controlled Column Resets

- Clock Skew Less Than 1 ns Across Chip

- Independently Configurable I/O (PCI Compatible)

- TTL/CMOS Input Thresholds

- Open Collector/Tristate Outputs

- Programmable Slew-rate Control

- I/O Drive of 16 mA (combinable to 64 mA)

- Easy Migration to Atmel Gate Arrays for High Volume Production

## **Description**

AT6000 Series SRAM-based Field Programmable Gate Arrays (FPGAs) are ideal for use as reconfigurable coprocessors and implementing compute-intensive logic.

Supporting system speeds greater than 100 MHz and using a typical operating current of 15 to 170 mA, AT6000 Series devices are ideal for high-speed, compute-intensive designs. These FPGAs are designed to implement Cache Logic<sup>®</sup>, which provides the user with the ability to implement adaptive hardware and perform hardware acceleration.

The patented AT6000 Series architecture employs a symmetrical grid of small yet powerful cells connected to a flexible busing network. Independently controlled clocks and resets govern every column of cells. The array is surrounded by programmable I/O.

(continued)

## AT6000 Series Field Programmable Gate Arrays

| Device                      | AT6002  | AT6003  | AT6005  | AT6010   |

|-----------------------------|---------|---------|---------|----------|

| Usable Gates                | 6,000   | 9,000   | 15,000  | 30,000   |

| Cells                       | 1,024   | 1,600   | 3,136   | 6,400    |

| Registers (maximum)         | 1,024   | 1,600   | 3,136   | 6,400    |

| I/O (maximum)               | 96      | 120     | 108     | 204      |

| Typ. Operating Current (mA) | 15 - 30 | 25 - 45 | 40 - 80 | 85 - 170 |

| Cell Rows x Columns         | 32 x 32 | 40 x 40 | 56 x 56 | 80 x 80  |

# Coprocessor Field Programmable Gate Arrays

AT6000(LV) Series

Rev. 0264F-10/99

Devices range in size from 4,000 to 30,000 usable gates, and 1024 to 6400 registers. Pin locations are consistent throughout the AT6000 Series for easy design migration. High-I/O versions are available for the lower gate count devices.

AT6000 Series FPGAs utilize a reliable 0.6 µm single-poly, double-metal CMOS process and are 100% factory-tested.

Atmel's PC- and workstation-based Integrated Development System is used to create AT6000 Series designs. Multiple design entry methods are supported.

The Atmel architecture was developed to provide the highest levels of performance, functional density and design flexibility in an FPGA. The cells in the Atmel array are small, very efficient and contain the most important and most commonly used logic and wiring functions. The cell's small size leads to arrays with large numbers of cells, greatly multiplying the functionality in each cell. A simple, high-speed busing network provides fast, efficient communication over medium and long distances.

## **The Symmetrical Array**

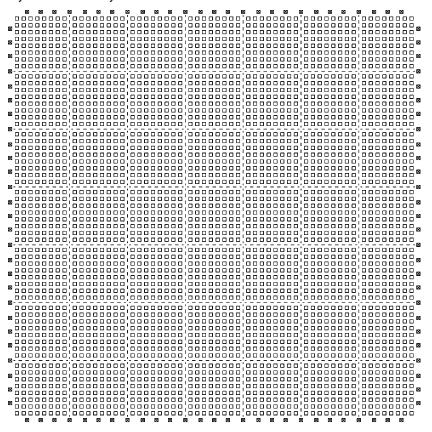

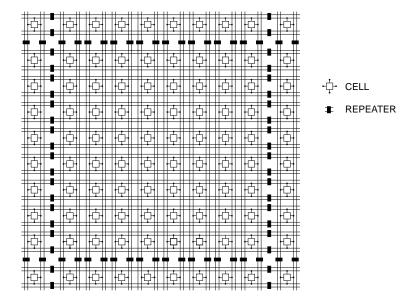

At the heart of the Atmel architecture is a symmetrical array of identical cells (Figure 1). The array is continuous and completely uninterrupted from one edge to the other, except for bus *repeaters* spaced every eight cells (Figure 2).

In addition to logic and storage, cells can also be used as wires to connect functions together over short distances and are useful for routing in tight spaces.

## The Busing Network

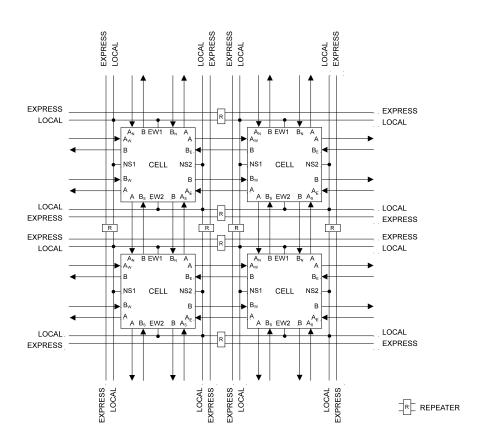

There are two kinds of buses: local and express (see Figures 2 and 3).

Local buses are the link between the array of cells and the busing network. There are two local buses – North-South 1 and 2 (NS1 and NS2) – for every column of cells, and two local buses – East-West 1 and 2 (EW1 and EW2) – for every row of cells. In a sector (an 8 x 8 array of cells enclosed by repeaters) each local bus is connected to every cell in its column or row, thus providing every cell in the array with read/write access to two North-South and two East-West buses.

Figure 1. Symmetrical Array Surrounded by I/O

Figure 2. Busing Network (one sector)

Figure 3. Cell-to-cell and Bus-to-bus Connections

Each cell, in addition, provides the ability to route a signal on a 90° turn between the NS1 bus and EW1 bus and between the NS2 bus and EW2 bus.

Express buses are not connected directly to cells, and thus provide higher speeds. They are the fastest way to cover long, straight-line distances within the array.

Each express bus is paired with a local bus, so there are two express buses for every column and two express buses for every row of cells.

Connective units, called repeaters, spaced every eight cells, divide each bus, both local and express, into segments spanning eight cells. Repeaters are aligned in rows and columns thereby partitioning the array into 8 x 8 sectors of cells. Each repeater is associated with a local/express pair, and on each side of the repeater are connections to a local-bus segment and an express-bus segment. The repeater can be programmed to provide any one of twenty-one connecting functions. These functions are symmetric with respect to both the two repeater sides and the two types of buses.

Among the functions provided are the ability to:

- Isolate bus segments from one another

- · Connect two local-bus segments

- · Connect two express-bus segments

- Implement a local/express transfer

In all of these cases, each connection provides signal regeneration and is thus unidirectional. For bidirectional connections, the basic repeater function for the NS2 and EW2 repeaters is augmented with a special programmable connection allowing bidirectional communication between local-bus segments. This option is primarily used to implement long, tristate buses.

### The Cell Structure

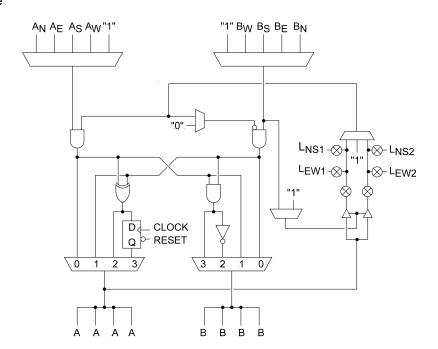

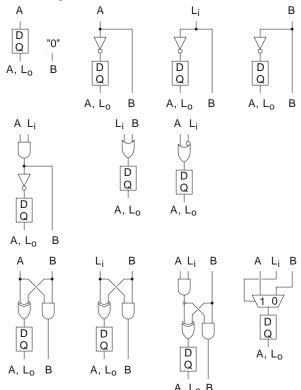

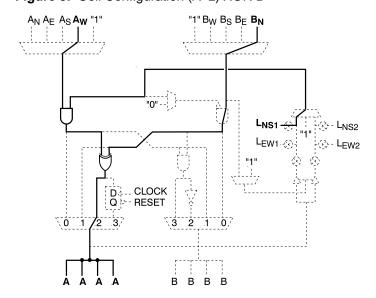

The Atmel cell (Figure 4) is simple and small and yet can be programmed to perform all the logic and wiring functions needed to implement any digital circuit. Its four sides are functionally identical, so each cell is completely symmetrical.

Read/write access to the four local buses – NS1, EW1, NS2 and EW2 – is controlled, in part, by four bidirectional pass gates connected directly to the buses. To read a local bus, the pass gate for that bus is turned on and the three-input multiplexer is set accordingly. To write to a local bus, the pass gate for that bus and the pass gate for the associated tristate driver are both turned on. The two-input multiplexer supplying the control signal to the drivers permits either: (1) active drive, or (2) dynamic tristating controlled by the B input. Turning between  $L_{\rm NS1}$  and  $L_{\rm EW1}$  or between  $L_{\rm NS2}$  and  $L_{\rm EW2}$  is accomplished by turning on the two associated pass gates. The operations of reading, writing and turning are subject to the restriction that each bus can be involved in no more than a *single* operation.

Figure 4. Cell Structure

In addition to the four local-bus connections, a cell receives two inputs and provides two outputs to each of its North (N), South (S), East (E) and West (W) neighbors. These inputs and outputs are divided into two classes: "A" and "B". There is an A input and a B input from each neighboring cell and an A output and a B output driving all four neighbors. Between cells, an A output is always connected to an A input and a B output to a B input.

Within the cell, the four A inputs and the four B inputs enter two separate, independently configurable multiplexers. Cell flexibility is enhanced by allowing each multiplexer to select also the logical constant "1". The two multiplexer outputs enter the two upstream AND gates.

Downstream from these two AND gates are an Exclusive-OR (XOR) gate, a register, an AND gate, an inverter and two four-input multiplexers producing the A and B outputs. These multiplexers are controlled in tandem (unlike the A and B input multiplexers) and determine the function of the cell.

- In State 0 corresponding to the "0" inputs of the multiplexers – the output of the left-hand upstream AND gate is connected to the cell's A output, and the output of the right-hand upstream AND gate is connected to the cell's B output.

- In State 1 corresponding to the "1" inputs of the multiplexers – the output of the left-hand upstream AND gate is connected to the cell's B output, the output of the right-hand upstream AND gate is connected to the cell's A output.

- In State 2 corresponding to the "2" inputs of the multiplexers – the XOR of the outputs from the two upstream AND gates is provided to the cell's A output, while the NAND of these two outputs is provided to the cell's B output.

In State 3 – corresponding to the "3" inputs of the

multiplexers – the XOR function of State 2 is provided to

the D input of a D-type flip-flop, the Q output of which is

connected to the cell's A output. Clock and

asynchronous reset signals are supplied externally as

described later. The AND of the outputs from the two

upstream AND gates is provided to the cell's B output.

## **Logic States**

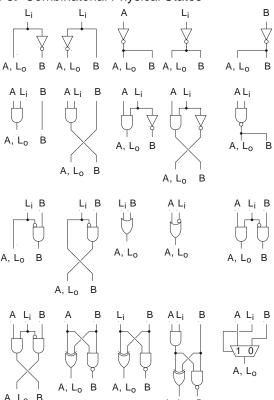

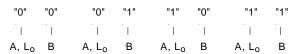

The Atmel cell implements a rich and powerful set of logic functions, stemming from 44 logical cell states which permutate into 72 physical states. Some states use both A and B inputs. Other states are created by selecting the "1" input on either or both of the input multiplexers.

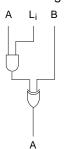

There are 28 combinatorial primitives created from the cell's tristate capabilities and the 20 physical states represented in Figure 5. Five logical primitives are derived from the physical constants shown in Figure 7. More complex functions are created by using cells in combination.

A two-input AND feeding an XOR (Figure 8) is produced using a single cell (Figure 9). A two-to-one multiplexer selects the logical constant "0" and feeds it to the right-hand AND gate. The AND gate acts as a feed-through, letting the B input pass through to the XOR. The three-to-one multiplexer on the right side selects the local-bus input, LNS1, and passes it to the left-hand AND gate. The A and LNS1 signals are the inputs to the AND gate. The output of the AND gate feeds into the XOR, producing the logic state (A•L) XOR B.

Figure 5. Combinatorial Physical States

Figure 7. Physical Constants

Figure 8. Two-input AND Feeding XOR

Figure 6. Register States

Figure 9. Cell Configuration (A•L) XOR B

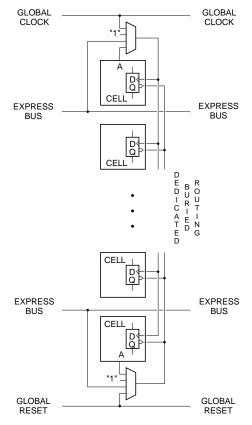

### **Clock Distribution**

Along the top edge of the array is logic for distributing clock signals to the D flip-flop in each logic cell (Figure 10). The distribution network is organized by column and permits columns of cells to be independently clocked. At the head of each column is a user-configurable multiplexer providing the clock signal for that column. It has four inputs:

- Global clock supplied through the CLOCK pin

- Express bus adjacent to the distribution logic

- "A" output of the cell at the head of the column

- Logical constant "1" to conserve power (no clock)

Through the global clock, the network provides low-skew distribution of an externally supplied clock to any or all of the columns of the array. The global clock pin is also connected directly to the array via the A input of the upper left and right corner cells (AW on the left, and AN on the right). The express bus is useful in distributing a secondary clock to multiple columns when the global clock line is used as a primary clock. The A output of a cell is useful in providing a clock signal to a single column. The constant "1" is used to reduce power dissipation in columns using no registers.

Figure 10. Column Clock and Column Reset

### **Asynchronous Reset**

Along the bottom edge of the array is logic for asynchronously resetting the D flip-flops in the logic cells (Figure 10). Like the clock network, the asynchronous reset network is organized by column and permits columns to be independently reset. At the bottom of each column is a user-configurable multiplexer providing the reset signal for that column. It has four inputs:

- Global asynchronous reset supplied through the RESET pin

- · Express bus adjacent to the distribution logic

- · "A" output of the cell at the foot of the column

- · Logical constant "1" to conserve power

The asynchronous reset logic uses these four inputs in the same way that the clock distribution logic does. Through the global asynchronous reset, any or all columns can be reset by an externally supplied signal. The global asynchronous reset pin is also connected directly to the array via the A input of the lower left and right corner cells (AS on the left, and AE on the right). The express bus can be used to distribute a secondary reset to multiple columns when the global reset line is used as a primary reset, the A output of a cell can also provide an asynchronous reset signal to a single column, and the constant "1" is used by columns with registers requiring no reset. All registers are reset during power-up.

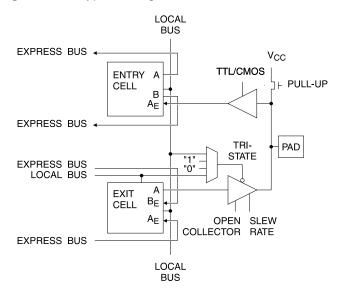

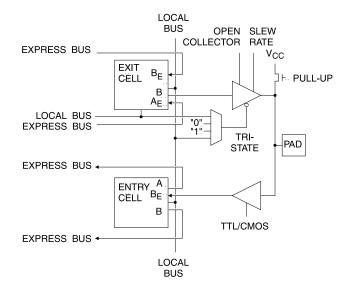

## Input/Output

The Atmel architecture provides a flexible interface between the logic array, the configuration control logic and the I/O pins.

Two adjacent cells – an "exit" and an "entrance" cell – on the perimeter of the logic array are associated with each I/O pin.

There are two types of I/Os: A-type (Figure 11) and B-type (Figure 12). For A-type I/Os, the edge-facing A output of an exit cell is connected to an output driver, and the edge-facing A input of the adjacent entrance cell is connected to an input buffer. The output of the output driver and the input of the input buffer are connected to a common pin.

B-type I/Os are the same as A-type I/Os, but use the B inputs and outputs of their respective entrance and exit cells. A- and B-type I/Os alternate around the array Control of the I/O logic is provided by user-configurable memory bits.

Figure 11. A-type I/O Logic

Figure 12. B-type I/O Logic

### **TTL/CMOS Inputs**

A user-configurable bit determines the threshold level – TTL or CMOS – of the input buffer.

#### **Open Collector/Tristate Outputs**

A user-configurable bit which enables or disables the active pull-up of the output device.

#### **Slew Rate Control**

A user-configurable bit controls the slew rate – fast or slow – of the output buffer. A slow slew rate, which reduces noise and ground bounce, is recommended for outputs that are not speed-critical. Fast and slow slew rates have the same DC-current sinking capabilities, but the rate at which each allows the output devices to reach full drive differs.

### Pull-up

A user-configurable bit controls the pull-up transistor in the I/O pin. It's primary function is to provide a logical "1" to unused input pins. When on, it is approximately equivalent to a 25K resistor to  $V_{\rm CC}$ .

#### **Enable Select**

User-configurable bits determine the output-enable for the output driver. The output driver can be static – always on or always off – or dynamically controlled by a signal generated in the array. Four options are available from the array: (1) the control is low and always driving; (2) the control is high and never driving; (3) the control is connected to a vertical local bus associated with the output cell; or (4) the control is connected to a horizontal local bus associated with the output cell. On power-up, the user I/Os are configured as inputs with pull-up resistors.

In addition to the functionality provided by the I/O logic, the entrance and exit cells provide the ability to register both inputs and outputs. Also, these perimeter cells (unlike interior cells) are connected directly to express buses: the edge-facing A and B outputs of the entrance cell are connected to express buses, as are the edge-facing A and B inputs of the exit cell. These buses are perpendicular to the edge, and provide a rapid means of bringing I/O signals to and from the array interior and the opposite edge of the chip.

## **Chip Configuration**

The Integrated Development System generates the SRAM bit pattern required to configure a AT6000 Series device. A PC parallel port, microprocessor, EPROM or serial configuration memory can be used to download configuration patterns.

Users select from several configuration modes. Many factors, including board area, configuration speed and the number of designs implemented in parallel can influence the user's final choice.

Configuration is controlled by dedicated configuration pins and dual-function pins that double as I/O pins when the device is in operation. The number of dual-function pins required for each mode varies.

The devices can be partially reconfigured while in operation. Portions of the device not being modified remain operational during reconfiguration. Simultaneous configuration of more than one device is also possible. Full configuration takes as little as a millisecond, partial configuration is even faster.

Refer to the Pin Function Description section following for a brief summary of the pins used in configuration. For more information about configuration, refer to the AT6000 Series Configuration data sheet.

## **Pin Function Description**

This section provides abbreviated descriptions of the various AT6000 Series pins. For more complete descriptions, refer to the AT6000 Series Configuration data sheet.

Pinout tables for the AT6000 series of devices follow.

### **Power Pins**

## $V_{CC}$ , $V_{DD}$ , GND, $V_{SS}$

$V_{CC}$  and GND are the I/O supply pins,  $V_{DD}$  and  $V_{SS}$  are the internal logic supply pins.  $V_{CC}$  and  $V_{DD}$  should be tied to the same trace on the printed circuit board. GND and  $V_{SS}$  should be tied to the same trace on the printed circuit board.

## **Input/Output Pins**

All I/O pins can be used in the same way (refer to the I/O section of the architecture description). Some I/O pins are dual-function pins used during configuration of the array. When not being used for configuration, dual-function I/Os are fully functional as normal I/O pins. On initial power-up, all I/Os are configured as TTL inputs with a pull-up.

## **Dedicated Timing and Control Pins**

### CON

Configuration-in-process pin. After power-up,  $\overline{\text{CON}}$  staysLow until power-up initialization is complete, at which time  $\overline{\text{CON}}$  is then released.  $\overline{\text{CON}}$  is an open collector signal. After power-up initialization, forcing  $\overline{\text{CON}}$  low begins the configuration process.

### CS

Configuration enable pin. All configuration pins are ignored if  $\overline{CS}$  is high.  $\overline{CS}$  must be held low throughout the configuration process.  $\overline{CS}$  is a TTL input pin.

#### M0, M1, M2

Configuration mode pins are used to determine the configuration mode. All three are TTL input pins.

#### **CCLK**

Configuration clock pin. CCLK is a TTL input or a CMOS output depending on the mode of operation. In modes 1, 2, 3, and 6 it is an input. In modes 4 and 5 it is an output with a typical frequency of 1 MHz. In all modes, the rising edge of the CCLK signal is used to sample inputs and change outputs.

### **CLOCK**

External logic source used to drive the internal global clock line. Registers toggle on the rising edge of CLOCK. The CLOCK signal is neither used nor affected by the configuration modes. It is always a TTL input.

### **RESET**

Array register asynchronous reset. RESET drives the internal global reset. The RESET signal is neither used nor affected by the configuration modes. It is always a TTL input.

#### **Dual-function Pins**

When  $\overline{\text{CON}}$  is high, dual-function I/O pins act as device I/Os; when  $\overline{\text{CON}}$  is low, dual-function pins are used as configuration control or data signals as determined by the configuration modes. Care must be taken when using these pins to ensure that configuration activity does not interfere with other circuitry connected to these pins in the application.

#### D0 or I/O

Serial configuration modes use D0 as the serial data input pin. Parallel configuration modes use D0 as the least-significant bit. Input data must meet setup and hold requirements with respect to the rising edge of CCLK. D0 is a TTL input during configuration.

#### D1 to D7 or I/O

Parallel configuration modes use these pins as inputs. Serial configuration modes do not use them. Data must meet setup and hold requirements with respect to the rising edge of CCLK. D1 - D7 are TTL inputs during configuration.

### A0 to A16 or I/O

During configuration in modes 1, 2 and 5, these pins are CMOS outputs and act as the address pins for a parallel EPROM. A0 - A16 eliminates the need for an external address counter when using an external parallel nonvolatile

memory to configure the FPGA. Addresses change after the rising edge of the CCLK signal.

### **CSOUT** or I/O

When cascading devices,  $\overline{\text{CSOUT}}$  is an output used to enable other devices.  $\overline{\text{CSOUT}}$  should be connected to the  $\overline{\text{CS}}$  input of the downstream device. The  $\overline{\text{CSOUT}}$  function is optional and can be disabled during initial programming when cascading is not used. When cascading devices,  $\overline{\text{CSOUT}}$  should be dedicated to configuration and not used as a configurable I/O.

### **CHECK** or I/O

During configuration,  $\overline{CHECK}$  is a TTL input that can be used to enable the data check function at the beginning of a configuration cycle. No data is written to the device while  $\overline{CHECK}$  is low. Instead, the configuration file being applied to D0 (or D0 - D7, in parallel mode) is compared with the

current contents of the internal configuration RAM. If a mismatch is detected between the data being loaded and the data already in the RAM, the  $\overline{\text{ERR}}$  pin goes low. The  $\overline{\text{CHECK}}$  function is optional and can be disabled during initial programming.

#### ERR or I/O

During configuration,  $\overline{ERR}$  is an output. When the  $\overline{CHECK}$  function is activated and a mismatch is detected between the current configuration data stream and the data already loaded in the configuration RAM,  $\overline{ERR}$  goes low. The  $\overline{ERR}$  ouput is a registered signal. Once a mismatch is found, the signal is set and is only reset after the configuration cycle is restarted.  $\overline{ERR}$  is also asserted for configuration file errors. The  $\overline{ERR}$  function is optional and can be disabled during initial programming.

## **Device Pinout Selection (Max. Number of User I/O)**

|          | AT6002 | AT6003  | AT6005  | AT6010  |

|----------|--------|---------|---------|---------|

| 84 PLCC  | 64 I/O | 64 I/O  | 64 I/O  | -       |

| 100 VQFP | 80 I/O | 80 I/O  | 80 I/O  | -       |

| 132 PQFP | 96 I/O | 108 I/O | 108 I/O | 108 I/O |

| 144 TQFP | 95 I/O | 120 I/O | 108 I/O | 120 I/O |

| 208 PQFP | -      | -       | -       | 172 I/O |

| 240 PQFP | -      | -       | -       | 204 I/O |

### **Bit-stream Sizes**

| Mode(s) | Туре     | Beginning Sequence | AT6002 | AT6003 | AT6005 | AT6010 |

|---------|----------|--------------------|--------|--------|--------|--------|

| 1       | Parallel | Preamble           | 2677   | 4153   | 8077   | 16393  |

| 2       | Parallel | Preamble           | 2677   | 4153   | 8077   | 16393  |

| 3       | Serial   | Null Byte/Preamble | 2678   | 4154   | 8078   | 16394  |

| 4       | Serial   | Null Byte/Preamble | 2678   | 4154   | 8078   | 16394  |

| 5       | Parallel | Preamble           | 2677   | 4153   | 8077   | 16393  |

| 6       | Parallel | Preamble/Preamble  | 2678   | 4154   | 8078   | 16394  |

# **Pinout Assignment**

|                |                |                | Left Side (Top |            |             |             |             |                    |             |             |

|----------------|----------------|----------------|----------------|------------|-------------|-------------|-------------|--------------------|-------------|-------------|

| AT6002         | AT6003         | AT6005         | AT6010         | 84<br>PLCC | 100<br>VQFP | 132<br>PQFP | 144<br>TQFP | 180<br>CPGA        | 208<br>PQFP | 240<br>PQFP |

| -              | -              | -              | I/O51(A)       | -          | -           | -           | -           | B1                 | 1           | 1           |

| I/O24(A) or A7 | I/O30(A) or A7 | I/O27(A) or A7 | I/O50(A) or A7 | 12         | 1           | 18          | 1           | C1                 | 2           | 2           |

| -              | I/O29(B)       | -              | I/O49(A)       | -          | -           | -           | 2           | D1                 | 3           | 3           |

| =              | -              | -              | I/O48(B)       | -          | -           | -           | -           | -                  | -           | 4           |

| -              | -              | -              | VCC            | -          | -           | -           | -           | PWR <sup>(1)</sup> | 4           | 5           |

| -              | -              | -              | I/O47(A)       | -          | -           | -           | -           | E1                 | 5           | 6           |

| -              | -              | -              | GND            | -          | -           | -           | -           | GND <sup>(2)</sup> | 6           | 7           |

| -              | I/O28(A)       | I/O26(A)       | I/O46(A)       | -          | -           | 19          | 3           | G1                 | 7           | 8           |

| I/O23(A) or A6 | I/O27(A) or A6 | I/O25(A) or A6 | I/O45(A) or A6 | 13         | 2           | 20          | 4           | H1                 | 8           | 9           |

| -              | -              | -              | I/O44(B)       | -          | -           | -           | -           | -                  | -           | 10          |

| -              | -              | -              | I/O43(A)       | -          | -           | -           | -           | C2                 | 9           | 11          |

| I/O22(B)       | I/O26(A)       | I/O24(A)       | I/O42(A)       | -          | -           | 21          | 5           | D2                 | 10          | 12          |

| I/O21(A) or A5 | I/O25(A) or A5 | I/O23(A) or A5 | I/O41(A) or A5 | 14         | 3           | 22          | 6           | E2                 | 11          | 13          |

| -              | -              | -              | I/O40(B)       | -          | -           | -           | -           | -                  | -           | 14          |

| -              | -              | -              | I/O39(A)       | -          | -           | -           | -           | F2                 | 12          | 15          |

| I/O20(B)       | I/O24(B)       | I/O22(A)       | I/O38(A)       | -          | 4           | 23          | 7           | G2                 | 13          | 16          |

| I/O19(A) or A4 | I/O23(A) or A4 | I/O21(A) or A4 | I/O37(A) or A4 | 15         | 5           | 24          | 8           | H2                 | 14          | 17          |

| -              | -              | -              | I/O36(B)       | -          | -           | -           | -           | -                  | -           | 18          |

| I/O18(B)       | I/O22(B)       | I/O20(A)       | I/O35(A)       | -          | -           | 25          | 9           | D3                 | 15          | 19          |

| I/O17(A) or A3 | I/O21(A) or A3 | I/O19(A) or A3 | I/O34(A) or A3 | 16         | 6           | 26          | 10          | E3                 | 16          | 20          |

| I/O16(B)       | I/O20(B)       | I/O18(A)       | I/O33(A)       | -          | 7           | 27          | 11          | F3                 | 17          | 21          |

| =              | -              | -              | I/O32(B)       | -          | -           | -           | -           | -                  | 18          | 22          |

| I/O15(A) or A2 | I/O19(A) or A2 | I/O17(A) or A2 | I/O31(A) or A2 | 17         | 8           | 28          | 12          | G3                 | 19          | 23          |

| -              | I/O18(B)       | I/O16(A)       | I/O30(A)       | -          | -           | 29          | 13          | НЗ                 | 20          | 24          |

| GND            | GND            | GND            | GND            | 18         | 9           | 30          | 14          | GND <sup>(2)</sup> | 21          | 25          |

| VSS            | VSS            | VSS            | VSS            | 19         | 10          | 31          | 15          | GND <sup>(2)</sup> | 22          | 26          |

| I/O14(A) or A1 | I/O17(A) or A1 | I/O15(A) or A1 | I/O29(A) or A1 | 20         | 11          | 32          | 16          | F4                 | 23          | 27          |

| -              | -              | -              | I/O28(B)       | -          | -           | -           | -           | -                  | 24          | 28          |

| -              | I/O16(B)       | -              | I/O27(A)       | -          | -           | -           | 17          | G4                 | 25          | 29          |

| I/O13(A) or A0 | I/O15(A) or A0 | I/O14(A) or A0 | I/O26(A) or A0 | 21         | 12          | 33          | 18          | H4                 | 26          | 30          |

| I/O12(B) or D7 | I/O14(A) or D7 | I/O13(A) or D7 | I/O25(B) or D7 | 22         | 13          | 34          | 19          | H5                 | 27          | 31          |

| -              | -              | -              | I/O24(B)       | -          | -           | -           | -           | -                  | 28          | 32          |

| I/O11(A) or D6 | I/O13(A) or D6 | I/O12(A) or D6 | I/O23(A) or D6 | 23         | 14          | 35          | 20          | J4                 | 29          | 33          |

| I/O10(A) or D5 | I/O12(A) or D5 | I/O11(A) or D5 | I/O22(A) or D5 | 24         | 15          | 36          | 21          | K4                 | 30          | 34          |

| VDD            | VDD            | VDD            | VDD            | 25         | 16          | 37          | 22          | PWR <sup>(1)</sup> | 31          | 35          |

| VCC            | VCC            | VCC            | vcc            | 26         | 17          | 38          | 23          | PWR <sup>(1)</sup> | 32          | 36          |

## **Pinout Assignment (Continued)**

|               |                |               | Left Side (Top | to Bottom  | 1)          |             |             |                    |             |             |

|---------------|----------------|---------------|----------------|------------|-------------|-------------|-------------|--------------------|-------------|-------------|

| AT6002        | AT6003         | AT6005        | AT6010         | 84<br>PLCC | 100<br>VQFP | 132<br>PQFP | 144<br>TQFP | 180<br>CPGA        | 208<br>PQFP | 240<br>PQFP |

| I/O9(B)       | I/O11(B)       | I/O10(A)      | I/O21(A)       | -          | -           | 39          | 24          | J3                 | 33          | 37          |

| -             | -              | -             | I/O20(B)       | -          | -           | -           | -           | -                  | 34          | 38          |

| I/O8(A) or D4 | I/O10(A) or D4 | I/O9(A) or D4 | I/O19(A) or D4 | 27         | 18          | 40          | 25          | КЗ                 | 35          | 39          |

| I/O7(B)       | I/O9(B)        | I/O8(A)       | I/O18(A)       | -          | 19          | 41          | 26          | L3                 | 36          | 40          |

| -             | -              | -             | I/O17(A)       | -          | -           | -           | -           | МЗ                 | 37          | 41          |

| -             | -              | -             | I/O16(B)       | -          | -           | -           | -           | -                  | -           | 42          |

| I/O6(A) or D3 | I/O8(A) or D3  | I/O7(A) or D3 | I/O15(A) or D3 | 28         | 20          | 42          | 27          | N3                 | 38          | 43          |

| -             | I/O7(B)        | I/O6(A)       | I/O14(A)       | -          | -           | 43          | 28          | J2                 | 39          | 44          |

| -             | -              | -             | I/O13(A)       | -          | -           | -           | -           | K2                 | 40          | 45          |

| GND           | GND            | GND           | GND            | -          | -           | 44          | 29          | GND <sup>(2)</sup> | 41          | 46          |

| =             | -              | -             | VSS            | -          | -           | -           | -           | GND <sup>(2)</sup> | 42          | 47          |

| -             | -              | -             | I/O12(B)       | -          | -           | -           | -           | -                  | -           | 48          |

| I/O5(A) or D2 | I/O6(A) or D2  | I/O5(A) or D2 | I/O11(A) or D2 | 29         | 21          | 45          | 30          | M2                 | 43          | 49          |

| I/O4(B)       | I/O5(B)        | I/O4(A)       | I/O10(A)       | -          | 22          | 46          | 31          | N2                 | 44          | 50          |

| -             | -              | -             | I/O9(A)        | -          | -           | -           | -           | P2                 | 45          | 51          |

| =             | -              | -             | I/O8(B)        | -          | -           | -           | -           | -                  | -           | 52          |

| I/O3(A) or D1 | I/O4(A) or D1  | I/O3(A) or D1 | I/O7(A) or D1  | 30         | 23          | 47          | 32          | J1                 | 46          | 53          |

| I/O2(B)       | I/O3(A)        | I/O2(A)       | I/O6(A)        | -          | -           | 48          | 33          | K1                 | 47          | 54          |

| =             | -              | -             | I/O5(A)        | -          | -           | -           | -           | L1                 | 48          | 55          |

| -             | -              | -             | I/O4(B)        | -          | -           | -           | -           | -                  | -           | 56          |

| -             | I/O2(B)        | -             | I/O3(A)        | -          | -           | -           | 34          | M1                 | 49          | 57          |

| I/O1(A) or D0 | I/O1(A) or D0  | I/O1(A) or D0 | I/O2(A) or D0  | 31         | 24          | 49          | 35          | N1                 | 50          | 58          |

| -             | -              | -             | I/O1(A)        | -          | -           | -           | -           | P1                 | 51          | 59          |

| CCLK          | CCLK           | CCLK          | CCLK           | 32         | 25          | 50          | 36          | R1                 | 52          | 60          |

Notes: 1. PWR = Pins connected to power plane = F1, E4/E5, L2, R4, K15, L12, E14, A12.

<sup>2.</sup> GND = Pins connected to ground plane = L4, M4, N9, N10, E12, D12, C7, C6.

# **Pinout Assignment**

|                      |                       |                       | Bottom Side (L        | eft to Right | )           |             |             |                    |             |             |

|----------------------|-----------------------|-----------------------|-----------------------|--------------|-------------|-------------|-------------|--------------------|-------------|-------------|

| AT6002               | AT6003                | AT6005                | AT6010                | 84<br>PLCC   | 100<br>VQFP | 132<br>PQFP | 144<br>TQFP | 180<br>CPGA        | 208<br>PQFP | 240<br>PQFP |

| CON                  | CON                   | CON                   | CON                   | 33           | 26          | 51          | 37          | M5                 | 53          | 61          |

| -                    | -                     | -                     | I/O204(A)             | -            | -           | -           | -           | M6                 | 54          | 62          |

| I/O96(A)             | I/O120(A)             | I/O108(A)             | I/O203(A)             | 34           | 27          | 52          | 38          | M7                 | 55          | 63          |

| -                    | I/O119(B)             | -                     | I/O202(A)             | -            | -           | -           | 39          | R2                 | 56          | 64          |

| -                    | -                     | -                     | I/O201(B)             | -            | -           | -           | -           | -                  | -           | 65          |

| -                    | -                     | -                     | VCC                   | -            | -           | -           | -           | PWR <sup>(1)</sup> | 57          | 66          |

| -                    | -                     | -                     | I/O200(A)             | -            | -           | -           | -           | R3                 | 58          | 67          |

| -                    | -                     | -                     | GND                   | -            | -           | -           | -           | GND <sup>(2)</sup> | 59          | 68          |

| -                    | I/O118(A)             | I/O107(A)             | I/O199(A)             | -            | -           | 53          | 40          | R5                 | 60          | 69          |

| I/O95(A) or<br>CSOUT | I/O117(A) or<br>CSOUT | I/O106(A) or<br>CSOUT | I/O198(A) or<br>CSOUT | 35           | 28          | 54          | 41          | R6                 | 61          | 70          |

| -                    | -                     | -                     | I/O197(B)             | -            | -           | -           | -           | -                  | -           | 71          |

| -                    | -                     | -                     | I/O196(A)             | -            | -           | -           | -           | R7                 | 62          | 72          |

| I/O94(B)             | I/O116(A)             | I/O105(A)             | I/O195(A)             | -            | -           | 55          | 42          | P3                 | 63          | 73          |

| I/O93(A)             | I/O115(A)             | I/O104(A)             | I/O194(A)             | 36           | 29          | 56          | 43          | P4                 | 64          | 74          |

| -                    | -                     | -                     | I/O193(B)             | -            | -           | -           | -           | -                  | -           | 75          |

| -                    | -                     | -                     | I/O192(A)             | -            | -           | -           | -           | P5                 | 65          | 76          |

| I/O92(B)             | I/O114(B)             | I/O103(A)             | I/O191(A)             | -            | 30          | 57          | 44          | P6                 | 66          | 77          |

| I/O91(A) or<br>CHECK | I/O113(A) or CHECK    | I/O102(A) or CHECK    | I/O190(A) or CHECK    | 37           | 31          | 58          | 45          | P7                 | 67          | 78          |

| -                    | -                     | -                     | I/O189(B)             | -            | -           | -           | -           | -                  | -           | 79          |

| I/O90(B)             | I/O112(B)             | I/O101(A)             | I/O188(A)             | -            | -           | 59          | 46          | N4                 | 68          | 80          |

| I/O89(A) or<br>ERR   | I/O111(A) or<br>ERR   | I/O100(A) or<br>ERR   | I/O187(A) or<br>ERR   | 38           | 32          | 60          | 47          | N5                 | 69          | 81          |

| I/O88(B)             | I/O110(B)             | I/O99(A)              | I/O186(A)             | -            | 33          | 61          | 48          | N6                 | 70          | 82          |

| -                    | -                     | -                     | I/O185(B)             | -            | -           | -           | -           | -                  | 71          | 83          |

| I/O87(A)             | I/O109(A)             | I/O98(A)              | I/O184(A)             | 39           | 34          | 62          | 49          | N7                 | 72          | 84          |

| -                    | I/O108(B)             | I/O97(A)              | I/O183(A)             | -            | -           | 63          | 50          | M8                 | 73          | 85          |

| GND                  | GND                   | GND                   | GND                   | 40           | 35          | 64          | 51          | GND <sup>(2)</sup> | 74          | 86          |

| I/O86(A)             | I/O107(A)             | I/O96(A)              | I/O182(A)             | 41           | 36          | 65          | 52          | M9                 | 75          | 87          |

| -                    | -                     | -                     | I/O181(B)             | -            | -           | -           | -           | -                  | 76          | 88          |

| -                    | I/O106(B)             | -                     | I/O180(A)             | -            | -           | -           | 53          | M10                | 77          | 89          |

| I/O85(A)             | I/O105(A)             | I/O95(A)              | I/O179(A)             | 42           | 37          | 66          | 54          | M11                | 78          | 90          |

| CS                   | CS                    | CS                    | CS                    | 43           | 38          | 67          | 55          | L8                 | 79          | 91          |

| I/O84(B)             | I/O104(A)             | I/O94(A)              | I/O178(A)             | 44           | 39          | 68          | 56          | M12                | 80          | 92          |

| -                    | -                     | -                     | I/O177(B)             | -            | -           | -           | -           | -                  | 81          | 93          |

| I/O83(A)             | I/O103(A)             | I/O93(A)              | I/O176(A)             | 45           | 40          | 69          | 57          | N8                 | 82          | 94          |

## **Pinout Assignment (Continued)**

|          |           |          | Bottom Side ( | Left to Right | )           |             |             |                    |             |             |

|----------|-----------|----------|---------------|---------------|-------------|-------------|-------------|--------------------|-------------|-------------|

| AT6002   | AT6003    | AT6005   | AT6010        | 84<br>PLCC    | 100<br>VQFP | 132<br>PQFP | 144<br>TQFP | 180<br>CPGA        | 208<br>PQFP | 240<br>PQFP |

| -        | -         | -        | VDD           | -             | -           | -           | -           | PWR <sup>(1)</sup> | 83          | 95          |

| VCC      | VCC       | vcc      | VCC           | 46            | 41          | 70          | 58          | PWR <sup>(1)</sup> | 84          | 96          |

| I/O82(A) | I/O102(A) | I/O92(A) | I/O175(A)     | 47            | 42          | 71          | 59          | N11                | 85          | 97          |

| I/O81(B) | I/O101(B) | I/O91(A) | I/O174(A)     | -             | -           | 72          | 60          | N12                | 86          | 98          |

| -        | -         | -        | I/O173(B)     | -             | -           | -           | -           | -                  | 87          | 99          |

| I/O80(A) | I/O100(A) | I/O90(A) | I/O172(A)     | 48            | 43          | 73          | 61          | N13                | 88          | 100         |

| I/O79(B) | I/O99(B)  | I/O89(A) | I/O171(A)     | -             | 44          | 74          | 62          | P8                 | 89          | 101         |

| -        | -         | -        | I/O170(A)     | -             | -           | -           | -           | P9                 | 90          | 102         |

| -        | -         | -        | I/O169(B)     | -             | -           | -           | -           | -                  | -           | 103         |

| I/O78(A) | I/O98(A)  | I/O88(A) | I/O168(A)     | 49            | 45          | 75          | 63          | P10                | 91          | 104         |

| -        | I/O97(B)  | I/O87(A) | I/O167(A)     | -             | -           | 76          | 64          | P11                | 92          | 105         |

| -        | -         | -        | I/O166(A)     | -             | -           | -           | -           | P12                | 93          | 106         |

| GND      | GND       | GND      | GND           | -             | -           | 77          | 65          | GND <sup>(2)</sup> | 94          | 107         |

| -        | -         | -        | I/O165(B)     | -             | -           | -           | -           | -                  | -           | 108         |

| I/O77(A) | I/O96(A)  | I/O86(A) | I/O164(A)     | 50            | 46          | 78          | 66          | P13                | 95          | 109         |

| I/O76(B) | I/O95(B)  | I/O85(A) | I/O163(A)     | -             | 47          | 79          | 67          | P14                | 96          | 110         |

| -        | -         | -        | I/O162(A)     | -             | -           | -           | -           | P8                 | 97          | 111         |

| -        | -         | -        | I/O161(B)     | -             | _           | -           | -           | -                  | -           | 112         |

| I/O75(A) | I/O94(A)  | I/O84(A) | I/O160(A)     | 51            | 48          | 80          | 68          | R9                 | 98          | 113         |

| I/O74(B) | I/O93(A)  | I/O83(A) | I/O159(A)     | -             | -           | 81          | 69          | R10                | 99          | 114         |

| -        | -         | -        | I/O158(A)     | -             | -           | -           | -           | R11                | 100         | 115         |

| -        | -         | -        | I/O157(B)     | -             | -           | -           | -           | -                  | -           | 116         |

| -        | I/O92(B)  | -        | I/O156(A)     | -             | -           | -           | 70          | R12                | 101         | 117         |

| I/O73(A) | I/O91(A)  | I/O82(A) | I/O155(A)     | 52            | 49          | 82          | 71          | R13                | 102         | 118         |

| -        | -         | -        | I/O154(A)     | -             | -           | -           | -           | R14                | 103         | 119         |

| RESET    | RESET     | RESET    | RESET         | 53            | 50          | 83          | 72          | R15                | 104         | 120         |

Notes: 1. PWR = Pins connected to power plane = F1, E4/E5, L2, R4, K15, L12, E14, A12.

<sup>2.</sup> GND = Pins connected to ground plane = L4, M4, N9, N10, E12, D12, C7, C6.

# **Pinout Assignment**

|          |          |          | Right Side (Bo | ottom to Top | )           |                   |             |                    |             |             |

|----------|----------|----------|----------------|--------------|-------------|-------------------|-------------|--------------------|-------------|-------------|

| AT6002   | AT6003   | AT6005   | AT6010         | 84<br>PLCC   | 100<br>VQFP | 132<br>PQFP       | 144<br>TQFP | 180<br>CPGA        | 208<br>PQFP | 240<br>PQFP |

| -        | -        | -        | I/O153(A)      | -            | -           | -                 | -           | P15                | 105         | 121         |

| I/O72(A) | I/O90(A) | I/O81(A) | I/O152(A)      | 54           | 51          | 84                | 73          | N15                | 106         | 122         |

| -        | I/O89(B) | I/O80(A) | I/O151(A)      | -            | -           | 85 <sup>(3)</sup> | 74          | M15                | 107         | 123         |

| -        | -        | -        | I/O150(B)      | -            | -           | -                 | -           | -                  | -           | 124         |

| -        | -        | -        | vcc            | -            | -           | -                 | -           | PWR <sup>(1)</sup> | 108         | 125         |

| -        | -        | -        | I/O149(A)      | -            | -           | -                 | -           | L15                | 109         | 126         |

| -        | -        | -        | GND            | -            | -           | -                 | -           | GND <sup>(2)</sup> | 110         | 127         |

| -        | I/O88(A) | -        | I/O148(A)      | -            | -           | 85 <sup>(4)</sup> | 75          | J15                | 111         | 128         |

| I/O71(A) | I/O87(A) | I/O79(A) | I/O147(A)      | 55           | 52          | 86                | 76          | H15                | 112         | 129         |

| -        | -        | -        | I/O146(B)      | -            | -           | -                 | -           | -                  | -           | 130         |

| -        | -        | -        | I/O145(A)      | -            | -           | -                 | -           | N14                | 113         | 131         |

| I/O70(B) | I/O86(A) | I/O78(A) | I/O144(A)      | -            | -           | 87                | 77          | M14                | 114         | 132         |

| I/O69(A) | I/O85(A) | I/O77(A) | I/O143(A)      | 56           | 53          | 88                | 78          | L14                | 115         | 133         |

| -        | -        | -        | I/O142(B)      | -            | -           | -                 | -           | -                  | -           | 134         |

| -        | -        | -        | I/O141(A)      | -            | -           | -                 | -           | K14                | 116         | 135         |

| I/O68(B) | I/O84(B) | I/O76(A) | I/O140(A)      | -            | 54          | 89                | 79          | J14                | 117         | 136         |

| I/O67(A) | I/O83(A) | I/O75(A) | I/O139(A)      | 57           | 55          | 90                | 80          | H14                | 118         | 137         |

| -        | -        | -        | I/O138B        | -            | -           | -                 | -           | -                  | -           | 138         |

| I/O66(B) | I/O82(B) | I/O74(A) | I/O137(A)      | -            | -           | 91                | 81          | M13                | 119         | 139         |

| I/O65(A) | I/O81(A) | I/O73(A) | I/O136(A)      | 58           | 56          | 92                | 82          | L13                | 120         | 140         |

| I/O64(B) | I/O80(B) | I/O72(A) | I/O135(A)      | -            | 57          | 93                | 83          | K13                | 121         | 141         |

| -        | -        | -        | I/O134(B)      | -            | -           | -                 | -           | -                  | 122         | 142         |

| I/O63(A) | I/O79(A) | I/O71(A  | I/O133(A)      | 59           | 58          | 94                | 84          | J13                | 123         | 143         |

| -        | I/O78(B) | I/O70(A) | I/O132(A)      | -            | -           | 95                | 85          | H13                | 124         | 144         |

| GND      | GND      | GND      | GND            | 60           | 59          | 96                | 86          | GND <sup>(2)</sup> | 125         | 145         |

| VSS      | VSS      | VSS      | VSS            | 61           | 60          | 97                | 87          | GND <sup>(2)</sup> | 126         | 146         |

| I/O62(A) | I/O77(A) | I/O69(A) | I/O131(A)      | 62           | 61          | 98                | 88          | K12                | 127         | 147         |

| -        | -        | -        | I/O130(B)      | -            | -           | -                 | -           | -                  | 128         | 148         |

| -        | I/O76(B) | -        | I/O129(A)      | -            | -           | -                 | 89          | J12                | 129         | 149         |

| I/O61(A) | I/O75(A) | I/O68(A) | I/O128(A)      | 63           | 62          | 99                | 90          | H12                | 130         | 150         |

| I/O60(B) | I/O74(A) | I/O67(A) | I/O127(A)      | 64           | 63          | 100               | 91          | H11                | 131         | 151         |

| -        | -        | -        | I/O126(B)      | -            | -           | -                 | -           | -                  | 132         | 152         |

| I/O59(A) | I/O73(A) | I/O66(A) | I/O125(A)      | 65           | 64          | 101               | 92          | G12                | 133         | 153         |

| I/O58(A) | I/O72(A) | I/O65(A) | I/O124(A)      | 66           | 65          | 102               | 93          | F12                | 134         | 154         |

| VDD      | VDD      | VDD      | VDD            | 67           | 66          | 103               | 94          | PWR <sup>(1)</sup> | 135         | 155         |

| VCC      | vcc      | vcc      | VCC            | 68           | 67          | 104               | 95          | PWR <sup>(1)</sup> | 136         | 156         |

## **Pinout Assignment (Continued)**

|          |          |          | Right Side (Be | ottom to Top | )           |             |             |                    |             |             |

|----------|----------|----------|----------------|--------------|-------------|-------------|-------------|--------------------|-------------|-------------|

| AT6002   | AT6003   | AT6005   | AT6010         | 84<br>PLCC   | 100<br>VQFP | 132<br>PQFP | 144<br>TQFP | 180<br>CPGA        | 208<br>PQFP | 240<br>PQFP |

| I/O57(B) | I/O71(B) | I/O64(A) | I/O123(A)      | -            | -           | 105         | 96          | G13                | 137         | 157         |

| -        | -        | -        | I/O122(B)      | -            | -           | -           | -           | -                  | 138         | 158         |

| I/O56(A) | I/O70(A) | I/O63(A) | I/O121(A)      | 69           | 68          | 106         | 97          | F13                | 139         | 159         |

| I/O55(B) | I/O69(B) | I/O62(A) | I/O120(A)      | -            | 69          | 107         | 98          | E13                | 140         | 160         |

| -        | -        | -        | I/O119(A)      | -            | -           | -           | -           | D13                | 141         | 161         |

| -        | -        | -        | I/O118(B)      | -            | -           | -           | -           | -                  | -           | 162         |

| I/O54(A) | I/O68(A) | I/O61(A) | I/O117(A)      | 70           | 70          | 108         | 99          | C13                | 142         | 163         |

| -        | I/O67(B) | I/O60(A) | I/O116(A)      | -            | -           | 109         | 100         | G14                | 143         | 164         |

| -        | -        | -        | I/O115(A)      | -            | -           | -           | -           | F14                | 144         | 165         |

| GND      | GND      | GND      | GND            | -            | -           | 110         | 101         | GND <sup>(2)</sup> | 145         | 166         |

| -        | -        | -        | VSS            | -            | -           | -           | -           | GND <sup>(2)</sup> | 146         | 167         |

| -        | -        | -        | I/O114(B)      | -            | -           | -           | -           | -                  | -           | 168         |

| I/O53(A) | I/O66(A) | I/O59(A) | I/O113(A)      | 71           | 71          | 111         | 102         | D14                | 147         | 169         |

| I/O52(B) | I/O65(B) | I/O58(A) | I/O112(A)      | -            | 72          | 112         | 103         | C14                | 148         | 170         |

| -        | -        | -        | I/O111(A)      | -            | -           | -           | -           | B14                | 149         | 171         |

| -        | -        | -        | I/O110(B)      | -            | -           | -           | -           | -                  | -           | 172         |

| I/O51(A) | I/O64(A) | I/O57(A) | I/O109(A)      | 72           | 73          | 113         | 104         | G15                | 150         | 173         |

| I/O50(B) | I/O63(A) | I/O56(A) | I/O108(A)      | -            | -           | 114         | 105         | F15                | 151         | 174         |

| -        | -        | -        | I/O107(A)      | -            | -           | -           | -           | E15                | 152         | 175         |

| -        | -        | -        | I/O106(B)      | -            | -           | -           | -           | -                  | -           | 176         |

| -        | I/O62(B) | -        | I/O105(A)      | -            | -           | -           | 106         | D15                | 153         | 177         |

| I/O49(A) | I/O61(A) | I/O55(A) | I/O104(A)      | 73           | 74          | 115         | 107         | C15                | 154         | 178'        |

| -        | -        | -        | I/O103(A)      | -            | -           | -           | -           | B15                | 155         | 179         |

| M2       | M2       | M2       | M2             | 74           | 75          | 116         | 108         | A15                | 156         | 180         |

Notes: 1. PWR = Pins connected to power plane = F1, E4/E5, L2, R4, K15, L12, E14, A12.

<sup>2.</sup> GND = Pins connected to ground plane = L4, M4, N9, N10, E12, D12, C7, C6.

<sup>3.</sup> 85 = Pin 85 on AT6005.

<sup>4. 85 =</sup> Pin 85 on AT6003 and AT6010.

# **Pinout Assignment**

|                 |                 |                 | Top Side (Righ  | t to Left) |             |             |             |                    |             |             |

|-----------------|-----------------|-----------------|-----------------|------------|-------------|-------------|-------------|--------------------|-------------|-------------|

| AT6002          | AT6003          | AT6005          | AT6010          | 84<br>PLCC | 100<br>VQFP | 132<br>PQFP | 144<br>TQFP | 180<br>CPGA        | 208<br>PQFP | 240<br>PQFP |

| M1              | M1              | M1              | M1              | 75         | 76          | 117         | 109         | D11                | 157         | 181         |

| -               | -               | -               | I/O102(A)       | -          | -           | -           | -           | D10                | 158         | 182         |

| I/O48(A)        | I/O60(A)        | I/O54(A)        | I/O101(A)       | 76         | 77          | 118         | 110         | D9                 | 159         | 183         |

| -               | I/O59(B)        | -               | I/O100(A)       | -          | -           | -           | 111         | A14                | 160         | 184         |

| -               | -               | -               | I/O99(B)        | -          | -           | -           | -           | -                  | -           | 185         |

| -               | -               | -               | VCC             | -          | -           | -           | -           | PWR <sup>(1)</sup> | 161         | 186         |

| -               | -               | -               | I/O98(A)        | -          | -           | -           | -           | A13                | 162         | 187         |

| -               | -               | -               | GND             | -          | -           | -           | -           | GND <sup>(2)</sup> | 163         | 188         |

| -               | I/O58(A)        | I/O53(A)        | I/O97(A)        | -          | -           | 119         | 112         | A11                | 164         | 189         |

| I/O47(A)        | I/O57(A)        | I/O52(A)        | I/O96(A)        | 77         | 78          | 120         | 113         | A10                | 165         | 190         |

| -               | -               | -               | I/O95(B)        | -          | -           | -           | -           | -                  | -           | 191         |

| -               | -               | -               | I/O94(A)        | -          | -           | -           | -           | A9                 | 166         | 192         |

| I/O46(B)        | I/O56(A)        | I/O51(A)        | I/O93(A)        | -          | -           | 121         | 114         | B13                | 167         | 193         |

| I/O45(A)        | I/O55(A)        | I/O50(A)        | I/O92(A)        | 78         | 79          | 122         | 115         | B12                | 168         | 194         |

| -               | -               | -               | I/O91(B)        | -          | -           | -           | -           | -                  | -           | 195         |

| -               | -               | -               | I/O90(A)        | -          | -           | -           | -           | B11                | 169         | 196         |

| I/O44(B)        | I/O54(B)        | I/O49(A)        | I/O89(A)        | -          | 80          | 123         | 116         | B10                | 170         | 197         |

| I/O43(A)        | I/O53(A)        | I/O48(A)        | I/O88(A)        | 79         | 81          | 124         | 117         | В9                 | 171         | 198         |

| -               | -               | -               | I/O87(B)        | -          | -           | -           | -           | -                  | -           | 199         |

| I/O42(B)        | I/O52(B)        | I/O47(A)        | I/O86(A)        | -          | -           | 125         | 118         | C12                | 172         | 200         |

| I/O41(A)        | I/O51(A)        | I/O46(A)        | I/O85(A)        | 80         | 82          | 126         | 119         | C11                | 173         | 201         |

| I/O40(B)        | I/O50(B)        | I/O45(A)        | I/O84(A)        | -          | 83          | 127         | 120         | C10                | 174         | 202         |

| -               | -               | -               | I/O83(B)        | -          | -           | -           | -           | -                  | 175         | 203         |

| I/O39(A)        | I/O49(A)        | I/O44(A)        | I/O82(A)        | 81         | 84          | 128         | 121         | C9                 | 176         | 204         |

| -               | I/O48(B)        | I/O43(A)        | I/O81(A)        | -          | -           | 129         | 122         | D8                 | 177         | 205         |

| GND             | GND             | GND             | GND             | 82         | 85          | 130         | 123         | GND <sup>(2)</sup> | 178         | 206         |

| I/O38(A)        | I/O47(A)        | I/O42(A)        | I/O80(A)        | 83         | 86          | 131         | 124         | D7                 | 179         | 207         |

| -               | -               | -               | I/O79(B)        | -          | -           | -           | -           | -                  | 180         | 208         |

| -               | I/O46(B)        | -               | I/O78(A)        | -          | -           | -           | 125         | D6                 | 181         | 209         |

| I/O37(A) or A16 | I/O45(A) or A16 | I/O41(A) or A16 | I/O77(A) or A16 | 84         | 87          | 132         | 126         | D5                 | 182         | 210         |

| CLOCK           | CLOCK           | CLOCK           | CLOCK           | 1          | 88          | 1           | 127         | E8                 | 183         | 211         |

| I/O36(B) or A15 | I/O44(B) or A15 | I/O40(A) or A15 | I/O76(A) or A15 | 2          | 89          | 2           | 128         | D4                 | 184         | 212         |

| -               | -               | -               | I/O75(B)        | -          | -           | -           | -           | -                  | 185         | 213         |

| I/O35(A) or A14 | I/O43(A) or A14 | I/O39(A) or A14 | I/O74(A) or A14 | 3          | 90          | 3           | 129         | C8                 | 186         | 214         |

| -               | -               | -               | VDD             | -          | -           | -           | -           | PWR <sup>(1)</sup> | 187         | 215         |

| VCC             | VCC             | VCC             | VCC             | 4          | 91          | 4           | 130         | PWR <sup>(1)</sup> | 188         | 216         |

## **Pinout Assignment (Continued)**

|                 |                 |                 | Top Side (Righ  | t to Left) |             |             |             |                    |             |             |

|-----------------|-----------------|-----------------|-----------------|------------|-------------|-------------|-------------|--------------------|-------------|-------------|

| AT6002          | AT6003          | AT6005          | AT6010          | 84<br>PLCC | 100<br>VQFP | 132<br>PQFP | 144<br>TQFP | 180<br>CPGA        | 208<br>PQFP | 240<br>PQFP |

| I/O34(A) or A13 | I/O42(A) or A13 | I/O38(A) or A13 | I/O73(A) or A13 | 5          | 92          | 5           | 131         | C5                 | 189         | 217         |

| I/O33(B)        | I/O41(B)        | I/O37(A)        | I/O72(A)        | -          | -           | 6           | 132         | C4                 | 190         | 218         |

| -               | -               | -               | I/O71(B)        | -          | -           | -           | -           | -                  | 191         | 219         |

| I/O32(A) or A12 | I/O40(A) or A12 | I/O36(A) or A12 | I/O70(A) or A12 | 6          | 93          | 7           | 133         | С3                 | 192         | 220         |

| I/O31(B)        | I/O39(B)        | I/O35(A)        | I/O69(A)        | -          | 94          | 8           | 134         | В8                 | 193         | 221         |

| -               | -               | -               | I/O68(A)        | -          | -           | -           | -           | В7                 | 194         | 222         |

| -               | -               | -               | I/O67(B)        | -          | -           | -           | -           | -                  | -           | 223         |

| I/O30(A) or A11 | I/O38(A) or A11 | I/O34(A) or A11 | I/O66(A) or A11 | 7          | 95          | 9           | 135         | В6                 | 195         | 224         |

| -               | I/O37(B)        | I/O33(A)        | I/O65(A)        | -          | -           | 10          | 136         | B5                 | 196         | 225         |

| -               | -               | -               | I/O64(A)        | -          | -           | -           | -           | B4                 | 197         | 226         |

| GND             | GND             | GND             | GND             | -          | -           | 11          | 137         | GND <sup>(2)</sup> | 198         | 227         |

| -               | -               | -               | I/O63(B)        | -          | -           | -           | -           | -                  | -           | 228         |

| I/O29(A) or A10 | I/O36(A) or A10 | I/O32(A) or A10 | I/O62(A) or A10 | 8          | 96          | 12          | 138         | В3                 | 199         | 229         |

| I/O28(B)        | I/O35(B)        | I/O31(A)        | I/O61(A)        | -          | 97          | 13          | 139         | B2                 | 200         | 230         |

| -               | -               | -               | I/O60(A)        | -          | -           | -           | -           | A8                 | 201         | 231         |

| -               | -               | -               | I/O59(B)        | -          | -           | -           | -           | -                  | -           | 232         |

| I/O27(A) or A9  | I/O34(A) or A9  | I/O30(A) or A9  | I/O58(A) or A9  | 9          | 98          | 14          | 140         | A7                 | 202         | 233         |

| I/O26(B)        | I/O33(A)        | I/O29(A)        | I/O57(A)        | -          | -           | 15          | 141         | A6                 | 203         | 234         |

| -               | -               | -               | I/O56(A)        | -          | -           | -           | -           | A5                 | 204         | 235         |

| -               | -               | -               | I/O55(B)        | -          | -           | -           | -           | -                  | -           | 236         |

| -               | I/O32(B)        | -               | I/O54(A)        | -          | -           | -           | 142         | A4                 | 205         | 237         |

| I/O25(A) or A8  | I/O31(A) or A8  | I/O28(A) or A8  | I/O53(A) or A8  | 10         | 99          | 16          | 143         | А3                 | 206         | 238         |

| -               | -               | -               | I/O52(A)        | -          | -           | -           | -           | A2                 | -207        | 239         |

| MO              | МО              | MO              | MO              | 11         | 100         | 17          | 144         | A1                 | 208         | 240         |

Notes: 1. PWR = Pins connected to power plane = F1, E4/E5, L2, R4, K15, L12, E14, A12.

<sup>2.</sup> GND = Pins connected to ground plane = L4, M4, N9, N10, E12, D12, C7, C6.

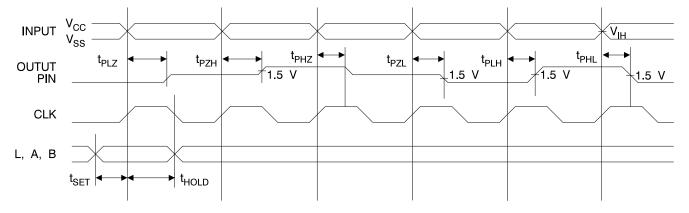

## **AC Timing Characteristics – 5V Operation**

Delays are based on fixed load. Loads for each type of device are described in the notes. Delays are in nanoseconds. Worst case:  $V_{CC} = 4.75V$  to 5.25V. Temperature = 0°C to 70°C.

| Cell Function                 | Parameter                            | From        | То      | Load<br>Definition <sup>(7)</sup> | -1  | -2  | -4   | Units |

|-------------------------------|--------------------------------------|-------------|---------|-----------------------------------|-----|-----|------|-------|

| Wire <sup>(4)</sup>           | t <sub>PD</sub> (max) <sup>(4)</sup> | A, B, L     | A, B    | 1                                 | 0.8 | 1.2 | 1.8  | ns    |

| NAND                          | t <sub>PD</sub> (max)                | A, B, L     | В       | 1                                 | 1.6 | 2.2 | 3.2  | ns    |

| XOR                           | t <sub>PD</sub> (max)                | A, B, L     | Α       | 1                                 | 1.8 | 2.4 | 4.0  | ns    |

| AND                           | t <sub>PD</sub> (max)                | A, B, L     | В       | 1                                 | 1.7 | 2.2 | 3.2  | ns    |

| NALLY.                        | 4 ()                                 | A, B        | Α       | 1                                 | 1.7 | 2.3 | 4.0  | ns    |

| MUX                           | t <sub>PD</sub> (max)                | L           | Α       | 1                                 | 2.1 | 3.0 | 4.9  | ns    |

| D-Flip-flop <sup>(5)</sup>    | t <sub>setup</sub> (min)             | A, B, L     | CLK     | -                                 | 1.5 | 2.0 | 3.0  | ns    |

| D-Flip-flop <sup>(5)</sup>    | t <sub>hold</sub> (min)              | CLK         | A, B, L | -                                 | 0   | 0   | 0    | ns    |

| D-Flip-flop                   | t <sub>PD</sub> (max)                | CLK         | Α       | 1                                 | 1.5 | 2.0 | 3.0  | ns    |

| Bus Driver                    | t <sub>PD</sub> (max)                | A           | L       | 2                                 | 2.0 | 2.6 | 4.0  | ns    |

| Deposter                      | 4 (222)                              | L, E        | E       | 3                                 | 1.3 | 1.6 | 2.3  | ns    |

| Repeater                      | t <sub>PD</sub> (max)                | L, E        | L       | 2                                 | 1.7 | 2.1 | 3.0  | ns    |

| Column Clock                  | t <sub>PD</sub> (max)                | GCLK, A, ES | CLK     | 3                                 | 1.8 | 2.4 | 3.0  | ns    |

| Column Reset                  | t <sub>PD</sub> (max)                | GRES, A, EN | RES     | 3                                 | 1.8 | 2.4 | 3.0  | ns    |

| Clock Buffer <sup>(5)</sup>   | t <sub>PD</sub> (max)                | CLOCK PIN   | GCLK    | -                                 | 1.6 | 2.0 | 2.9  | ns    |

| Reset Buffer <sup>(5)</sup>   | t <sub>PD</sub> (max)                | RESET PIN   | GRES    | -                                 | 1.5 | 1.9 | 2.8  | ns    |

| TTL Input <sup>(1)</sup>      | t <sub>PD</sub> (max)                | I/O         | Α       | 3                                 | 1.0 | 1.2 | 1.5  | ns    |

| CMOS Input <sup>(2)</sup>     | t <sub>PD</sub> (max)                | I/O         | Α       | 3                                 | 1.3 | 1.4 | 2.3  | ns    |

| Fast Output <sup>(3)</sup>    | t <sub>PD</sub> (max)                | A           | I/O PIN | 4                                 | 3.3 | 3.5 | 6.0  | ns    |

| Slow Output <sup>(3)</sup>    | t <sub>PD</sub> (max)                | A           | I/O PIN | 4                                 | 7.5 | 8.0 | 12.0 | ns    |

| Output Disable <sup>(5)</sup> | t <sub>PXZ</sub> (max)               | L           | I/O PIN | 4                                 | 3.1 | 3.3 | 5.5  | ns    |

| Fast Enable <sup>(3)(5)</sup> | t <sub>PXZ</sub> (max)               | L           | I/O PIN | 4                                 | 3.8 | 4.0 | 6.5  | ns    |

| Slow Enable <sup>(3)(5)</sup> | t <sub>PXZ</sub> (max)               | L           | I/O PIN | 4                                 | 8.2 | 8.5 | 12.5 | ns    |

| Device                      | Cell Types                                   | Outputs | I <sub>CC</sub> (max) |

|-----------------------------|----------------------------------------------|---------|-----------------------|

| Cell <sup>(6)</sup>         | Wire, XWire, Half-adder, Flip-flop           | A, B    | 4.5 µA/MHz            |

| Bus <sup>(6)</sup>          | Wire, XWire, Half-adder, Flip-flop, Repeater | L       | 2.5 µA/MHz            |

| Column Clock <sup>(6)</sup> | Column Clock Driver                          | CLK     | 40 μA/MHz             |

Notes:

- 1. TTL buffer delays are measured from a  $V_{IH}$  of 1.5V at the pad to the internal  $V_{IH}$  at A. The input buffer load is constant.

- 2. CMOS buffer delays are measured from a  $V_{IH}$  of 1/2  $V_{CC}$  at the apd to the internal  $V_{IH}$  at A. The input buffer load is constant.

- 3. Buffer delay is to a pad voltage of 1.5V with one output switching.

- 4. Max specifications are the average of mas  $t_{PDLH}$  and  $t_{PDHL}$ .

- 5. Parameter based on characterization and simulation; not tested in production

- 6. Exact power calculation is available in an Atmel application note.

- 7. Load Definition: 1 = Load of one A or B input; 2 = Load of one L input; 3 = Constant Load; 4 = Tester Load of 50 pF.

## AC Timing Characteristics – 3.3V Operation

Delays are based on fixed load. Loads for each type of device are described in the notes. Delays are in nanoseconds. Worst case:  $V_{CC} = 3.0V$  to 3.6V. Temperature = 0°C to 70°C.

| Cell Function                 | Parameter                            | From        | То      | Load<br>Definition <sup>(7)</sup> | -4   | Units |