#### PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

932SQ420D

### **General Description**

The 932SQ420D is a main clock synthesizer for Romley-generation Intel based server platforms. The 932SQ420D is driven with a 25 MHz crystal for maximum performance. It generates CPU outputs of 100 or 133.33 MHz.

### **Recommended Application**

CK420BQ

### **Output Features**

- 4 HCSL CPU outputs

- 4 HCSL Non-Spread SAS/SRC outputs

- 3 HCSL SRC outputs

- 1 HCSL DOT96 output

- 1 3.3V 48M output

- 5 3.3V PCI outputs

- 1-3.3V REF output

#### Features/Benefits

- 0.5% down spread capable on CPU/SRC/PCI outputs/Lower EMI

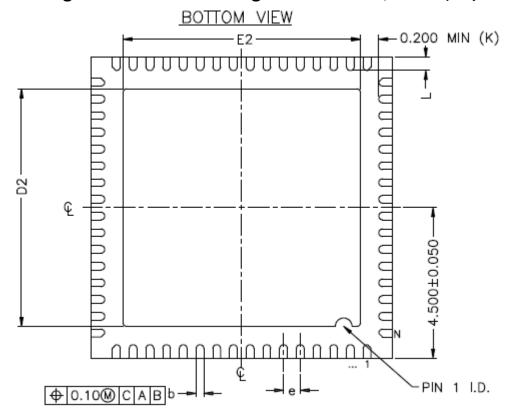

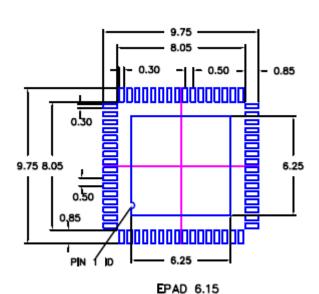

- 64-pin TSSOP and MLF packages/Space Savings

### **Key Specifications**

- Cycle to cycle jitter: CPU/SRC/NS\_SRC/NS\_SAS < 50ps.</li>

- Phase jitter: PCle Gen2 < 3ps rms, Gen3 < 1ps rms</li>

- Phase jitter: QPI 9.6GB/s < 0.2ps rms

- Phase jitter: NS-SAS < 0.4ps rms using raw phase data

- Phase jitter: NS-SAS < 1.3ps rms using Clk Jit Tool 1.6.3

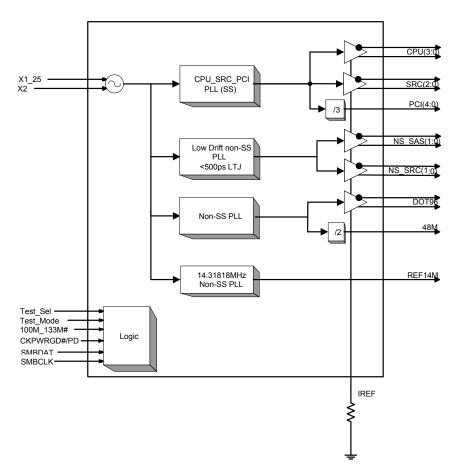

### **Block Diagram**

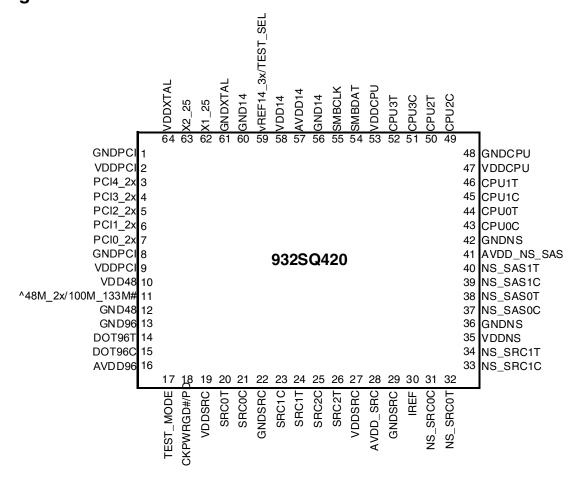

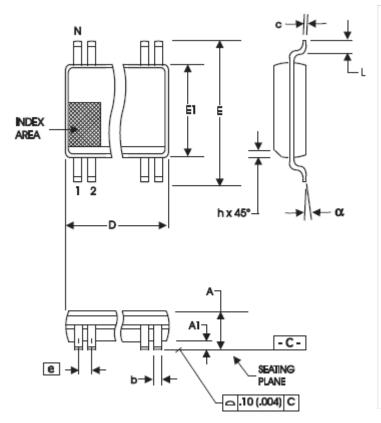

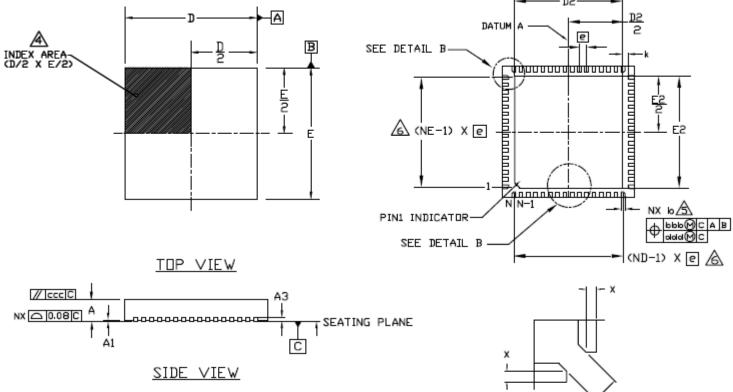

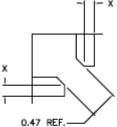

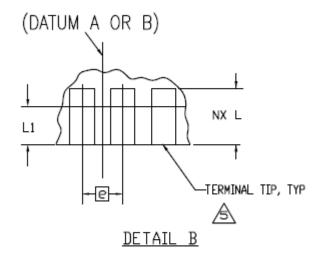

# Pin Configuration - 64TSSOP

| SMBCLK 1 GND14 2 AVDD14 3 VDD14 4  *REF14_3x/TEST_SEL 5 GND14 6 GNDXTAL 7                                                                                                |          | 64 SMBDAT 63 VDDCPU 62 CPU3T 61 CPU3C 60 CPU2T 59 CPU2C 58 GNDCPU                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------|

| X1_25 8<br>X2_25 9<br>VDDXTAL 10<br>GNDPCI 11<br>VDDPCI 12<br>PCI4_2x 13<br>PCI3_2x 14<br>PCI2_2x 15<br>PCI1_2x 16<br>PCI0_2x 17<br>GNDPCI 18<br>VDDPCI 19<br>VDD48 20   | 932SQ420 | 57 VDDCPU 56 CPU1T 55 CPU1C 54 CPU0T 53 CPU0C 52 GNDNS 51 AVDD_NS_SAS 50 NS_SAS1T 49 NS_SAS1C 48 NS_SAS0T 47 NS_SAS0C 46 GNDNS |

| ^48M_2x/100M_133M# 21<br>GND48 22<br>GND96 23<br>DOT96T 24<br>DOT96C 25<br>AVDD96 26<br>TEST_MODE 27<br>CKPWRGD#/PD 28<br>VDDSRC 29<br>SRC0T 30<br>SRC0C 31<br>GNDSRC 32 |          | 44 NS_SRC1T 43 NS_SRC1C 42 NS_SRC0T 41 NS_SRC0C 40 IREF 39 GNDSRC 38 AVDD_SRC 37 VDDSRC 36 SRC2T 35 SRC2C 34 SRC1T 33 SRC1C    |

|                                                                                                                                                                          | 64-TSSOP | ·                                                                                                                              |

Note: Pins with ^ prefix have internal 120K pullup Pins with v prefix have internal 120K pulldown

#### **Spread Spectrum Control**

| SS_Enable | CPU, SRC & |

|-----------|------------|

| (B1 b0)   | PCI        |

| 0         | OFF        |

| 1         | ON         |

#### **Power Group Pin Numbers**

| ML     | F   | TSSOP  |        | Description                                |  |

|--------|-----|--------|--------|--------------------------------------------|--|

| VDD    | GND | VDD    | GND    | Description                                |  |

| 57     | 56  | 3      | 2      | 14MHz PLL Analog                           |  |

| 58     | 60  | 4      | 6      | REF14M Output and Logic                    |  |

| 64     | 61  | 10     | 7      | 25MHz XTAL                                 |  |

| 2,9    | 1,8 | 12, 19 | 11, 18 | PCI Outputs and Logic                      |  |

| 10     | 12  | 20     | 22     | 48MHz Output and Logic                     |  |

| 16     | 13  | 26     | 23     | 96MHz PLL Analog, Output and Logic         |  |

| 19, 27 | 22  | 29, 37 | 32     | SRC Outputs and Logic                      |  |

| 28     | 29  | 38     | 39     | SRC PLL Analog                             |  |

| 35     | 36  | 45     | 46     | Non-Spreading Differential Outputs & Logic |  |

| 41     | 42  | 51     | 52     | NS-SAS/SRC PLL Analog                      |  |

| 47, 53 | 48  | 57,63  | 58     | CPU Outputs and Logic                      |  |

#### 932SQ420 Power Down Functionality

| CKPWRGD#/PD | Differential<br>Outputs | Single-ended<br>Outputs | Single ended<br>Outputs w/Latch |

|-------------|-------------------------|-------------------------|---------------------------------|

| 1           | HI-Z <sup>1</sup>       | Low                     | Low <sup>2</sup>                |

| 0           |                         | Running                 |                                 |

- Hi-Z on the differential outputs will result in both True and Complement being low due to the termination network

- 2. These outputs are Hi-Z after VDD is applied and before the first assertion of CKPWRGD#.

# **Pin Descriptions - 64 TSSOP**

| 1 SMBCLK IN Clock pin of SMBUS circuitry, 5V tolerant 2 GND14 PWR 3 AVDD14 PWR 4 VDD14 PWR 5 Count pin for 14MHz output and logic. 3 AVDD14 PWR 5 Count pin for 14MHz output and logic. 5 WREF14_3V/TEST_SEL 10 14.3 MHz reference cock. 3X drive strength as default / TEST_SEL latched input to enable Refer to Test Clarification Table. This pin has a weak (-120Kohm) internal pull down. 6 GND14 PWR Ground pin for 14MHz output and logic. 7 GNDXTAL PWR Ground pin for 14MHz output and logic. 8 X1_25 IN Crystal input, Norminally 250MHz. 9 X2_25 OUT Crystal input, Norminally 250MHz. 10 VDDXTAL PWR Ground pin for FOL outputs and logic. 11 GNDPCI PWR Ground pin for PCI outputs and logic. 12 VDDPCI PWR Ground pin for PCI outputs and logic. 13 PCI4_2x OUT 3.3V PCI dock output 14 PCI3_2x OUT 3.3V PCI dock output 15 PCI2_2x OUT 3.3V PCI dock output 16 PCI2_2x OUT 3.3V PCI dock output 17 PCI0_2x OUT 3.3V PCI dock output 18 GNDPCI PWR Ground pin for PCI outputs and logic. 19 VDDPCI PWR 3.3V PCI dock output 19 VDDPCI PWR 3.3V PCI dock output 10 PWR GROUND pWR G |       |                       |      |                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------|------|-----------------------------------------------------------------------------------------------------------------|

| 2 GND14 PWB Ground pin for 14MHz output and logic.  3 AVD14 PWB Power pin for 14MHz output and logic.  4 VDD14 PWB Power pin for 14MHz output and logic.  5 WREF14_3wTEST_SEL ID Refer to Tset Clarification Table. This pin has a weak (-120kohm) internal pull down.  6 GND14 PWB Ground pin for 14MHz output and logic.  7 GNDXTAL PWB Ground pin for 14MHz output and logic.  8 X1_25 IN Crystal input, Nominally 25.00MHz.  9 X2_25 OUT Crystal output, Nominally 25.00MHz.  10 VDDXTAL PWB 3.3V power for the crystal oscillator.  11 GNDPCI PWB 3.3V power for the CPI outputs and logic.  12 VDDPCI PWB 3.3V power for the PCI output and logic.  13 PCI4_2x OUT 3.3V PCI clock output  14 PCI3_2x OUT 3.3V PCI clock output  15 PCI2_2x OUT 3.3V PCI clock output  16 PCI1_2x OUT 3.3V PCI clock output  17 PCI0_2x OUT 3.3V PCI clock output  18 GNDPCI PWB Ground pin for PCI outputs and logic.  19 VDDPCI PWB Ground pin for PCI output and logic.  19 VDDPCI PWB 3.3V PCI clock output  10 PWB 3.3V PCI clock output  11 GNDPCI PWB 3.3V PCI clock output  12 PCI0_2x OUT 3.3V PCI clock output  13 PCI4_2x OUT 3.3V PCI clock output  14 PCI3_2x OUT 3.3V PCI clock output  15 PCI2_2x OUT 3.3V PCI clock output  16 PCI1_2x OUT 3.3V PCI clock output  17 PCI0_2x OUT 3.3V PCI clock output  18 GNDPCI PWB 3.3V power for the PCI outputs and logic.  19 VDDPCI PWB 3.3V power for the 48MHz output and logic.  20 VDD48 PWB Ground pin for PCI outputs and logic.  21 V48M_2x/100M_133M# I/O thresholds. This pin has a weak (-120Kom) internal pull up.  22 GND48 PWB 3.3V power for the 48MHz output and logic.  23 GND96 PWB 3.3V power for the 48MHz output and logic.  24 GND96 PWB 3.3V power for the 48MHz output and logic.  25 GND96 PWB 3.3V power for the 58MHz output and logic.  26 AVD96 PWB 3.3V power for the 58MHz output and logic.  27 TEST_MODE IN The 58MHz output and logic.  28 GND96 PWB 3.3V power for the 58MHz output and logic.  29 VDDSRC PWB 3.3V power for the 58MHz output and logic.  29 VDDSRC PWB 3.3V power for the 58MHz output and logic.  20 CKPWRGD#/PD IN The 58MHz  | PIN # | PIN NAME              | TYPE |                                                                                                                 |

| AVDD14 PWR Analog power pin for 14MHz PLL  VDD14 PWR Grower pin for 14MHz output and logic  NDFEF14_3WTEST_SEL  NDFEF14_3WTEST |       |                       |      |                                                                                                                 |

| VDD14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2     | GND14                 |      |                                                                                                                 |

| Secolar   Seco   | 3     | AVDD14                | PWR  | Analog power pin for 14MHz PLL                                                                                  |

| Second Color   Second Prices   | 4     | VDD14                 | PWR  | Power pin for 14MHz output and logic                                                                            |

| Hefer to 1 set Clantication 1 able. This pin has a weak (~120Kohm) internal pull down.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _     | DEETA OVEROT OF       | 1/0  | 14.318 MHz reference clock. 3X drive strength as default / TEST_SEL latched input to enable test mode.          |

| Tue clock of differential SRC output. These are current mode outputs. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.   SRCOT   SRC1T   SRC2T   SRC1T   SRC1T   SRC2T   | 5     | VREF14_3X/1ES1_SEL    | 1/0  | Refer to Test Clarification Table. This pin has a weak (~120Kohm) internal pull down.                           |

| Tue clock of differential SRC output. These are current mode outputs. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.   SRCOT   SRC1T   SRC2T   SRC1T   SRC1T   SRC2T   | 6     | GND14                 | PWR  | Ground pin for 14MHz output and logic.                                                                          |

| 8 X1_25 IN Crystal input, Nominally 25.00MHz. 9 X2_25 OUT Crystal output, Nominally 25.00MHz. 10 VDDXTAL PWB 3.3V power for the crystal oscillator. 11 GNDPCI PWR Ground pin for PCI outputs and logic. 12 VDDPCI PWR 3.3V power for the PCI outputs and logic. 13 PCI4_2x OUT 3.3V PCI clock output 14 PCI3_2x OUT 3.3V PCI clock output 15 PCI2_2x OUT 3.3V PCI clock output 16 PCI1_2x OUT 3.3V PCI clock output 17 PCI0_2x OUT 3.3V PCI clock output 18 GNDPCI PWR Ground pin for PCI outputs and logic. 19 VDDPCI PWR Ground pin for PCI outputs and logic. 20 VDD48 PWR 3.3V power for the PCI outputs and logic. 21 V48M_2x/100M_133M# PWR Ground pin for PCI outputs and logic. 22 GND48 PWR 3.3V power for the PCI output and logic. 23 GND96 PWR Ground pin for 48MHz output and logic. 24 GND96 PWR Ground pin for PMHz output and logic. 25 D0T96C OUT 17 Tue clock of differential 96MHz output. These are current mode outputs. These are current and external 3.3 ohm series resistors and 49.9 ohm shunt resistors are required for termination. 26 AVDD96 PWR 3.3V power for the 48/96MHz output. These are current mode outputs and external 30 hm series resistors and 49.9 ohm shunt resistors are required for termination. 26 CKPWRGD#/PD IN Resistors and 49.9 ohm shunt resistors are required for termination. 27 TEST_MODE PWR 3.3V power for the 5RC output and logic. 28 CKPWRGD#/PD IN S.3V power for the 5RC output and logic. 29 VDDSRC PWR 3.3V power for the 5RC output and logic. 31 SRCOT OUT GROUND SAC OUT Series are sell time input to select between Hi-Z and REF/N divider mode while in test Test Clarification Table. 32 GNDSRC PWR 3.3V power for the 5RC output. These are current mode outputs and external 30 Shm series resistors and 49.9 ohm shunt resistors are required for termination. 31 SRCOC OUT Gromplementary clock of differential SRC output. These are current mode outputs and external 33 Shm series resistors and 49.9 ohm shunt resistors are required for termination. 32 GNDSRC PWR Ground pin for SRC output. These are current mode outputs and external | 7     | GNDXTAL               |      |                                                                                                                 |

| 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8     |                       |      |                                                                                                                 |

| 10   VDDXTAL   PWR   3.3V power for the crystal oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |                       |      |                                                                                                                 |

| 11   GNDPCI   PWR   Ground pin for PCI outputs and logic   12   VDDPCI   PWR   3.3V power for the PCI outputs and logic   13   PCI4_2x   OUT   3.3V PCI dlock output   14   PCI3_2x   OUT   3.3V PCI dlock output   15   PCI2_2x   OUT   3.3V PCI dlock output   16   PCI1_2x   OUT   3.3V PCI dlock output   17   PCI0_2x   OUT   3.3V PCI dlock output   18   GNDPCI   PWR   Ground pin for PCI outputs and logic   19   VDDPCI   PWR   Ground pin for PCI outputs and logic   19   VDDPCI   PWR   3.3V power for the PCI outputs and logic   19   VDDPCI   PWR   3.3V power for the PCI outputs and logic   19   VDDPCI   PWR   3.3V power for the PCI outputs and logic   10   VDD48   PWR   3.3V power for the 48MHz output and logic   10   VDD48   PWR   3.3V power for the 48MHz output and logic   10   VDD48   PWR   3.3V power for the 48MHz output and logic   10   VDD48   PWR   Ground pin for PCI outputs and logic   10   VDD48   PWR   Ground pin for PCI output and logic   10   VDD48   PWR   Ground pin for DD796 output and logic   10   VDD48   PWR   Ground pin for DD796 output and logic   10   VDD48   PWR   Ground pin for DD796 output and logic   10   VDD49   PWR   3.3V power for the 48MHz output. These are current mode outputs. These are current mode outputs and extension   10   VDD49   PWR   3.3V power for the 48MHz output and logic   10   VDD49   PWR   3.3V power for the 48MHz output not select between Hi-Z and REF/N divider mode while in test rest California   10   VDD49   PWR   3.3V power for the 48MHz output self to sample latched inputs and allow the device to Power than 19   VDD59   PWR   3.3V power for the 48MHz output in the self the power    |       |                       |      |                                                                                                                 |

| 12   VDDPCI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |                       |      |                                                                                                                 |

| 13   PCI4 2x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -     |                       |      |                                                                                                                 |

| 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |                       |      | · · · · · · · · · · · · · · · · · · ·                                                                           |

| 15   PCIZ_2X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |                       |      | '                                                                                                               |

| 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       | _                     |      |                                                                                                                 |

| 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |                       |      |                                                                                                                 |

| 18    GNDPCI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -     | _                     |      |                                                                                                                 |

| 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       | _                     |      |                                                                                                                 |

| 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |                       |      |                                                                                                                 |

| 3.3V 48MHz output/ 3.3V tolerant CPU frequency select latched input pin. See ViiFS and Vinf thresholds. This pin has a weak (~120Kom) internal pull up.   1 = 100MHz, 0 = 133MHz operating frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |                       |      |                                                                                                                 |

| Alignment   Alig   | 20    | VDD48                 | PWR  | 3.3V power for the 48MHz output and logic                                                                       |

| 1 = 100MHz, 0 = 133MHz operating frequency 22 GND48 PWR Ground p in for 48MHz output and logic. 23 GND96 PWR Ground p in for 100T96 output and logic. 24 DOT96T 25 DOT96C 26 AVDD96 PWR 3.30 hm series resistors and 49.9 ohm shunt resistors are required for termination. 26 AVDD96 PWR 3.3V power for the 48/96MHz PLL and the 96MHz output and logic 27 TEST_MODE 28 CKPWRGD#/PD 29 VDDSRC 29 VDDSRC 29 VDDSRC 29 VDDSRC 29 VDDSRC 30 SRC0T 30 SRC0T 31 SRC0C 31 SRC1C 32 GNDSRC 33 SRC1C 34 SRC1C 35 SRC2C 36 OUTT 37 Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination. 36 SRC2C 37 TEST_MODE 38 CKPWRGD#/PD 40 TEST_MODE Is a real time input to select between Hi-Z and REF/N divider mode while in test Test Clarification Table. 39 CKPWRGD# is an active low input used to sample latched inputs and allow the device to Pow asynchronous active high input pin used to put the device into a low power state. The internal in a restopped. 39 SRC0T 40 True clock of differential SRC output. These are current mode outputs. These are current mode external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination. 30 SRC1C 31 SRC1C 42 Complementary clock of differential SRC output. These are current mode outputs and external 35 ohm series resistors and 49.9 ohm shunt resistors are required for termination. 30 SRC1C 31 SRC1C 52 Complementary clock of differential SRC output. These are current mode outputs and external 35 ohm series resistors and 49.9 ohm shunt resistors are required for termination. 36 SRC1C 53 Complementary clock of differential SRC output. These are current mode outputs and external 35 ohm series resistors and 49.9 ohm shunt resistors are required for termination. 37 True clock of differential SRC output. These are current mode outputs and external 35 ohm series resistors and 49.9 ohm shunt resistors are required for termination. 36 SRC2C 57 Complementary clock of differential SRC outpu | 0.4   | A40N4 0 /400N4 400N4# |      |                                                                                                                 |

| 22 GND48   PWR   Ground pin for 48MHz output and logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21    | ^48M_2x/100M_133M#    | 1/0  |                                                                                                                 |

| 23 GND96 PWR Ground pin for DOT96 output and logic.  True clock of differential 96MHz output. These are current mode outputs. These are current and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  25 DOT96C OUT Complementary clock of differential 96MHz output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  26 AVDD96 PWR 3.3V power for the 48/96MHz PLL and the 96MHz output and logic  27 TEST_MODE IN TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode while in test Test Clarification Table.  28 CKPWRGD#/PD IN asynchronous active high input pin used to sample latched inputs and allow the device to Pow asynchronous active high input pin used to put the device into a low power state. The internal are stopped.  29 VDDSRC PWR 3.3V power for the SRC outputs and logic  30 SRC0T OUT True clock of differential SRC output. These are current mode outputs. These are current mode external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  31 SRC0C OUT Complementary clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.  32 GNDSRC PWR Ground pin for SRC outputs and logic.  33 SRC1C OUT Complementary clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.  34 SRC1T OUT True clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  35 SRC2C OUT True clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  36 SRC2T True clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are |       |                       |      |                                                                                                                 |

| DOT96T  OUT True clock of differential 96MHz output. These are current mode outputs. These are current and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  DOT96C  OUT Complementary clock of differential 96MHz output. These are current mode outputs and ext series resistors and 49.9 ohm shunt resistors are required for termination.  PWR 3.3V power for the 48/96MHz PLL and the 96MHz output and logic  TEST_MODE  IN TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode while in test Test Clarification Table.  CKPWRGD#/PD  IN SHCOR PWR 3.3V power for the 48/96MHz PLL and the 96MHz output and logic  TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode while in test Test Clarification Table.  CKPWRGD#/PD  IN SHCOR PWR 3.3V power for the SRC output used to sample latched inputs and allow the device to Pow asynchronous active high input pin used to put the device into a low power state. The internal are stopped.  30 SRCOT  OUT True clock of differential SRC output. These are current mode outputs. These are current mode external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  31 SRCOC  OUT Complementary clock of differential SRC output. These are current mode outputs and external 33 SRCOC  OUT Series resistors and 49.9 ohm shunt resistors are required for termination.  32 GNDSRC  PWR Ground pin for SRC outputs and logic.  Complementary clock of differential SRC output. These are current mode outputs and external 34 SRCOC  OUT True clock of differential SRC output. These are current mode outputs and external 35 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  35 SRC2C  OUT Complementary clock of differential SRC output. These are current mode outputs and external 35 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  OUT True clock of differential SRC output. These are current mode outputs and external 36 ohm series resistors and 49.9 oh |       |                       |      |                                                                                                                 |

| DOT96C  DOT96C  DOT96C  OUT  Complementary clock of differential 96MHz output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  26 AVDD96  PWR 3.3V power for the 48/96MHz PLL and the 96MHz output and logic  TEST_MODE  IN TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode while in test Test Clarification Table.  CKPWRGD# is an active low input used to sample latched inputs and allow the device to Pow asynchronous active high input pin used to put the device into a low power state. The internal are stopped.  29 VDDSRC  PWR 3.3V power for the SRC outputs and logic  30 SRC0T  OUT  Complementary clock of differential SRC output. These are current mode outputs. These are current mode external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  31 SRC0C  OUT  Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  32 GNDSRC  PWR  Ground pin for SRC outputs and logic  Complementary clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.  33 SRC1C  OUT  Complementary clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.  34 SRC1T  OUT  Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  True clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.  True clock of differential SRC outpu | 23    | GND96                 | PWR  |                                                                                                                 |

| DOT96C  DOT Complementary clock of differential 96MHz output. These are current mode outputs and ext series resistors and 49.9 ohm shunt resistors are required for termination.  PWR 3.3V power for the 48/96MHz PLL and the 96MHz output and logic  TEST_MODE  IN TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode while in test Test Clarification Table.  CKPWRGD#/PD  IN CKPWRGD#/PD  IN CKPWRGD# is an active low input used to sample latched inputs and allow the device to Pow asynchronous active high input pin used to put the device into a low power state. The internal are stopped.  PWR 3.3V power for the SRC outputs and logic  SRCOT  OUT  True clock of differential SRC output. These are current mode outputs. These are current mode external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  Complementary clock of differential SRC output. These are current mode outputs and external 32 GNDSRC  OUT  Ground pin for SRC outputs and logic.  OUT  Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  SRC1C  OUT  Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  SRC1T  OUT  True clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  True clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  True clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for terminat | 24    | DOT96T                | ОПТ  | ·                                                                                                               |

| Series resistors and 49.9 ohm shunt resistors are required for termination.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       | B01001                | 00.  |                                                                                                                 |

| 26 AVDD96 PWR 3.3V power for the 48/96MHz PLL and the 96MHz output and logic  27 TEST_MODE IN TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode while in test Test Clarification Table.  28 CKPWRGD#/PD IN CKPWRGD# is an active low input used to sample latched inputs and allow the device to Pow asynchronous active high input pin used to put the device into a low power state. The internal real real time input to select between Hi-Z and REF/N divider mode while in test Test Clarification Table.  29 VDDSRC PWR 3.3V power for the SRC outputs and logic  30 SRC0T True clock of differential SRC output. These are current mode outputs. These are current mode external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  31 SRC0C OUT Complementary clock of differential SRC output. These are current mode outputs and extern series resistors and 49.9 ohm shunt resistors are required for termination.  32 GNDSRC PWR Ground pin for SRC outputs and logic.  33 SRC1C OUT Complementary clock of differential SRC output. These are current mode outputs and extern series resistors and 49.9 ohm shunt resistors are required for termination.  34 SRC1T OUT True clock of differential SRC output. These are current mode outputs and extern series resistors and 49.9 ohm shunt resistors are required for termination.  35 SRC2C OUT Complementary clock of differential SRC output. These are current mode outputs and extern series resistors and 49.9 ohm shunt resistors are required for termination.  36 SRC2T OUT True clock of differential SRC output. These are current mode outputs and extern series resistors and 49.9 ohm shunt resistors are required for termination.  36 SRC2T OUT True clock of differential SRC output. These are current mode outputs and extern series resistors and 49.9 ohm shunt resistors are required for termination.                                                                                                                                                                        | 25    | DOT96C                | OUT  |                                                                                                                 |

| TEST_MODE  IN TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode while in test Test Clarification Table.  CKPWRGD#/PD  IN asynchronous active low input used to sample latched inputs and allow the device to Pow asynchronous active high input pin used to put the device into a low power state. The internal are stopped.  29 VDDSRC PWR 3.3V power for the SRC outputs and logic  30 SRC0T  OUT True clock of differential SRC output. These are current mode outputs. These are current mode external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  31 SRC0C  OUT Complementary clock of differential SRC output. These are current mode outputs and external 32 GNDSRC  PWR Ground pin for SRC outputs and logic.  32 GNDSRC  OUT Complementary clock of differential SRC output. These are current mode outputs and external 32 SRC1C  OUT True clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  34 SRC1T  OUT True clock of differential SRC output. These are current mode outputs. These are current mode external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  35 SRC2C  OUT Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  OUT True clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.  True clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.  True clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.                                                                                                                            | 25    | DO 1900               |      |                                                                                                                 |

| Test Clarification Table.  CKPWRGD#/PD  IN Synchronous active high input used to sample latched inputs and allow the device to Pow asynchronous active high input pin used to put the device into a low power state. The internal are stopped.  PWR 3.3V power for the SRC outputs and logic  SRCOT  OUT  Complementary clock of differential SRC output. These are current mode outputs. These are current mode external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  SRCOC  OUT  Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  SRC1C  OUT  True clock of differential SRC output. These are current mode outputs and external 34 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  True clock of differential SRC output. These are current mode outputs. These are current mode outputs. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  Complementary clock of differential SRC output. These are current mode outputs and external 35 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  Complementary clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.  Complementary clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.  True clock of differential SRC output. These are current mode outputs. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.                                                                           | 26    | AVDD96                | PWR  |                                                                                                                 |

| CKPWRGD#/PD  IN  CKPWRGD# is an active low input used to sample latched inputs and allow the device to Pow asynchronous active high input pin used to put the device into a low power state. The internal are stopped.  29 VDDSRC  PWR 3.3V power for the SRC outputs and logic  OUT  True clock of differential SRC output. These are current mode outputs. These are current mode external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  SRCOC  OUT  Complementary clock of differential SRC output. These are current mode outputs and external 32 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  PWR GDM# is an active low input used to sample latched inputs and allow the device to Pow asynchronous active high input pin used to put the device into a low power state. The internal asynchronous active high input pin used to put the device into a low power state. The internal are stopped.  OUT  True clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.  OUT  True clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  OUT  Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  OUT  Complementary clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.  True clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.                                                                                                                                                                                                                                                          | 27    | TEST MODE             | INI  | TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode while in test mode. Refer to       |

| 28 CKPWRGD#/PD IN asynchronous active high input pin used to put the device into a low power state. The internal are stopped.  29 VDDSRC PWR 3.3V power for the SRC outputs and logic  30 SRC0T OUT True clock of differential SRC output. These are current mode outputs. These are current mode external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  31 SRC0C OUT Complementary clock of differential SRC output. These are current mode outputs and external 32 GNDSRC PWR Ground pin for SRC outputs and logic.  32 GNDSRC PWR Ground pin for SRC outputs and logic.  33 SRC1C OUT Complementary clock of differential SRC output. These are current mode outputs and extern series resistors and 49.9 ohm shunt resistors are required for termination.  34 SRC1T OUT Complementary clock of differential SRC output. These are current mode outputs. These are current mode outputs and extern series resistors and 49.9 ohm shunt resistors are required for termination.  35 SRC2C OUT Complementary clock of differential SRC output. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  36 SRC2T OUT True clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.  37 True clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.  38 SRC2T OUT True clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.                                                                                                                                                                                                                                                                                                                                                                             | 21    | TEST_WODE             | IIV  |                                                                                                                 |

| are stopped.  29 VDDSRC PWR 3.3V power for the SRC outputs and logic  30 SRC0T OUT  True clock of differential SRC output. These are current mode outputs. These are current mode external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  31 SRC0C OUT  Complementary clock of differential SRC output. These are current mode outputs and external 32 GNDSRC PWR Ground pin for SRC outputs and logic.  32 GNDSRC OUT  SRC1C OUT  SRC1C OUT  True clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.  34 SRC1T OUT  True clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.  35 SRC2C OUT  Complementary clock of differential SRC output. These are current mode outputs. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.  36 SRC2T OUT  True clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.  37 SRC2T OUT  True clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.  38 SRC2T OUT  True clock of differential SRC output. These are current mode outputs and external series resistors and 49.9 ohm shunt resistors are required for termination.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |                       |      |                                                                                                                 |

| PWR 3.3V power for the SRC outputs and logic  OUT True clock of differential SRC output. These are current mode outputs. These are current mode outputs and external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  OUT Complementary clock of differential SRC output. These are current mode outputs and extern series resistors and 49.9 ohm shunt resistors are required for termination.  PWR Ground pin for SRC outputs and logic.  OUT Complementary clock of differential SRC output. These are current mode outputs and extern series resistors and 49.9 ohm shunt resistors are required for termination.  OUT True clock of differential SRC output. These are current mode outputs. These are current mode outputs and extern external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  OUT Complementary clock of differential SRC output. These are current mode outputs. These are current mode outputs and extern external 33 ohm series resistors and 49.9 ohm shunt resistors are required for termination.  OUT True clock of differential SRC output. These are current mode outputs and extern series resistors and 49.9 ohm shunt resistors are required for termination.  OUT True clock of differential SRC output. These are current mode outputs and extern series resistors and 49.9 ohm shunt resistors are required for termination.  True clock of differential SRC output. These are current mode outputs and extern series resistors and 49.9 ohm shunt resistors are required for termination.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 28    | CKPWRGD#/PD           | IN   | asynchronous active high input pin used to put the device into a low power state. The internal clocks and PLLs  |