# JESD204B Intel® FPGA IP User Guide

Updated for Intel® Quartus® Prime Design Suite: 19.4

IP Version: **19.2.0**

# **Contents**

| 1. JESD204B IP Quick Reference                          | 4  |

|---------------------------------------------------------|----|

| 2. About the JESD204B Intel FPGA IP                     | 6  |

| 2.1. Release Information                                | 8  |

| 2.2. Device Family Support                              |    |

| 2.3. Datapath Modes                                     | 9  |

| 2.4. IP Variation                                       |    |

| 2.5. JESD204B IP Configuration                          | 10 |

| 2.5.1. Run-Time Configuration                           |    |

| 2.6. Channel Bonding                                    |    |

| 2.7. Performance and Resource Utilization               |    |

| 3. Getting Started                                      | 20 |

| 3.1. Introduction to Intel FPGA IP Cores                | 20 |

| 3.2. Installing and Licensing Intel FPGA IP Cores       | 21 |

| 3.3. Intel FPGA IP Evaluation Mode                      | 22 |

| 3.4. Upgrading IP Cores                                 | 24 |

| 3.5. IP Catalog and Parameter Editor                    |    |

| 3.6. Design Walkthrough                                 |    |

| 3.6.1. Creating a New Intel Quartus Prime Project       |    |

| 3.6.2. Parameterizing and Generating the IP             | 29 |

| 3.6.3. Compiling the JESD204B IP Core Design            |    |

| 3.6.4. Programming an FPGA Device                       | 31 |

| 3.7. JESD204B Design Examples                           | 31 |

| 3.8. JESD204B IP Design Considerations                  | 31 |

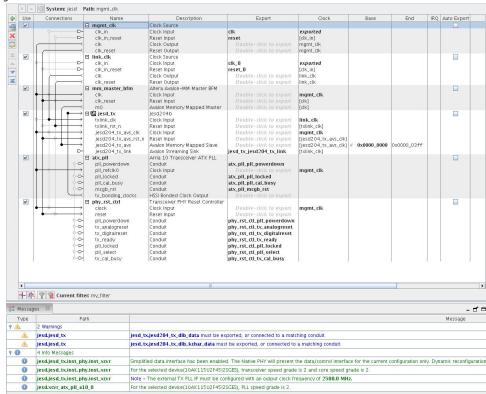

| 3.8.1. Integrating the JESD204B IP in Platform Designer |    |

| 3.8.2. Pin Assignments                                  | 33 |

| 3.8.3. Adding External Transceiver PLLs                 | 33 |

| 3.8.4. Timing Constraints For Input Clocks              | 33 |

| 3.9. JESD204B Intel FPGA IP Parameters                  | 36 |

| 3.10. JESD204B IP Component Files                       | 41 |

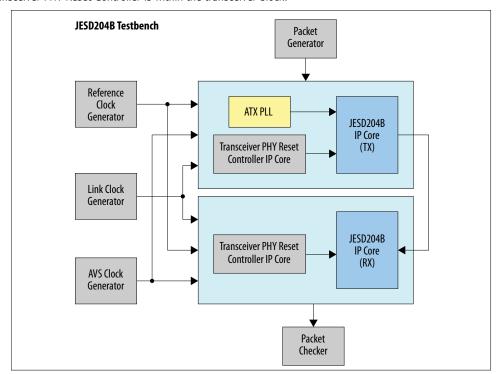

| 3.11. JESD204B IP Testbench                             | 41 |

| 3.11.1. Generating and Simulating the IP Testbench      | 42 |

| 3.11.2. Testbench Simulation Flow                       | 45 |

| 4. JESD204B IP Functional Description                   | 46 |

| 4.1. Transmitter                                        | 48 |

| 4.1.1. TX Data Link Layer                               | 49 |

| 4.1.2. TX PHY Layer                                     | 52 |

| 4.2. Receiver                                           |    |

| 4.2.1. RX Data Link Layer                               | 53 |

| 4.2.2. RX PHY Layer                                     | 56 |

| 4.3. Operation                                          |    |

| 4.3.1. Operating Modes                                  |    |

| 4.3.2. Scrambler/Descrambler                            |    |

| 4.3.3. SYNC_N Signal                                    |    |

| 4.3.4. Link Reinitialization                            |    |

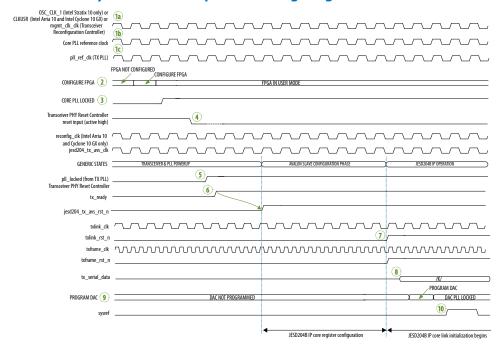

| 4.3.5. Link Startup Sequence                            | 62 |

### Contents

|       | 4.3.6. Error Reporting Through SYNC_N Signal                                                                                                                                                                                                                                                                                                                                         | 63                       |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|       | 4.4. Clocking Scheme                                                                                                                                                                                                                                                                                                                                                                 | 63                       |

|       | 4.4.1. Device Clock                                                                                                                                                                                                                                                                                                                                                                  | 65                       |

|       | 4.4.2. Link Clock                                                                                                                                                                                                                                                                                                                                                                    | 67                       |

|       | 4.4.3. Local MultiFrame Clock                                                                                                                                                                                                                                                                                                                                                        | 68                       |

|       | 4.4.4. Clock Correlation                                                                                                                                                                                                                                                                                                                                                             | 69                       |

|       | 4.5. Reset Scheme                                                                                                                                                                                                                                                                                                                                                                    | 70                       |

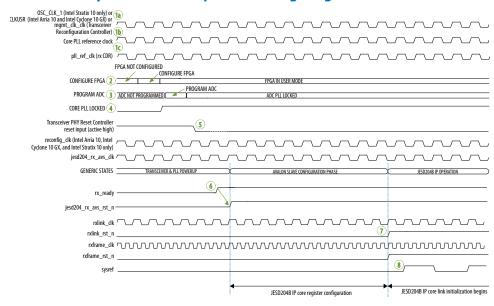

|       | 4.5.1. Reset Sequence                                                                                                                                                                                                                                                                                                                                                                |                          |

|       | 4.5.2. ADC-FPGA Subsystem Reset Sequence                                                                                                                                                                                                                                                                                                                                             |                          |

|       | 4.5.3. FPGA-DAC Subsystem Reset Sequence                                                                                                                                                                                                                                                                                                                                             |                          |

|       | 4.6. Signals                                                                                                                                                                                                                                                                                                                                                                         |                          |

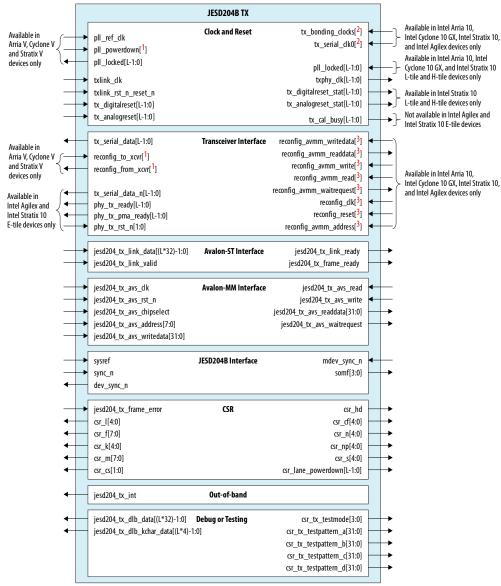

|       | 4.6.1. Transmitter Signals                                                                                                                                                                                                                                                                                                                                                           |                          |

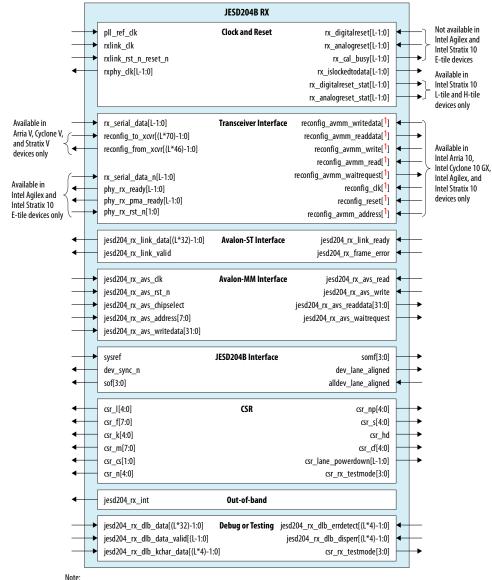

|       | 4.6.2. Receiver Signals                                                                                                                                                                                                                                                                                                                                                              |                          |

|       | 4.7. Registers                                                                                                                                                                                                                                                                                                                                                                       |                          |

|       | 4.7.1. Register Access Type Convention                                                                                                                                                                                                                                                                                                                                               |                          |

|       | 4.7.2. Transmitter Registers                                                                                                                                                                                                                                                                                                                                                         |                          |

|       | 4.7.3. Receiver Registers                                                                                                                                                                                                                                                                                                                                                            | 123                      |

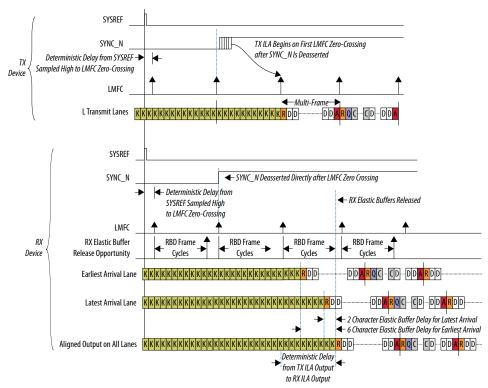

| 5. JI | ESD204B IP Deterministic Latency Implementation Guidelines                                                                                                                                                                                                                                                                                                                           | 149                      |

|       | 5.1. Constraining Incoming SYSREF Signal                                                                                                                                                                                                                                                                                                                                             | 149                      |

|       | 5.2. Programmable RBD Offset                                                                                                                                                                                                                                                                                                                                                         |                          |

|       | 5.3. Programmable LMFC Offset                                                                                                                                                                                                                                                                                                                                                        | 4.50                     |

|       |                                                                                                                                                                                                                                                                                                                                                                                      | 153                      |

|       | 5.4. Maintaining Deterministic Latency during Link Reinitialization                                                                                                                                                                                                                                                                                                                  |                          |

| 6. JI | 5.4. Maintaining Deterministic Latency during Link Reinitialization                                                                                                                                                                                                                                                                                                                  | 157                      |

| 6. JI | 5.4. Maintaining Deterministic Latency during Link Reinitialization  ESD204B IP Debug Guidelines                                                                                                                                                                                                                                                                                     | 157                      |

| 6. JI | 5.4. Maintaining Deterministic Latency during Link Reinitialization  ESD204B IP Debug Guidelines                                                                                                                                                                                                                                                                                     | 157<br><b>159</b><br>159 |

| 6. JI | 5.4. Maintaining Deterministic Latency during Link Reinitialization                                                                                                                                                                                                                                                                                                                  | 157159159                |

| 6. JI | 5.4. Maintaining Deterministic Latency during Link Reinitialization                                                                                                                                                                                                                                                                                                                  | 157159159159             |

| 6. JI | 5.4. Maintaining Deterministic Latency during Link Reinitialization                                                                                                                                                                                                                                                                                                                  |                          |

| 6. JI | 5.4. Maintaining Deterministic Latency during Link Reinitialization                                                                                                                                                                                                                                                                                                                  |                          |

| 6. JI | 5.4. Maintaining Deterministic Latency during Link Reinitialization                                                                                                                                                                                                                                                                                                                  |                          |

|       | 5.4. Maintaining Deterministic Latency during Link Reinitialization  ESD204B IP Debug Guidelines 6.1. Clocking Scheme 6.2. JESD204B Parameters 6.3. SPI Programming 6.4. Converter and FPGA Operating Conditions 6.5. Signal Polarity and FPGA Pin Assignment 6.6. Creating a Signal Tap Debug File to Match Your Design Hierarchy 6.7. Debugging JESD204B Link Using System Console |                          |

| 7. JI | 5.4. Maintaining Deterministic Latency during Link Reinitialization                                                                                                                                                                                                                                                                                                                  |                          |

# 1. JESD204B IP Quick Reference

The JESD204B Intel FPGA IP is a high-speed point-to-point serial interface intellectual property (IP).

Note: For system requirements and installation instructions, refer to Intel FPGA Software

Installation & Licensing.

#### Table 1. Brief Information About the JESD204B IP

| Item                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Protocol Features     | Joint Electron Device Engineering Council (JEDEC) JESD204B.01, 2012 standard release specification     Device subclass:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Core Features         | <ul> <li>Run-time configuration of parameters L, M, and F</li> <li>Data rate of up to 12.5 gigabits per second (Gbps)—per JESD204B specification</li> <li>Data rate of up to 19.2 Gbps—not certified per JESD204B specification (uncharacterized support)</li> <li>Single or multiple lanes (up to 8 lanes per link)</li> <li>Serial lane alignment and monitoring</li> <li>Lane synchronization</li> <li>Modular design that supports multidevice synchronization</li> <li>MAC and PHY partitioning</li> <li>Deterministic latency support</li> <li>8B/10B encoding</li> <li>Scrambling/Descrambling</li> <li>Avalon® Streaming (Avalon-ST) interface for transmit and receive datapaths</li> <li>Avalon Memory-Mapped (Avalon-MM) interface for Configuration and Status registers (CSR)</li> <li>Dynamic generation of simulation testbench</li> </ul> |

| Typical Application   | Wireless communication equipment     Broadcast equipment     Military equipment     Medical equipment     Test and measurement equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Device Family Support | <ul> <li>Intel Agilex™ devices (E-tile)</li> <li>Intel Cyclone® 10 GX FPGA devices</li> <li>Intel Stratix® 10 FPGA devices (L-tile/H-tile/E-tile)</li> <li>Intel Arria® 10 FPGA devices</li> <li>Stratix V FPGA devices</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

| Item         | Description                                                                                                                                                                                                                                                                                                                                                                        |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | <ul> <li>Arria V FPGA devices</li> <li>Arria V GZ FPGA devices</li> <li>Cyclone V FPGA devices</li> </ul>                                                                                                                                                                                                                                                                          |

| Design Tools | <ul> <li>Platform Designer parameter editor in the Intel Quartus<sup>®</sup> Prime software for design creation and compilation</li> <li>Timing Analyzer in the Intel Quartus Prime software for timing analysis</li> <li>ModelSim* - Intel FPGA Edition, Riviera-PRO*, VCS*/VCS MX, NCSim, and Xcelium* Parallel simulator software for design simulation or synthesis</li> </ul> |

#### **Related Information**

- Design Examples for JESD204B IP Core User Guide

Provides information about design examples for Arria V, Cyclone V, Stratix V, and Intel Arria 10 devices using Intel Quartus Prime Standard Edition software.

- JESD204B Intel Arria 10 FPGA IP Design Example User Guide

- JESD204B Intel Stratix 10 FPGA IP Design Example User Guide

- JESD204B Intel Cyclone 10 GX FPGA IP Design Example User Guide

- JESD204B Intel Agilex FPGA IP Design Example User Guide

- Intel FPGA Software Installation and Licensing

- JESD204B IP Core Release Notes

- Errata for JESD204B IP Core in the Knowledge Base

- AN803: Implementing ADC-Intel Arria 10 Multi-Link Design with JESD204B RX IP Core

- AN804: Implementing ADC-Intel Stratix 10 Multi-Link Design with JESD204B RX IP Core

- JESD204B Intel FPGA IP User Guide Archives on page 169

Provides a list of user guides for previous versions of the JESD204B IP core.

## 2. About the JESD204B Intel FPGA IP

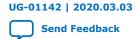

The JESD204B Intel FPGA IP is a high-speed point-to-point serial interface for digital-to-analog (DAC) or analog-to-digital (ADC) converters to transfer data to FPGA devices. This unidirectional serial interface runs at a maximum data rate of 17.4 Gbps. This protocol offers higher bandwidth, low I/O count and supports scalability in both number of lanes and data rates. The JESD204B Intel FPGA IP addresses multi-device synchronization by introducing Subclass 1 and Subclass 2 to achieve deterministic latency.

Note:

The full product name, JESD204B Intel FPGA IP, is shortened to JESD204B IP in this document.

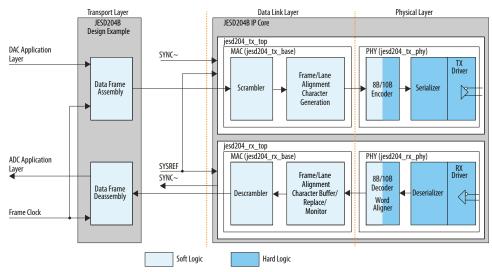

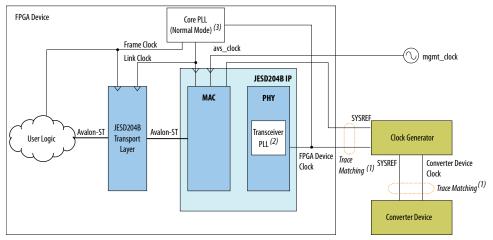

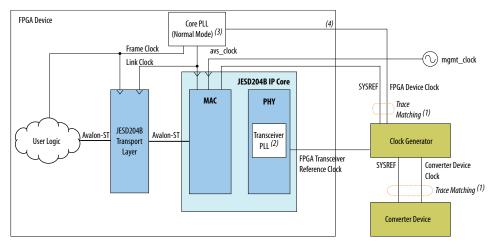

The JESD204B IP incorporates:

- Media access control (MAC)—data link layer (DLL) block that controls the link states and character replacement.

- Physical layer (PHY)—physical coding sublayer (PCS) and physical media attachment (PMA) block.

The JESD204B IP does not incorporate the Transport Layer (TL) that controls the frame assembly and disassembly. The TL and test components are provided as part of a design example component where you can customize the design for different converter devices.

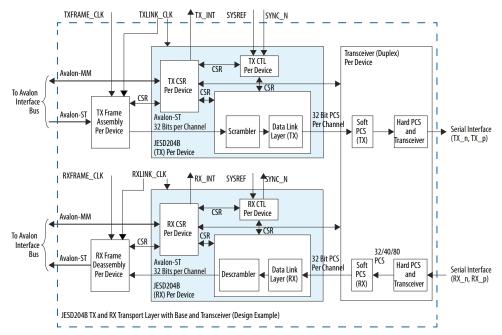

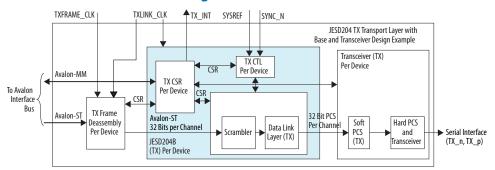

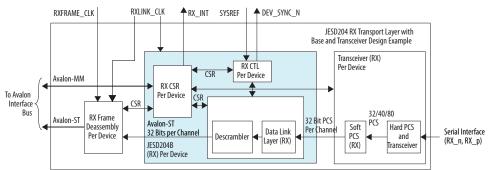

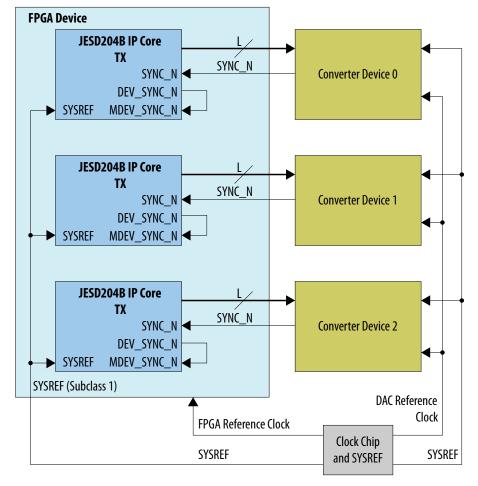

Figure 1. Typical System Application for JESD204B IP

The JESD204B IP uses the Avalon-ST source and sink interfaces, with unidirectional flow of data, to transmit and receive data on the FPGA fabric interface.

Key features of the JESD204B IP:

- Data rate of up to 19.2 Gbps (characterization up to 12.5 G)

- Run-time JESD204B parameter configuration (L, M, F, S, N, K, CS, CF)

- · MAC and PHY partitioning for portability

- Subclass 0 mode for backward compatibility to JESD204A

- Subclass 1 mode for deterministic latency support (using SYSREF) between the ADC/DAC and logic device

- Subclass 2 mode for deterministic latency support (using SYNC\_N) between the ADC/DAC and logic device

- Multi-device synchronization

#### **Related Information**

- V-Series Transceiver PHY User Guide

- Intel Arria 10 Transceiver PHY User Guide

- Intel Cyclone 10 GX Transceiver PHY User Guide

- Intel Stratix 10 L- and H-tile Transceiver PHY User Guide

- E-tile Transceiver PHY User Guide

- Intel Agilex Device Datasheet

- Intel Stratix 10 Device Datasheet

- Intel Arria 10 Device Datasheet

#### 2.1. Release Information

IP versions are the same as the Intel Quartus Prime Design Suite software versions up to v19.1. From Intel Quartus Prime Design Suite software version 19.2 or later, IP cores have a new IP versioning scheme.

The IP versioning scheme (X.Y.Z) number changes from one software version to another. A change in:

- X indicates a major revision of the IP. If you update your Intel Quartus Prime software, you must regenerate the IP.

- Y indicates the IP includes new features. Regenerate your IP to include these new features.

- Z indicates the IP includes minor changes. Regenerate your IP to include these changes.

#### Table 2. JESD204B IP Release Information

| Item                        | Description   |

|-----------------------------|---------------|

| IP Version                  | 19.3.0        |

| Intel Quartus Prime Version | 19.4          |

| Release Date                | December 2019 |

| Ordering Code               | IP-JESD204B   |

# 2.2. Device Family Support

**Table 3.** Intel Device Family Support

| Device Family                                 | Support Level |

|-----------------------------------------------|---------------|

| Intel Agilex (E-tile)                         | Advance       |

| Intel Stratix 10 (E-tile, H-tile, and L-tile) | Final         |

| Intel Arria 10                                | Final         |

| Intel Cyclone 10 GX                           | Final         |

|                                               | continued     |

| Device Family | Support Level |

|---------------|---------------|

| Stratix V     | Final         |

| Arria V       | Final         |

| Cyclone V     | Final         |

The following terms define device support levels for Intel FPGA IP cores:

- Advance support—the IP core is available for simulation and compilation for this

device family. Timing models include initial engineering estimates of delays based

on early post-layout information. The timing models are subject to change as

silicon testing improves the correlation between the actual silicon and the timing

models. You can use this IP core for system architecture and resource utilization

studies, simulation, pinout, system latency assessments, basic timing assessments

(pipeline budgeting), and I/O transfer strategy (data-path width, burst depth, I/O

standards tradeoffs).

- Preliminary support—the IP core is verified with preliminary timing models for this

device family. The IP core meets all functional requirements, but might still be

undergoing timing analysis for the device family. It can be used in production

designs with caution.

- Final support—the IP core is verified with final timing models for this device family. The IP core meets all functional and timing requirements for the device family and can be used in production designs.

### 2.3. Datapath Modes

The JESD204B IP supports TX-only, RX-only, and Duplex (TX and RX) mode. The IP is a unidirectional protocol where interfacing to ADC utilizes the transceiver RX path and interfacing to DAC utilizes the transceiver TX path.

The JESD204B IP generates a single link with a single lane and up to a maximum of 8 lanes. If there are two ADC links that need to be synchronized, you have to generate two JESD204B IP cores and then manage the deterministic latency and synchronization signals, like SYSREF and SYNC\_N, at your custom wrapper level.

The JESD204B IP supports duplex mode only if the LMF configuration for ADC (RX) is the same as DAC (TX) and with the same data rate. This use case is mainly for prototyping with internal serial loopback mode. This is because typically as a unidirectional protocol, the LMF configuration of converter devices for both DAC and ADC are not identical.

### 2.4. IP Variation

The JESD204B IP has three core variations:

- JESD204B MAC only

- JESD204B PHY only

- JESD204B MAC and PHY

In a subsystem where there are multiple ADC and DAC converters, you need to use the Intel Quartus Prime software to merge the transceivers and group them into the transceiver architecture. For example, to create two instances of the JESD204B TX IP with four lanes each and four instances of the JESD204B RX IP with two lanes each, you can apply one of the following options:

- MAC and PHY option

- 1. Generate JESD204B TX IP with four lanes and JESD204B RX IP with two lanes.

- 2. Instantiate the desired components.

- 3. Use the Intel Quartus Prime software to merge the PHY lanes.

- MAC only and PHY only option—based on the configuration above, there are a total

of eight lanes in duplex mode.

- 1. Generate the JESD204B Duplex PHY with a total of eight lanes. (TX skew is reduced in this configuration as the channels are bonded).

- 2. Generate the JESD204B TX MAC with four lanes and instantiate it two times.

- 3. Generate the JESD204B RX MAC with two lanes and instantiate it four times.

- 4. Create a wrapper to connect the JESD204B TX MAC and RX MAC with the JESD204B Duplex PHY.

Note:

If the data rate for TX and RX is different, the transceiver does not allow duplex mode to generate a duplex PHY. In this case, you have to generate a RX-only PHY on the RX data rate and a TX-only PHY on the TX data rate.

### 2.5. JESD204B IP Configuration

**Table 5. JESD204B IP Configuration**

| Symbol | Description                                                                         | Value                                                                                              |

|--------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| L      | Number of lanes per converter device                                                | 1-8                                                                                                |

| М      | Number of converters per device                                                     | 1-256                                                                                              |

| F      | Number of octets per frame                                                          | 1-256 (for Intel Stratix<br>10 devices only)     1, 2, 4-256 (for non<br>Intel Stratix 10 devices) |

| S      | Number of transmitted samples per converter per frame                               | 1-32                                                                                               |

| N      | Number of conversion bits per converter                                             | 1-32                                                                                               |

| N'     | Number of transmitted bits per sample (JESD204 word size, which is in nibble group) | 1-32                                                                                               |

| К      | Number of frames per multiframe                                                     | 17/F ≤ K ≤ 32 ; 1-32                                                                               |

| CS     | Number of control bits per conversion sample                                        | 0-3                                                                                                |

| CF     | Number of control words per frame clock period per link                             | 0-32                                                                                               |

| HD     | High Density user data format                                                       | 0 or 1                                                                                             |

| LMFC   | Local multiframe clock                                                              | (F × K /4) link clock counts                                                                       |

<sup>(1)</sup> The value of F x K must be divisible by 4.

### 2.5.1. Run-Time Configuration

The JESD204B IP allows run-time configuration of LMF parameters in all supported devices except for Intel Stratix 10. For Intel Stratix 10 devices, the JESD204B IP core must be parameterized according to your target converter device with the IP configurations shown in *JESD204B Configurations Tab* of Table 15 on page 36

Note:

For Intel Stratix 10 devices, run-time access for certain registers have been disabled. Refer to the TX and RX register map for more information.

The most critical parameters that must be set correctly during IP generation are the  $\tt L$  and  $\tt F$  parameters. Parameter  $\tt L$  denotes the maximum lanes supported while parameter  $\tt F$  denotes the size of the deskew buffer needed for deterministic latency. The hardware generates during parameterization, which means that run-time programmability can only fall back from the parameterized and generated hardware, but not beyond the parameterized IP core.

You can use run-time configuration for prototyping or evaluating the performance of converter devices with various LMF configurations. However, in actual production,Intel recommends that you generate the JESD204B IP core with the intended LMF to get an optimized gate count.

For example, if a converter device supports LMF = 442 and LMF = 222, to check the performance for both configurations, you need to generate the JESD204B IP with maximum F and L, which is L = 4 and F = 2. During operation, you can use the fall back configuration to disable the lanes that are not used in LMF = 222 mode. You must ensure that other JESD204B configurations like M, N, S, CS, CF, and HD do not violate the parameter F setting. You can access the Configuration and Status Register (CSR) space to modify other configurations such as:

- K (multiframe)

- · device and lane IDs

- enable or disable scrambler

- enable or disable character replacement

#### **F Parameter**

This parameter indicates how many octets per frame per lane that the JESD204B link is operating in.

- Intel Agilex and Intel Stratix 10 (L-tile, H-tile, and E-tile) devices support F = 1–256 (F = 3 available)

- Intel Cyclone 10 GX , Intel Arria 10, Stratix V, Arria V, Arria V GZ, and Cyclone V devices support F = 1, 2, 4-256 (F = 3 not available)

To support the High Density (HD) data format, the JESD204B IP tracks the start of frame and end of frame because F can be either an odd or even number. The start of frame and start of multiframe wrap around the 32-bit data width architecture. The RX IP outputs the start of frame (sof[3:0]) and start of multiframe (somf[3:0]), which act as markers, using the Avalon-ST data stream. Based on these markers, the transport layer build the frames.

In a simpler system where the HD data format is set to 0, the F will always be 1, 2, 4, 6, 8, and so forth. This simplifies the transport layer design, so you do not need to use the sof[3:0] and somf[3:0] markers.

#### **Related Information**

- Transmitter Registers on page 99

- Receiver Registers on page 123

### 2.6. Channel Bonding

The JESD204B IP supports channel bonding—bonded (PMA bonding for Intel Agilex, Intel Stratix 10, Intel Arria 10, and Intel Cyclone 10 GX) and non-bonded modes.

The channel bonding mode that you select may contribute to the transmitter channel-to-channel skew. A bonded transmitter datapath clocking provides low channel-to-channel skew as compared to non-bonded channel configurations.

For Intel Stratix 10 L-tile and H-tile, Intel Arria 10, and Intel Cyclone 10 GX devices, refer to PMA Bonding chapter of the respective *Transceiver PHY User Guides*, about how to connect the ATX PLL and fPLL in bonded configuration and non-bonded configuration. For the non-bonded configuration, refer to *Implementing Multi-Channel xN Non-Bonded Configuration*. For bonded configuration, refer to *Implementing x6/xN Bonding Mode*.

• In PHY-only mode, you can generate up to 32 channels, provided that the channels are on the same side. In MAC and PHY integrated mode, you can generate up to 8 channels.

Note: The maximum channels of 32 is for configuration simplicity. Refer to the Intel FPGA Transceiver PHY User Guide for the actual number of channels supported.

- In bonded channel configuration, the lower transceiver clock skew for all channels result in a lower channel-to-channel skew.

- For Stratix V, Arria V, and Cyclone V devices, you must use contiguous channels when you select bonded mode. The JESD204B IP automatically selects between ×6, ×N or feedback compensation (fb\_compensation) bonding depending on the number of transceiver channels you set.

- For Intel Arria 10, Intel Cyclone 10 GX, and Intel Stratix 10 L-tile and H-tile devices, you do not have to place the channels in bonded group contiguously. Refer to Table 7 on page 13 for the clock network selection. Refer to Channel Bonding section of the respective Transceiver PHY User Guides for more information about PMA Bonding.

- For Intel Agilex and Intel Stratix 10 E-tile devices, you must use contiguous channels to enable channel bonding with NRZ PMA transceiver channels.

- In non-bonded channel configuration, the transceiver clock skew is higher and latency is unequal in the transmitter phase compensation FIFO for each channel. This may result in a higher channel-to-channel skew.

Table 6. Maximum Number of Lanes (L) Supported in Bonded and Non-Bonded Mode

| Device Family                      | Core Variation | <b>Bonding Mode Configuration</b> | Maximum Number of Lanes (L) |

|------------------------------------|----------------|-----------------------------------|-----------------------------|

| Intel Agilex                       | PHY only       | Bonded                            | 32 (2)                      |

| Intel Stratix 10<br>Intel Arria 10 |                | Non-bonded                        | 32 (2)                      |

| Intel Cyclone 10 GX                | MAC and PHY    | Bonded                            | 8                           |

|                                    | ·              |                                   | continued                   |

| <b>Device Family</b>                 | Core Variation | <b>Bonding Mode Configuration</b> | Maximum Number of<br>Lanes (L) |

|--------------------------------------|----------------|-----------------------------------|--------------------------------|

| Stratix V<br>Arria V GZ<br>Cyclone V |                | Non-bonded                        | 8                              |

| Arria V                              | PHY only       | Bonded                            | 32 (2)                         |

|                                      |                | Non-bonded                        | 32 (2)                         |

|                                      | MAC and PHY    | Bonded                            | 6                              |

|                                      |                | Non-bonded                        | 8                              |

#### **Table 7.** Clock Network Selection for Bonded Mode

Note: The clock network selection is not applicable for Intel Stratix 10 E-tile devices.

| <b>Device Family</b>                                                        | L ≤ 6 | L > 6                 |

|-----------------------------------------------------------------------------|-------|-----------------------|

| Intel Stratix 10 L-tile and H-tile<br>Intel Arria 10<br>Intel Cyclone 10 GX | ×6    | ×N <sup>(3)</sup>     |

| Stratix V                                                                   | ×6    | Feedback compensation |

| Arria V                                                                     | ×N    | ×N                    |

| Arria V GZ                                                                  | ×6    | Feedback compensation |

| Cyclone V                                                                   | ×N    | ×N                    |

#### **Related Information**

- V-Series Transceiver PHY User Guide

- Intel Arria 10 Transceiver PHY User Guide

- Intel Cyclone 10 GX Transceiver PHY User Guide

- Intel Stratix 10 L- and H-tile Transceiver PHY User Guide

- E-tile Transceiver PHY User Guide

- Intel Agilex Device Datasheet

- Intel Stratix 10 Device Datasheet

- Intel Arria 10 Device Datasheet

<sup>(3)</sup> Bonded mode is not supported for data rate > 15 Gbps. Refer to the respective datasheet for the maximum data rate and channel span supported by the ×N clock network and the transceiver power supply operating condition for your device.

<sup>(2)</sup> The maximum lanes listed here is for configuration simplicity. Refer to the *Intel FPGA Transceiver PHY User Guides* for the actual number of channels supported.

### 2.7. Performance and Resource Utilization

Table 8. JESD204B Intel FPGA IP Performance

| <b>Device Family</b>                      | PMA Speed Grade | FPGA Fabric | Data Rate              |                               | Link Clock                |

|-------------------------------------------|-----------------|-------------|------------------------|-------------------------------|---------------------------|

|                                           |                 | Speed Grade | Enable Hard PCS (Gbps) | Enable Soft PCS<br>(Gbps) (4) | F <sub>MAX</sub><br>(MHz) |

| Intel Agilex (E-tile)                     | 1               | -1          | Not supported          | 2.0 to 19.2                   | data_rate/<br>40          |

|                                           | 2               | -2          | Not supported          | 2.0 to 17.4                   | data_rate/<br>40          |

|                                           | 3               | -2          | Not supported          | 2.0 to 17.4                   | data_rate/<br>40          |

|                                           |                 | -3          | Not supported          | 2.0 to 16.0                   | data_rate/<br>40          |

| Intel Stratix 10 (L-<br>tile, and H-tile) | 1               | -1          | 2.0 to 12.0            | 2.0 to 16.0 <sup>(6)</sup>    | data_rate/<br>40          |

|                                           |                 | -2          | 2.0 to 12.0            | 2.0 to 14.0                   | data_rate/<br>40          |

|                                           | 2               | -1          | 2.0 to 9.83            | 2.0 to 16.0 <sup>(6)</sup>    | data_rate/<br>40          |

|                                           |                 | -2          | 2.0 to 9.83            | 2.0 to 14.0                   | data_rate/<br>40          |

|                                           | 3               | -1          | 2.0 to 9.83            | 2.0 to 16.0 <sup>(6)</sup>    | data_rate/<br>40          |

|                                           |                 | -2          | 2.0 to 9.83            | 2.0 to 14.0                   | data_rate/<br>40          |

|                                           |                 | -3          | 2.0 to 9.83            | 2.0 to 13.0                   | data_rate/<br>40          |

| Intel Stratix 10 (E-tile)                 | 1               | -1          | Not supported          | 2.0 to 16.0 <sup>(6)</sup>    | data_rate/<br>40          |

|                                           |                 | -2          | Not supported          | 2.0 to 14.0                   | data_rate/<br>40          |

|                                           | 2               | -1          | Not supported          | 2.0 to 16.0 <sup>(6)</sup>    | data_rate/<br>40          |

|                                           |                 | -2          | Not supported          | 2.0 to 14.0                   | data_rate/<br>40          |

|                                           | 3               | -3          | Not supported          | 2.0 to 13.0                   | data_rate/<br>40          |

| Intel Arria 10                            | 1               | -1          | 2.0 to 12.0            | 2.0 to 15.0 <sup>(6)(5)</sup> | data<br>rate/40           |

|                                           | ` <u></u>       |             |                        | C                             | ontinued                  |

<sup>(4)</sup> Select Enable Soft PCS to achieve maximum data rate. For the TX IP core, enabling soft PCS incurs an additional 3–8% increase in resource utilization. For the RX IP core, enabling soft PCS incurs an additional 10–20% increase in resource utilization.

<sup>(5)</sup> When using Soft PCS mode at 15.0 Gbps, the timing margin is very limited. You are advised to enable high fitter effort, register duplication, and register retiming to improve timing performance.

#### UG-01142 | 2020.03.03

| Device Family       | PMA Speed Grade FPGA Fabric Speed Grade    |                                            | Data                              | Rate                                       | Link Clock                |

|---------------------|--------------------------------------------|--------------------------------------------|-----------------------------------|--------------------------------------------|---------------------------|

|                     |                                            |                                            | Enable Hard PCS (Gbps) (Gbps) (4) |                                            | F <sub>MAX</sub><br>(MHz) |

|                     | 2                                          | -1                                         | 2.0 to 12.0                       | 2.0 to 15.0 <sup>(6) (5)</sup>             | data<br>rate/40           |

|                     | 2                                          | -2                                         | 2.0 to 9.83                       | 2.0 to 15.0 <sup>(6) (5)</sup>             | data<br>rate/40           |

|                     | 3                                          | -1                                         | 2.0 to 12.0                       | 2.0 to 14.2 <sup>(6) (7)</sup>             | data<br>rate/40           |

|                     | 3                                          | -2                                         | 2.0 to 9.83                       | 2.0 to 14.2 <sup>(6) (8)</sup>             | data<br>rate/40           |

|                     | 4                                          | -3                                         | 2.0 to 8.83                       | 2.0 to 12.5 <sup>(9)</sup>                 | data<br>rate/40           |

| Intel Cyclone 10 GX | <any grade="" speed="" supported=""></any> | <any grade="" speed="" supported=""></any> | 2.0 to 6.25                       | 2.0 to 6.25                                | data<br>rate/40           |

| Stratix V           | 1                                          | -1 or -2                                   | 2.0 to 12.2                       | 2.0 to 12.5                                | data<br>rate/40           |

|                     | 2                                          | −1 or −2                                   | 2.0 to 12.2                       | 2.0 to 12.5                                | data<br>rate/40           |

|                     | 2                                          | -3                                         | 2.0 to 9.8                        | 2.0 to 12.5 <sup>(10)</sup>                | data<br>rate/40           |

|                     | 3                                          | -1, -2, -3, or -4                          | 2.0 to 8.5                        | 2.0 to 8.5                                 | data<br>rate/40           |

| Arria V GX/SX       | <any grade="" speed="" supported=""></any> | <any grade="" speed="" supported=""></any> | 1.0 to 6.55                       | _ (11)                                     | data<br>rate/40           |

| Arria V GT/ST       | <any grade="" speed="" supported=""></any> | <any supported<br="">speed grade&gt;</any> | 1.0 to 6.55                       | 4.0 to 7.5<br>(PMA direct) <sup>(11)</sup> | data<br>rate/40           |

|                     |                                            |                                            |                                   |                                            | ontinued                  |

<sup>(4)</sup> Select Enable Soft PCS to achieve maximum data rate. For the TX IP core, enabling soft PCS incurs an additional 3–8% increase in resource utilization. For the RX IP core, enabling soft PCS incurs an additional 10–20% increase in resource utilization.

<sup>(6)</sup> Refer to the Intel Arria 10 and Intel Stratix 10 Device Datasheet for the maximum data rate supported across transceiver speed grades and transceiver power supply operating conditions.

<sup>(7)</sup> For Intel Arria 10 GX 160, SX 160, GX 220 and SX 220 devices, the supported data rate is up to 12.288 Gbps.

<sup>(8)</sup> For Intel Arria 10 GX 160, SX 160, GX 220 and SX 220 devices, the supported data rate is 11.0 Gbps.

<sup>(9)</sup> For Intel Arria 10 GX 160, SX 160, GX 220 and SX 220 devices, the supported data rate is 10.0 Gbps.

<sup>(10)</sup> When using Soft PCS mode at 12.5 Gbps, the timing margin is very limited. You are advised to enable high fitter effort, register duplication, and register retiming to improve timing performance.

<sup>(11)</sup> Enabling Soft PCS does not increase the data rate for the device family and speed grade. You are recommended to select the *Enable Hard PCS* option.

| Device Family | PMA Speed Grade | FPGA Fabric                                | Data                          | Data Rate                 |                 |  |

|---------------|-----------------|--------------------------------------------|-------------------------------|---------------------------|-----------------|--|

|               | Speed Grade     | Enable Hard PCS<br>(Gbps)                  | Enable Soft PCS<br>(Gbps) (4) | F <sub>MAX</sub><br>(MHz) |                 |  |

| Arria V GZ    | 2               | -3                                         | 2.0 to 9.9                    | (11)                      | data<br>rate/40 |  |

|               | 3               | -4                                         | 2.0 to 8.8                    | (11)                      | data<br>rate/40 |  |

| Cyclone V     | 5               | <any supported<br="">speed grade&gt;</any> | 1.0 to 5.0                    | _                         | data<br>rate/40 |  |

|               | 6               | -6 or -7                                   | 1.0 to 3.125                  | _                         | data<br>rate/40 |  |

The following table lists the resources and expected performance of the JESD204B IP core. These results are obtained using the Intel Quartus Prime software targeting the following Intel FPGA devices:

Cyclone V: 5CGTFD9E5F31I7

Arria V GT/S/GT: 5AGXFB3H4F35C5

Arria V GZ: 5AGZME5K2F40C3

• Stratix V: 5SGXEA7H3F35C3

Intel Arria 10: 10AX115H2F34I2SGES

Intel Stratix 10: 1SG280LN3F43E3VG

Intel Cyclone 10 GX: 10CX105YF672I6G

All the variations for resource utilization are configured with the following parameter settings:

**Table 9.** Parameter Settings To Obtain the Resource Utilization Data

| Parameter                 | Setting                                                                                                                                               |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| JESD204B Wrapper          | Base and PHY                                                                                                                                          |

| JESD204B Subclass         | 1                                                                                                                                                     |

| Data Rate                 | 5 Gbps                                                                                                                                                |

| PCS Option                | Enabled Hard PCS                                                                                                                                      |

| PLL Type                  | ATX (for Intel Arria 10, Intel Cyclone 10 GX, and Intel Stratix 10 L-tile and H-tile devices)     CMU (for Arria V, Cyclone V, and Stratix V devices) |

| Bonding Mode              | Non-bonded                                                                                                                                            |

| Reference Clock Frequency | 125.0 MHz                                                                                                                                             |

|                           | continued                                                                                                                                             |

<sup>(4)</sup> Select Enable Soft PCS to achieve maximum data rate. For the TX IP core, enabling soft PCS incurs an additional 3–8% increase in resource utilization. For the RX IP core, enabling soft PCS incurs an additional 10–20% increase in resource utilization.

#### UG-01142 | 2020.03.03

| Parameter                             | Setting                                                                                  |  |

|---------------------------------------|------------------------------------------------------------------------------------------|--|

| Octets per frame (F)                  | 1 (For all devices, including Intel Stratix 10)     3 (For Intel Stratix 10 device only) |  |

| Enable Scrambler (SCR)                | Off                                                                                      |  |

| Enable Error Code Correction (ECC_EN) | Off                                                                                      |  |

Table 10. JESD204B IP Core Resource Utilization

Note:

The resource utilization data are extracted from a full design which includes the Intel FPGA Transceiver PHY Reset Controller IP core. Thus, the actual resource utilization for the JESD204B IP core should be smaller by about 15 ALMs and 20 registers.

| Device Family    | Data Path | Number of Lanes (L) | ALMs   | ALUTs | Logic<br>Registers | Memory Block<br>(M10K/M20K)<br>(12) (13) |

|------------------|-----------|---------------------|--------|-------|--------------------|------------------------------------------|

| Intel Stratix 10 | RX        | 1                   | 889.4  | 1230  | 1334               | 0                                        |

| (F=1)            |           | 2                   | 1329.7 | 1810  | 2119               | 0                                        |

|                  |           | 4                   | 2302.8 | 3101  | 3634               | 0                                        |

|                  |           | 8                   | 4218.1 | 5638  | 6650               | 0                                        |

|                  | TX        | 1                   | 534.4  | 694   | 869                | 0                                        |

|                  |           | 2                   | 746    | 1061  | 1078               | 0                                        |

|                  |           | 4                   | 1049.8 | 1557  | 1580               | 0                                        |

|                  |           | 8                   | 1534.2 | 1980  | 2507               | 0                                        |

| Intel Stratix 10 | RX        | 1                   | 905.1  | 1336  | 1453               | 1                                        |

| (F=3)            |           | 2                   | 1431.5 | 2102  | 2281               | 2                                        |

|                  |           | 4                   | 2445.9 | 3487  | 3899               | 4                                        |

|                  |           | 8                   | 4568   | 6592  | 6870               | 8                                        |

|                  | TX        | 1                   | 568.7  | 737   | 907                | 0                                        |

|                  |           | 2                   | 790.2  | 1126  | 1126               | 0                                        |

|                  |           | 4                   | 1096.4 | 1659  | 1545               | 0                                        |

|                  |           | 8                   | 1617.1 | 2082  | 2524               | 0                                        |

|                  |           | 1                   | 1047   | 1496  | 1264               | 0                                        |

|                  | RX        | 2                   | 1584   | 2262  | 1903               | 0                                        |

| Intel Arria 10   | KX        | 4                   | 2884.5 | 3870  | 3211               | 0                                        |

|                  |           | 8                   | 5339   | 7196  | 5768               | 0                                        |

|                  | TX        | 1                   | 701.5  | 1090  | 989                | 0                                        |

|                  |           |                     |        |       |                    | continued                                |

<sup>(12)</sup> M10K for Arria V, Cyclone V devices, M20K for Arria V GZ, Stratix V, Intel Arria 10, Intel Cyclone 10 GX, and Intel Stratix 10 devices.

<sup>(13)</sup> The Intel Quartus Prime software may auto-fit to use MLAB when the memory size is too small. Conversion from MLAB to M20K or M10K was performed for the numbers listed above.

| Device Family    | Data Path | Number of Lanes (L) | ALMs   | ALUTs | Logic<br>Registers | Memory Block<br>(M10K/M20K)<br>(12) (13) |

|------------------|-----------|---------------------|--------|-------|--------------------|------------------------------------------|

|                  |           | 2                   | 875.5  | 1341  | 1126               | 0                                        |

|                  |           | 4                   | 1248.5 | 1888  | 1382               | 0                                        |

|                  |           | 8                   | 1917.5 | 2820  | 1878               | 0                                        |

|                  |           | 1                   | 1020.5 | 1496  | 1250               | 1                                        |

|                  | RX        | 2                   | 1551.5 | 2262  | 1877               | 2                                        |

|                  | KA        | 4                   | 2801   | 3870  | 3159               | 4                                        |

| Intel Cyclone 10 |           | 8                   | 5173.5 | 7196  | 5749               | 8                                        |

| ĞX               |           | 1                   | 710    | 1090  | 989                | 0                                        |

|                  | TX        | 2                   | 875.4  | 1341  | 1118               | 0                                        |

|                  | IX        | 4                   | 1249   | 1888  | 1369               | 0                                        |

|                  |           | 8                   | 1926.5 | 2820  | 1869               | 0                                        |

|                  |           | 1                   | 1047.2 | 1530  | 1225               | 0                                        |

|                  | RX        | 2                   | 1608.7 | 2322  | 1871               | 0                                        |

|                  |           | 4                   | 2897.2 | 4037  | 3161               | 0                                        |

| Stratix V        |           | 8                   | 5412.5 | 7506  | 5742               | 0                                        |

| Stratix V        |           | 1                   | 711    | 1152  | 948                | 0                                        |

|                  | TX        | 2                   | 926.7  | 1491  | 1086               | 0                                        |

|                  | 17        | 4                   | 1345.7 | 2134  | 1361               | 0                                        |

|                  |           | 8                   | 2114.7 | 3358  | 1907               | 0                                        |

|                  |           | 1                   | 1024.5 | 1516  | 1207               | 1                                        |

|                  | RX        | 2                   | 1555.5 | 2302  | 1838               | 2                                        |

|                  | NA.       | 4                   | 2769.5 | 3951  | 3102               | 4                                        |

| Arria V          |           | 8                   | 5189   | 7399  | 5619               | 8                                        |

| Airia v          |           | 1                   | 711.7  | 1149  | 948                | 0                                        |

|                  | TX        | 2                   | 860.5  | 1418  | 1065               | 0                                        |

|                  | 1.^       | 4                   | 1188.7 | 1932  | 1299               | 0                                        |

|                  |           | 8                   | 1721   | 2854  | 1767               | 0                                        |

|                  |           | 1                   | 1048.7 | 1530  | 1226               | 0                                        |

| Arria V GZ       | RX        | 2                   | 1601.5 | 2322  | 1870               | 0                                        |

|                  |           | 4                   | 2894   | 4037  | 3163               | 0                                        |

|                  |           |                     |        |       |                    | continued                                |

<sup>(12)</sup> M10K for Arria V, Cyclone V devices, M20K for Arria V GZ, Stratix V, Intel Arria 10, Intel Cyclone 10 GX, and Intel Stratix 10 devices.

<sup>(13)</sup> The Intel Quartus Prime software may auto-fit to use MLAB when the memory size is too small. Conversion from MLAB to M20K or M10K was performed for the numbers listed above.

### UG-01142 | 2020.03.03

| Device Family | Data Path    | Number of<br>Lanes (L) | ALMs   | ALUTS | Logic<br>Registers | Memory Block<br>(M10K/M20K)<br>(12) (13) |

|---------------|--------------|------------------------|--------|-------|--------------------|------------------------------------------|

|               |              | 8                      | 5400.5 | 7506  | 5748               | 0                                        |

|               |              | 1                      | 712.2  | 1152  | 948                | 0                                        |

|               | TX           | 2                      | 926.5  | 1491  | 1087               | 0                                        |

|               | 1.           | 4                      | 1349.2 | 2134  | 1359               | 0                                        |

|               |              | 8                      | 2104.7 | 3358  | 1907               | 0                                        |

| Cyclone V     | Cyclone V RX | 1                      | 1022   | 1516  | 1210               | 1                                        |

|               |              | 2                      | 1555.5 | 2302  | 1839               | 2                                        |

|               |              | 4                      | 2777.5 | 3951  | 3099               | 4                                        |

|               |              | 8                      | 5195   | 7399  | 5619               | 8                                        |

|               |              | 1                      | 713.5  | 1149  | 948                | 0                                        |

|               |              | 2                      | 867    | 1418  | 1066               | 0                                        |

|               |              | 4                      | 1198   | 1932  | 1300               | 0                                        |

|               |              | 8                      | 1709.2 | 2838  | 1769               | 0                                        |

### **Related Information**

JESD204B Intel FPGA IP Parameters on page 36

<sup>(13)</sup> The Intel Quartus Prime software may auto-fit to use MLAB when the memory size is too small. Conversion from MLAB to M20K or M10K was performed for the numbers listed above.

$<sup>^{(12)}</sup>$  M10K for Arria V, Cyclone V devices, M20K for Arria V GZ, Stratix V, Intel Arria 10, Intel Cyclone 10 GX, and Intel Stratix 10 devices.

# 3. Getting Started

#### **Related Information**

- Intel FPGA Software Installation & Licensing

- Introduction to Intel FPGA IP Cores

Provides general information about all Intel FPGA IP cores, including parameterizing, generating, upgrading, and simulating IP cores.

- Creating Version-Independent IP and Platform Designer Simulation Scripts

Create simulation scripts that do not require manual updates for software or IP

version upgrades.

- Project Management Best Practices

Guidelines for efficient management and portability of your project and IP files.

### 3.1. Introduction to Intel FPGA IP Cores

Intel and strategic IP partners offer a broad portfolio of configurable IP cores optimized for Intel FPGA devices.

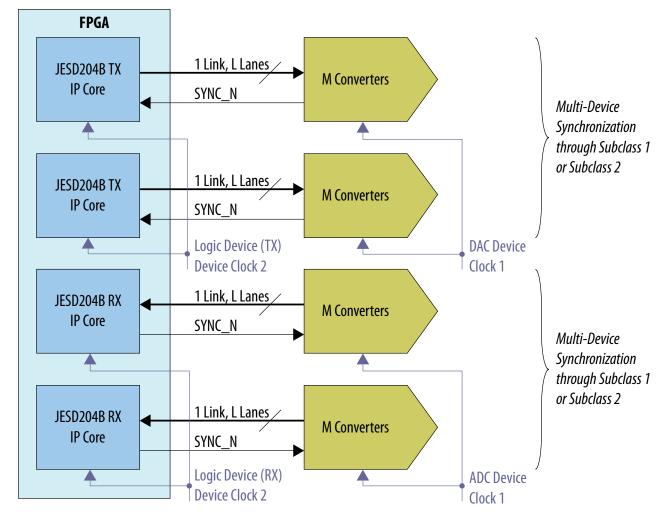

The Intel Quartus Prime software installation includes the Intel FPGA IP library. Integrate optimized and verified Intel FPGA IP cores into your design to shorten design cycles and maximize performance. The Intel Quartus Prime software also supports integration of IP cores from other sources. Use the IP Catalog (**Tools** ➤ **IP Catalog**) to efficiently parameterize and generate synthesis and simulation files for your custom IP variation. The Intel FPGA IP library includes the following types of IP cores:

- Basic functions

- DSP functions

- Interface protocols

- Low power functions

- Memory interfaces and controllers

- Processors and peripherals

This document provides basic information about parameterizing, generating, upgrading, and simulating stand-alone IP cores in the Intel Quartus Prime software.

Figure 2. IP Catalog

### 3.2. Installing and Licensing Intel FPGA IP Cores

The Intel Quartus Prime software installation includes the Intel FPGA IP library. This library provides many useful IP cores for your production use without the need for an additional license. Some Intel FPGA IP cores require purchase of a separate license for production use. The Intel FPGA IP Evaluation Mode allows you to evaluate these licensed Intel FPGA IP cores in simulation and hardware, before deciding to purchase a full production IP core license. You only need to purchase a full production license for licensed Intel IP cores after you complete hardware testing and are ready to use the IP in production.

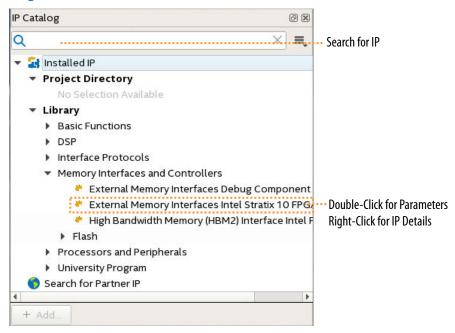

The Intel Quartus Prime software installs IP cores in the following locations by default:

#### Figure 3. IP Core Installation Path

#### Table 11. IP Core Installation Locations

| Location                                                               | Software                                | Platform |

|------------------------------------------------------------------------|-----------------------------------------|----------|

| <pre><drive>:\intelFPGA_pro\quartus\ip\altera</drive></pre>            | Intel Quartus Prime Pro Edition         | Windows* |

| <pre><drive>:\intelFPGA\quartus\ip\altera</drive></pre>                | Intel Quartus Prime Standard<br>Edition | Windows  |

| <pre><home directory="">:/intelFPGA_pro/quartus/ip/altera</home></pre> | Intel Quartus Prime Pro Edition         | Linux*   |

| <pre><home directory="">:/intelFPGA/quartus/ip/altera</home></pre>     | Intel Quartus Prime Standard<br>Edition | Linux    |

Note: The Intel Quartus Prime software does not support spaces in the installation path.

#### 3.3. Intel FPGA IP Evaluation Mode

The free Intel FPGA IP Evaluation Mode allows you to evaluate licensed Intel FPGA IP cores in simulation and hardware before purchase. Intel FPGA IP Evaluation Mode supports the following evaluations without additional license:

- Simulate the behavior of a licensed Intel FPGA IP core in your system.

- Verify the functionality, size, and speed of the IP core quickly and easily.

- Generate time-limited device programming files for designs that include IP cores.

- Program a device with your IP core and verify your design in hardware.

Intel FPGA IP Evaluation Mode supports the following operation modes:

- **Tethered**—Allows running the design containing the licensed Intel FPGA IP indefinitely with a connection between your board and the host computer. Tethered mode requires a serial joint test action group (JTAG) cable connected between the JTAG port on your board and the host computer, which is running the Intel Quartus Prime Programmer for the duration of the hardware evaluation period. The Programmer only requires a minimum installation of the Intel Quartus Prime software, and requires no Intel Quartus Prime license. The host computer controls the evaluation time by sending a periodic signal to the device via the JTAG port. If all licensed IP cores in the design support tethered mode, the evaluation time runs until any IP core evaluation expires. If all of the IP cores support unlimited evaluation time, the device does not time-out.

- **Untethered**—Allows running the design containing the licensed IP for a limited time. The IP core reverts to untethered mode if the device disconnects from the host computer running the Intel Quartus Prime software. The IP core also reverts to untethered mode if any other licensed IP core in the design does not support tethered mode.

When the evaluation time expires for any licensed Intel FPGA IP in the design, the design stops functioning. All IP cores that use the Intel FPGA IP Evaluation Mode time out simultaneously when any IP core in the design times out. When the evaluation time expires, you must reprogram the FPGA device before continuing hardware verification. To extend use of the IP core for production, purchase a full production license for the IP core.

You must purchase the license and generate a full production license key before you can generate an unrestricted device programming file. During Intel FPGA IP Evaluation Mode, the Compiler only generates a time-limited device programming file (ct name>\_time\_limited.sof) that expires at the time limit.

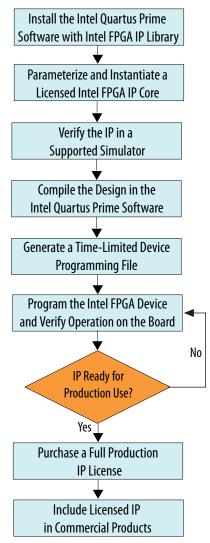

Figure 4. Intel FPGA IP Evaluation Mode Flow

Note: Refer to each IP core's user guide for parameterization steps and implementation details.

Intel licenses IP cores on a per-seat, perpetual basis. The license fee includes first-year maintenance and support. You must renew the maintenance contract to receive updates, bug fixes, and technical support beyond the first year. You must purchase a full production license for Intel FPGA IP cores that require a production license, before generating programming files that you may use for an unlimited time. During Intel FPGA IP Evaluation Mode, the Compiler only generates a time-limited device programming file (project name>\_time\_limited.sof) that expires at the time limit. To obtain your production license keys, visit the Self-Service Licensing Center.

The Intel FPGA Software License Agreements govern the installation and use of licensed IP cores, the Intel Quartus Prime design software, and all unlicensed IP cores.

#### **Related Information**

- Intel Quartus Prime Licensing Site

- Introduction to Intel FPGA Software Installation and Licensing

### 3.4. Upgrading IP Cores

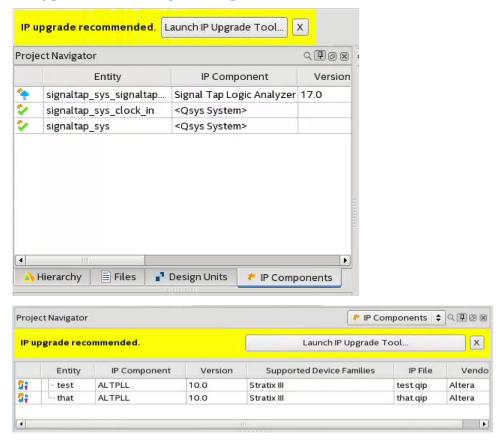

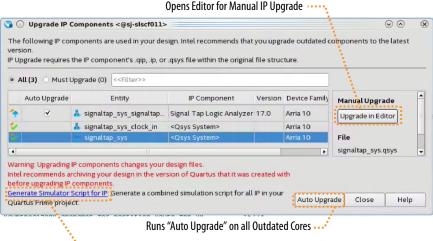

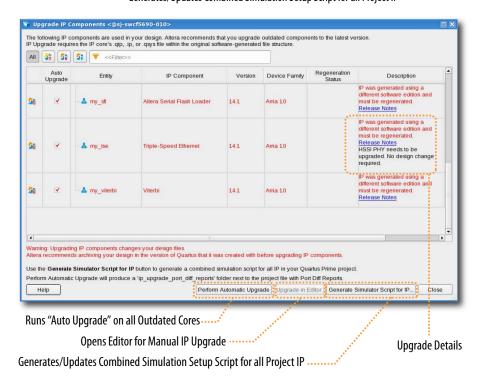

Any Intel FPGA IP variations that you generate from a previous version or different edition of the Intel Quartus Prime software, may require upgrade before compilation in the current software edition or version. The Project Navigator displays a banner indicating the IP upgrade status. Click **Launch IP Upgrade Tool** or **Project** ➤ **Upgrade IP Components** to upgrade outdated IP cores.

Figure 5. IP Upgrade Alert in Project Navigator

Icons in the **Upgrade IP Components** dialog box indicate when IP upgrade is required, optional, or unsupported for an IP variation in the project. Upgrade IP variations that require upgrade before compilation in the current version of the Intel Quartus Prime software.

#### UG-01142 | 2020.03.03

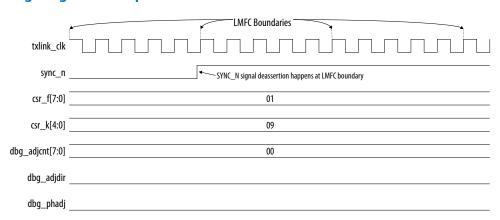

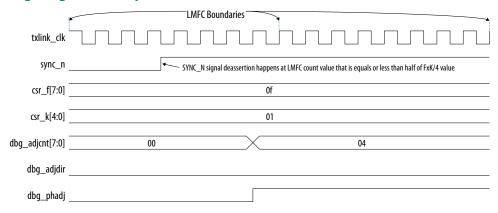

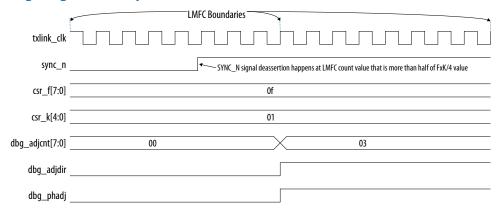

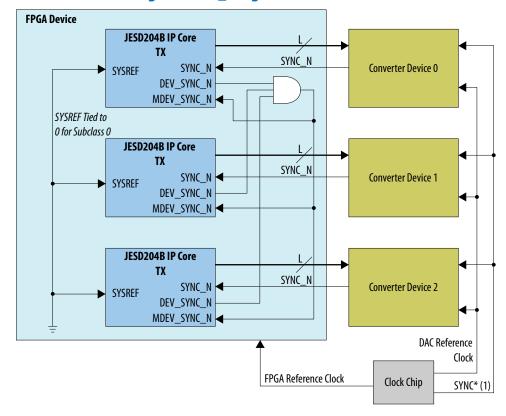

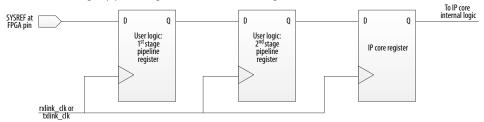

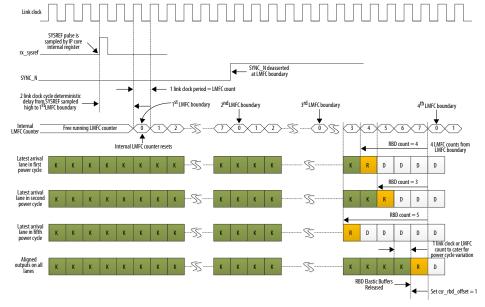

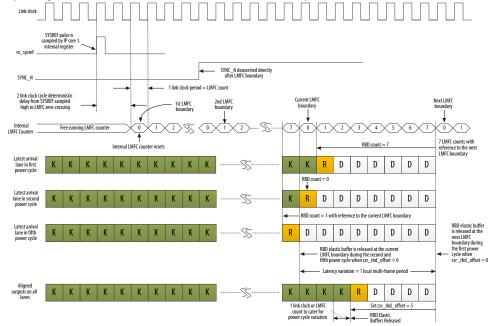

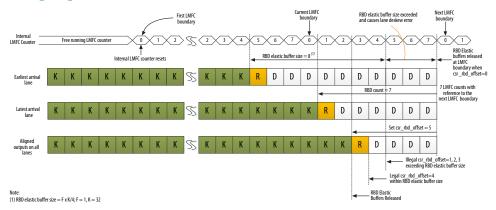

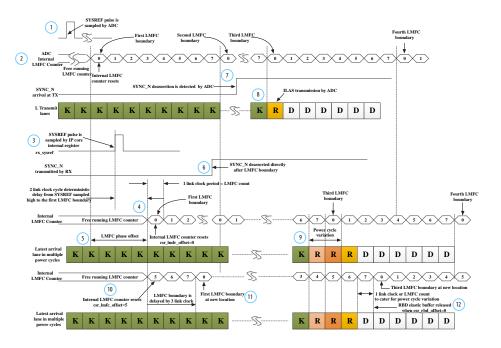

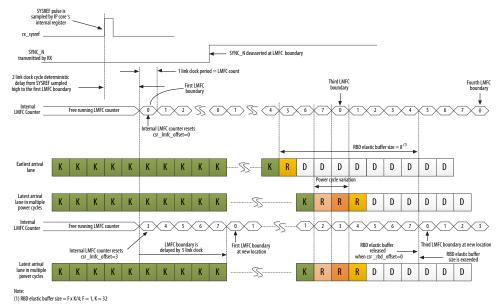

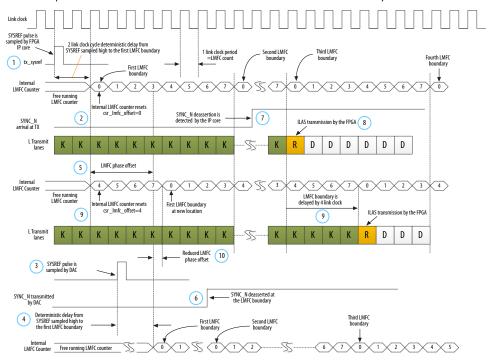

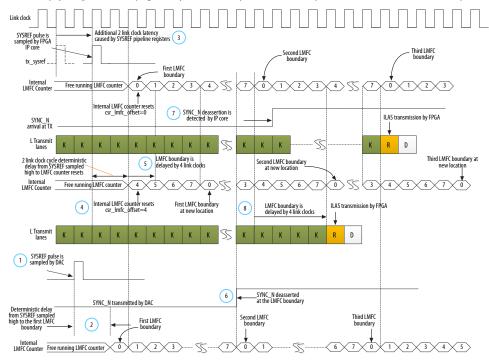

Note: