"Spansion, Inc." and "Cypress Semiconductor Corp." have merged together to deliver high-performance, high-quality solutions at the heart of today's most advanced embedded systems, from automotive, industrial and networking platforms to highly interactive consumer and mobile devices. The new company "Cypress Semiconductor Corp." will continue to offer "Spansion, Inc." products to new and existing customers.

### **Continuity of Specifications**

There is no change to this document as a result of offering the device as a Cypress product. Any changes that have been made are the result of normal document improvements and are noted in the document history page, where supported. Future revisions will occur when appropriate, and changes will be noted in a document history page.

### **Continuity of Ordering Part Numbers**

Cypress continues to support existing part numbers. To order these products, please use only the Ordering Part Numbers listed in this document.

### For More Information

Please contact your local sales office for additional information about Cypress products and solutions.

## S98GL064NB0-007 MCP S98GL064NB0-008 MCP

64 Mbit (4M x 16-bit), 3 V, Flash and 32 Mbit (2M x 16-bit) Async Pseudo Static RAM

# **Distinctive Characteristics**

### **MCP** Features

- Power supply voltage of 2.7 to 3.6 volt

- High performance

- 90 ns access time (90 ns Flash, 70 ns pSRAM/SRAM)

- 25 ns page read times

## **General Description**

The S98GL064NB0-007, -008 product series consists of:

- One S29GL064N flash memory device

- Top Boot (-007)

- Bottom Boot (-008)

- One 32 Mb asynchronous pSRAM (SPG032D970R3R)

Packages

- 7 x 9 x 1.2 mm 56-ball FBGA

- Operating temperature

- -40°C to +85°C

For detailed specifications, please refer to the individual data sheets.

| Document      | Publication Identification Number (PID) |  |

|---------------|-----------------------------------------|--|

| S29GL-N       | S29GL-N_00                              |  |

| SPG032D970R3R | SPG032D970R3R                           |  |

198 Champion Court

٠

# 1. Product Selector Guide

| Device-Model#         | Flash Access<br>time (ns) | (p)SRAM<br>density | (p)SRAM Access time<br>(ns) | (p)SRAM type  | Package |

|-----------------------|---------------------------|--------------------|-----------------------------|---------------|---------|

| S98GL064NB0-007, -008 | 90                        | 32 Mb              | 70                          | SPG032D970R3R | TLC056  |

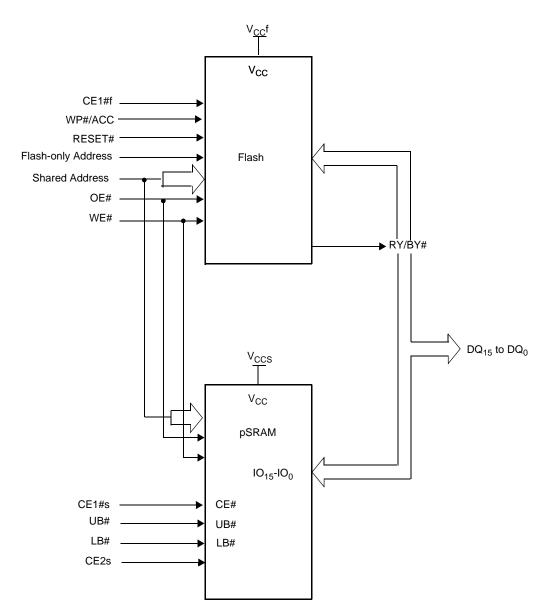

# 2. MCP Block Diagram

# 3. Connection Diagram

56-ball Fine-Pitch Ball Grid Array

| MCP         | Flash-only Addresses | Shared Addresses |

|-------------|----------------------|------------------|

| S98GL064NB0 | A21                  | A20-A0           |

# 3.1 Special Handling Instructions For FBGA Package

Special handling is required for flash memory products in FBGA packages.

Flash memory devices in FBGA packages may be damaged if exposed to ultrasonic cleaning methods. The package and/or data integrity may be compromised if the package body is exposed to temperatures above 150°C for prolonged periods of time.

# 4. Pin Description

| Pin               | Description                                                                                                                                                                                                                                                                                                                               |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A21–A0            | 22 Address Inputs (Common and Flash only) (A20-A0 for the S71GL032N)                                                                                                                                                                                                                                                                      |

| DQ15-DQ0          | 16 Data Inputs/Outputs (Common)                                                                                                                                                                                                                                                                                                           |

| CE1#f             | Chip Enable (Flash)                                                                                                                                                                                                                                                                                                                       |

| CE1#s             | Chip Enable 1 (pSRAM/SRAM)                                                                                                                                                                                                                                                                                                                |

| CE2s              | Chip Enable 2 (pSRAM/SRAM)                                                                                                                                                                                                                                                                                                                |

| OE#               | Output Enable (Common)                                                                                                                                                                                                                                                                                                                    |

| WE#               | Write Enable (Common)                                                                                                                                                                                                                                                                                                                     |

| RY/BY#            | Ready/Busy Output (Flash 1)                                                                                                                                                                                                                                                                                                               |

| UB#               | Upper Byte Control (pSRAM/SRAM)                                                                                                                                                                                                                                                                                                           |

| LB#               | Lower Byte Control (pSRAM/SRAM)                                                                                                                                                                                                                                                                                                           |

| RESET#            | Hardware Reset Pin, Active Low (Flash)                                                                                                                                                                                                                                                                                                    |

| WP#/ACC           | Hardware Write Protect/Acceleration Pin (Flash)                                                                                                                                                                                                                                                                                           |

| V <sub>CC</sub> f | Flash 3.0 volt-only single power supply (see <i>Product Selector Guide</i> for speed options and voltage supply tolerances)                                                                                                                                                                                                               |

| V <sub>CCS</sub>  | pSRAM/SRAM Power Supply                                                                                                                                                                                                                                                                                                                   |

| V <sub>SS</sub>   | Device Ground (Common)                                                                                                                                                                                                                                                                                                                    |

| NC                | Not Connected. No device internal signal is connected to the package connector nor is there any future plan to use the connector for a signal. The connection may safely be used for routing space for a signal on a Printed Circuit Board (PCB).                                                                                         |

| RFU               | Reserved for Future Use. No device internal signal is currently connected to the package connector but there is potential future use for the connector for a signal. It is recommended to not use RFU connectors for PCB routing channels so that the PCB may take advantage of future enhanced features in compatible footprint devices. |

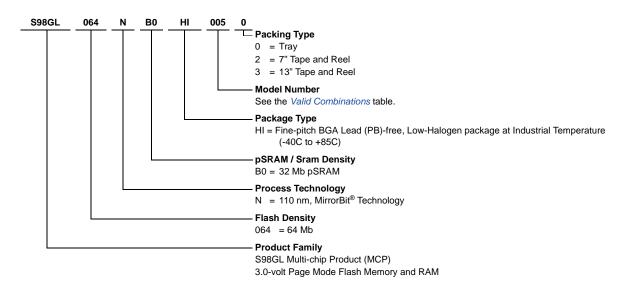

# 5. Ordering Information

The order number is formed by a valid combinations of the following:

#### Valid Combinations

| S98GL064NB0 Valid Combinations |                          |                                    | Speed Options (ns) / | (p)SRAM Type /          |                  |         |

|--------------------------------|--------------------------|------------------------------------|----------------------|-------------------------|------------------|---------|

| Base Ordering<br>Part Number   | Package &<br>Temperature | Package Modifier /<br>Model Number | Packing Type         | Boot Sector Option      | Access Time (ns) | Package |

| S98GL064NB0                    | D64NB0 HI                | 007                                | 0, 2, 3 (1)          | 90 / Top Boot Sector    | SPG032D970R3R    | TLC056  |

| 390GL004INB0                   |                          | 008                                |                      | 90 / Bottom Boot Sector | 3FG032D970R3R    | TLC056  |

Note

1. Type 0 is standard. Specify other options as required.

### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult your local sales office to confirm availability of specific valid combinations and to check on newly released combinations.

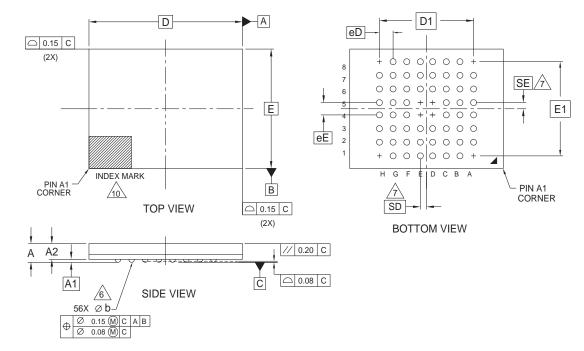

## 6. Physical Dimensions

## 6.1 TLC056—56-ball Fine-Pitch Ball Grid Array (FBGA) 9 x 7 mm Package

| PACKAGE | TLC 056                      |      |      |                          |

|---------|------------------------------|------|------|--------------------------|

| JEDEC   | N/A                          |      |      |                          |

| D x E   | 9.00 mm x 7.00 mm<br>PACKAGE |      |      |                          |

| SYMBOL  | MIN                          | NOM  | MAX  | NOTE                     |

| A       |                              |      | 1.20 | PROFILE                  |

| A1      | 0.20                         |      |      | BALL HEIGHT              |

| A2      | 0.81                         |      | 0.97 | BODY THICKNESS           |

| D       | 9.00 BSC.                    |      |      | BODY SIZE                |

| E       | 7.00 BSC.                    |      |      | BODY SIZE                |

| D1      | 5.60 BSC.                    |      |      | MATRIX FOOTPRINT         |

| E1      | 5.60 BSC.                    |      |      | MATRIX FOOTPRINT         |

| MD      | 8                            |      |      | MATRIX SIZE D DIRECTION  |

| ME      | 8                            |      |      | MATRIX SIZE E DIRECTION  |

| n       | 56                           |      |      | BALL COUNT               |

| φb      | 0.35                         | 0.40 | 0.45 | BALL DIAMETER            |

| eE      | 0.80 BSC.                    |      |      | BALL PITCH               |

| eD      | 0.80 BSC                     |      |      | BALL PITCH               |

| SD / SE | 0.40 BSC.                    |      |      | SOLDER BALL PLACEMENT    |

|         | A1,A8,D4,D5,E4,E5,H1,H8      |      |      | DEPOPULATED SOLDER BALLS |

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING METHODS PER ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS.

- 3. BALL POSITION DESIGNATION PER JESD 95-1, SPP-010.

- 4. e REPRESENTS THE SOLDER BALL GRID PITCH.

- 5. SYMBOL "MD" IS THE BALL MATRIX SIZE IN THE "D" DIRECTION.

- SYMBOL "ME" IS THE BALL MATRIX SIZE IN THE "E" DIRECTION.

${\sf n}$  IS THE NUMBER OF POPULTED SOLDER BALL POSITIONS FOR MATRIX SIZE MD X ME.

- DIMENSION "b" IS MEASURED AT THE MAXIMUM BALL DIAMETER IN A PLANE PARALLEL TO DATUM C.

- A SD AND SE ARE MEASURED WITH RESPECT TO DATUMS A AND B AND DEFINE THE POSITION OF THE CENTER SOLDER BALL IN THE OUTER ROW.

WHEN THERE IS AN ODD NUMBER OF SOLDER BALLS IN THE OUTER ROW SD OR SE = 0.000.

WHEN THERE IS AN EVEN NUMBER OF SOLDER BALLS IN THE OUTER ROW, SD OR SE =  $\fbox{0/2}$

8. "+" INDICATES THE THEORETICAL CENTER OF DEPOPULATED BALLS.

9. N/A

A1 CORNER TO BE IDENTIFIED BY CHAMFER, LASER OR INK MARK, METALLIZED MARK INDENTATION OR OTHER MEANS.

3348 \ 16-038.22a

# 7. Revision History

Spansion Publication Number: S98GL064NB0-007\_008

| Section                        | Description     |  |

|--------------------------------|-----------------|--|

| Revision 01 (October 21, 2014) |                 |  |

|                                | Initial release |  |

## **Document History Page**

| Document Title: S98GL064NB0-007 MCP, S98GL064NB0-008 MCP 64 Mbit (4M x 16 bit), 3 V, Flash and 32 Mbit (2M x 16 bit)<br>Async Pseudo Static RAM<br>Document Number: 002-00509 |         |                    |                    |                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|-----------------------------|

| Rev.                                                                                                                                                                          | ECN No. | Orig. of<br>Change | Submission<br>Date | Description of Change       |

| **                                                                                                                                                                            | —       | RYSU               | 10/21/2014         | Initial release             |

| *A                                                                                                                                                                            | 4996550 | RYSU               | 10/30/2015         | Updated to Cypress template |

### Sales, Solutions, and Legal Information

### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### Products

| Automotive               | cypress.com/go/automotive |

|--------------------------|---------------------------|

| Clocks & Buffers         | cypress.com/go/clocks     |

| Interface                | cypress.com/go/interface  |

| Lighting & Power Control | cypress.com/go/powerpsoc  |

| Memory                   | cypress.com/go/memory     |

| PSoC                     | cypress.com/go/psoc       |

| Touch Sensing            | cypress.com/go/touch      |

| USB Controllers          | cypress.com/go/USB        |

| Wireless/RF              | cypress.com/go/wireless   |

### PSoC<sup>®</sup> Solutions

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

#### **Cypress Developer Community**

Community | Forums | Blogs | Video | Training

#### **Technical Support**

cypress.com/go/support

© Cypress Semiconductor Corporation, 2014-2015. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

#### Document Number: 002-00509 Rev. \*A

#### Revised November 04, 2015

Page 7 of 7

Cypress<sup>®</sup>, Spansion<sup>®</sup>, MirrorBit<sup>®</sup>, MirrorBit<sup>®</sup> Eclipse™, ORNAND™, HyperBus™, HyperFlash™, and combinations thereof, are trademarks and registered trademarks of Cypress Semiconductor Corp. All products and company names mentioned in this document may be the trademarks of their respective holders.