# **General Description**

DA7217 is a high-performance, low-power audio codec optimized for use in headsets or wearable devices. It has differential headphone outputs for use inside headset devices, offering excellent left to right channel separation and common mode noise rejection. DA7217 also has a stereo DAC to headphone output path and ultra-low power operating modes to support always-on audio detect applications.

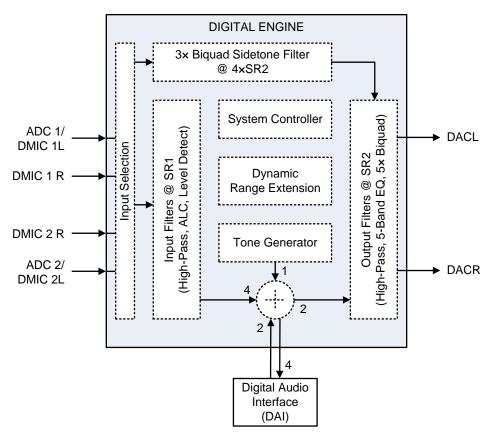

DA7217 contains two analog microphone input paths, or up to four digital microphone input paths, or a combination of both. The other chip in this family, the DA7218, has single-ended headphone outputs, and has been designed with headphone detect for use in accessories.

# **Key Features**

- High performance stereo DAC to headphone

playback path with 110 dB dynamic range

- 4 mW stereo playback power consumption

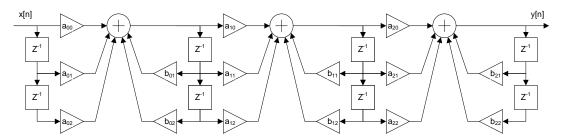

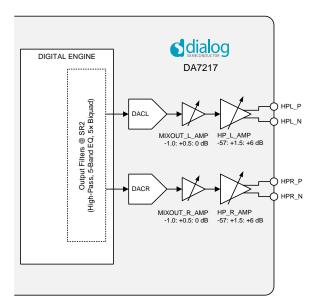

- DAC digital filters with audio and voice mode options, five-band equalizer and five programmable biguad stages

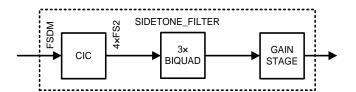

- Dedicated low-latency digital sideband filter with three programmable biquad stages

- High performance microphone to ADC record path with 105 dB dynamic range

- 2.5 mW stereo record power consumption

- ADC digital filters with audio and voice mode options

- 500 µW always-on record mode with automatic level detection

- Hybrid analog / digital automatic level control to dynamically control the record level

- Shutdown mode offering current consumption during standby of 2.5 µA

- Two low-noise microphone bias regulators with programmable output voltage and ultralow power mode

- A high efficiency two-level, true-ground charge pump for generating class-G headphone supplies

- Voice mode filtering up to 32 kHz

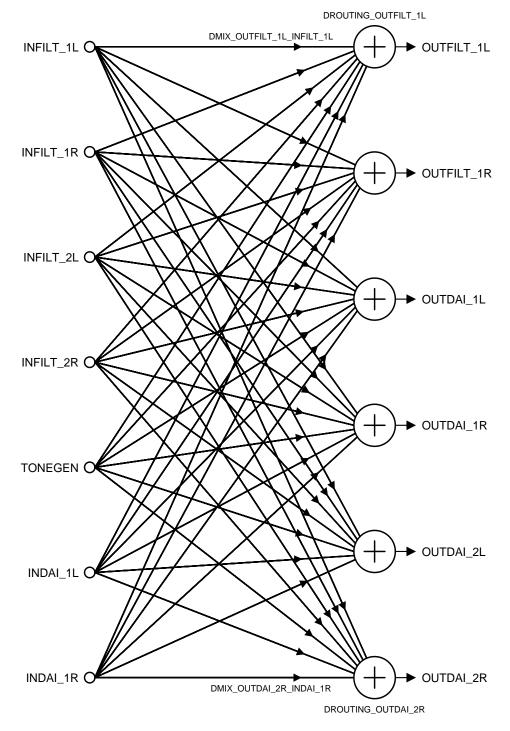

#### Flexible digital mixing from all seven inputs to all six outputs with independent gain on each mixer path

- Ability to run the ADCs at a different sample rate to the DACs on a single I<sup>2</sup>S interface

- Digital tone generator with built-in support for DTMF

- System controller for simplified, pop-free startup and shutdown

- Phase-locked loop with sample rate tracking supporting MCLK frequencies from 2 MHz to 54 MHz

- Automatic tuning of on-chip reference oscillator for clock-free operation in low-power modes

- 4-wire digital audio interface with support for I<sup>2</sup>S, four-channel I<sup>2</sup>S, TDM and other audio formats

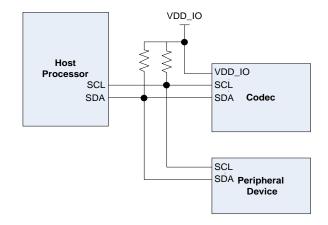

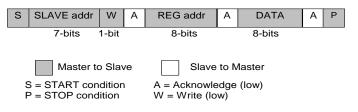

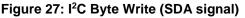

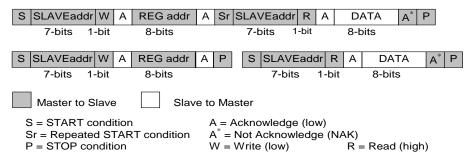

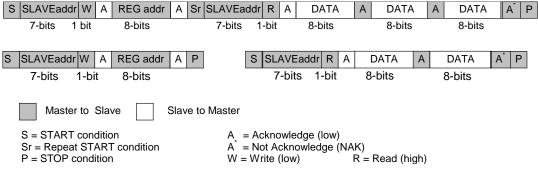

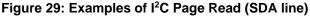

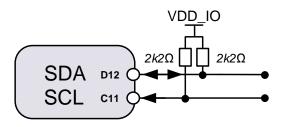

- 2-wire I<sup>2</sup>C compatible control interface with support for High Speed mode up to 3.4 MHz

- 24-bit data at up to 96 kHz sample rate

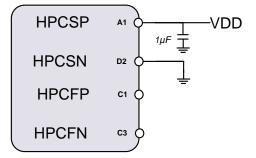

- The headphone amplifier can be run directly from the supply, thus eliminating the need for charge pump capacitors

# **Applications**

- Hearables

- Wireless and wired headphones

- Wireless and wired headsets

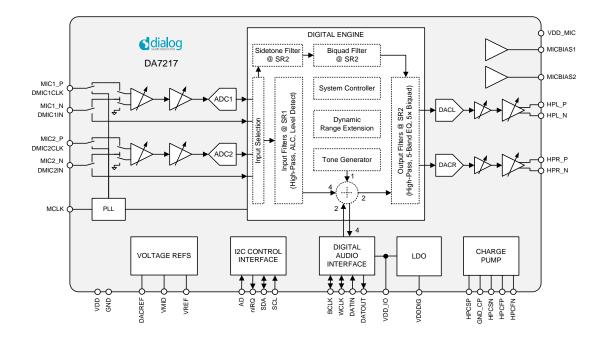

# System Diagram

Figure 1: DA7217 with Differential Stereo Headphone Outputs

**Datasheet**

# **DA7217**

# **Ultra-Low Power Stereo Codec**

# Contents

| Ge | eneral I | Descriptio                  | on                | 1  |  |  |  |  |  |  |

|----|----------|-----------------------------|-------------------|----|--|--|--|--|--|--|

| Ke | y Feat   | ures                        |                   | 1  |  |  |  |  |  |  |

| Ар | plicati  | ons                         |                   | 1  |  |  |  |  |  |  |

| Sv | stem D   | Diagram                     |                   | 2  |  |  |  |  |  |  |

| •  |          | U                           |                   |    |  |  |  |  |  |  |

| 1  |          |                             | finitions         | -  |  |  |  |  |  |  |

|    |          |                             |                   |    |  |  |  |  |  |  |

| 2  |          | •••                         |                   |    |  |  |  |  |  |  |

| 3  | Block    | Block Diagram               |                   |    |  |  |  |  |  |  |

| 4  | Pinou    | nout                        |                   |    |  |  |  |  |  |  |

|    | 4.1      |                             |                   |    |  |  |  |  |  |  |

|    |          | 4.1.1                       | MIC1_P (DMIC1CLK) |    |  |  |  |  |  |  |

|    |          | 4.1.2                       | MIC1_N (DMIC1IN)  |    |  |  |  |  |  |  |

|    |          | 4.1.3                       | MIC2_P (DMIC2CLK) | 11 |  |  |  |  |  |  |

|    |          | 4.1.4                       | MIC2_N (DMIC2IN)  | 11 |  |  |  |  |  |  |

|    |          | 4.1.5                       | MCLK              | 11 |  |  |  |  |  |  |

|    |          | 4.1.6                       | SCL               | 11 |  |  |  |  |  |  |

|    |          | 4.1.7                       | AD                | 12 |  |  |  |  |  |  |

|    |          | 4.1.8                       | DATIN             | 12 |  |  |  |  |  |  |

|    | 4.2      | Output P                    | ins               | 12 |  |  |  |  |  |  |

|    |          | 4.2.1                       | nIRQ              | 12 |  |  |  |  |  |  |

|    |          | 4.2.2                       | DATOUT            | 12 |  |  |  |  |  |  |

|    | 4.3      | Bi-Directional Pins         |                   |    |  |  |  |  |  |  |

|    |          | 4.3.1                       | SDA               | 12 |  |  |  |  |  |  |

|    |          | 4.3.2                       | BCLK              | 12 |  |  |  |  |  |  |

|    |          | 4.3.3                       | WCLK              | 12 |  |  |  |  |  |  |

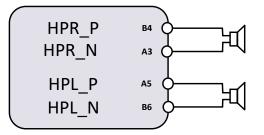

|    | 4.4      | Differential Headphone Pins |                   |    |  |  |  |  |  |  |

|    |          | 4.4.1                       | HPL_P             | 12 |  |  |  |  |  |  |

|    |          | 4.4.2                       | HPL_N             | 12 |  |  |  |  |  |  |

|    |          | 4.4.3                       | HPR_P             |    |  |  |  |  |  |  |

|    |          | 4.4.4                       | HPR_N             | 12 |  |  |  |  |  |  |

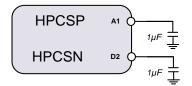

|    | 4.5      | Charge F                    | Pump Pins         | 13 |  |  |  |  |  |  |

|    |          | 4.5.1                       | HPCSP             | 13 |  |  |  |  |  |  |

|    |          | 4.5.2                       | HPCSN             | 13 |  |  |  |  |  |  |

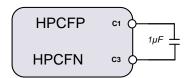

|    |          | 4.5.3                       | HPCFP             | 13 |  |  |  |  |  |  |

|    |          | 4.5.4                       | HPCFN             | 13 |  |  |  |  |  |  |

|    | 4.6      | Reference                   | es                | -  |  |  |  |  |  |  |

|    |          | 4.6.1                       | VMID              | 13 |  |  |  |  |  |  |

|    |          | 4.6.2                       | DACREF            | 13 |  |  |  |  |  |  |

|    |          | 4.6.3                       | VREF              | 13 |  |  |  |  |  |  |

|    |          | 4.6.4                       | MICBIAS1          | 13 |  |  |  |  |  |  |

|    |          | 4.6.5                       | MICBIAS2          |    |  |  |  |  |  |  |

|    |          | 4.6.6                       | VDDDIG            |    |  |  |  |  |  |  |

|    | 4.7      |                             | ins               |    |  |  |  |  |  |  |

|    |          | 4.7.1                       | VDD               | 13 |  |  |  |  |  |  |

|    |          |                             |                   |    |  |  |  |  |  |  |

|   |        | 4.7.2       | VDD_IO        |                                                                          | 14 |

|---|--------|-------------|---------------|--------------------------------------------------------------------------|----|

|   |        | 4.7.3       | VDD_MIC       |                                                                          | 14 |

|   | 4.8    | Ground F    |               |                                                                          |    |

|   |        | 4.8.1       |               |                                                                          |    |

|   |        | 4.8.2       | GND_CP        |                                                                          | 14 |

| 5 | Abso   | lute Maxi   | mum Rating    | gs                                                                       | 15 |

| 6 | Reco   | mmende      | d Operating   | Conditions                                                               | 15 |

| 7 | Elect  | rical Cha   | racteristics  |                                                                          | 16 |

| 8 | Digita | al Interfac | es            |                                                                          | 24 |

| 9 | Func   | tional De   | scription     |                                                                          | 27 |

|   | 9.1    | Device C    | peration      |                                                                          | 27 |

|   |        | 9.1.1       | Power Mode    | es                                                                       | 27 |

|   |        |             | 9.1.1.1       | STANDBY Mode                                                             | 27 |

|   |        |             | 9.1.1.2       | ACTIVE Mode                                                              | 27 |

|   | 9.2    | Input Pat   | ths           |                                                                          | 27 |

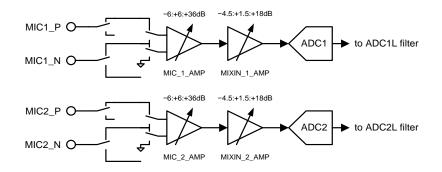

|   |        | 9.2.1       | Microphone    | Inputs                                                                   | 27 |

|   |        |             | 9.2.1.1       | Microphone Biases                                                        |    |

|   |        |             | 9.2.1.2       | Microphone Amplifier                                                     |    |

|   |        |             | 9.2.1.3       | Digital Microphones                                                      |    |

|   |        |             | 9.2.1.4       | Input Amplifiers                                                         |    |

|   |        | 9.2.2       | 0             | igital Converters                                                        |    |

|   |        |             | 9.2.2.1       | High Performance Mode                                                    |    |

|   |        |             | 9.2.2.2       | Low-Power Mode                                                           |    |

|   | 0.0    | Distal F    | 9.2.2.3       | Anti-Alias Filters                                                       |    |

|   | 9.3    | 9.3.1       | -             |                                                                          |    |

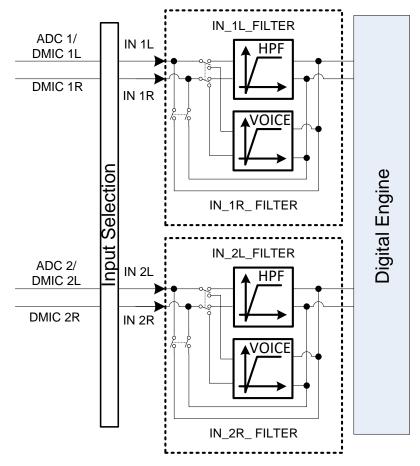

|   |        | 9.3.1       | 9.3.1.1       | ssing<br>Input Filters                                                   |    |

|   |        |             | 9.3.1.1       | High-Pass Filter                                                         |    |

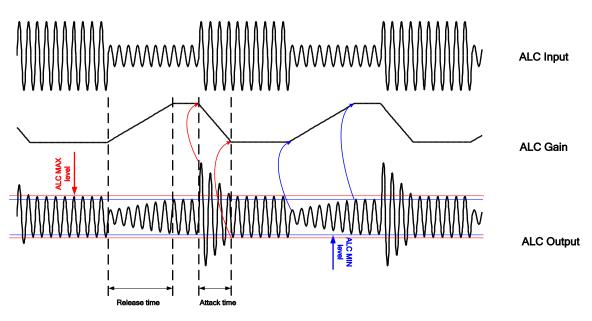

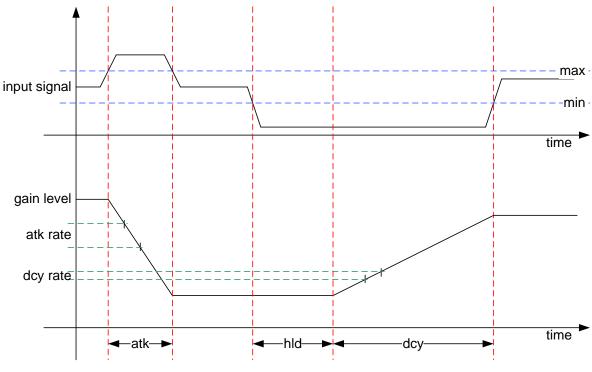

|   |        |             | 9.3.1.2       | Automatic Level Control                                                  |    |

|   |        |             | 9.3.1.4       | Input Dynamic Range Extension                                            |    |

|   |        |             | 9.3.1.5       | Automatic Level Control and Input Dynamic Range Extension<br>Calibration |    |

|   |        |             | 9.3.1.6       | Level Detection                                                          |    |

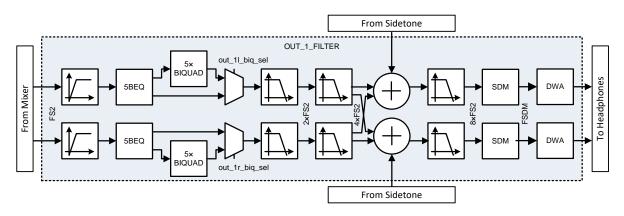

|   |        | 9.3.2       | Sidetone Pr   | ocessing                                                                 | 38 |

|   |        | 9.3.3       | Tone Gener    | rator                                                                    | 41 |

|   |        | 9.3.4       | Output Proc   | cessing                                                                  | 42 |

|   |        |             | 9.3.4.1       | Output Filters                                                           | 42 |

|   |        |             | 9.3.4.2       | High-Pass Filter                                                         | 42 |

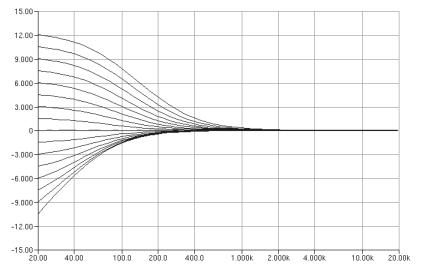

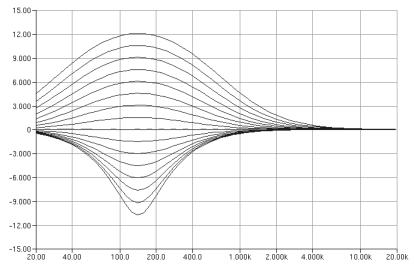

|   |        |             | 9.3.4.3       | 5-Band Equalizer                                                         | 44 |

|   |        |             | 9.3.4.4       | 5-Stage Biquad Filter                                                    | 46 |

|   |        |             | 9.3.4.5       | Output Dynamic Range Extension                                           | 49 |

|   |        |             | 9.3.4.6       | DAC Noise Gate                                                           |    |

|   |        |             | 9.3.4.7       | Digital Mixer                                                            |    |

|   |        | _           | 9.3.4.8       | Digital Gain                                                             |    |

|   | 9.4    |             |               |                                                                          |    |

|   |        | 9.4.1       | Digital to Ar | nalog Converter                                                          | 54 |

Datasheet

#### 01-Feb-2019

|    |        | 9.4.2                       | Headphone    | Amplifiers                                             | 54  |  |  |

|----|--------|-----------------------------|--------------|--------------------------------------------------------|-----|--|--|

|    |        | 9.4.3                       | Charge Pu    | np Control                                             | 57  |  |  |

|    |        |                             | 9.4.3.1      | Charge Pump Initial and Switching Current              | 58  |  |  |

|    |        | 9.4.4                       | Tracking th  | e Demands on the Charge Pump Output                    | 58  |  |  |

|    |        |                             | 9.4.4.1      | cp_mchange = 00 (Manual Mode)                          | 58  |  |  |

|    |        |                             | 9.4.4.2      | cp_mchange = 01 (Tracking the PGA Gain Setting)        | 58  |  |  |

|    |        |                             | 9.4.4.3      | cp_mchange = 10 (Tracking the DAC Signal Setting)      | 58  |  |  |

|    |        |                             | 9.4.4.4      | cp_mchange = 11 (Tracking the Output Signal Magnitude) | 59  |  |  |

|    |        | 9.4.5                       |              | Clock Frequencies when Tracking the Charge Pump Output | 60  |  |  |

|    |        | 9.4.6                       | Other Char   | ge Pump Controls                                       | 60  |  |  |

|    |        | 9.4.7                       | True-Grour   | nd Supply Mode                                         | 60  |  |  |

|    | 9.5    | Phase Lo                    | •            |                                                        |     |  |  |

|    |        | 9.5.1                       | PLL Bypass   | s Mode                                                 | 60  |  |  |

|    |        | 9.5.2                       | Normal PLI   | _ Mode (DAI Master)                                    | 61  |  |  |

|    |        | 9.5.3                       | •            | alculation of the Feedback Divider Setting:            |     |  |  |

|    |        | 9.5.4                       |              | te Matching PLL Mode (DAI Slave)                       |     |  |  |

|    |        | 9.5.5                       | MCLK Inpu    | t                                                      |     |  |  |

|    |        |                             | 9.5.5.1      | MCLK Detection                                         |     |  |  |

|    |        | 9.5.6                       | Audio Refe   | rence Oscillator                                       |     |  |  |

|    |        |                             | 9.5.6.1      | Oscillator Calibration                                 |     |  |  |

|    |        |                             | 9.5.6.2      | Procedure for Calibrating the Reference Oscillator     |     |  |  |

|    |        | 9.5.7 Internal System Clock |              |                                                        |     |  |  |

|    | 9.6    | Reference Generation        |              |                                                        |     |  |  |

|    |        | 9.6.1                       | •            | ferences                                               |     |  |  |

|    |        | 9.6.2                       |              | nts                                                    |     |  |  |

|    |        | 9.6.3                       | 0            | /els                                                   |     |  |  |

|    |        |                             | 9.6.3.1      | Digital Regulator                                      |     |  |  |

|    |        |                             | 9.6.3.2      | Digital Input/Output Pins Voltage Level                |     |  |  |

|    | 9.7    |                             |              |                                                        |     |  |  |

|    | 9.8    | •                           |              | e                                                      |     |  |  |

|    |        | 9.8.1                       |              |                                                        |     |  |  |

|    | ~ ~    | 9.8.2                       | -            | Tristate Mode                                          | -   |  |  |

|    | 9.9    | •                           |              |                                                        |     |  |  |

|    | 0.40   | 9.9.1                       |              | ct Events                                              |     |  |  |

|    | 9.10   | •                           | 0            | ·····                                                  |     |  |  |

|    |        | 9.10.1<br>9.10.2            | •            | Rete                                                   |     |  |  |

|    |        | 9.10.2                      | •            | Rate                                                   |     |  |  |

|    |        | 9.10.3<br>9.10.4            | -            | ounter Control                                         |     |  |  |

|    |        |                             |              |                                                        |     |  |  |

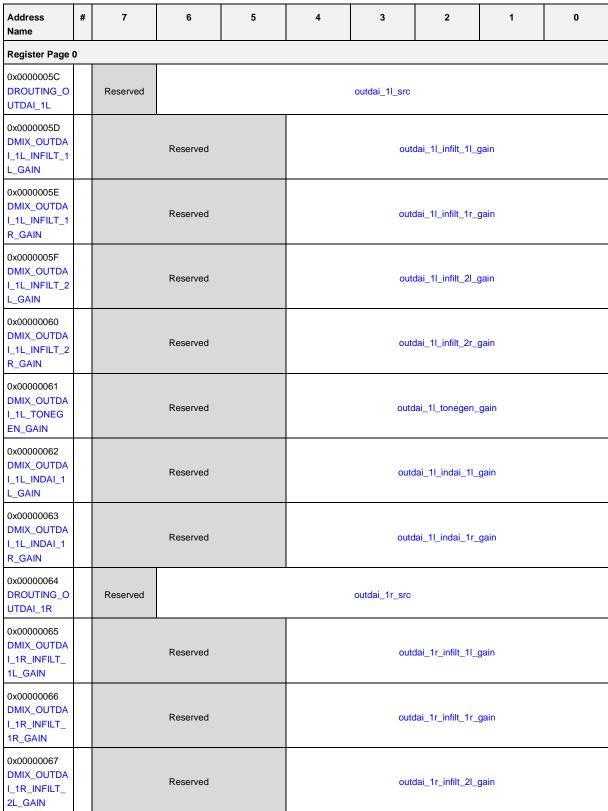

| 10 | -      | -                           |              | tions                                                  |     |  |  |

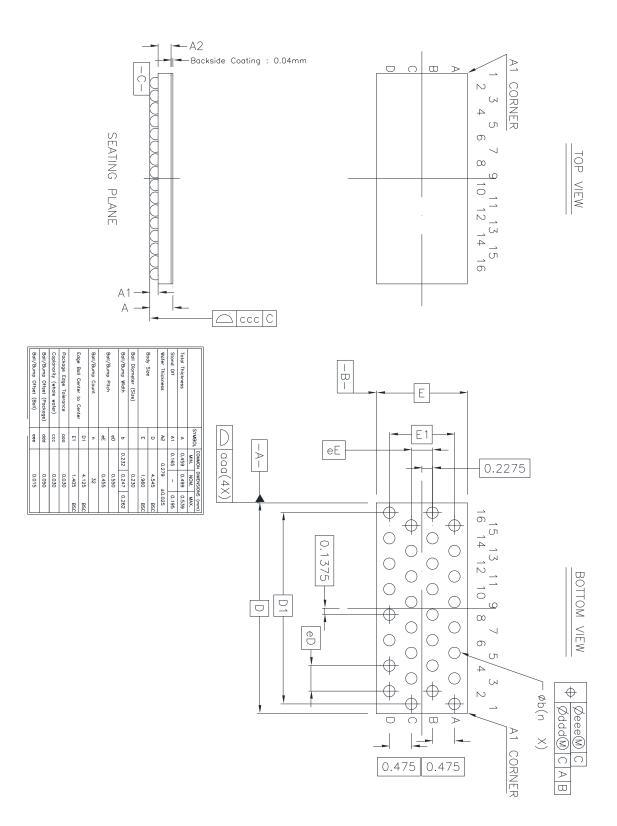

| 11 | Packa  | age Infor                   | mation       |                                                        | 156 |  |  |

| 12 | Exter  | nal Comp                    | oonents      |                                                        | 157 |  |  |

| 13 | Orde   | ring Infor                  | mation       |                                                        | 158 |  |  |

| Ар | pendix | k A Appli                   | cations Info | rmation                                                | 159 |  |  |

| •  | A.1    |                             |              |                                                        |     |  |  |

| - 4 |    |   | _ | - 4 |

|-----|----|---|---|-----|

| ат  | as | n | 0 | ΡТ  |

|     |    |   |   |     |

| A.2     | Automatic Level Control Calibration | 159 |

|---------|-------------------------------------|-----|

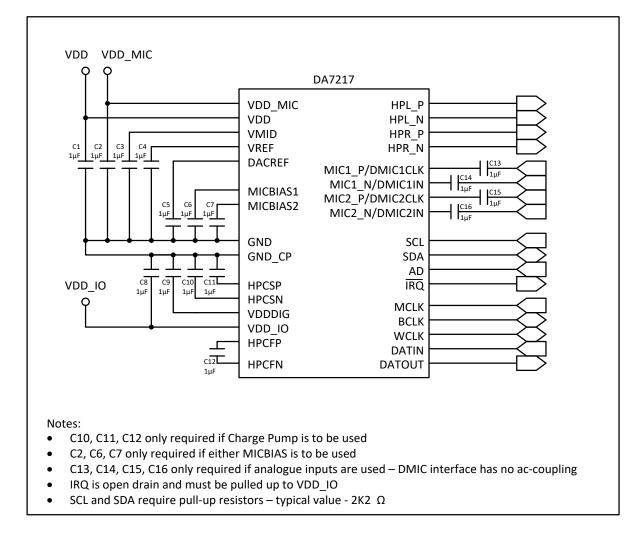

| Appendi | x B Components                      |     |

| B.1     | Audio Inputs                        |     |

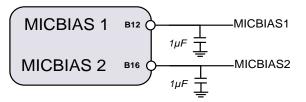

| B.2     | Microphone Bias                     |     |

| B.3     | Audio Outputs                       |     |

| B.4     | Headphone Charge Pump               |     |

|         | B.4.1 Single Supply Mode            |     |

| B.5     | Digital Interfaces                  |     |

| B.6     | References                          |     |

| B.7     | Supplies                            |     |

| B.8     | Ground                              |     |

| B.9     | Capacitor Selection                 |     |

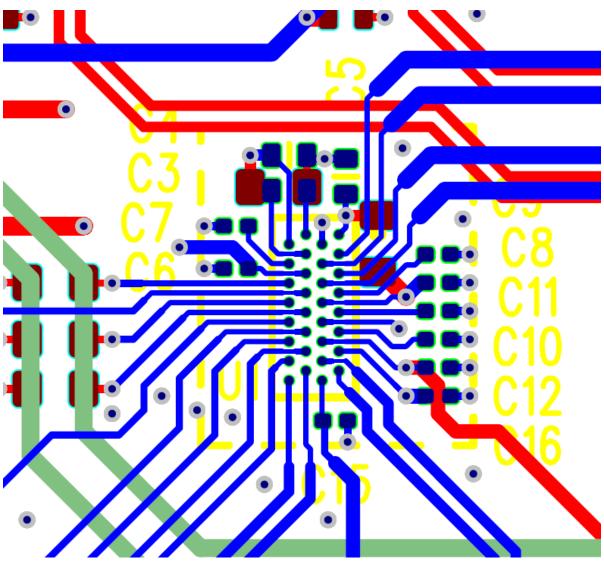

| Appendi | x C PCB Layout Guidelines           |     |

| C.1     | Layout and Schematic Support        |     |

| C.2     | General Recommendations             |     |

# **1** Terms and Definitions

| ADC              | Analog to Digital Converter                    |

|------------------|------------------------------------------------|

| AGS              | ADC Gain Swap (input Dynamic Range Extension)  |

| ALC              | Automatic Level Control                        |

| ANC              | Active Noise Cancelling                        |

| BIQ              | Biquad Filter                                  |

| CIC              | Cascaded Integrator and Comb                   |

| DAC              | Digital to Analog Converter                    |

| DAI              | Digital Audio Interface                        |

| DGS              | DAC Gain Swap (output Dynamic Range Extension) |

| DMIC             | Digital Microphone                             |

| DRE              | Dynamic Range Extension                        |

| DTMF             | Dual Tone Multi-Frequency                      |

| DWA              | Data-Weighted Averager                         |

| HBM              | Human Body Model                               |

| HPF              | High-Pass Filter                               |

| I <sup>2</sup> C | Inter-Integrated Circuit interface             |

| l²S              | Inter-IC Sound                                 |

| LDO              | Low Dropout Regulator                          |

| LPF              | Low-Pass Filter                                |

| MCLK             | Master Clock                                   |

| PC               | Program Counter                                |

| PDM              | Pulse Density Modulated                        |

| PGA              | Programmable Gain Amplifier                    |

| PLL              | Phase Locked Loop                              |

| PSRR             | Power Supply Rejection Ratio[4]                |

| RC               | Resistance-Capacitance                         |

| SC               | System Controller                              |

| SDM              | Sigma Delta Modulator                          |

| SNR              | Signal to Noise Ratio[5]                       |

| SRM              | Sample Rate Matching                           |

| SWG              | Sine Wave Generator                            |

| TDM              | Time Division Multiplexing                     |

| THD+N            | Total Harmonic Distortion plus Noise[6]        |

| VCO              | Voltage-Controlled Oscillator                  |

|                  |                                                |

# 2 Terminology

- [1] Crosstalk (dB) is the level difference between the active path output and the idle path measured signal level, at the test signal frequency. The active path is configured and supplied with an input signal capable of driving a full scale output, with the signal measured at the output of the specified idle path.

- [2] Mute Attenuation is the difference in level between the full scale output signal and the output with mute applied.

- [3] Channel Separation (dB) [left-to-right and right-to-left] is the difference in level between the active channel (driven to maximum full scale output) and the signal level measured in the idle channel at the test signal frequency. The active channel is configured and supplied with an input signal capable of driving a full scale output, with the signal measured at the output of the associated idle channel.

- [4] PSRR is the ratio of a given power supply change relative to the output signal that results from it. PSRR is measured under quiescent signal path conditions.

- [5] SNR is the difference in level between the maximum full scale output signal and the output with no input signal applied.

- [6] THD+N is the level of the rms value of the sum of harmonic distortion products plus noise in the specified bandwidth relative to the amplitude of the measured output signal.

All performance measurements carried out with 20 kHz low pass filter, and where noted an Aweighted filter. Failure to use such a filter will result in higher THD and lower SNR readings than are found in the Electrical Characteristics. The low-pass filter removes out of band noise; although it is not audible it may affect dynamic specification values.

# 3 Block Diagram

#### Figure 2: DA7217 Block Diagram

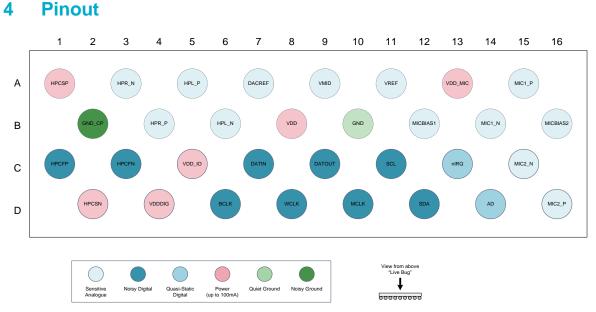

#### Figure 3: DA7217 Ballout Diagram

| Def |     |      |

|-----|-----|------|

| Dat | asn | leer |

|     |     |      |

# Table 1: DA7217 Pin Description

| Pin No.     | Pin Name           | Type (Table 2) | Description                                                                       |

|-------------|--------------------|----------------|-----------------------------------------------------------------------------------|

| Micropho    | ne Inputs          |                |                                                                                   |

| A15         | MIC1_P<br>DMIC1CLK | AI/DO          | Differential analog microphone 1 input (Pos)<br>Digital microphone 1 clock output |

| B14         | MIC1_N<br>DMIC1IN  | AI/DI          | Differential analog microphone 1 input (Neg)<br>Digital microphone 1 data input   |

| D16         | MIC2_P<br>DMIC2CLK | AI/DO          | Differential analog microphone 2 input (Pos)<br>Digital microphone 2 clock output |

| C15         | MIC2_N<br>DMIC2IN  | AI/DI          | Differential analog microphone 2 input (Neg)<br>Digital microphone 2 data input   |

| B12         | MICBIAS1           | AIO            | Microphone bias output 1                                                          |

| B16         | MICBIAS2           | AIO            | Microphone bias output 2                                                          |

| Headpho     | ne Outputs         |                |                                                                                   |

| A5          | HPL_P              | AO             | Differential headphone output (Left, Pos)                                         |

| B6          | HPL_N              | AO             | Differential headphone output (Left, Neg)                                         |

| B4          | HPR_P              | AO             | Differential headphone output (Right, Pos)                                        |

| A3          | HPR_N              | AO             | Differential headphone output (Right, Neg)                                        |

| Charge P    | ump                |                |                                                                                   |

| A1          | HPCSP              | AIO            | Charge pump reservoir capacitor (Pos)                                             |

| D2          | HPCSN              | AIO            | Charge pump reservoir capacitor (Neg)                                             |

| C1          | HPCFP              | AIO            | Charge pump flying capacitor (Pos)                                                |

| C3          | HPCFN              | AIO            | Charge pump flying capacitor (Neg)                                                |

| Digital Int | terface            |                |                                                                                   |

| D12         | SDA                | DIOD           | I <sup>2</sup> C bi-directional data                                              |

| C11         | SCL                | DI             | I <sup>2</sup> C clock                                                            |

| D14         | AD                 | DI             | I <sup>2</sup> C slave address select (high = 1B, low = 1A)                       |

| C13         | nIRQ               | DIOD           | Interrupt output (open drain active low)                                          |

| C7          | DATIN              | DIO            | DAI data input to DA7217                                                          |

| C9          | DATOUT             | DIO            | DAI data output from DA7217                                                       |

| D6          | BCLK               | DIO            | DAI bit clock                                                                     |

| D8          | WCLK               | DIO            | DAI word clock                                                                    |

| D10         | MCLK               | DI             | Master clock input                                                                |

| Reference   | es                 |                |                                                                                   |

| A7          | DACREF             | AIO            | DAC reference decoupling capacitor                                                |

| A9          | VMID               | AIO            | Mid-rail reference decoupling capacitor                                           |

| A11         | VREF               | AIO            | Bandgap reference decoupling capacitor                                            |

| Linear Re   | gulator            |                |                                                                                   |

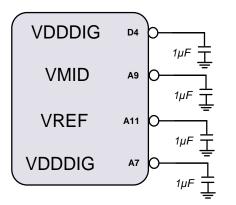

| D4          | VDDDIG             | AO             | Output from digital supply LDO                                                    |

| Supplies    |                    |                |                                                                                   |

| B8          | VDD                | AI             | Main analog supply                                                                |

**Datasheet**

**Revision 3.3**

01-Feb-2019

| Pin No. | Pin Name | Type (Table 2) | Description                          |

|---------|----------|----------------|--------------------------------------|

| A13     | VDD_MIC  | AI             | Supply for MICBIAS LDO               |

| C5      | VDD_IO   | AI             | Supply for digital interface and LDO |

| B2      | GND_CP   | AI             | Ground reference                     |

| B10     | GND      | AI             | Ground reference                     |

#### Table 2: Pin Type Definition

| Pin Type | Description                     | Pin Type | Description                   |

|----------|---------------------------------|----------|-------------------------------|

| DI       | Digital Input                   | AI       | Analog Input                  |

| DO       | Digital Output                  | AO       | Analog Output                 |

| DIO      | Digital Input/Output            | AIO      | Analog Input/Output           |

| DIOD     | Digital Input/Output open drain | SPU      | Switchable pull-up resistor   |

| PU       | Fixed pull-up resistor          | SPD      | Switchable pull-down resistor |

| PD       | Fixed pull-down resistor        |          |                               |

# 4.1 Input Pins

## 4.1.1 MIC1\_P (DMIC1CLK)

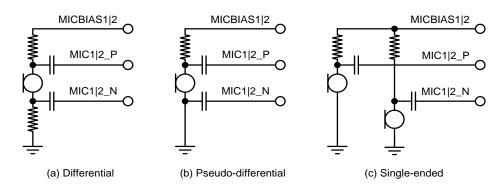

MIC1\_P is the positive differential input for the first analog microphone channel. It can be used as a single-ended input (see Figure 8).

Alternatively for digital microphones, MIC1\_P is used to provide a clock output.

#### 4.1.2 MIC1\_N (DMIC1IN)

MIC1\_N is the negative differential input for the first analog microphone channel. It can be used as a single-ended input.

Alternatively for digital microphones and active noise cancelling (ANC) applications, MIC1\_N is used as a pulse density modulated (PDM) data input.

# 4.1.3 MIC2\_P (DMIC2CLK)

MIC2\_P is the positive differential input for the second analog microphone channel. It can be used as a single-ended input.

Alternatively for digital microphones, MIC2\_P is used to provide a clock output.

#### 4.1.4 MIC2\_N (DMIC2IN)

MIC2\_N is the negative differential input for the second analog microphone channel. It can be used as a single-ended input.

Alternatively for digital microphones and ANC applications, MIC2\_N is used as a PDM data input.

#### 4.1.5 MCLK

MCLK is the master clock input pin. It is used as the main system clock either directly or via the PLL.

#### 4.1.6 SCL

SCL is the control interface (I<sup>2</sup>C) clock input and is used in conjunction with SDA to control the device.

| Datasheet | Revision 3.3 | 01-Feb-2019 |

|-----------|--------------|-------------|

| Datasneet | Revision 3.3 | 01-Feb-2019 |

# 4.1.7 AD

AD is used to select between one of two possible  $I^2C$  slave addresses by connecting the pin to GND or VDD\_IO. (High = 1B, Low = 1A).

#### 4.1.8 **DATIN**

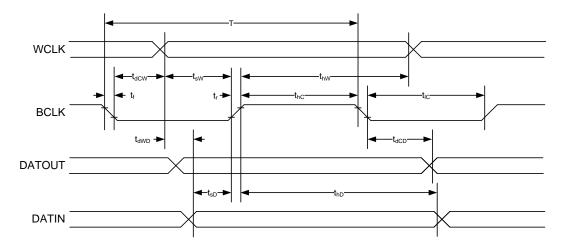

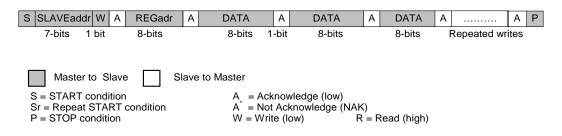

DATIN is the data input pin which forms part of the digital audio interface (DAI). It is used to present audio playback data to the device.

# 4.2 Output Pins

#### 4.2.1 nIRQ

nIRQ is the open drain active-low interrupt output to alert the host to either an accessory or a leveldetect event.

#### 4.2.2 **DATOUT**

DATOUT is the data output pin, which forms part of the DAI.

#### 4.3 **Bi-Directional Pins**

#### 4.3.1 SDA

SDA is the control interface (I<sup>2</sup>C) data input/output and is used in conjunction with SCL to control the device.

#### 4.3.2 BCLK

BCLK is the bit clock input/output pin which forms part of the DAI. It is used to clock audio data bits into or out from the device or both.

#### 4.3.3 WCLK

WCLK is the word clock input/output pin that forms part of the DAI.

# 4.4 Differential Headphone Pins

#### 4.4.1 HPL\_P

HPL\_P is the positive left-channel headphone output for a headphone speaker connected between HPL\_P and HPL\_N.

#### 4.4.2 HPL\_N

HPL\_N is the negative left-channel headphone output for a headphone speaker connected between HPL\_P and HPL\_N.

#### 4.4.3 HPR\_P

HPR\_P is the positive right-channel headphone output for a headphone speaker connected between HPR\_P and HPR\_N.

#### 4.4.4 HPR\_N

HPR\_N is the negative right-channel headphone output for a headphone speaker connected between HPR\_P and HPR\_N.

| - 4    |    |   |    |

|--------|----|---|----|

| <br>ат | 26 | n | ١. |

| αι     | as |   |    |

01-Feb-2019

## 4.5 Charge Pump Pins

#### 4.5.1 HPCSP

HPCSP is the positive output from the headphone charge pump. This pin should be connected to ground via a reservoir capacitor.

#### 4.5.2 HPCSN

HPCSN is the negative output from the headphone charge pump. If using the charge pump, this pin must be connected to ground via a reservoir capacitor. If the charge pump is not being used, then this pin should be tied directly to ground.

#### 4.5.3 HPCFP

HPCFP is one of the flying capacitor connections required by the headphone charge pump. If the charge pump is in use it must be connected to HPCFN via a capacitor. If the charge pump is not being used, then this pin can be left floating.

#### 4.5.4 HPCFN

HPCFP is one of the flying capacitor connections required by the headphone charge pump. If the charge pump is in use it must be connected to HPCFP via a capacitor. If the charge pump is not being used, then this pin can be left floating.

#### 4.6 References

#### 4.6.1 VMID

VMID is mid-rail reference decoupling capacitor connection.

#### 4.6.2 DACREF

DACREF is the DAC reference decoupling capacitor connection.

#### 4.6.3 VREF

VREF is the bandgap reference decoupling capacitor connection.

#### 4.6.4 MICBIAS1

MICBIAS1 is the first of two MICBIAS outputs. This must be decoupled with a 1 µF capacitor

#### 4.6.5 MICBIAS2

MICBIAS2 is the second of two MICBIAS outputs. This must be decoupled with a 1 µF capacitor.

#### 4.6.6 VDDDIG

VDDDIG is the internal digital supply rail decoupling pin and is used to monitor the LDO output. This must be decoupled with a 1  $\mu$ F capacitor.

# 4.7 Supply Pins

#### 4.7.1 VDD

VDD is main analog supply pin. It supplies all the analog circuits except the MICBIAS outputs and the HPAMP outputs.

| Datasheet | <b>Revision 3.3</b> |  | 01-Feb-2019 |

|-----------|---------------------|--|-------------|

|-----------|---------------------|--|-------------|

# DA7217

# **Ultra-Low Power Stereo Codec**

## 4.7.2 VDD\_IO

VDD\_IO is the supply pin for the digital input/output signals.

#### 4.7.3 VDD\_MIC

VDD\_MIC is the supply pin for the MICBIAS outputs.

#### 4.8 Ground Pins

#### 4.8.1 GND

GND is one of the two ground reference pins (the other is GND\_CP) on the device. Connect this pin to a ground plane as close as possible to the device.

#### 4.8.2 **GND\_CP**

GND\_CP is one of the two ground reference pins (the other is GND) on the device. Connect this pin to a ground plane as close as possible to the device.

**Datasheet**

# 5 Absolute Maximum Ratings

#### Table 3: Absolute Maximum Ratings (Note 1)

| Parameter          | Description                    | Conditions                                                | Min  | Max                         | Unit |

|--------------------|--------------------------------|-----------------------------------------------------------|------|-----------------------------|------|

|                    | Storage temperature            |                                                           | -65  | +165                        | °C   |

| Ta                 | Operating temperature          |                                                           | -40  | +85                         | °C   |

| V <sub>DD</sub>    | Main supply voltage            |                                                           | -0.3 | +2.75                       | V    |

| V <sub>DD_IO</sub> | Digital IO supply voltage      |                                                           | -0.3 | +5.5                        | V    |

| VDD_MIC            | Microphone bias supply voltage |                                                           | -0.3 | +5.5                        | V    |

| Vddio              | Digital IO pins                | SDA, SCL, AD, BCLK,<br>WCLK, DATIN, DATOUT,<br>MCLK, nIRQ | -0.3 | V <sub>DD_IO</sub> + 0.3    | V    |

|                    | Digital microphone IO pins     | DMIC1CLK, DMIC1IN                                         | -0.3 | VMICBIAS1 + 0.3             | V    |

|                    | Digital microphone IO pins     | DMIC2CLK, DMIC2IN                                         | -0.3 | V <sub>MICBIAS2</sub> + 0.3 | V    |

|                    | Analog input pins              | MIC1_P, MIC1_N, MIC2_P,<br>MIC2_N                         | -0.3 | V <sub>DD</sub> + 0.3       | V    |

|                    | Package thermal resistance     |                                                           | 60   |                             | °CW  |

| Vesd_hbm           | ESD susceptibility             | Human body model (HBM)                                    |      | 2                           | kV   |

**Note 1** Stresses beyond those listed under 'Absolute maximum ratings' may cause permanent damage to the device. These are stress ratings only, so functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification are not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# 6 Recommended Operating Conditions

#### Table 4: Recommended Operating Conditions

| Parameter          | Description                    | Conditions | Min  | Тур | Max   | Unit |

|--------------------|--------------------------------|------------|------|-----|-------|------|

| Ta                 | Operating temperature          |            | -25  |     | +85   | °C   |

| V <sub>DD</sub>    | Main supply voltage            |            | +1.7 |     | +2.65 | V    |

| V <sub>DD_IO</sub> | Digital IO supply voltage      |            | +1.5 |     | +3.6  | V    |

| VDD_MIC            | Microphone bias supply voltage |            | +1.8 |     | +3.6  | V    |

# 7 Electrical Characteristics

Unless otherwise stated, test conditions are as follows:  $V_{DD} = V_{DD_{-}IO} = 1.8 \text{ V}, V_{DD_{-}MIC} = 3.3 \text{ V}, V_{DDDIG} = 1.05 \text{ V}, T_a = 25 \text{ °C}, \text{MCLK} = 12.288 \text{ MHz}, \text{SR} = 48 \text{ kHz}, \text{PLL} = \text{Bypass mode}, \text{Slave mode}.$

#### Table 5: Power Consumption

| Description                                                                 | Conditions (Note 1)                                                       | Min | Тур | Max | Unit |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------|-----|-----|-----|------|

| Powerdown mode                                                              |                                                                           |     | 2.5 | 7   | μA   |

| Digital playback to headphone, no load                                      | DACL/R to HP_L/R, quiescent                                               |     | 4   |     | mW   |

| Digital playback to headphone, with load                                    | DACL/R to HP_L/R, 32 $\Omega$ load, 0.1 mW at 0 dBFS                      |     | 7.7 |     | mW   |

| Microphone stereo record                                                    | MICL/R to ADCL/R                                                          |     | 2.5 |     | mW   |

| Microphone stereo record and<br>digital playback to Headphone, no<br>load   | MICL/R to ADCL/R and DACL/R to HP_L/R, quiescent                          |     | 5.5 |     | mW   |

| Microphone stereo record and<br>digital playback to headphone, with<br>load | MICL/R to ADCL/R and DACL/R to HP_L/R, 32 $\Omega$ load, 0.1 mW at 0 dBFS |     | 8.8 |     | mW   |

Note 1  $V_{DD} = V_{DD\_IO} = V_{DD\_MIC} = 1.8 V$

#### **Table 6: Electrical Characteristics: Microphone Bias**

| Description                  | Condition                                                       | Min      | Тур | Max | Unit              |

|------------------------------|-----------------------------------------------------------------|----------|-----|-----|-------------------|

| Programmable output voltage  | No load, V <sub>DD_MIC</sub> ><br>V <sub>MICBIAS</sub> + 200 mV | 1.6      |     | 3.0 | V                 |

| Output voltage step          |                                                                 |          | 200 |     | mV                |

| Output current               | Output voltage droop < 50 mV                                    | 2        |     |     | mA                |

| Power supply rejection ratio | 20 Hz to 2 kHz<br>2 kHz to 20 kHz                               | 70<br>50 |     |     | dB                |

| Output voltage noise         | V <sub>MICBIAS</sub> ≤ 2.2 V                                    |          | 5   |     | μV <sub>RMS</sub> |

#### Table 7: Electrical Characteristics: Microphone Amplifier

| Description                  | Condition                                                             | Min      | Тур                   | Max | Unit              |

|------------------------------|-----------------------------------------------------------------------|----------|-----------------------|-----|-------------------|

| Full-scale input signal      | 0 dB gain, single-ended                                               |          | 0.8 * V <sub>DD</sub> |     | Vpp               |

|                              | 0 dB gain, differential                                               |          | 1.6 * V <sub>DD</sub> |     | VPP               |

| Input resistance             |                                                                       | 12       | 15                    | 18  | kΩ                |

| Programmable gain            |                                                                       | -6       |                       | 36  | dB                |

| Gain step size               |                                                                       |          | 6                     |     | dB                |

| Absolute gain accuracy       | 0 dB @ 1 kHz                                                          | -0.5     |                       | 0.5 | dB                |

| Gain step error              | 20 Hz to 20 kHz                                                       | -0.1     |                       | 0.1 | dB                |

| Input noise level            | Inputs connected to GND,<br>24 dB gain, input-referred,<br>A-weighted |          | 5                     |     | µV <sub>RMS</sub> |

| Amplitude ripple             | 20 Hz to 20 kHz                                                       | -0.5     |                       | 0.5 | dB                |

| Power supply rejection ratio | 20 Hz to 2 kHz<br>2 kHz to 20 kHz                                     | 90<br>70 |                       |     | dB                |

#### Datasheet

| Description | Condition       | Min | Тур | Max | Unit |

|-------------|-----------------|-----|-----|-----|------|

| Crosstalk   | 20 Hz to 20 kHz |     | 88  |     | dB   |

#### Table 8: Electrical Characteristics: Input Amplifier

| Description                  | Condition       | Min  | Тур                   | Max | Unit     |

|------------------------------|-----------------|------|-----------------------|-----|----------|

| Full-scale input signal      | 0 dB gain       |      | 1.6 * V <sub>DD</sub> |     | $V_{PP}$ |

| Programmable gain            |                 | -4.5 |                       | 18  | dB       |

| Gain step size               |                 |      | 1.5                   |     | dB       |

| Absolute gain accuracy       | 0 dB @ 1 kHz    | -0.5 |                       | 0.5 | dB       |

| Gain step error              | 20 Hz to 20 kHz | -0.1 |                       | 0.1 | dB       |

| Amplitude ripple             | 20 Hz to 20 kHz | -0.5 |                       | 0.5 | dB       |

| Power supply rejection ratio | 20 Hz to 2 kHz  | 90   |                       |     | dB       |

|                              | 2 kHz to 20 kHz | 70   |                       |     | uD       |

## Table 9: Electrical Characteristics: ADC

| Description                          | Condition                         | Min      | Тур                   | Max | Unit |

|--------------------------------------|-----------------------------------|----------|-----------------------|-----|------|

| Full-scale input signal              | 0 dBFS digital output level       |          | 1.6 * V <sub>DD</sub> |     | Vpp  |

| Signal to noise ratio                | A-weighted                        |          | 90                    |     | dB   |

| Dynamic range                        | ADC DRE enabled,<br>A-weighted    |          | 105                   |     | dB   |

| Total harmonic distortion plus noise | -1 dBFS ADC output level          |          | -85                   |     | dB   |

| Power supply rejection ratio         | 20 Hz to 2 kHz<br>2 kHz to 20 kHz | 70<br>50 |                       |     | dB   |

#### Table 10: Electrical Characteristics: DAC

| Description                          | Condition                         | Min      | Тур                   | Max | Unit     |

|--------------------------------------|-----------------------------------|----------|-----------------------|-----|----------|

| Full-scale output signal             | 0 dBFS digital input level        |          | 1.6 * V <sub>DD</sub> |     | $V_{PP}$ |

| Signal to noise ratio                | A-weighted                        |          | 100                   |     | dB       |

| Dynamic range                        | DAC DRE enabled,<br>A-weighted    |          | 110                   |     | dB       |

| Total harmonic distortion plus noise | -1 dBFS digital input level       |          | -90                   |     | dB       |

| Power supply rejection ratio         | 20 Hz to 2 kHz<br>2 kHz to 20 kHz | 70<br>50 |                       |     | dB       |

## Table 11: Electrical Characteristics: Headphone Amplifier

| Description                                            | Condition                                                           | Min | Тур       | Max | Unit     |

|--------------------------------------------------------|---------------------------------------------------------------------|-----|-----------|-----|----------|

| Full-scale output signal                               | No load                                                             |     | 1.6 * Vdd |     | $V_{PP}$ |

| DC output offset                                       | −30 dB gain                                                         |     |           | 250 | μV       |

| Maximum output power per channel<br>(charge pump mode) | $V_{DD}$ = 1.8 V, THD < 0.005 %,<br>R <sub>LOAD</sub> = 32 Ω, 1 kHz |     | 30        |     |          |

Datasheet

| Description                          | Condition                                                                                                                                                   | Min      | Тур  | Max  | Unit          |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|------|---------------|

|                                      | $\label{eq:VDD} \begin{array}{l} V_{\text{DD}} = 2.5 \ \text{V}, \ \text{THD} < 0.005 \ \%, \\ R_{\text{LOAD}} = 32 \ \Omega, \ 1 \ \text{kHz} \end{array}$ |          | 58   |      |               |

| Maximum output power per channel     | $V_{DD}$ = 1.8 V, THD < 0.1 %,<br>R <sub>LOAD</sub> = 32 $\Omega$ , 1 kHz                                                                                   |          | 19   |      |               |

| (single supply mode)                 | $\label{eq:VDD} \begin{array}{l} V_{DD} = 2.5 \ V, \ THD < 0.1 \ \%, \\ R_{LOAD} = 32 \ \Omega, \ 1 \ \text{kHz} \end{array}$                               |          | 49   |      |               |

| Quiescent current per channel        |                                                                                                                                                             |          |      | 150  | μA            |

| Load resistance                      |                                                                                                                                                             | 26       | 32   |      | Ω             |

| Load capacitance                     |                                                                                                                                                             |          |      | 500  | pF            |

| Load inductance                      |                                                                                                                                                             |          |      | 400  | μH            |

| Frequency Response                   | 20 Hz to 20 kHz                                                                                                                                             | -0.5     |      | +0.5 | dB            |

| Signal to noise ratio                | V <sub>DD</sub> = 1.8 V, 0 dB gain<br>A-weighted                                                                                                            |          | 98   |      | dB            |

|                                      | V <sub>DD</sub> = 2.5 V, 0 dB gain<br>A-weighted                                                                                                            |          | 100  |      | dB            |

| Output noise level                   | 20 Hz to 20 kHz, < -20 dB gain                                                                                                                              |          |      | 2.5  | $\mu V_{RMS}$ |

| Total harmonic distortion plus noise | $V_{\text{DD}} = 1.8 \text{ V},  \text{R}_{\text{LOAD}} = 32  \Omega,  \text{-} \\ \text{5 dBFS, 1 kHz}$                                                    |          | -88  |      | dB            |

| Channel separation [3]               | $V_{DD} = 1.8V, R_{LOAD} = 32 \Omega,$<br>1 kHz                                                                                                             |          | -110 |      | dB            |

| Programmable gain                    |                                                                                                                                                             | -57      |      | 6    | dB            |

| Gain step size                       |                                                                                                                                                             |          | 1.5  |      | dB            |

| Absolute gain accuracy               | 0 dB @ 1 kHz                                                                                                                                                | -0.5     |      | 0.5  | dB            |

| Left/right gain mismatch             | 20 Hz to 20 kHz                                                                                                                                             | -0.1     |      | 0.1  | dB            |

| Gain step error                      | 20 Hz to 20 kHz                                                                                                                                             | -0.1     |      | 0.1  | dB            |

| Amplitude ripple                     | 20 Hz to 20 kHz                                                                                                                                             | -0.5     |      | 0.5  | dB            |

| Mute attenuation [2]                 |                                                                                                                                                             |          | -70  |      | dB            |

| Power supply rejection ratio         | 20 Hz to 2 kHz<br>2 kHz to 20 kHz                                                                                                                           | 70<br>50 |      |      | dB            |

# Table 12: Electrical Characteristics: Output Amplifier

| Description                  | Condition                  | Min  | Тур       | Мах | Unit |

|------------------------------|----------------------------|------|-----------|-----|------|

| Full-scale input signal      | 0 dBFS output from the DAC |      | 1.6 * Vdd |     | VPP  |

| Programmable gain            |                            | -1.0 |           | 0   | dB   |

| Gain step size               |                            |      | 0.5       |     | dB   |

| Absolute gain accuracy       | 0 dB @ 1 kHz               | -0.5 |           | 0.5 | dB   |

| Amplitude ripple             | 20 Hz to 20 kHz            | -0.5 |           | 0.5 | dB   |

| Power supply rejection ratio | 20 Hz to 2 kHz             | 90   |           |     | dB   |

|                              | 2 kHz to 20 kHz            | 70   |           |     | uD   |

#### **Table 13: Electrical Characteristics: Input Filters**

| Description           | Condition                                                      | Min       | Тур                           | Мах                   | Unit |

|-----------------------|----------------------------------------------------------------|-----------|-------------------------------|-----------------------|------|

| Pass band             |                                                                |           |                               | 0.45 * F <sub>S</sub> | Hz   |

| Pass band ripple      | Voice mode<br>Music mode                                       |           |                               | ±0.3<br>±0.1          | dB   |

| Stop band             | F <sub>S</sub> ≤ 48 kHz<br>F <sub>S</sub> = 88.2 kHz or 96 kHz | 0.56 * Fs |                               | 7 * Fs<br>3.5 * Fs    | Hz   |

| Stop band attenuation | Voice mode<br>Music mode                                       | 70<br>55  |                               |                       | dB   |

| Group delay           | Voice mode<br>Music mode<br>Fs = 88.2 kHz or 96 kHz            |           | 4.3 / Fs<br>18 / Fs<br>9 / Fs |                       | S    |

| Gain step size        |                                                                |           | 0.75                          |                       | dB   |

| Programmable gain     |                                                                | -83.25    |                               | 12                    | dB   |

#### Table 14: Electrical Characteristics: Automatic Level Control

| Description                 | Condition               | Min   | Тур | Max   | Unit |

|-----------------------------|-------------------------|-------|-----|-------|------|

| Attack rate                 | F <sub>S</sub> = 48 kHz | 1.6   |     | 6500  | dB/s |

| Release rate                | F <sub>S</sub> = 48 kHz | 1.6   |     | 1675  | dB/s |

| Hold time                   | F <sub>S</sub> = 48 kHz | 1.3   |     | 42300 | ms   |

| Maximum threshold           |                         | -94.5 |     | 0     | dBFS |

| Minimum threshold           |                         | -94.5 |     | 0     | dBFS |

| Noise threshold             |                         | -94.5 |     | 0     | dBFS |

| Threshold step size         |                         |       | 1.5 |       | dB   |

| Maximum overall gain        |                         | 0     |     | 90    | dB   |

| Maximum overall attenuation |                         | 0     |     | 90    | dB   |

| Maximum analog gain         |                         | 0     |     | 36    | dB   |

| Minimum analog gain         |                         | 0     |     | 36    | dB   |

| Gain step size              |                         |       | 1.5 |       | dB   |

| Table 15: Electrical Characteristics: DAC Filter Specifications |

|-----------------------------------------------------------------|

|-----------------------------------------------------------------|

| Description                             | Conditions                                                                      | Min          | Тур                           | Мах                   | Unit |

|-----------------------------------------|---------------------------------------------------------------------------------|--------------|-------------------------------|-----------------------|------|

| Pass band                               |                                                                                 |              |                               | 0.45 * F <sub>S</sub> | Hz   |

| Pass band ripple                        | Voice mode<br>Music mode                                                        |              |                               | ±0.3<br>±0.1          | dB   |

| Stop band                               | $F_S \le 48 \text{ kHz}$<br>$F_S = 88.2 \text{ kHz} \text{ or } 96 \text{ kHz}$ | 0.56 *<br>Fs |                               | 7 * Fs<br>3.5 * Fs    | Hz   |

| Stop band attenuation                   | Voice mode<br>Music mode                                                        | 70<br>55     |                               |                       | dB   |

| Group delay                             | Voice mode<br>Music mode<br>Fs = 88.2 kHz or 96 kHz                             |              | 4.3 / Fs<br>18 / Fs<br>9 / Fs |                       | s    |

| Group delay variation                   | 20 Hz to 20 kHz                                                                 |              | 1                             |                       | μs   |

| Left/right channel group delay mismatch |                                                                                 |              | 2                             |                       | μs   |

| Gain step size                          |                                                                                 |              | 0.75                          |                       | dB   |

| Programmable gain                       |                                                                                 | -83.25       |                               | 108                   | dB   |

# Table 16: Electrical Characteristics: High-Pass Filter (Input and Output, ADC in High-Power Mode)

| out_1_voice_en /<br>in_1_voice_en | out_1_voice_hpf_corner<br>in_1_voice_hpf_corner | out_1_audio_hpf_corner/<br>in_1_audio_hpf_corner |      |        |      |      | SR Sam | ole Rate | e (kHz) |                             |           |          |         |

|-----------------------------------|-------------------------------------------------|--------------------------------------------------|------|--------|------|------|--------|----------|---------|-----------------------------|-----------|----------|---------|

|                                   | ier /<br>ier                                    | her/<br>her                                      | 8    | 11.025 | 12   | 16   | 22.05  | 24       | 32      | 44.1                        | 48        | 88.2     | 96      |

|                                   |                                                 | 00                                               | 0.33 | 0.46   | 0.5  | 0.67 | 0.92   | 1        | 1.33    | 1.84                        | 2         | 3.68     | 4       |

| 0                                 |                                                 | 01                                               | 0.67 | 0.92   | 1    | 1.33 | 1.84   | 2        | 2.67    | 3.68                        | 4         | 7.35     | 8       |

| 0                                 |                                                 | 10                                               | 1.33 | 1.84   | 2    | 2.67 | 3.68   | 4        | 5.33    | 7.35                        | 8         | 14.7     | 16      |

|                                   |                                                 | 11                                               | 2.67 | 3.68   | 4    | 5.33 | 7.35   | 8        | 10.67   | 14.7                        | 16        | 29.4     | 32      |

|                                   | 000                                             |                                                  | 2.5  | 3.45   | 3.75 | 5    | 6.89   | 7.5      | 10      |                             |           |          |         |

|                                   | 001                                             |                                                  | 25   | 34.5   | 37.5 | 50   | 68.9   | 75       | 100     |                             |           |          |         |

|                                   | 010                                             |                                                  | 50   | 68.9   | 75   | 100  | 137.8  | 150      | 200     |                             |           |          |         |

| 1                                 | 011                                             |                                                  | 100  | 137.8  | 150  | 200  | 275.6  | 300      | 400     | Voice HPF not available for |           |          | ole for |

|                                   | 100                                             |                                                  | 150  | 206.7  | 225  | 300  | 413.4  | 450      | 600     | sampl                       | e rates a | above 32 | 2 kHz.  |

|                                   | 101                                             |                                                  | 200  | 275.6  | 300  | 400  | 551.3  | 600      | 800     |                             |           |          |         |

|                                   | 110                                             |                                                  | 300  | 413.4  | 450  | 600  | 826.9  | 900      | 1200    |                             |           |          |         |

|                                   | 111                                             |                                                  | 400  | 551.3  | 600  | 800  | 1102.5 | 1200     | 1600    |                             |           |          |         |

| in_1_voice_en<br>out_1_voice_en | in_1_voice_hpf_corner<br>out_1_voice_hpf_corner | in_1_audio_hpf_corner<br>out_1_audio_hpf_corner. |      |           |        |         | SR Sam   | ple Ra     | te (kHz)              |               |                      |                   |                      |                 |

|---------------------------------|-------------------------------------------------|--------------------------------------------------|------|-----------|--------|---------|----------|------------|-----------------------|---------------|----------------------|-------------------|----------------------|-----------------|

|                                 | er<br>1er                                       | er<br>Ier.                                       | 8    | 11.025    | 12     | 16      | 22.05    | 24         | 32                    | 44.1          | 48                   | 88.2              | 96                   |                 |

|                                 |                                                 | 00                                               | 0.33 | 0.46      | 0.5    | 0.67    | 0.92     | 1          | 32 kHz                | 1.84          | 2                    | 88.2              |                      |                 |

|                                 |                                                 | 01                                               | 0.67 | 0.92      | 1      | 1.33    | 1.84     | 2          | rate not<br>available | available 7.3 | 3.68                 | 4                 | and 96 kHz<br>sample |                 |

| 0                               |                                                 | 10                                               | 1.33 | 1.84      | 2      | 2.67    | 3.68     | 4          |                       |               | available<br>in Low- | 7.35              | 8                    | rates<br>availa |

|                                 |                                                 | 11                                               | 2.67 | 3.68      | 4      | 5.33    | 7.35     | 8          | Power<br>mode         | 14.7          | 16                   | Low-Power<br>mode |                      |                 |

|                                 | 000                                             |                                                  | 2.5  |           |        |         |          |            |                       |               |                      |                   |                      |                 |

|                                 | 001                                             |                                                  | 25   |           |        |         |          |            |                       |               |                      |                   |                      |                 |

|                                 | 010                                             |                                                  | 50   |           |        |         |          |            |                       |               |                      |                   |                      |                 |

|                                 | 011                                             |                                                  | 100  |           |        | -l- (l  |          | <b>-</b> : |                       |               | -1                   | - 6 0 1-11        | L_                   |                 |

| 1                               | 100                                             |                                                  | 150  | in iow-po | wer mo | ae, the | VOICE HP | F IS ON    | y available a         | at a sam      | pie rate             | OT 8 KH           | IZ                   |                 |

|                                 | 101                                             |                                                  | 200  |           |        |         |          |            |                       |               |                      |                   |                      |                 |

|                                 | 110                                             |                                                  | 300  |           |        |         |          |            |                       |               |                      |                   |                      |                 |

|                                 | 111                                             |                                                  | 400  |           |        |         |          |            |                       |               |                      |                   |                      |                 |

# Table 17: High-Pass Filter Settings (ADC in Low-Power Mode)

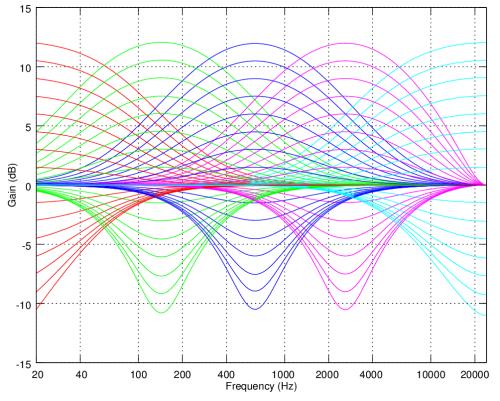

## Table 18: Electrical Characteristics: 5-Band Equalizer

| FS (kHz) | Center Frequency (Hz) At Programmed Setting |        |               |        |        |  |  |  |

|----------|---------------------------------------------|--------|---------------|--------|--------|--|--|--|

|          | Band 1                                      | Band 2 | Band 3        | Band 4 | Band 5 |  |  |  |

| 8        | 0                                           | 99     | 493           | 1528   | 4000   |  |  |  |

| 11.025   | 0                                           | 136    | 680           | 2106   | 5512   |  |  |  |

| 12       | 0                                           | 148    | 740           | 2293   | 6000   |  |  |  |

| 16       | 0                                           | 96     | 440           | 2128   | 8000   |  |  |  |

| 22.05    | 0                                           | 133    | 607           | 2933   | 11025  |  |  |  |

| 24       | 0                                           | 145    | 660           | 3191   | 12000  |  |  |  |

| 32       | 0                                           | 95     | 418           | 1797   | 16000  |  |  |  |

| 44.1     | 0                                           | 131    | 576           | 2386   | 22050  |  |  |  |

| 48       | 0                                           | 143    | 627           | 2596   | 24000  |  |  |  |

| 88.2     |                                             |        | Not available |        |        |  |  |  |

| 96       |                                             |        |               |        |        |  |  |  |

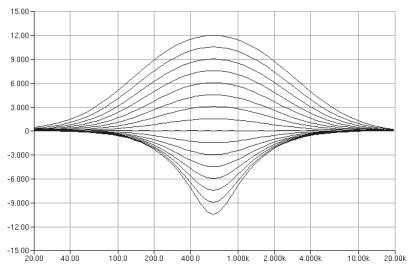

Figure 4: 5-Band Equalizer Response at 48 kHz

## Table 19: PLL Mode

| Description                                      | Conditions                                                |   | Тур | Max | Unit  |

|--------------------------------------------------|-----------------------------------------------------------|---|-----|-----|-------|

| MCLK input jitter                                | Absolute jitter (rms) (Note 1)                            |   |     | 540 | ps    |

| MCLK input frequency                             | Normal mode                                               | 2 |     | 54  | MHz   |

| SRM tracking range                               | RM tracking range DAI slave mode WCLK frequency variation |   |     | 4   | %     |

| SRM tracking rate DAI slave mode WCLK drift rate |                                                           |   |     | 54  | ppm/s |

| Note 1 Jitter in the 100 Hz to 40 kHz band |  |

|--------------------------------------------|--|

|--------------------------------------------|--|

#### Table 20: Bypass Mode

| Description Conditions |                                                                                                  | Min | Тур               | Max | Unit |

|------------------------|--------------------------------------------------------------------------------------------------|-----|-------------------|-----|------|

| MCLK input jitter      | Absolute jitter (rms) (Note 1)                                                                   |     |                   | 540 | ps   |

| MCLK input frequency   | F <sub>S</sub> = 11.025, 22.05, 44.1, 88.2 kHz<br>F <sub>S</sub> = 8, 12, 16, 24, 32, 48, 96 kHz |     | 11.2896<br>12.288 |     | MHz  |

Note 1 Jitter in the 100 Hz to 40 kHz band

| _ |     |      |      |

|---|-----|------|------|

| n | ats | heh  | leet |

|   | atc | 1311 | ICCL |

#### Table 21: Tone Generator

| Description                | Conditions                                      | Min | Тур         | Max   | Unit   |

|----------------------------|-------------------------------------------------|-----|-------------|-------|--------|

| Single-tone frequency      | F <sub>S</sub> = 8, 12, 16, 24, 32, 48, 96 kHz  | 1   |             | 12000 | Hz     |

|                            | Fs = 11.025, 22.05, 44.1, 88.2 kHz              | 1   |             | 11025 |        |

| Single-tone frequency step | Fs = 8, 12, 16, 24, 32, 48, 96 kHz              |     | 0.18        |       | Hz     |

|                            | $F_{S} = 11.025, 22.05, 44.1, 88.2 \text{ kHz}$ |     | 0.17        |       |        |

| Dual-tone modulation       |                                                 |     | 697         |       | Hz     |

| frequency A                |                                                 |     | 770         |       |        |

|                            |                                                 |     | 852         |       |        |

|                            |                                                 |     | 941         |       |        |

| Dual-tone modulation       |                                                 |     | 1209        |       | Hz     |

| frequency B                |                                                 |     | 1336        |       |        |

|                            |                                                 |     | 1477        |       |        |

|                            |                                                 |     | 1633        |       |        |

| Output signal level        |                                                 |     | 0           |       | dBFS   |

| On/off pulse duration      |                                                 | 10  |             | 2000  | ms     |

| On/off pulse step size     | 10 ms to 200 ms duration                        |     | 10          |       | ms     |

|                            | 200 ms to 2000 ms duration                      |     | 50          |       |        |

| On/off pulse repeat        | Programmable                                    |     | 1, 2, 3, 4, |       | Cycles |

|                            | Continuous                                      |     | 5,6∞        |       |        |

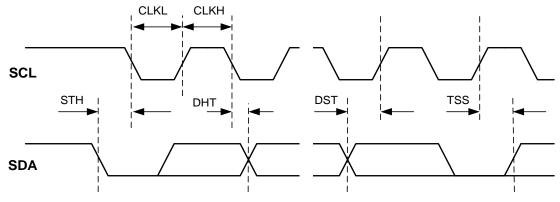

# 8 Digital Interfaces

## Table 22: I/O Characteristics

| Parameter       | Description                                                            | Conditions              | Min                         | Тур | Мах                            | Unit |

|-----------------|------------------------------------------------------------------------|-------------------------|-----------------------------|-----|--------------------------------|------|

| Viн             | SCL, SDA, MCLK, BCLK,<br>WCLK, DATIN, DATOUT, AD<br>Input HIGH voltage |                         | 0.7 * V <sub>DD_IO</sub>    |     |                                | V    |

| VIL             | SCL, SDA, MCLK, BCLK,<br>WCLK, DATIN, DATOUT<br>Input LOW voltage      |                         |                             |     | 0.3 * V <sub>DD_</sub> io      | V    |

| V <sub>OL</sub> | SDA, nIRQ<br>Output LOW voltage                                        | I <sub>OUT =</sub> 3 mA |                             |     | 0.24                           | V    |

| Vон             | DMIC1CLK<br>Output HIGH voltage                                        |                         | 0.7 * VMICBIAS1             |     |                                |      |