### **Description**

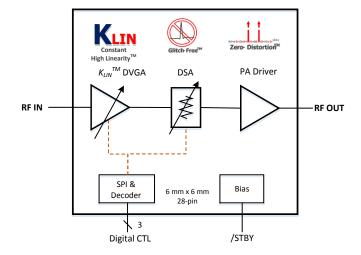

The F1455 is a High Gain / High Linearity 1400 MHz to 2300 MHz TX Digital Variable Gain Amplifier used in transmitter applications.

The F1455 TX DVGA provides 32.8 dB maximum gain with +38.5 dBm OIP3 and 3.9 dB noise figure. Up to 29.5 dB gain control is achieved using the combination of a digital step attenuator (DSA) and a  $K_{LIN}^{TM}$  RF Digital Gain Amplifier. This device uses a single 5 V supply and 220 mA of I<sub>CC</sub>.

This device is packaged in a 6 mm x 6 mm, 28-pin QFN with 50  $\Omega$  single-ended RF input and RF output impedances for ease of integration into the signal-path.

### **Competitive Advantage**

In typical Base Stations, RF VGAs are used in the TX traffic paths to drive the transmit power amplifier. The F1455 TX DVGA offers very high reliability due to its construction from a monolithic silicon die in a QFN package. The F1455 is configured to provide an optimum balance of noise and linearity performance consisting of a  $K_{LIN}^{TM}$  RF amplifier, digital step attenuator (DSA) and a PA driver amplifier. The  $K_{LIN}^{TM}$  amplifier maintains the OIP3 and output P1dB performance over an extended attenuation range when compared to competitive devices.

## **Typical Applications**

- Multi-mode. Multi-carrier Transmitters

- PCS1900 Base Stations

- DCS1800 Base Stations

- WiMAX and LTE Base Stations

- UMTS/WCDMA 3G Base Stations

- PHS/PAS Base Stations

- Public Safety Infrastructure

#### **Features**

- Broadband 1400 MHz to 2300 MHz

- 32.8 dB max gain

- 3.9 dB NF @ max gain (2000 MHz)

- 29.5 dB total gain control range, 0.5 dB step

- < 2 dB overshoot between gain transitions</p>

- Maintains flat +23 dBm OP1dB for more than 13 dB gain adjustment range

- Maintains flat +38.5 dBm OIP3 for more than 15 dB gain adjustment range

- SPI interface for DSA control

- Single 5 V supply voltage

- I<sub>CC</sub> = 220 mA

- Up to +105 °C T<sub>CASE</sub> operating temperature

- 50 Ω input and output impedance

- Standby mode for power savings

- Pin compatible with 700 MHz and 2700 MHz versions

- 6 mm x 6 mm, 28-pin QFN package

### **Block Diagram**

Figure 1. Block Diagram

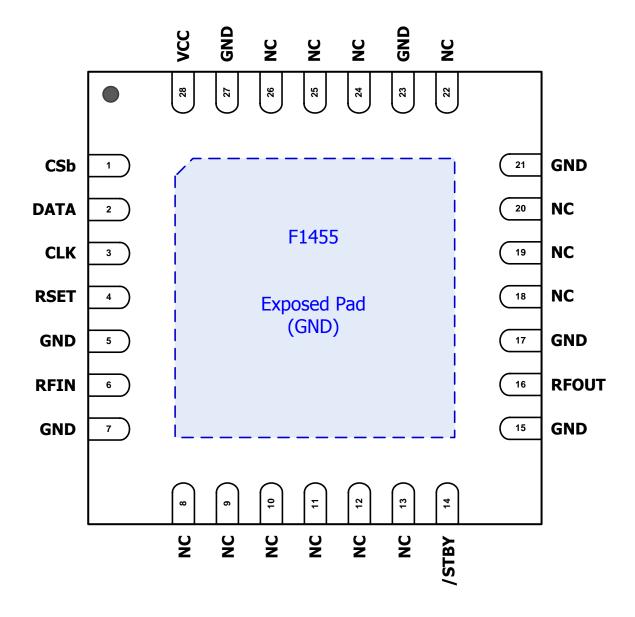

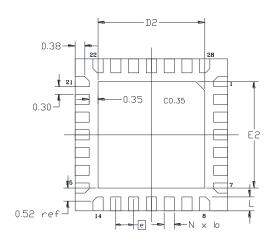

## **Pin Assignments**

Figure 2. Pin Assignments for 6 mm x 6 mm x 0.9 mm QFN Package – Top View

# **Pin Descriptions**

**Table 1. Pin Descriptions**

| Number                                                    | Name  | Description                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                         | CSb   | Chip Select Input: 1.8 V or 3.3 V logic compatible.                                                                                                                                                                                                                    |

| 2                                                         | DATA  | Data Input: 1.8 V or 3.3 V logic compatible.                                                                                                                                                                                                                           |

| 3                                                         | CLK   | Clock Input: 1.8 V or 3.3 V logic compatible.                                                                                                                                                                                                                          |

| 4 [a]                                                     | RSET  | Connect 1.74 kΩ external resistor to GND to set amplifier bias.                                                                                                                                                                                                        |

| 5, 7, 15, 17,<br>21, 23, 27                               | GND   | Pins internally tied to exposed paddle. Connect to ground on PCB.                                                                                                                                                                                                      |

| 6                                                         | RFIN  | RF input internally matched to 50 Ω. Must use external DC block.                                                                                                                                                                                                       |

| 8, 9, 10, 11,<br>12, 13, 18,<br>19, 20, 22,<br>24, 25, 26 | NC    | No internal connection. These pins can be left unconnected, voltage applied, or connected to ground (recommended).                                                                                                                                                     |

| 14                                                        | /STBY | Standby pin. With Logic Low applied to this pin or with this pin left open, the amplifier is powered off with the SPI still powered on. With Logic High applied to this pin the part is in full operation mode.                                                        |

| 16                                                        | RFOUT | RF output internally matched to 50 Ω. Must use external DC block.                                                                                                                                                                                                      |

| 28                                                        | VCC   | 5 V Power Supply. Connect to V <sub>cc</sub> and use bypass capacitors as close to the pin as possible.                                                                                                                                                                |

|                                                           | — ЕР  | Exposed Pad. Internally connected to GND. Solder this exposed pad to a PCB pad that uses multiple ground vias to provide heat transfer out of the device into the PCB ground planes. These multiple ground vias are also required to achieve the noted RF performance. |

a. External resistor on pin 4 used to optimize the overall device for DC current and linearity performance across the entire frequency band.

## **Absolute Maximum Ratings**

Stresses above those listed below may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Table 2. Absolute Maximum Ratings**

| Parameter                                                 | Symbol               | Minimum                | Maximum                | Units |

|-----------------------------------------------------------|----------------------|------------------------|------------------------|-------|

| V <sub>cc</sub> to GND                                    | V <sub>CC</sub>      | -0.5                   | 5.5                    | ٧     |

| DATA, CSb, CLK, /STBY                                     | $V_{Cntrl}$          | -0.5                   | V <sub>CC</sub>        | V     |

| RSET                                                      | I <sub>RSET</sub>    |                        | +1.5                   | mA    |

| RFIN externally applied DC voltage                        | $V_{RFIN}$           | +1.4                   | +3.6                   | V     |

| RFOUT externally applied DC voltage                       | $V_{RFOUT}$          | V <sub>CC</sub> - 0.15 | V <sub>CC</sub> + 0.15 | V     |

| RF Input Power (RFIN) applied for 24 hours max. [a]       | P <sub>max_in</sub>  |                        | +12                    | dBm   |

| RF Output Power (RFOUT) present for 24 hours maximum [a]  | P <sub>max_out</sub> |                        | +26                    | dBm   |

| Continuous Power Dissipation                              | P <sub>diss</sub>    |                        | 1.75                   | W     |

| Junction Temperature                                      | Tj                   |                        | 150                    | °C    |

| Storage Temperature Range                                 | T <sub>st</sub>      | -65                    | 150                    | °C    |

| Lead Temperature (soldering, 10s)                         |                      |                        | 260                    | °C    |

| ElectroStatic Discharge – HBM<br>(JEDEC/ESDA JS-001-2012) |                      |                        | 2000<br>(Class 2)      | V     |

| ElectroStatic Discharge – CDM (JEDEC 22-C101F)            |                      |                        | 1000<br>(Class C3)     | V     |

a. Exposure to these maximum RF levels can result in significantly higher  $l_{cc}$  current draw due to overdriving the amplifier stages.

# **Recommended Operating Conditions**

## **Table 3. Recommended Operating Conditions**

| Parameter                                 | Symbol            | Condition               | Minimum | Typical | Maximum | Units |

|-------------------------------------------|-------------------|-------------------------|---------|---------|---------|-------|

| Power Supply Voltage                      | Vcc               |                         | 4.75    |         | 5.25    | V     |

| Operating Temperature Range               | T <sub>CASE</sub> | Exposed Paddle          | -40     |         | +105    | °C    |

| RF Frequency Range                        | $F_RF$            |                         | 1400    |         | 2300    | MHz   |

| Maximum Operating Average RF Output Power |                   | $Z_S = Z_L = 50 \Omega$ |         |         | 14      | dBm   |

| RFIN Port Impedance                       | $Z_{RFI}$         | Single Ended            |         | 50      |         | Ω     |

| RFOUT Port Impedance                      | Z <sub>RFO</sub>  | Single Ended            |         | 50      |         | Ω     |

#### **Electrical Characteristics - General**

See Typical Application Circuit. Unless otherwise stated, specifications apply when operated as a TX VGA,  $V_{CC}$  = +5.0 V,  $F_{RF}$  = 1.88 GHz,  $T_{CASE}$  = +25 °C, /STBY = High,  $Z_S$  =  $Z_L$  = 50  $\Omega$ , maximum gain setting.

**Table 4. Electrical Characteristics**

| Parameter                                         | Symbol                            | Condition                                                           | Minimum | Typical | Maximum         | Units     |

|---------------------------------------------------|-----------------------------------|---------------------------------------------------------------------|---------|---------|-----------------|-----------|

| Logic Input High Threshold                        | V <sub>IH</sub>                   | JEDEC 1.8V or 3.3V logic                                            | 1.1 [a] |         | V <sub>cc</sub> | V         |

| Logic Input Low Threshold                         | V <sub>IL</sub>                   | JEDEC 1.8V or 3.3V logic                                            | -0.3    |         | 0.8             | V         |

| Lania Cumant                                      | I <sub>IH</sub> , I <sub>IL</sub> | SPI                                                                 | -1      |         | +1              |           |

| Logic Current                                     | I <sub>STBY</sub>                 | /STBY                                                               | -10     |         | +10             | μA        |

| DC Current                                        | Icc                               |                                                                     |         | 220     | 250             | mA        |

| Standby Current                                   | I <sub>CC_STBY</sub>              | /STBY = Low                                                         |         | 1       | 2               | mA        |

| Standby Switching Time                            | T <sub>STBY</sub>                 | 50% /STBY control to within 0.2 dB of the on state final gain value |         | 250     |                 | ns        |

| Gain Step                                         | G <sub>STEP</sub>                 | Least Significant Bit                                               |         | 0.5     |                 | dB        |

| Maximum Attenuator Glitching                      | $ATTN_G$                          | Any state to state transition                                       |         | 2       |                 | dB        |

|                                                   |                                   | F <sub>RF</sub> = 1.40 GHz                                          | -0.47   |         | +0.33           | -<br>- dB |

| Maximum Step Error (DNL)                          | ERROR <sub>STEP</sub>             | F <sub>RF</sub> = 1.70 GHz                                          | -0.38   |         | +0.28           |           |

| [Over Recommended Supply Voltage Range, Operating |                                   | F <sub>RF</sub> = 1.88 GHz                                          | -0.30   |         | +0.28           |           |

| Temperature Range, All Attenuation                | LINIONSIEP                        | F <sub>RF</sub> = 2.00 GHz                                          | -0.27   |         | +0.25           |           |

| States ]                                          |                                   | F <sub>RF</sub> = 2.10 GHz                                          | -0.26   |         | +0.23           |           |

|                                                   |                                   | F <sub>RF</sub> = 2.30 GHz                                          | -0.20   |         | +0.32           |           |

| Maximum Absolute Error (INL)                      | <b>ERROR</b> <sub>ABS</sub>       |                                                                     |         | 0.8     |                 | dB        |

| Gain Settling Time [c]                            | $G_{ST}$                          | 50% of CSb to 10% / 90% RF                                          |         | 200     |                 | ns        |

| SPI @                                             |                                   |                                                                     |         |         |                 |           |

| Serial Clock Speed                                | Fclock                            |                                                                     |         |         | 25              | MHz       |

| CSb to CLK Setup Time                             | $T_{LS}$                          |                                                                     | 5       |         |                 | ns        |

| CLK to Data Hold Time                             | Тн                                |                                                                     | 5       |         |                 | ns        |

| CSb Trigger to CLK Setup Time                     | $T_LC$                            |                                                                     | 5       |         |                 | ns        |

- a. Items in min/max columns in **bold italics** are Guaranteed by Test.

- b. Items in min/max columns that are not bold/italics are Guaranteed by Design Characterization.

- c. Excludes SPI write time.

- d. SPI 3 wire bus (refer to serial Control Mode Timing diagram).

#### **Electrical Characteristics - RF**

See Typical Application Circuit. Unless otherwise stated, specifications apply when operated as a TX VGA,  $V_{CC}$  = +5.0 V,  $F_{RF}$  = 1.88 GHz,  $T_{CASE}$  = +25 °C, /STBY = High,  $Z_S$  =  $Z_L$  = 50  $\Omega$ , maximum gain setting. Evaluation Kit trace and connector losses are de-embedded.

**Table 5. Electrical Characteristics**

| Parameter                          | Symbol              | Condition                                                      | Minimum  | Typical | Maximum | Units |

|------------------------------------|---------------------|----------------------------------------------------------------|----------|---------|---------|-------|

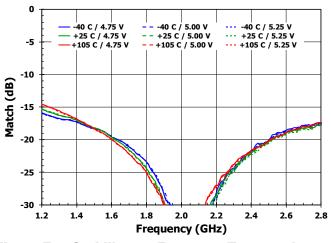

| RF Input Return Loss               | RL <sub>RFIN</sub>  |                                                                |          | 15      |         | dB    |

| RF Output Return Loss              | RL <sub>RFOUT</sub> |                                                                |          | 13      |         | dB    |

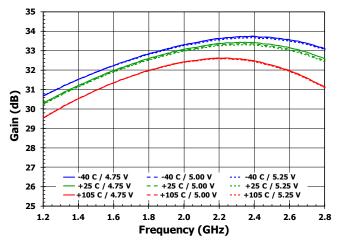

| Gain - Max Gain Setting            | G <sub>MAX</sub>    |                                                                | 31.0 [a] | 32.8    | 34.6    | dB    |

| Gain - Min Gain Setting            | G <sub>MIN</sub>    | Max attenuation                                                | 1.0      | 2.8     | 4.6     | dB    |

| Gain Flatness                      | G <sub>FLAT</sub>   | F <sub>RF</sub> = 1800 MHz to 2200 MHz                         |          | 0.7 [c] |         | dB    |

|                                    |                     | 0 dB attenuation                                               |          | 3.9     |         |       |

| Maios Figuro                       | NF                  | 10 dB attenuation                                              |          | 6.8     |         | dB    |

| Noise Figure                       | INF                 | 20 dB attenuation                                              |          | 13.4    |         | UB    |

|                                    |                     | 29.5 dB attenuation                                            |          | 22.6    |         |       |

|                                    | oint OIP3           | 0 dB attenuation Pout = +7 dBm / tone 5 MHz tone separation    |          | 38.5    |         |       |

|                                    |                     | 6 dB attenuation Pin = -21 dBm / tone 5 MHz tone separation    |          | 38.3    |         |       |

| Output Third Order Intercept Point |                     | 10 dB attenuation Pin = -21 dBm / tone 5 MHz tone separation   | 35       | 38      |         | dBm   |

|                                    |                     | 20 dB attenuation Pin = -21 dBm / tone 5 MHz tone separation   |          | 33.6    |         |       |

|                                    |                     | 29.5 dB attenuation Pin = -21 dBm / tone 5 MHz tone separation |          | 23      |         |       |

|                                    |                     | 0 dB attenuation                                               |          | 23.4    |         |       |

| Output 1dB Compression Point       | OP1dB               | 0 dB attenuation,<br>T <sub>CASE</sub> = +105 °C               |          | 22.8    |         | dBm   |

|                                    |                     | 6 dB attenuation                                               | 21.5     | 23.3    |         |       |

- a. Items in min/max columns in **bold italics** are Guaranteed by Test.

- b. Items in min/max columns that are not bold/italics are Guaranteed by Design Characterization.

- c. Includes a positive slope feature over the noted RF range to compensate for typical system roll-off.

#### **Thermal Characteristics**

#### **Table 6. Package Thermal Characteristics**

| Parameter                                                                    | Symbol        | Value | Units |

|------------------------------------------------------------------------------|---------------|-------|-------|

| Junction to Ambient Thermal Resistance.                                      | $\theta_{JA}$ | 40    | °C/W  |

| Junction to Case Thermal Resistance. (Case is defined as the exposed paddle) | θЈС           | 4     | °C/W  |

| Moisture Sensitivity Rating (Per J-STD-020)                                  |               | MSL 1 |       |

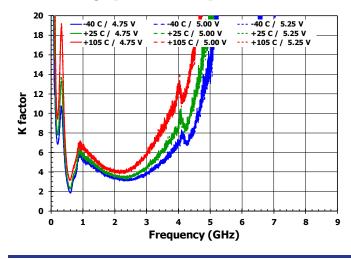

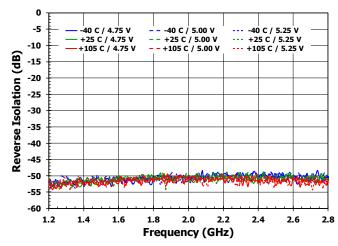

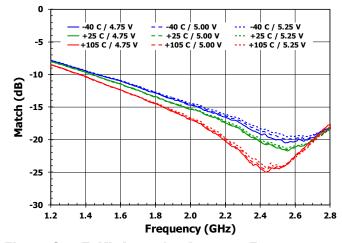

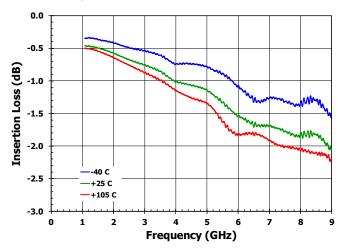

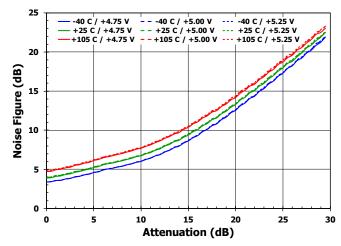

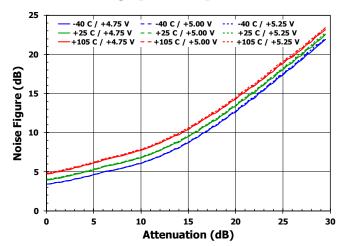

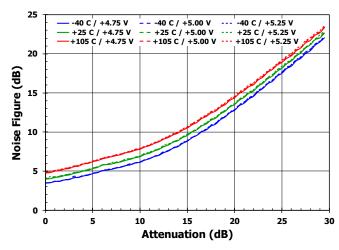

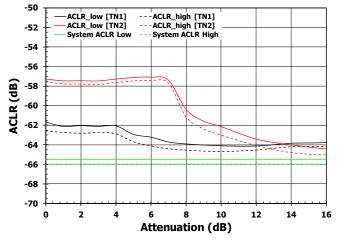

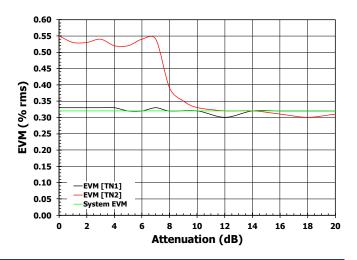

## **Typical Operating Conditions (TOC)**

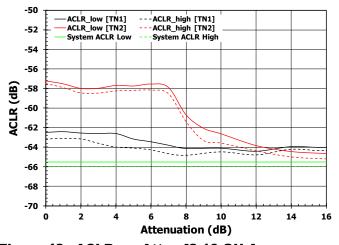

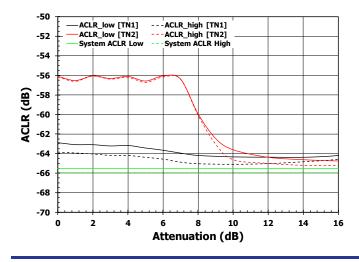

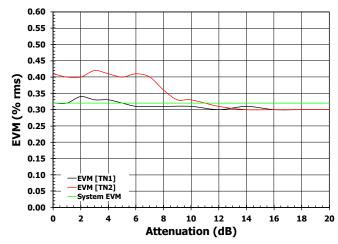

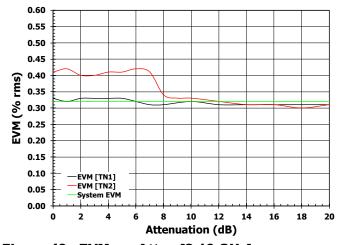

Unless otherwise stated the typical operating graphs were measured under the following conditions:

- V<sub>cc</sub> = 5.0 V

- Z<sub>L</sub> = Z<sub>S</sub> = 50 Ohms Single Ended

- F<sub>RF</sub> = 1.88 GHz

- T<sub>CASE</sub> = +25 °C

- /STBY = High

- 5 MHz Tone Spacing

- Gain setting = Maximum Gain

- All temperatures are referenced to the exposed paddle

- ACLR measurements used with a Basic LTE FDD Downlink 20 MHz TM1.2 Test signal

- EVM measurements used with a Basic LTE FDD Downlink 20 MHz TM3.1 Test signal

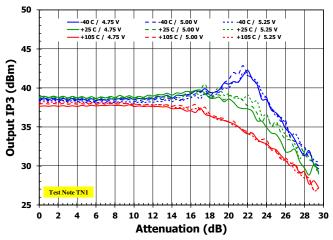

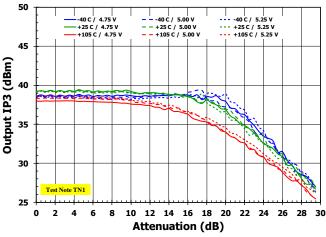

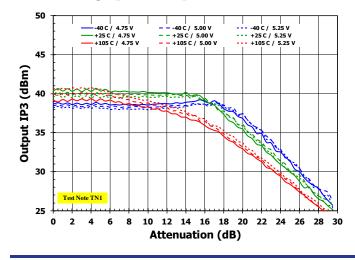

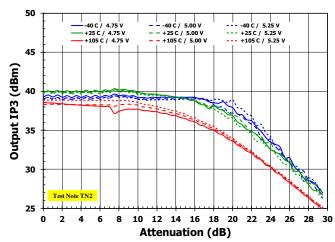

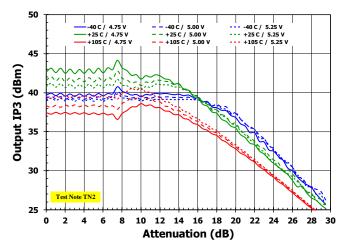

- Note TN1: Atten ≤ 4 dB Fixed Pout = 7 dBm per waveform or per tone, Atten > 4 dB Fixed Pin = -21 dBm per waveform or per tone

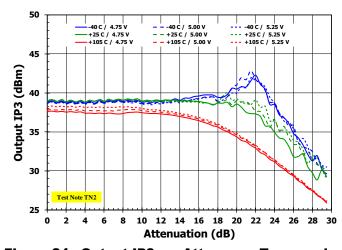

- Note TN2: Atten ≤ 7 dB Fixed Pout = 10.5 dBm per waveform or per tone, Atten > 7 dB Fixed Pin = -14.5 dBm per waveform or per tone

- Evaluation Kit traces and connector losses are de-embedded

Figure 3. Maximum Gain vs. Freq over Temp and Voltage [Attn = 0.0 dB]

Figure 5. Input Return Loss vs. Freq over Temp and Voltage [Attn = 0.0 dB]

Figure 7. Stability vs. Freq over Temp and Voltage [Attn = 0.0 dB]

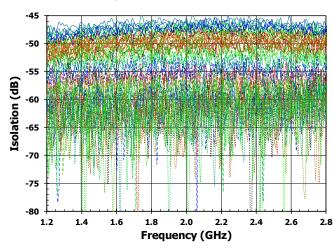

Figure 4. Reverse Isolation vs. Freq over Temp and Voltage [Attn = 0.0 dB]

Figure 6. Output Return Loss vs. Freq over Temp. and Voltage [Attn = 0.0 dB]

Figure 8. EvKit Insertion Loss vs. Freq over Temp

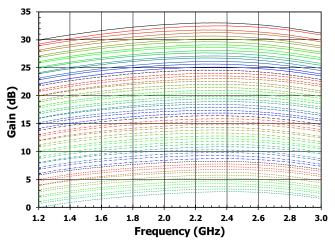

Figure 9. Gain vs. Freq [+25 °C, All States]

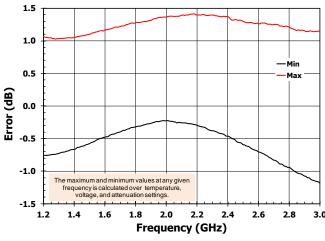

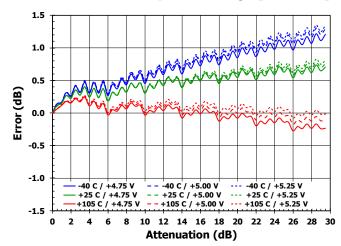

Figure 11. Worse Case Attenuator Absolute Accuracy vs. Freq [All parameters]

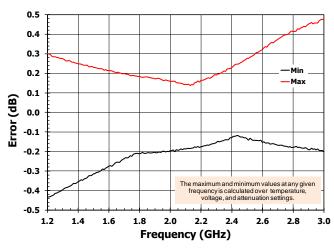

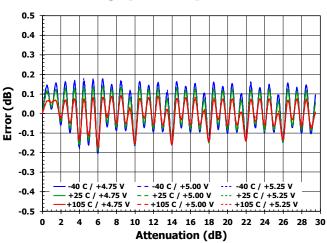

Figure 13. Worse Case Step Accuracy vs. Freq [All parameters]

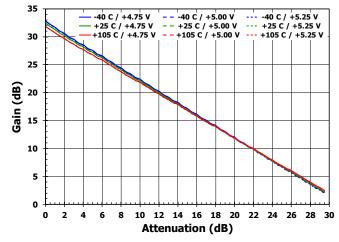

Figure 10. Gain vs. Atten over Temp and Voltage [1.88 GHz]

Figure 12. Attenuator Absolute Accuracy vs.

Atten over Temp and Voltage [1.88 GHz]

Figure 14. Step Accuracy vs. Atten over Temp and Voltage [1.88 GHz]

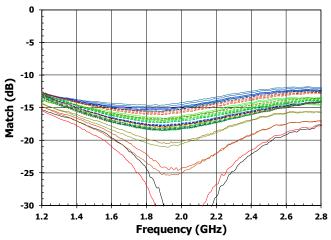

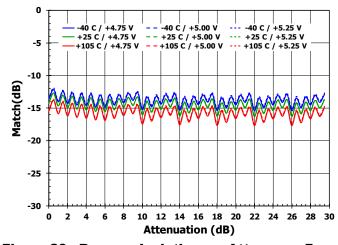

Figure 15. Input Return Loss vs. Freq [+25  $^{\circ}$ C, All states]

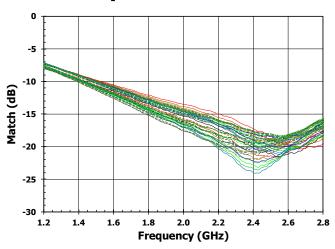

Figure 17. Output Return Loss vs. Freq [+25  $^{\circ}$ C, All states]

Figure 19. Reverse Isolation vs. Freq [+25  $^{\circ}$ C, All states]

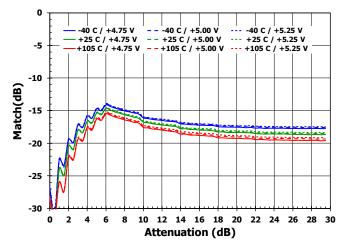

Figure 16. Input Return Loss vs. Atten over Temp and Voltage [1.88 GHz]

Figure 18. Output Return Loss vs. Atten over Temp and Voltage [1.88 GHz]

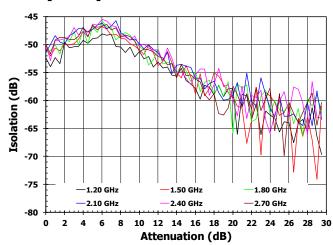

Figure 20. Reverse Isolation vs. Atten over Freq [+25 °C]

Figure 21. Output IP3 vs. Atten over Temp and Voltage [1.70 GHz]

Figure 23. Output IP3 vs. Atten over Temp and Voltage [1.88 GHz]

Figure 25. Output IP3 vs. Atten over Temp and Voltage [2.10 GHz]

Figure 22. Output IP3 vs. Atten over Temp and Voltage [1.70 GHz]

Figure 24. Output IP3 vs. Atten over Temp and Voltage [1.88 GHz]

Figure 26. Output IP3 vs. Atten over Temp and Voltage [2.10 GHz]

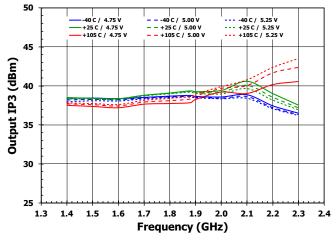

Figure 27. Output IP3 vs. Freq over Temp and Voltage [Attn = 0.0 dB]

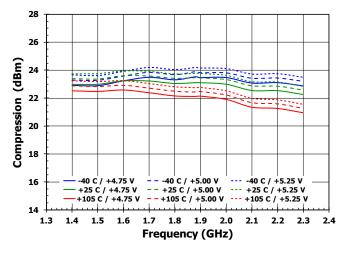

Figure 29. Output P1dB vs. Freq over Temp and Voltage [Attn = 0.0 dB]

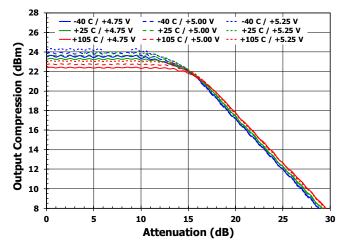

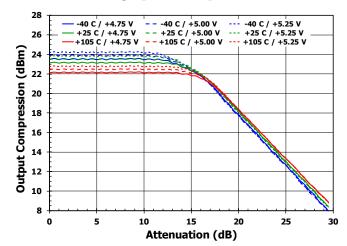

Figure 28. Output P1dB vs. Atten over Temp and Voltage [1.70 GHz]

Figure 30. Output P1dB vs. Atten over Temp and Voltage [1.88 GHz]

Figure 31. Output P1dB vs. Atten over Temp and Voltage [2.10 GHz]

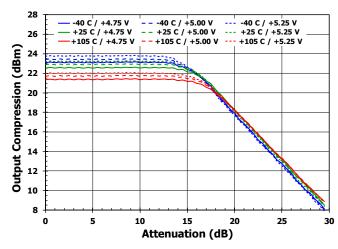

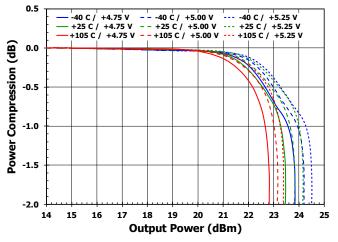

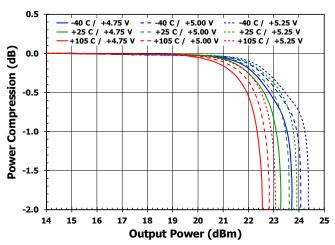

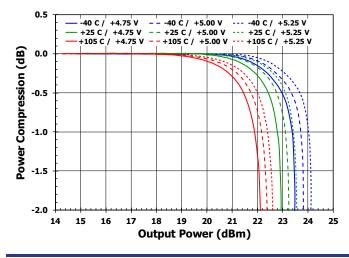

Figure 32. Gain Compression vs. Pout over Temp and Voltage [1.70 GHz]

Figure 34. Gain Compression vs. Pout over Temp and Voltage [1.88 GHz]

Figure 36. Gain Compression vs. Pout over Temp and Voltage [2.10 GHz]

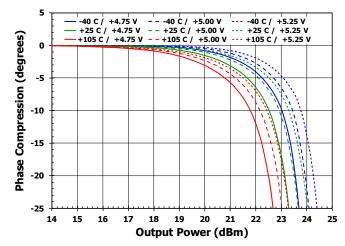

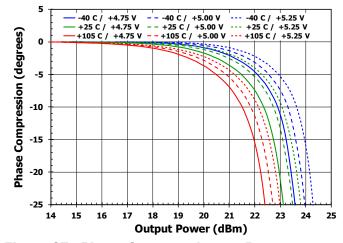

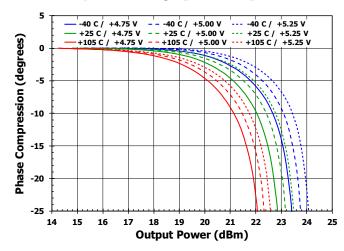

Figure 33. Phase Compression vs. Pout over Temp and Voltage [1.70 GHz]

Figure 35. Phase Compression vs. Pout over Temp and Voltage [1.88 GHz]

Figure 37. Phase Compression vs. Pout over Temp and Voltage [2.10 GHz]

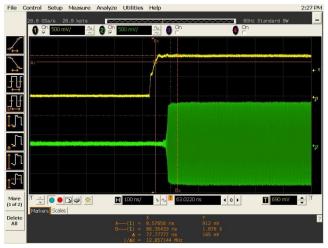

Figure 38. Switching Speed 31.5 to 0.0 dB

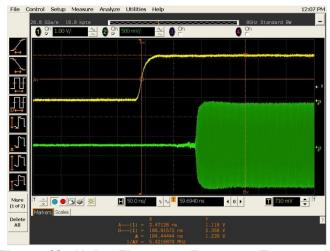

Figure 40. Standby Switching Off to On

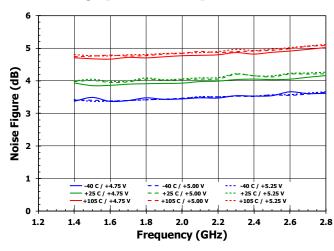

Figure 42. Noise Figure vs. Freq over Temp and Voltage [Attn = 0.0 dB]

Figure 39. Noise Figure vs. Atten over Temp and Voltage [1.70 GHz]

Figure 41. Noise Figure vs. Atten over Temp and Voltage [1.88 GHz]

Figure 43. Noise Figure vs. Atten over Temp and Voltage [2.10 GHz]

Figure 44. ACLR vs. Atten [1.70 GHz]

Figure 46. ACLR vs. Atten [1.88 GHz]

Figure 48. ACLR vs. Atten [2.10 GHz]

Figure 45. EVM vs. Atten [1.70 GHz]

Figure 47. EVM vs. Atten [1.88 GHz]

Figure 49. EVM vs. Atten [2.10 GHz]

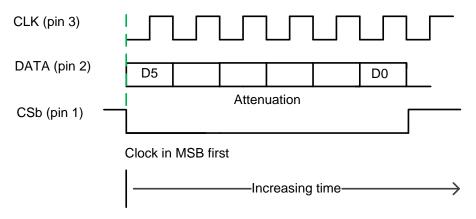

### **Serial Port Interface**

Serial data is formatted as a 6-bit word clocking data in MSB first.

**Table 7. Attenuation Word Truth Table**

|    |    |    | Attenuator |    |    |             |

|----|----|----|------------|----|----|-------------|

| D5 | D4 | D3 | D2         | D1 | D0 | Setting [a] |

| 1  | 1  | 1  | 1          | 1  | 1  | 0.0 dB      |

| 1  | 1  | 1  | 1          | 1  | 0  | 0.5 dB      |

| 1  | 1  | 1  | 1          | 0  | 1  | 1.0 dB      |

| 1  | 1  | 1  | 0          | 1  | 1  | 2.0 dB      |

| 1  | 1  | 0  | 1          | 1  | 1  | 4.0 dB      |

| 1  | 0  | 1  | 1          | 1  | 1  | 8.0 dB      |

| 0  | 1  | 1  | 1          | 1  | 1  | 16.0 dB     |

| 0  | 0  | 0  | 1          | 0  | 0  | 29.5 dB     |

| 0  | 0  | 0  | 0          | 1  | 1  | 29.5 dB     |

| 0  | 0  | 0  | 0          | 1  | 0  | 29.5 dB     |

| 0  | 0  | 0  | 0          | 0  | 1  | 29.5 dB     |

| 0  | 0  | 0  | 0          | 0  | 0  | 29.5 dB     |

a. The attenuation setting is designed to operate from 0 dB (111111) to 29.5 dB (000100).

Figure 50. Serial Register Timing Diagram

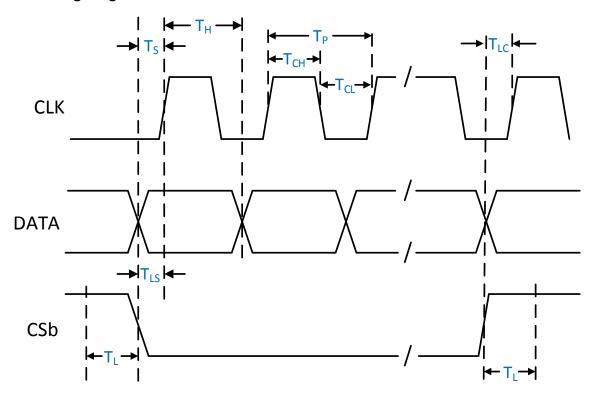

Figure 51. SPI Timing Diagram

**Table 8. SPI Timing Diagram Values for Figure 51**

| Parameter                         | Symbol         | Test Condition | Min | Тур | Max | Units |

|-----------------------------------|----------------|----------------|-----|-----|-----|-------|

| CLK Frequency                     | Fc             |                |     |     | 25  | MHz   |

| CLK High Duration Time            | Тсн            |                | 20  |     |     | ns    |

| CLK Low Duration Time             | $T_CL$         |                | 20  |     |     | ns    |

| DATA to CLK Setup Time            | Ts             |                | 5   |     |     | ns    |

| CLK Period [a]                    | $T_P$          |                | 40  |     |     | ns    |

| CLK to DATA Hold Time             | T <sub>H</sub> |                | 5   |     |     | ns    |

| CSb to CLK Setup Time             | $T_{LS}$       |                | 5   |     |     | ns    |

| CSb Trigger Pulse Width           | $T_L$          |                | 10  |     |     | ns    |

| CSb Trigger to CLK Setup Time [b] | $T_LC$         |                | 5   |     |     | ns    |

a.  $(T_{CH} + T_{CL}) \ge 1/F_C$

**Table 9. Standby Truth Table**

| /STBY (pin 14) | Condition                         |

|----------------|-----------------------------------|

| 0 V            | Amplifier OFF with SPI powered ON |

| $V_{cc}$       | Full operation                    |

b. Once all desired DATA is clocked in,  $T_{LC}$  represents the time a CSb high needs to occur before any subsequent CLK signals.

### **Application Information**

The F1455 has been optimized for use in high performance RF applications from 1700 MHz to 2300 MHz. The device maintains good performance outside of the optimized band as shown by the Typical Performance Characteristics.

#### **Power Up Attenuation Setting**

When the part is initially powered up, the default VGA setting is the 29.5 dB [000000] attenuation state.

#### Chip Select (CSb)

When CSb is set to logic high, the CLK input is disabled. When CSb is set to logic low, the CLK input is enabled and the DATA word can be programmed into the shift registers. The programmed word is then latched into the F1455 on the CSb rising edge (refer to Figure 51). The operation of the SPI bus in independent of the /STBY pin setting (see Standby Mode section below).

#### Standby Mode (/STBY)

The F1455 has a power down feature for power savings. Connecting pin 14 to a logic high will enable the device. With a logic low applied to pin 14 or with pin 14 left open (internal 1  $M\Omega$  pull down to ground) the amplifier is placed in standby mode. The Standby mode is a high isolation state. The level of this isolation is not specified and is dependent on the device. In Standby mode the SPI bus is operational and the device attenuation setting can be programmed. Therefore, the device will present the desired attenuation when it is enabled.

#### **Power Supplies**

A common  $V_{CC}$  power supply should be used for all power supply pins. To minimize noise and fast transients de-coupling capacitors should be placed at all supply pins. Supply noise can degrade noise figure and fast transients can trigger ESD clamps causing them to fail. Supply voltage change or transients should have a slew rate smaller than 1 V / 20  $\mu$ s. In addition, all control pins should remain at 0 V ( $\pm$  0.3 V) while the supply voltage ramps or while it returns to zero.

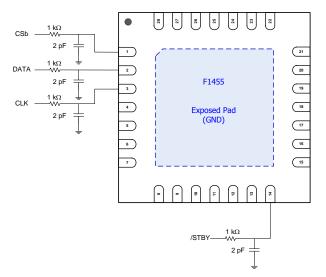

#### **Control Pin Interface**

If control signal integrity is a concern and clean signals cannot be guaranteed due to overshoot, undershoot, ringing, etc., the following circuit at the input of each control pin is recommended. This applies to SPI and control pins 1, 2, 3 and 14 as shown below. Note the recommended resistor and capacitor values do not necessarily match the EV kit BOM for the case of poor control signal integrity. For multiple devices driven by a single control line, the component values will need to be adjusted accordingly so as not to load down the control line.

Figure 52. Control Pin Interface for Signal Integrity

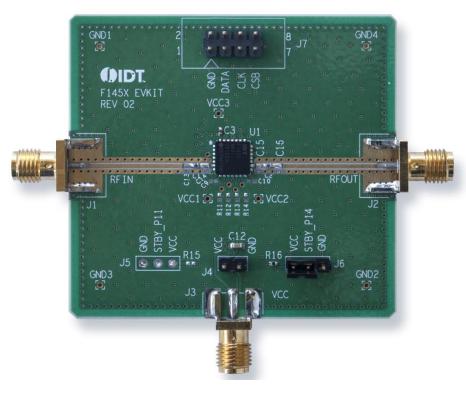

## **Evaluation Kit Picture**

## Figure 53. Top View

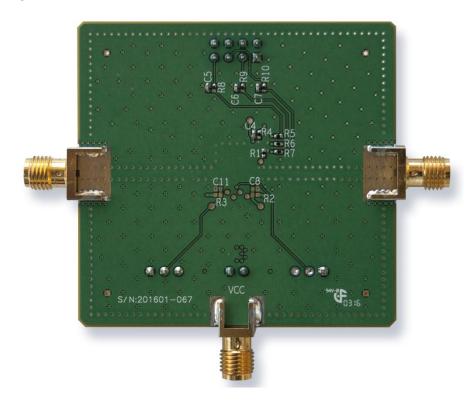

Figure 54. Bottom View

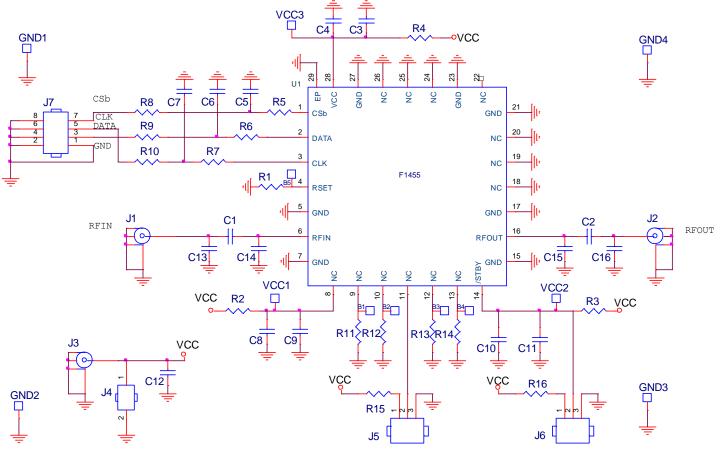

## **Evaluation Kit / Applications Circuit**

#### Figure 55. Electrical Schematic

Not All Components are used. Please check the Bill of Material (BOM) table.

## Table 10. Bill of Material (BOM)

| Part Reference                                | QTY | Description                                      | Manufacturer Part # | Manufacturer    |

|-----------------------------------------------|-----|--------------------------------------------------|---------------------|-----------------|

| C1, C2                                        | 2   | 22 pF ±5%, 50V, C0G Ceramic Capacitor (0402)     | GRM1555C1H220J      | MURATA          |

| C3                                            | 1   | 100 nF ±10%, 16V, X7R Ceramic Capacitor (0402)   | GRM155R71C104K      | MURATA          |

| C4                                            | 1   | 1000 pF ±5%, 50V, C0G Ceramic Capacitor (0402)   | GRM1555C1H102J      | MURATA          |

| C5, C6, C7                                    | 3   | 2 pF ±0.1pF, 50V, C0G Ceramic Capacitor (0402)   | GRM1555C1H2R0B      | MURATA          |

| C12                                           | 1   | 10 uF ±20%, 16V, X6S Ceramic Capacitor (0603)    | GRM188C81C106M      | MURATA          |

| R1                                            | 1   | 1.74 kΩ ±1%, 1/10W, Resistor (0402)              | ERJ-2RKF1741X       | PANASONIC       |

| R4 - R7                                       | 4   | 0 Ω Resistors (0402)                             | ERJ-2GE0R00X        | PANASONIC       |

| R8 - R10, R16                                 | 4   | 1 kΩ ±1%, 1/10W, Resistor (0402)                 | ERJ-2RKF1001X       | PANASONIC       |

| J4                                            | 1   | CONN HEADER VERT SGL 2 X 1 POS GOLD              | 961102-6404-AR      | 3M              |

| J6                                            | 1   | CONN HEADER VERT SGL 3 X 1 POS GOLD              | 961103-6404-AR      | 3M              |

| J7                                            | 1   | CONN HEADER VERT DBL 4 X 2 POS GOLD              | 67997-108HLF        | FCI             |

| J1, J2                                        | 2   | Edge Launch SMA (0.375 inch pitch ground, tab)   | 142-0701-851        | Emerson Johnson |

| J3                                            | 1   | Edge Launch SMA (0.250 inch pitch ground, round) | 142-0711-821        | Emerson Johnson |

| U1                                            | 1   | VGA AMP                                          | F1455NKGI           | IDT             |

| C8 - C11, C13 - C16,<br>R2, R3, R11 - R15, J5 |     | DNP<br>(Do Not Populate)                         |                     |                 |

|                                               | 1   | Printed Circuit Board                            | F145X EVKIT REV 02  |                 |

## **Evaluation Kit Operation**

#### **Standby**

Connector J6 allows the F1455 to be put into the standby mode (STBY). Making no connection or connecting J6 pin 2 (the center pin) to  $V_{cc}$  the amplifier will be placed in normal operating mode. To put the F1455 into standby mode for very low power consumption ground J6 pin 2 (the center pin).

Figure 56. Image of J6 connector for Standby mode control

#### **Serial Programming Pins**

Connector J7 pins 1, 2, 4, 6, 8 are ground. Pin 3 is DATA, pin 5 is Clock (CLK), pin 7 is Chip Select (CSB).

Figure 57. Image of J7 connector for SPI

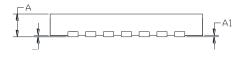

## **Package Drawings**

### Figure 58. Package Outline Drawing NKG28 PSC-4606

**TOP VIEW**

**BOTTOM VIEW**

SIDE VIEW

| SYMBOL | DIMENSION |       |       |  |  |

|--------|-----------|-------|-------|--|--|

| 6      | MIN       | NOM   | MAX   |  |  |

| D2     | 4.10      | 4.20  | 4.30  |  |  |

| E2     | 4.10      | 4.20  | 4.30  |  |  |

| L      | 0.45      | 0.55  | 0.65  |  |  |

| D      | 6.        | 00 BS | SC SC |  |  |

| Ε      | 6.        | 00 BS | SC    |  |  |

| е      | 0.70 BSC  |       |       |  |  |

| Α      | 0.80      | 0.90  | 1.00  |  |  |

| A1     | 0.00      | 0.02  | 0.05  |  |  |

| b      | 0.35      | 0.40  | 0.45  |  |  |

| N      |           | 28    |       |  |  |

| aaa    |           | 0.15  |       |  |  |

| bbb    |           | 0.10  |       |  |  |

| ССС    | 0.10      |       |       |  |  |

| ddd    | 0.05      |       |       |  |  |

| eee    | 0.08      |       |       |  |  |

| fff    |           | 0.10  |       |  |  |

### NOTES:

- 1. ALL DIMENSIONING AND TOLERANCING CONFORM TO ANSI Y14.5M-1982 2. ALL DIMENSIONS ARE IN MILLIMETERS.

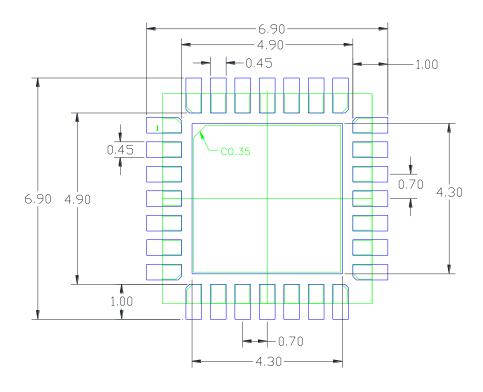

#### **Recommended Land Pattern**

#### Figure 59. Recommended Land Pattern

RECOMMENDED LAND PATTERN DIMENSION

#### NOTES:

- 1. ALL DIMENSIONS ARE IN mm. ANGLES IN DEGREES.

- 2. TOP DOWN VIEW, AS VIEWED ON PCB.

- 3. COMPONENT OUTLINE IS SHOWN FOR REFERENCE IN GREEN.

- 4. LAND PATTERN IN BLUE. NSMD PATTERN ASSUMED.

- LAND PATTERN RECOMMENDATION PER IPC-7351B GENERIC REQUIREMENT FOR SURFACE MOUNT DESIGN AND LAND PATTERN.

# **Ordering Information**

| Orderable Part Number | Package             | MSL Rating | Shipping Packaging | Temperature    |

|-----------------------|---------------------|------------|--------------------|----------------|

| F1455NKGK             | 6 x 6 x 0.9 mm QFN  | 1          | Tray               | -40° to +105°C |

| F1455NKGK8            | 6 x 6 x 0.9 mm QFN  | 1          | Tape and Reel      | -40° to +105°C |

| F1455EVBK             | Evaluation Board    |            |                    |                |

| F1455EVSK             | Evaluation Solution |            |                    |                |

# **Marking Diagram**

IDT F1455 NKGI ZS1616L Q51A028PY

- 1. Line 2 and 3 are the part number.

- 2. Line 4 "ZS" Assembly Stepping.

- 3. Line 4 "yyww = 1616" is has two digits for the year and week that the part was assembled.

- 4. Line 4 "L" denotes Assembly Site.

- 5. Line 5 "Q51A028PY" is the Assembly Lot number

## **Revision History**

| Revision Date       | Description of Change                                             |

|---------------------|-------------------------------------------------------------------|

| 2016 - July - 08    | Initial Release                                                   |

| 2016 - October - 18 | Updated Step Error specification. Other minor formatting changes. |

Corporate Headquarters 6024 Silver Creek Valley Road

San Jose, CA 95138

www.IDT.com

Sales

1-800-345-7015 or 408-284-8200 Fax: 408-284-2775

www.IDT.com/go/sales

**Tech Support**

www.IDT.com/go/support

DISCLAIMER Integrated Device Technology, Inc. (IDT) reserves the right to modify the products and/or specifications described herein at any time, without notice, at IDT's sole discretion. Performance specifications and operating parameters of the described products are determined in an independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the property of IDT or their respective third party owners. For datasheet type definitions and a glossary of common terms, visit <a href="www.idt.com/go/glossary">www.idt.com/go/glossary</a>. All contents of this document are copyright of Integrated Device Technology, Inc. All rights reserved